应用AD9444的并采用AFB技术的四通道时间交叉采样ADC系统在提高分辨率的同时,也提高了系统的采样速率。

数字、软件无线电和微电子技术的高速发展,极大的促进了模数转换电路设计的发展。模数转换器件经历了从低性能到高性能的发展过程,并产生了多种结构类型的转换器件。在对高速高性能的模数转换系统的需求不断增加的情况下,时间交叉采样法是最佳的选择。伴随着低价、高速、可配置的数字硬件平台(DSP、FPGA、CPLD和ASIC等)的出现,新的数字处理技术的发展已经为时间交叉采样法的ADC系统性能的突破开辟了道路。数字后处理方法比起传统的模拟匹配技术有很多优点,实现起来比较灵活,并且可以被设计成所期望得到的精度。

AD9444的功能和特性

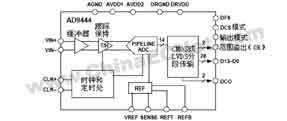

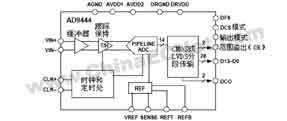

图1:AD9444的内部结构框图 |

图1是14位模数转换器(ADC)AD9444的内部结构框图。AD9444的采样速率为80MSPS,高SFDR扩大了无线基站接收机的动态范围,提高了服务质量并降低了成本。AD9444拥有片上基准电压和跟踪保持电路,输出时钟使数据的输出简单化,并且当信号超过所选择的信号范围时输出提示。AD9444的LVDS输出可连接AD6636多通道宽带数字下变频器,特别适合于TigerSHARC处理器。此外,当AD9444和AD9510时钟分配器一起使用时,AD9444便可以获得一个优良的时钟源。

AD9444具有如下特性。

100dB的双通道无杂波失真动态范围:69.3~70.3MHz;

70MHz输入时,信噪比为73.1dB,无杂波动态失真范围为97dBc;

差分非线性=±0.4LSB,积分非线性=±0.6LSB;

功耗为1.2W;

3.3V和5V的供电电压

2.0Vp-p满量程差分输入

原理及系统组成

1. 时间交叉采样法

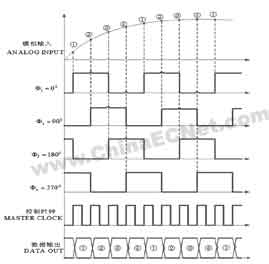

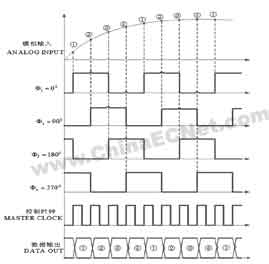

图2:四通道时间交叉采样系统数据流图 |

多路输出的时间交叉法模数转换是一个比较成熟的概念,这种方法不仅节省空间,并且能成倍提高现有的高性能ADC的采样速率,适合于需要高采样率的模数转换系统。时间交叉采样ADC系统采用的运行理念是:m路ADC中每一片ADC的采样频率是整个系统采样频率的1/m。每一路通道锁定在一个相位上,使系统作为一个整体在相等的时间间隔增量上采样,每片ADC在全速采样下得到连接完好的图像。图2给出了典型的四通道的时间交叉采样ADC系统的数据流图。最终输出的数据流是由系统中的每一通道的输出数据按照适当的顺序交叉输出产生的。

2. AFB法

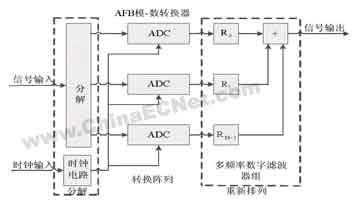

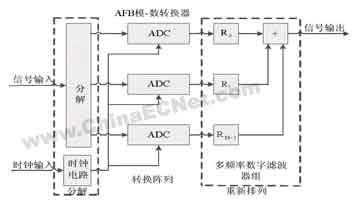

图3:AFB法基本模块框图 |

图3是AFB(Advanced Filter Bank)法的基本模块框图。通过使用特殊的多频FIR滤波器结构,AFB法可以通过一个简单的数字硬件平台实现,例如FPGA或CPLD。通过使用AFB法,时间交叉采样的ADC系统占用奈奎斯特频带的90%,并可以在任何一个转换器的奈奎斯特频带中进行设定。通过使用AFB的特殊的FIR结构和系数计算程序,就可以实现宽带宽匹配。

3. 系统组成

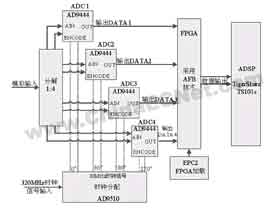

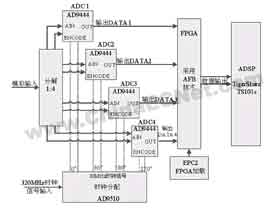

图4:基于AD9444的时间交叉采样系统 |

本系统是某雷达的数字采集部分,由4片AD9444、1片FPGA、1片TS101和1片AD9510(时钟分配)组成。系统的框图如图4所示,30MHz的中频信号输入经过ADC后进行数字滤波和正交解调,然后送入DSP内进行处理。数字带通滤波、正交解调、数字低通滤波和抽取都在FPGA内完成。由于对各通道对应的相位精确度要求比较高,本系统采用了专用的时钟分配芯片AD9510来降低操作中的误差。AD9510带有一个片上PLL核,具有多路输出的时钟分配功能和低抖动、低相位噪声的优点,可以大大提高转换性能。系统中的增益匹配、失调匹配和相位匹配直接影响着整个系统的性能,而分辨率的高低又对这三种匹配有影响。

在FPGA内采用AFB法来处理接收到的数据,以达到所期望的信号输出。AFB ADC结构克服了时间交叉采样结构对转换器之间的失配极为敏感的缺点以及开关电容结构的速度和噪声方面的限制,同时减小了由增益和相位失配引起的误差。“Advanced Filter Bank”所指的滤波器组既包括数字滤波器,也包括模拟滤波器,不同于只包括数字滤波器的普通滤波器组。AFB ADC采用模拟分解滤波器,将输入分解成m通道的模拟输入信号,系统的理想采样率为每一个转换器通道的m倍,分辨率与每一个通道的分辨率相同。

4. 系统设计注意事项

通常模数转换电路工作在混合信号(模拟和数字)的环境中,数字电路相对于模拟电路而言是一种噪声源,所以高速模数转换电路的供电及接地设计对其工作特性有较大的影响。转换电路中的高速ADC是一个混合器件,即在器件内部同时有数字电路和模拟电路两部分。为了避免数字信号耦合到模拟电路中去,数字地和模拟地通常要分开,只在一点会合。另外,模拟转换电路单电源供电设计的好坏对转换性能也有很大的影响。同接地一样,应将电路中的模拟部分和数字部分的电源线(最好是电源平面)分开,将数据转换器的数字电源按模拟电源处理。必要情况下应将模拟电源引脚与数字电源引脚用跨接电感的方式隔离。另外,在各个电源的引脚附近应分别接去耦电容,通常是0.01μF,如果空间允许的话,每个器件都应加接一个10μF的电容。

|