5-62

特点

• 两个 操作 模式

- 模式 0 - 功能上 兼容 与 行业

类型 这样的 作为 这 tr1602a 和 cdp6402

- 模式 1 - 接口 直接 与 cdp1800 系列

微处理器 无 附加 组件

• 已满 或 半双工 操作

• 奇偶校验, 框架, 和 超支 错误 检测

• 完全 可编程 与 外部 可选择 字

长度 (5-8 比特), 奇偶校验 抑制, 甚至/奇数 parity, 和

1, 1-1/2, 或 2 停止 比特

描述

这 cdp1854a/3 和 cdp1854ac/3 是 高 可靠性

硅 闸门 cmos 通用 异步 接收器/trans-

mitter (uart) 电路. 他们 是 设计 至 提供 这

必要的 格式化 和 控制 用于 接口 之间

串行 和 平行 数据. 用于 示例, 这些 uarts 可以 是

已使用 至 接口 之间 一个 外围设备 或 终端 与 串行

我/o 端口 和 这 8-有点 cdp1800-系列 微处理器

平行 数据 总线 系统. 这 cdp1854a/3 是 有能力 的 已满

双工 操作, 我.e?., 同时 换算 的 串行

输入 数据 至 平行 输出 数据 和 平行 输入 数据 至

串行 输出 数据.

这 cdp1854a/3 uart 可以 是 编程 至 操作 入点

一个 的 两个 模式 由 使用 这 模式 控制 输入. 当 这

模式 输入 是 高 (模式 = 1), 这 cdp1854a/3 是 直接

兼容 与 这 cdp1800 系列 微处理器 系统

无 附加 接口 电路. 当 这 模式 输入 是

低 (模式 = 0), 这 设备 是 功能上 兼容 与

行业 标准 uarts 这样的 作为 这 tr1602a 和

cdp6402. 它 是 也 管脚 兼容 与 这些 类型, 除了

那 管脚 2 是 已使用 用于 这 模式 控制 输入.

这 cdp1854a/3 和 这 cdp1854ac/3 是 功能上

相同. 这 cdp1854a/3 有 一个 推荐 操作

电压 范围 的 4v 至 10.5v, 和 这 cdp1854ac/3 有 一个

推荐 操作 电压 范围 的 4v 至 6.5v.

订购 信息

空调组件-

年龄

温度

范围

5v/200k

波特

10v/400k

波特

pkg.

否.

SBDIP -55

o

c 至 +125

o

c CDP1854ACD3 CDP1854ACD3 d40.6

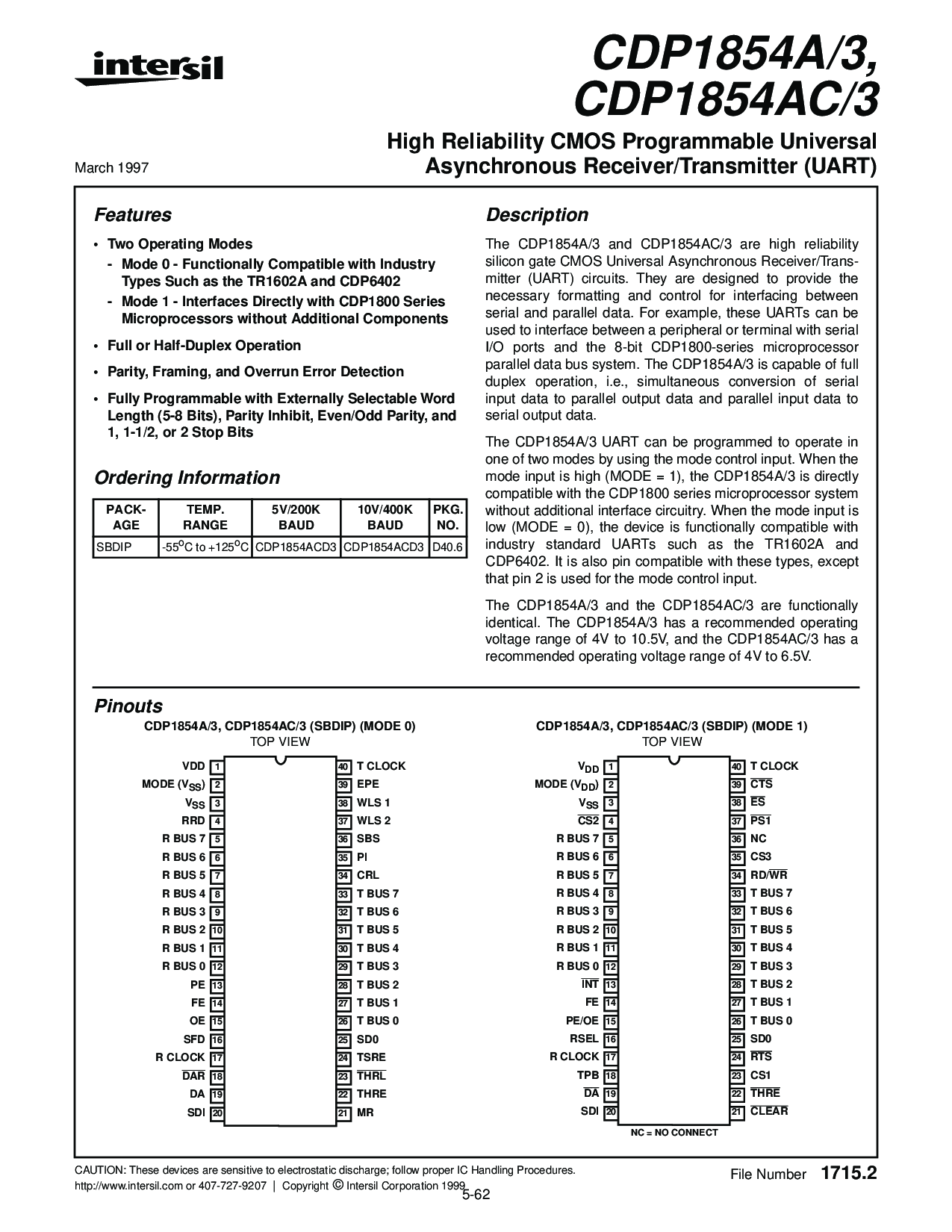

引出线

cdp1854a/3, cdp1854ac/3 (sbdip) (模式 0)

顶部 查看

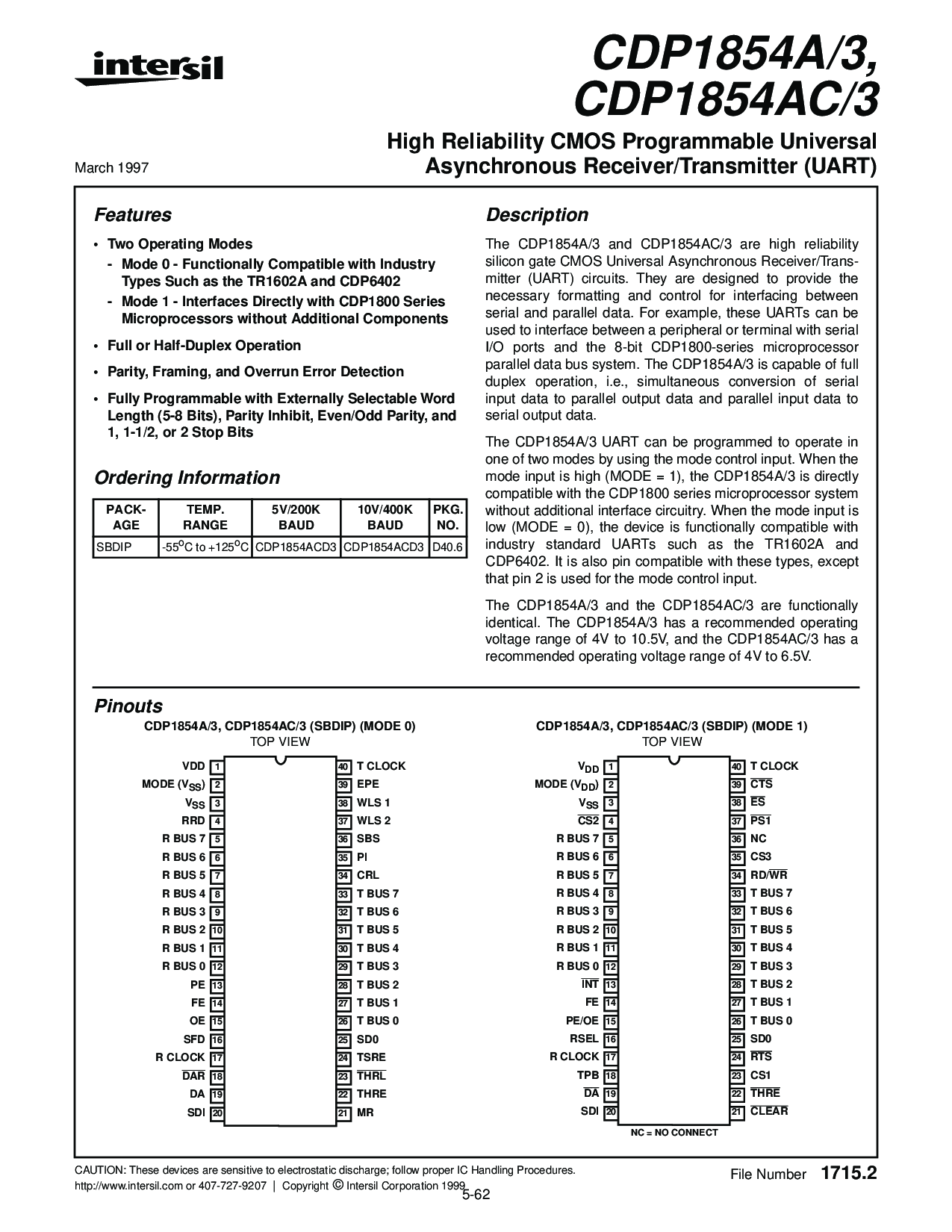

cdp1854a/3, cdp1854ac/3 (sbdip) (模式 1)

顶部 查看

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

VDD

模式 (v

ss

)

v

ss

rrd

右 总线 7

右 总线 6

右 总线 5

右 总线 4

右 总线 3

右 总线 2

右 总线 1

右 总线 0

pe

铁

oe

SFD

右 时钟

dar

da

SDI

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

t 时钟

EPE

wls 1

wls 2

SBS

pi

CRL

t 总线 7

t 总线 6

t 总线 5

t 总线 4

t 总线 3

t 总线 2

t 总线 1

t 总线 0

SD0

TSRE

THRL

三

MR

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

v

dd

模式 (v

dd

)

v

ss

CS2

右 总线 7

右 总线 6

右 总线 5

右 总线 4

右 总线 3

右 总线 2

右 总线 1

右 总线 0

智力

铁

pe/oe

RSEL

右 时钟

TPB

da

SDI

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

t 时钟

cts

es

PS1

nc

CS3

rd/

wr

t 总线 7

t 总线 6

t 总线 5

t 总线 4

t 总线 3

t 总线 2

t 总线 1

t 总线 0

SD0

rts

CS1

三

清除

nc = 否 连接

march 1997

cdp1854a/3,

cdp1854ac/3

高 可靠性 cmos 可编程 通用

异步 接收器/变送器 (uart)

文件 号码

1715.2

注意事项: 这些 设备 是 敏感 至 静电 放电; 跟着 适当的 集成电路 搬运 程序.

http://www.intersil.com 或 407-727-9207

|

版权

©

intersil 公司 1999