4-mb (512k x 8) mobl

静态 ram

CY62148DV30

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-05341 rev. *b 修订 二月 10, 2004

特点

• 很 高 速度: 55 ns

— 宽 电压 范围: 2.20v – 3.60v

• 引脚兼容 与 cy62148cv25, cy62148cv30 和

CY62148CV33

• 超 低 活动 电源

— 典型 活动 电流: 1.5 ma @ f = 1 mhz

— 典型 活动 电流: 8 ma @ f = f

最大值

(55-ns 速度)

• 超 低 备用 电源

• 容易 记忆 扩展 与 ce

,

和 oe特点

• 自动 掉电 当 取消选择

• cmos 用于 最佳 速度/电源

• 软件包 提供: 36-球 bga, 32-管脚 tsopii 和

32-管脚 soic

功能 描述

[1]

这 cy62148dv30 是 一个 高性能 cmos 静态 rams

有组织的 作为 512k 字词 由 8 比特. 这个 设备 特点

高级 电路 设计 至 提供 超-低 活动 电流.

这个 是 理想 用于 提供 更多 蓄电池 life™ (mobl

) 入点

便携式 应用程序 这样的 作为 细胞 电话. 这 设备

也 有 一个 自动 掉电 功能 那 显著

减少 电源 消费. 这 设备 可以 是 put 进入

备用 模式 减少 电源 消费 当 取消选择

(ce

高).

写作 至 这 设备 是 已完成 由 服用 芯片 启用

(ce

) 和 写 启用 (我们) 输入 低. 数据 开启 这 八 我/o

针脚 (我/o

0

通过 我/o

7

) 是 然后 书面 进入 这 位置

指定 开启 这 地址 针脚 (一个

0

通过 一个

18

).

阅读 从 这 设备 是 已完成 由 服用 芯片

启用 (ce

) 和 输出 启用 (oe) 低 同时 强迫 写

启用 (我们

) 高. 下 这些 条件, 这 内容 的

这 记忆 位置 指定 由 这 地址 针脚 将 出现

开启 这 我/o 针脚.

这 八 输入/输出 针脚 (我/o

0

通过 我/o

7

) 是 已放置 入点 一个

高阻抗 州 当 这 设备 是 取消选择 (ce

高), 这 产出 是 已禁用 (oe高), 或 期间 一个 写

操作 (ce低 和 我们低).

备注:

1. 用于 最好 实践 建议, 请 参考 至 这 柏树 应用程序 备注 “system 设计 guidelines” 开启 http://www.cypress.com.

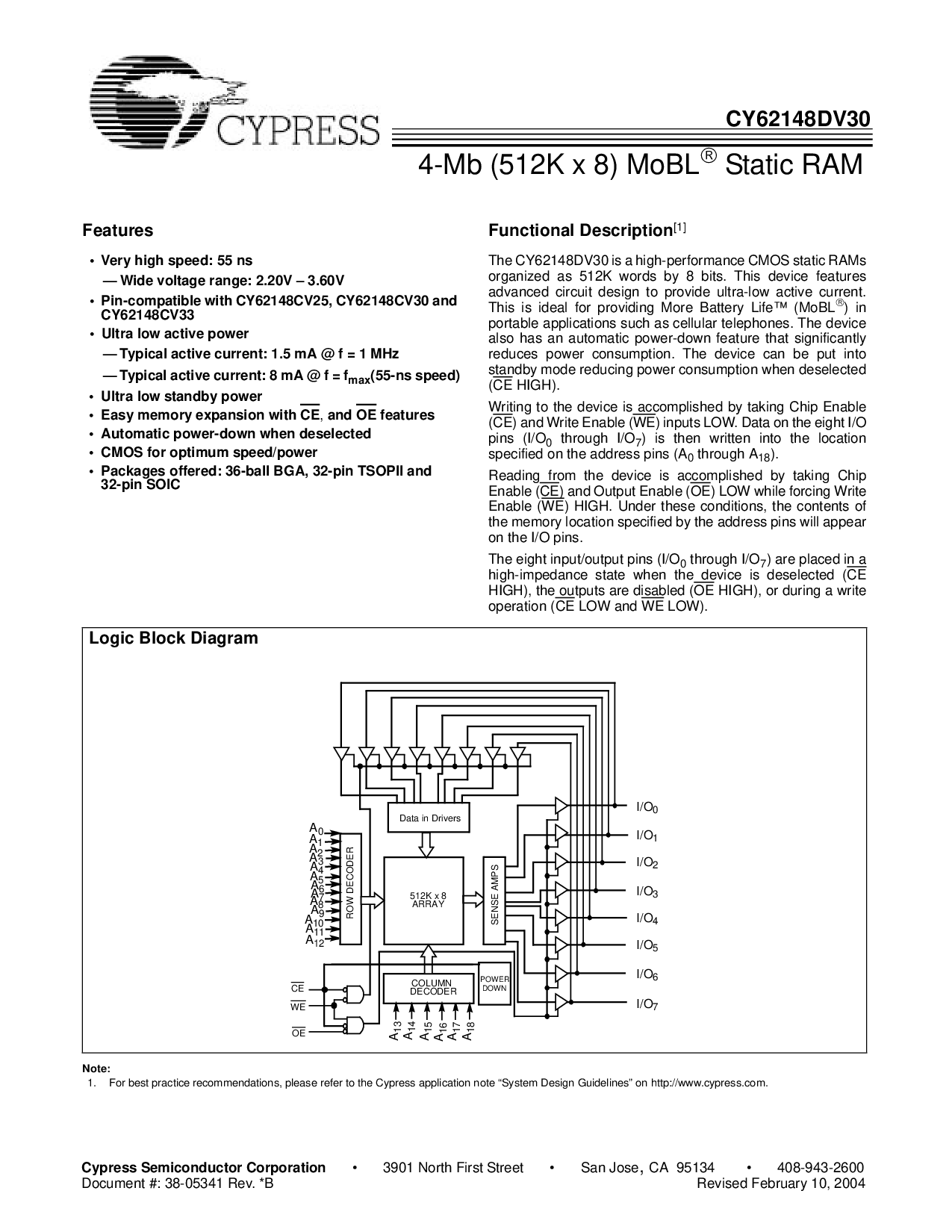

逻辑 块 图表

一个

1

色谱柱

解码器

行 解码器

感觉 安培数

数据 入点 驱动程序

电源

向下

我们

oe

我/o

0

我/o

1

我/o

2

我/o

3

512k x 8

阵列

我/o

7

我/o

6

我/o

5

我/o

4

一个

0

一个

13

ce

一个

14

一个

15

一个

16

一个

17

一个

18

一个

2

一个

3

一个

4

一个

5

一个

6

一个

7

一个

8

一个

9

一个

10

一个

11

一个

12