### 1.0 Features

- Generates clocks required for Intel<sup>®</sup> i820 based desktop and workstation systems, including:

- Four enabled 2.5V 133/100MHz CPU Front Side Bus (FSB) clocks

- ♦ Two 2.5V CPU/2 clocks for synchronous memory

- Seven enabled 3.3V PCI bus clocks and one free-running PCI clock

- ♦ Four enabled 3.3V 66MHz AGP clocks

- Three 2.5V 16.67MHz APIC bus clocks

- ♦ Two 3.3V 14.318MHz REF clocks

- One 3.3V 48MHz USB clock

- CPU clock cycle cycle jitter < 150ps p-p</li>

- Non-linear spread-spectrum modulation (-0.5% at 31.5kHz)

- Supports test mode and tristate output control

- Separate CPU-enable, PCI-enable and power-down inputs with glitch-free stop clock controls on all clocks for clock control and power management

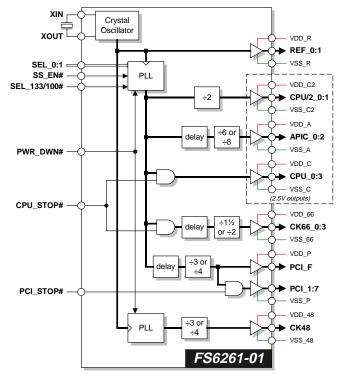

## Figure 1: Block Diagram

## 2.0 Description

The FS6261-01 is a CMOS clock generator IC designed for high-speed motherboard applications. Two different frequencies can be selected for the CPU clocks via two SEL pins. Glitch-free stop clock control of the CPU, AGP (66MHz) and PCI clocks is provided. A low current power-down mode is available for mobile applications. Separate clock buffers provide for a 2.5V voltage range on the CPU 0:3, CPU/2 0:1 and APIC 0:2 clocks.

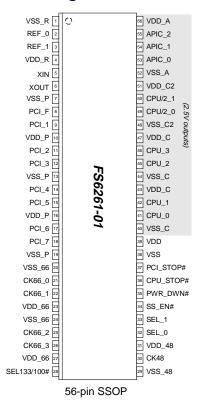

**Figure 2: Pin Configuration**

**Table 1: CPU/PCI Frequency Selection**

| SEL_133/100# | SEL_1 | SEL_0 | CPU (MHz)  | PCI (MHz)  |

|--------------|-------|-------|------------|------------|

| 0            | 0     | 0     | tristate   | tristate   |

| 0            | 0     | 1     | (reserved) | (reserved) |

| 0            | 1     | 0     | 100        | 33.33      |

| 0            | 1     | 1     | 100        | 33.33      |

| 1            | 0     | 0     | XIN/2      | XIN/6      |

| 1            | 0     | 1     | (reserved) | (reserved) |

| 1            | 1     | 0     | 133        | 33.33      |

| 1            | 1     | 1     | 133        | 33.33      |

Intel and Pentium are registered trademarks of Intel Corporation. Spread spectrum modulation is licensed under US Patent No. 5488627, Lexmark International, Inc. American Microsystems, Inc. reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

## **Motherboard Clock Generator IC**

January 2000

### **Table 2: Pin Descriptions**

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI $^{U}$  = Input with Internal Pull-Up; DI $_{D}$  = Input with Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input, DO = Digital Output; P = Power/Ground; # = Active-low pin

| PIN                          | TYPE            | NAME         | DESCRIPTION                                                                                                                                                        |

|------------------------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53, 54, 55                   | DO              | APIC_0:2     | Three low-skew (<250ps @ 1.25V) 2.5V 16.67MHz clock outputs for APIC bus timing. APIC clocks are synchronous with CPU clocks but lag the CPU clocks by 1.5 to 4ns. |

| 30                           | DO              | CK48         | One 3.3V 48MHz clock output for Universal Serial Bus (USB) timing                                                                                                  |

| 21, 22, 25, 26               | DO              | CK66_0:3     | Four 3.3V 66MHz AGP clock outputs. CK66 clocks are synchronous with CPU clocks but lag the CPU clocks by 0 to 1.5ns.                                               |

| 41, 42, 45, 46               | DO              | CPU_0:3      | Four low-skew 2.5V 133/100MHz CPU clock outputs for host frequencies                                                                                               |

| 49, 50                       | DO              | CPU/2_0:1    | Two low-skew 2.5V clock outputs at half the CPU clock frequencies (66/50MHz)                                                                                       |

| 36                           | DI <sup>U</sup> | CPU_STOP#    | CPU_0:3 and CK66_0:3 clock output enable. Asynchronous, active-low disable stops all CPU and CK66 clocks in the low state.                                         |

| 9, 11, 12, 14,<br>15, 17, 18 | DO              | PCI_1:7      | Seven 3.3V PCI clock outputs. PCI clocks are synchronous with CPU clocks but lag the CK66 clocks by 1.5 to 4ns.                                                    |

| 8                            | DO              | PCI_F        | One free-running 3.3V PCI clock output                                                                                                                             |

| 37                           | DI <sup>U</sup> | PCI_STOP#    | PCI_1:7 clock output enable. Asynchronous, active-low disable stops all PCI clocks in the low state.                                                               |

| 35                           | DI <sup>U</sup> | PWR_DWN#     | Asynchronous active-low power-down signal shuts down oscillator, all PLLs, puts all clocks in low state. Clock re-enable latency of $\leq$ 3ms.                    |

| 2, 3                         | DO              | REF_0:1      | Two buffered outputs of the 14.318MHz reference clock                                                                                                              |

| 32, 33                       | DI <sup>U</sup> | SEL_0:1      | Two frequency select inputs (see Table 4)                                                                                                                          |

| 28                           | DI              | SEL_133/100# | Selects 133MHz or 100MHz CPU frequency (pull-up/pull-down <u>must</u> be provided externally)                                                                      |

| 34                           | DI <sup>U</sup> | SS_EN#       | Spread spectrum enable. Active-low enable turns on the spread spectrum feature; a logic-high turns off the spread spectrum modulation.                             |

| 39                           | Р               | VDD          | 3.3V ± 10%                                                                                                                                                         |

| 31                           | Р               | VDD_48       | Power supply for 3.3V CK48 clock output                                                                                                                            |

| 23, 27                       | Р               | VDD_66       | Power supply for 3.3V CK66_0:3 clock outputs                                                                                                                       |

| 56                           | Р               | VDD_A        | Power supply for 2.5V APIC_0:2 clock outputs                                                                                                                       |

| 43, 47                       | Р               | VDD_C        | Power supply for 2.5V CPU_0:3 clock outputs                                                                                                                        |

| 51                           | Р               | VDD_C2       | Power supply for 2.5V CPU/2_0:1 clock outputs                                                                                                                      |

| 10, 16                       | Р               | VDD_P        | Power supply for 3.3V PCI_1:7 and PCI_F clock outputs                                                                                                              |

| 4                            | Р               | VDD_R        | Power supply for 3.3V REF_0:1 clock outputs                                                                                                                        |

| 38                           | Р               | VSS          | Ground                                                                                                                                                             |

| 29                           | Р               | VSS_48       | Ground for CK48 clock outputs                                                                                                                                      |

| 20, 24                       | Р               | VSS_66       | Ground for CK66_0:3 clock outputs                                                                                                                                  |

| 52                           | Р               | VSS_A        | Ground for APIC_0:2 clock outputs                                                                                                                                  |

| 40, 44                       | Р               | VSS_C        | Ground for CPU_0:3 clock outputs                                                                                                                                   |

| 48                           | Р               | VSS_C2       | Ground for CPU/2_0:1 clock outputs                                                                                                                                 |

| 7, 13, 19                    | Р               | VSS_P        | Ground for PCI_1:7 and PCI_F clock outputs                                                                                                                         |

| 1                            | Р               | VSS_R        | Ground for REF_0:1 clock outputs                                                                                                                                   |

| 5                            | AI              | XIN          | 14.318MHz crystal oscillator input. XIN can be driven by an external frequency source.                                                                             |

| 6                            | AO              | XOUT         | 14.318MHz crystal oscillator output                                                                                                                                |

|                              | 1               |              | <u>,                                      </u>                                                                                                                     |

**Table 3: Actual Clock Frequencies**

Note: Spread spectrum disabled

| CLOCK               | TARGET (MHz)             | ACTUAL (MHz) | DEVIATION (ppm) |  |  |

|---------------------|--------------------------|--------------|-----------------|--|--|

| ADIC 0.0            | 16.67 (with CPU = 133.3) | 16.6634      | -195.92         |  |  |

| APIC_0:2            | 16.67 (with CPU = 100.0) | 16.6661      | -36.657         |  |  |

| CDU 0.2             | 133.33                   | 133.3072     | -195.92         |  |  |

| CPU_0:3             | 100.00                   | 99.9963      | -36.657         |  |  |

| ODII/O 0.4          | 66.67                    | 66.6536      | -195.92         |  |  |

| CPU/2_0:1           | 50.00                    | 49.9982      | -36.657         |  |  |

| DOI 4-7 DOI E       | 33.33 (with CPU = 133.3) | 33.3268      | -195.92         |  |  |

| PCI_1:7, PCI_F      | 33.33 (with CPU = 100.0) | 33.3321      | -36.657         |  |  |

| CKCC 0.2            | 66.67 (with CPU = 133.3) | 66.6536      | -195.92         |  |  |

| CK66_0:3            | 66.67 (with CPU = 100.0) | 66.6642      | -36.657         |  |  |

| CK48 <sup>(1)</sup> | 48                       | 48.0080      | +167            |  |  |

<sup>(1) 48</sup>MHz USB clock is required to be 167ppm off from 48.000MHz to conform to USB requirements.

## 3.0 Programming Information

**Table 4: Function/Clock Enable Configuration**

|                  |            | CONTRO           | L INPUTS     |               |               |            |            | C             | LOCK OUT   | PUTS (MI   | łz)          |            |              |

|------------------|------------|------------------|--------------|---------------|---------------|------------|------------|---------------|------------|------------|--------------|------------|--------------|

| SEL_<br>133/100# | SEL_1      | SEL_0            | PWR_<br>DWN# | CPU_<br>STOP# | PCI_<br>STOP# | REF_0:1    | CPU_0:3    | CPU/2_<br>0:1 | PCI_F      | PCI_1:7    | APIC_<br>0:2 | CK48       | CK66_<br>0:3 |

| 0                | 0          | 0                | 1            | Χ             | Х             | tristate   | tristate   | tristate      | tristate   | tristate   | tristate     | tristate   | tristate     |

| 0                | 0          | 1                | 1            | 1             | 1             | (reserved) | (reserved) | (reserved)    | (reserved) | (reserved) | (reserved)   | (reserved) | (reserved)   |

| 0                | 1          | 0                | 1            | 1             | 1             | 14.318     | 100        | 50            | 33.33      | 33.33      | 16.67        | tristate   | 66.67        |

| 0                | 1          | 1                | 1            | 1             | 1             | 14.318     | 100        | 50            | 33.33      | 33.33      | 16.67        | 48         | 66.67        |

| 1                | 0          | 0                | 1            | 1             | 1             | XIN        | XIN÷2      | XIN÷4         | XIN÷8      | XIN÷8      | XIN÷16       | XIN÷2      | XIN÷4        |

| 1                | 0          | 1                | 1            | 1             | 1             | (reserved) | (reserved) | (reserved)    | (reserved) | (reserved) | (reserved)   | (reserved) | (reserved)   |

| 1                | 1          | 0                | 1            | 1             | 1             | 14.318     | 133.33     | 66.67         | 33.33      | 33.33      | 16.67        | tristate   | 66.67        |

| 1                | 1          | 1                | 1            | 1             | 1             | 14.318     | 133.33     | 66.67         | 33.33      | 33.33      | 16.67        | 48         | 66.67        |

| Х                | Х          | Х                | 0            | Х             | Х             | low        | low        | low           | low        | low        | low          | low        | low          |

| S                | EL_0:1 an  | d                | 1            | 0             | 0             | 14.318     | low        | running       | 33.33      | low        | 16.67        | 48         | low          |

| SEL              | _133/100#  | <sup>‡</sup> ≠ 0 | 1            | 0             | 1             | 14.318     | low        | running       | 33.33      | 33.33      | 16.67        | 48         | low          |

|                  | or         |                  | 1            | 1             | 0             | 14.318     | running    | running       | 33.33      | low        | 16.67        | 48         | 66.67        |

| S                | EL_0:1 ≠ 0 | 01               | 1            | 1             | 1             | 14.318     | running    | running       | 33.33      | 33.33      | 16.67        | 48         | 66.67        |

### **Motherboard Clock Generator IC**

January 2000

### 3.1 SEL\_1, SEL\_0

These two input pins can either tristate the output drivers, select the Test Mode frequency, or choose the CPU frequencies. Both the SEL\_1 and SEL\_0 pins have pull-ups that default the CPU output frequency to either 100MHz or 133MHz, depending on the state of the SEL\_133/100# pin. These pins should be fixed at a logic state before power-up occurs.

### 3.2 SEL 133/100#

This pin is an active-low LVTTL input that switches between a 133MHz or a 100MHz system (CPU) clock. A pull-up or pull-down must be provided externally and this pin should be fixed at a logic state before power-up occurs.

### 4.0 Clock Latency

All clock outputs are stopped in the low state, and are started so that the first high pulse is a full pulse width. All clocks complete a full period on transitions between running (enabled) and stopped (disabled) to ensure glitch-free stop clock control.

All enabled clocks will continue to run while disabled clocks are stopped. The clock enable signals are assumed to be asynchronous inputs relative to clock outputs. Enable signals are synchronized to their respective clocks by this device. The CPU and PCI clocks will transition between running and stopped according to Table 5.

### 4.1 Power-Up Latency

Power-up latency is defined as the time from the moment when PWR\_DWN# goes inactive (a rising edge) to when the first valid clocks are driven from the device. Upon release of PWR\_DWN#, external circuitry should allow a minimum of 3ms for the PLLs to lock before enabling any clocks.

#### 4.1.1 PWR DWN#

The PWR\_DWN# signal is an asynchronous, active-low LVTTL input that puts the device in a low power inactive state without removing power from the device. All internal clocks are turned off, and all clock outputs are held low.

Powering down occurs in less than two PCI clocks from the falling edge of PWR\_DWN# to when all clock outputs are forced low. The REF and CK48 clocks are brought low as soon as possible.

### 4.2 Clock Enable Latency

Clock enable latency is defined in the number of rising edges of free-running PCI clocks between when the enable signal becomes active (a rising edge) to when the first valid clock is driven from the device.

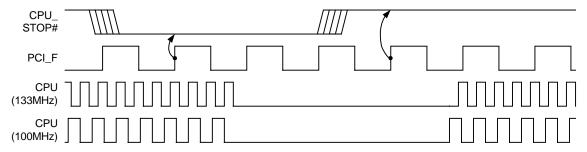

#### 4.2.1 CPU STOP#

The CPU\_STOP# pin is an active-low LVTTL input pin that disables the CPU\_0:3 and CK66\_0:3 clocks for low power operation. CPU\_STOP# can be asserted asynchronously, and the stop clock control is glitch-free, in that the CPU clock must complete a full cycle before the clock is stopped low. One rising edge of the PCI\_F clock is allowed before the CPU and CK66 clocks are enabled or disabled.

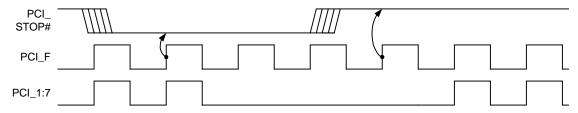

### 4.2.2 PCI STOP#

The PCI\_STOP# pin is an active-low LVTTL input pin that disables the PCI\_1:7 clocks for low power operation, except for the PCI\_F clock. The PCI\_F is a free-running clock, and will continue to run even if all other PCI clocks have stopped. PCI\_STOP# can be asserted asynchronously, and the stop-clock control is glitch-free, in that the PCI clock must complete a full cycle before the clock is stopped low. Only one rising edge of the PCI\_F clock is allowed after the PCI\_STOP# signal is enabled/disabled.

**Table 5: Latency Table**

| SIGNAL          | SI      | GNAL STATE | PCI CLOCK ENABLE<br>LATENCY |

|-----------------|---------|------------|-----------------------------|

| CPU STOP#       | 0       | disabled   | 1                           |

| CFU_310F#       | 1       | enabled    | 1                           |

| PCI STOP#       | 0       | disabled   | 1                           |

| PCI_310F#       | 1       | enabled    | 1                           |

| PWR DWN#        | DWD DWM |            | 2 (max.)                    |

| F VV IX_DVV IN# | 1       | Power ON   | 3ms                         |

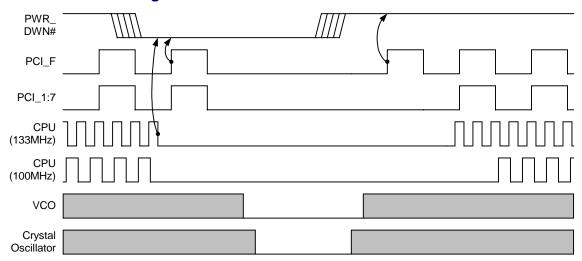

## Figure 2: CPU\_STOP# Timing

Figure 3: PCI\_STOP# Timing

Figure 4: PWR\_DWN# Timing

Shaded regions in the Crystal Oscillator and VCO waveforms indicate that the clock is valid and the Crystal Oscillator and VCO are active.

### **Motherboard Clock Generator IC**

January 2000

## 5.0 Spread Spectrum Modulation

To limit peak EMI emissions, high-speed motherboard designs now require the reduction of the peak harmonic energy contained in the system bus frequencies. A reduction in the peak energy of a specific frequency can be accomplished by spreading the energy over a limited range of frequencies through a technique known as spread spectrum clocking. In this technique, a generated clock frequency is dithered in a tightly controlled sweep near the clock frequency using a predetermined modulation profile and period.

**Figure 5: Spectral Energy Distribution**

The amount of EMI reduction is directly related to three parameters: the modulation percentage, the frequency of the modulation, and the modulation profile.

### 5.1 Modulation Percentage

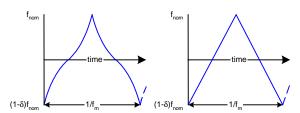

The modulation percentage  $\delta$ , is typically 0.5% of the center frequency (denoted here as  $f_{nom}$ ). The modulation percentage determines the range of frequencies the spectral energy is distributed over. For a 100MHz clock frequency, a ±0.5% modulation sweeps the clock frequency between 99.5MHz and 100.5MHz. If the sweep is symmetrical around the center frequency, the technique is known as center-spread modulation. However, a circuit that is designed for a 100MHz reference may not have enough timing margin to support a clock greater then 100MHz. The clock frequency can instead be modulated between  $f_{nom}$ , and  $(1-\delta)$   $f_{nom}$ ; the technique is known as down-spread modulation. For a  $\delta$  of -0.5%, the clock will sweep between 99.5MHz and 100MHz. A small degradation in circuit performance may be noticed, as the clock frequency now averages 99.75MHz.

### 5.2 Modulation Frequency

The frequency of modulation, noted as  $f_m$ , describes how fast the center frequency sweeps between  $f_{nom}$ , and (1- $\delta$ )  $f_{nom}$ . Typical modulation frequencies must be greater than 30kHz (above the audio band) but small enough to not upset system timing. Since a tracking PLL cannot instantaneously update the output clock to match a modulated input clock, any accumulation of the difference in phase between the modulated input clock and a tracking PLL output clock is called tracking skew. The resulting phase error will decrease the timing margins in any successive circuitry.

### 5.3 Modulation Profile

The modulation profile determines the shape of the spectral energy distribution by defining the time that the clock spends at a specific frequency. The longer a clock remains at a specific frequency, the larger the energy concentration at that frequency. A sinusoidal modulation spends a large portion of time between  $f_{nom}$ , and  $(1-\delta)$   $f_{nom}$ , resulting in large energy peaks at the edges of the spectral energy distribution. A linear modulation, such as a triangle profile, improves the spectral distribution but also exhibits energy peaking at the edges. A non-linear modulation profile, known as the "Hershey Kiss" profile offers the best distribution of spectral energy.

**Figure 6: Modulation Profiles**

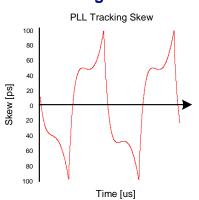

The type of modulation profile used will also impact tracking skew. The maximum frequency change occurs at the profile limits where the modulation changes the slew rate polarity. To track the sudden reversal in clock frequency, the downstream PLL must have a large loop bandwidth.

Compared to the profile limits the modulation slew rate is relatively slow between the limits, allowing the downstream PLL a chance to reduce the tracking skew. The ability of the downstream PLL to catch up is determined by the loop transfer function phase angle.

Spread spectrum clocking can be shown to have a negligible effect on cycle-to-cycle jitter performance. Any increase in jitter is less than 1ps when  $\delta$ <1% and  $f_m$ <50kHz. Careful design of downstream PLLs can ensure that tracking skew is minimized. To have less than 100ps of tracking skew, a downstream PLL should have a loop bandwidth greater than 1MHz, and a phase angle less than 0.1°.

Figure 7 shows the tracking skew of a downstream PLL with a loop bandwidth of 1.5MHz and a phase angle of  $0.26^{\circ}$  following a non-linear profile-modulated 100MHz input clock with a  $\delta$ =-0.5% and an  $f_m$ =31.2kHz.

Figure 7: PLL Tracking Skew

### 5.4 Spread Spectrum Enable

The active-low LVTTL SS\_EN# input pin enables spread spectrum modulation of the CPU and PCI clocks. When SS\_EN# is a logic-high, the spread spectrum modulation of these clocks is disabled. If SS\_EN# is a logic-low, spread spectrum modulation is enabled.

A pull-up on this pin disables spread spectrum modulation by default.

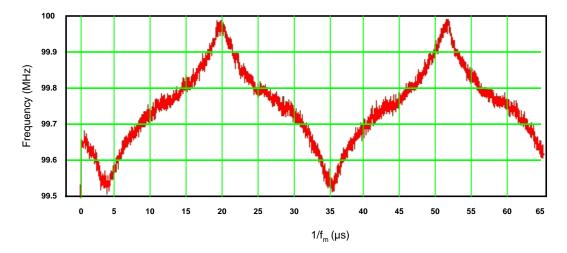

**Figure 8: Actual Modulation Profile**

### **Motherboard Clock Generator IC**

January 2000

## 6.0 Electrical Specifications

## **Table 6: Absolute Maximum Ratings**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality, and reliability.

| PARAMETER                                                                          | SYMBOL          | MIN.                 | MAX.                 | UNITS |

|------------------------------------------------------------------------------------|-----------------|----------------------|----------------------|-------|

| Supply Voltage (V <sub>SS</sub> = ground)                                          | $V_{DD}$        | V <sub>SS</sub> -0.5 | 7                    | V     |

| Input Voltage, dc                                                                  | Vı              | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                                                                 | Vo              | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Input Clamp Current, dc (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> )  | I <sub>IK</sub> | -50                  | 50                   | mA    |

| Output Clamp Current, dc (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> ) | I <sub>OK</sub> | -50                  | 50                   | mA    |

| Storage Temperature Range (non-condensing)                                         | Ts              | -65                  | 150                  | °C    |

| Ambient Temperature Range, Under Bias                                              | T <sub>A</sub>  | -55                  | 125                  | °C    |

| Junction Temperature                                                               | TJ              |                      | 125                  | °C    |

| Lead Temperature (soldering, 10s)                                                  |                 |                      | 260                  | °C    |

| Input Static Discharge Voltage Protection (MIL-STD 883E, method 3015.7)            |                 |                      | 2                    | kV    |

### **CAUTION: ELECTROSTATIC SENSITIVE DEVICE**

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy electrostatic discharge.

## **Table 7: Operating Conditions**

| PARAMETER                          | SYMBOL            | CONDITIONS/DESCRIPTION                                   | MIN.   | TYP.   | MAX.  | UNITS |  |

|------------------------------------|-------------------|----------------------------------------------------------|--------|--------|-------|-------|--|

|                                    |                   | Core (VDD) @ 3.3V ± 5%                                   | 3.135  | 3.3    | 3.465 |       |  |

| Supply Voltage                     | $V_{DD}$          | Clock Buffers (VDD_P, VDD_R, VDD_66, VDD_48) @ 3.3V ± 5% | 3.135  | 3.3    | 3.465 | V     |  |

|                                    |                   | Clock Buffers (VDD_A, VDD_C, VDD_C2) @ 2.5V ± 5%         | 2.375  | 2.5    | 2.625 |       |  |

| Operating Temperature Range        | T <sub>A</sub>    |                                                          | 0      |        | 70    | °C    |  |

| Crystal Resonator Frequency        | f <sub>XTAL</sub> |                                                          | 14.316 | 14.318 | 14.32 | MHz   |  |

| Crystal Resonator Load Capacitance | C <sub>XL</sub>   | XIN, XOUT pins                                           | 13.5   | 18     | 22.5  | pF    |  |

|                                    |                   | APIC_0:2                                                 | 10     |        | 20    |       |  |

|                                    |                   | CPU_0:3                                                  | 10     |        | 20    |       |  |

|                                    |                   | CPU/2_0:3                                                | 10     |        | 20    |       |  |

| Load Capacitance                   | CL                | PCI_F, PCI_1:7                                           | 10     |        | 30    | рF    |  |

|                                    |                   | CK48                                                     | 10     |        | 20    |       |  |

|                                    |                   | CK66_0:3                                                 | 10     |        | 30    |       |  |

|                                    |                   | REF_0:1                                                  | 10     |        | 20    |       |  |

### **Motherboard Clock Generator IC**

January 2000

### **Table 8: DC Electrical Specifications**

Unless otherwise stated, all power supplies =  $3.3V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Negative currents indicate current flows out of the device.

| PARAMETER                               | SYMBOL               | CONDITIONS/DESCRIPTION                                                     | MIN.                 | TYP. | MAX.                 | UNITS |

|-----------------------------------------|----------------------|----------------------------------------------------------------------------|----------------------|------|----------------------|-------|

| Overall                                 |                      |                                                                            |                      |      |                      |       |

|                                         |                      | f <sub>CPU</sub> = 133MHz; SEL_0:1 = 11<br>VDD_A = VDD_C = VDD_C2 = 3.465V |                      | 120  |                      |       |

| Supply Current, Dynamic, with Loaded    | I <sub>DD</sub>      | f <sub>CPU</sub> = 133MHz; SEL_0:1 = 11<br>VDD_A = VDD_C = VDD_C2 = 2.625V |                      | 88   |                      | mA    |

| Outputs                                 | IDD                  | f <sub>CPU</sub> = 100MHz; SEL_0:1 = 11<br>VDD_A = VDD_C = VDD_C2 = 3.465V |                      | 120  |                      | IIIA  |

|                                         |                      | f <sub>CPU</sub> = 100MHz; SEL_0:1 = 11<br>VDD_A = VDD_C = VDD_C2 = 2.625V |                      | 86   |                      |       |

| Cumply Current Statio                   |                      | PWR_DWN# low<br>VDD_A = VDD_C = VDD_C2 = 3.465V                            |                      | 12   |                      | ^     |

| Supply Current, Static                  | I <sub>DDs</sub>     | PWR_DWN# low<br>VDD_A = VDD_C = VDD_C2 = 2.625V                            |                      | 8    |                      | μΑ    |

| Digital Inputs (CPU_STOP#, PCI_STOP#, F | WR_DWN#, S           | EL_0:1, SS_EN#)                                                            |                      |      |                      |       |

| High-Level Input Voltage                | V <sub>IH</sub>      |                                                                            | 2.0                  |      | V <sub>DD</sub> +0.3 | V     |

| Low-Level Input Voltage                 | V <sub>IL</sub>      |                                                                            | V <sub>SS</sub> -0.3 |      | 0.8                  | V     |

| High-Level Input Current                | I <sub>IH</sub>      |                                                                            |                      |      | 5                    | μΑ    |

| Low-Level Input Current (pull-up)       | I <sub>IL</sub>      | V <sub>IL</sub> = 0.4V                                                     | -2                   | -0.8 |                      | μΑ    |

| Digital Inputs (SEL_133/100#)           |                      |                                                                            |                      |      |                      |       |

| High-Level Input Voltage                | V <sub>IH</sub>      |                                                                            | 2.0                  |      | V <sub>DD</sub> +0.3 | V     |

| Low-Level Input Voltage                 | V <sub>IL</sub>      |                                                                            | V <sub>SS</sub> -0.3 |      | 8.0                  | V     |

| Input Leakage Current                   | I <sub>I</sub>       |                                                                            | -5                   |      | +5                   | μΑ    |

| Crystal Oscillator Feedback (XIN)       |                      |                                                                            |                      |      |                      |       |

| Threshold Bias Voltage                  | $V_{TH}$             |                                                                            |                      | 1.5  |                      | V     |

| High-Level Input Current                | I <sub>IH</sub>      | V <sub>IH</sub> = 3.3V                                                     |                      | 32   |                      | μΑ    |

| Low-Level Input Current                 | I <sub>IL</sub>      | V <sub>IL</sub> = 0V                                                       |                      | -32  |                      | μΑ    |

| Crystal Loading Capacitance *           | C <sub>L(xtal)</sub> | As seen by an external crystal connected to XIN and XOUT                   | 13.5                 | 18   | 22.5                 | pF    |

| Input Loading Capacitance *             | C <sub>L(XIN)</sub>  | As seen by an external clock driver on XOUT; XIN unconnected               |                      | 36   |                      | pF    |

| Crystal Oscillator Drive (XOUT)         |                      |                                                                            |                      |      |                      |       |

| High Level Output Source Current        | I <sub>OH</sub>      | $V_1 = 3.3V, V_0 = 0V$                                                     |                      | -8.0 |                      | mA    |

| Low Level Output Sink Current           | I <sub>OL</sub>      | $V_1 = 0V, V_0 = 3.3V$                                                     |                      | 8.7  |                      | mA    |

## **Motherboard Clock Generator IC**

January 2000

### **Table 8: DC Electrical Specifications, continued**

Unless otherwise stated, all power supplies =  $3.3V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Negative currents indicate current flows out of the device.

| PARAMETER                              | SYMBOL              | CONDITIONS/DESCRIPTION                                    | MIN. | TYP. | MAX. | UNITS |  |

|----------------------------------------|---------------------|-----------------------------------------------------------|------|------|------|-------|--|

| CPU_0:3, CPU/2_0:1, APIC_0:2 Clock Ou  | tputs (2.5V Type    | e 1 Clock Buffer)                                         |      | "    |      | -     |  |

|                                        | I <sub>OH min</sub> | VDD_C, VDD_C2, VDD_A = 2.375V, V <sub>O</sub> = 1.0V      | -27  |      |      |       |  |

| High Level Output Source Current       | I <sub>OH max</sub> | VDD_C, VDD_C2, VDD_A = 2.625V,<br>V <sub>0</sub> = 2.375V |      |      | -27  | mA    |  |

| Louis and Output Sink Current          | I <sub>OL min</sub> | VDD_C, VDD_C2, VDD_A = 2.375V,<br>V <sub>O</sub> = 1.2V   | 27   |      |      |       |  |

| Low Level Output Sink Current          | I <sub>OL max</sub> | VDD_C, VDD_C2, VDD_A = 2.625V,<br>V <sub>O</sub> = 0.3V   |      |      | 30   | - mA  |  |

| Output Impedance                       | Z <sub>OL</sub>     | Measured at 1.25V, output driving low                     | 13.5 | 23   | 45   | Ω     |  |

| Output Impedance                       | Z <sub>OH</sub>     | Measured at 1.25V, output driving high                    | 13.5 | 25   | 45   | 52    |  |

| Tristate Output Current                | l <sub>oz</sub>     |                                                           | -10  |      | 10   | μΑ    |  |

| Short Circuit Output Source Current    | I <sub>SCH</sub>    | V <sub>O</sub> = 0V; shorted for 30s, max.                |      | -56  |      | mA    |  |

| Short Circuit Output Sink Current      | I <sub>SCL</sub>    | V <sub>O</sub> = 2.5V; shorted for 30s, max.              |      | 58   |      | mA    |  |

| REF_0:1, CK48 Clock Outputs (3.3V Type | 3 Clock Buffer      | )                                                         |      |      |      |       |  |

| High-Level Output Source Current       | I <sub>OH min</sub> | VDD_R, VDD_48 = 3.135V, V <sub>O</sub> = 1.0V             | -29  |      |      |       |  |

|                                        | I <sub>OH max</sub> | VDD_R, VDD_48 = 3.465V, V <sub>0</sub> = 3.135V           |      |      | -23  | mA    |  |

| Low-Level Output Sink Current          | I <sub>OL min</sub> | VDD_R, VDD_48 = 3.135V, V <sub>O</sub> = 1.95V            | 29   |      |      | mA    |  |

|                                        | I <sub>OL max</sub> | VDD_R, VDD_48 = 3.465V, V <sub>O</sub> = 0.4V             |      |      | 27   | mA    |  |

| Output Impedence                       | Z <sub>OL</sub>     | Measured at 1.65V, output driving low                     | 20   | 45   | 60   | Ω     |  |

| Output Impedance                       | Z <sub>OH</sub>     | Measured at 1.65V, output driving high                    | 20   | 46   | 60   | 52    |  |

| Tristate Output Current                | l <sub>oz</sub>     |                                                           | -10  |      | 10   | μΑ    |  |

| Short Circuit Output Source Current    | I <sub>OSH</sub>    | V <sub>O</sub> = 0V; shorted for 30s, max.                |      | -41  |      | mA    |  |

| Short Circuit Output Sink Current      | I <sub>OSL</sub>    | V <sub>O</sub> = 3.3V; shorted for 30s, max.              |      | 40   |      | mA    |  |

| PCI_1:7, PCI_F, CK66_0:1 Clock Outputs | (3.3V Type 5 CI     | ock Buffer)                                               |      |      |      |       |  |

| High Lord Order Order                  | I <sub>OH min</sub> | VDD_P, VDD_66 = 3.135V, V <sub>O</sub> = 1.0V             | -33  |      |      | ^     |  |

| High Level Output Source Current       | I <sub>OH max</sub> | VDD_P, VDD_66 = 3.465V, V <sub>O</sub> = 3.135V           |      |      | -33  | mA    |  |

| Lave Lavel Ovine in Sink Command       | I <sub>OL min</sub> | VDD_P, VDD_66 = 3.135V, V <sub>O</sub> = 1.95V            | 30   |      |      | A     |  |

| Low Level Output Sink Current          | I <sub>OL max</sub> | VDD_P, VDD_66 = 3.465V, V <sub>O</sub> = 0.4V             |      |      | 38   | mA    |  |

| Output Impedance                       | Z <sub>OL</sub>     | Measured at 1.65V, output driving low                     | 12   | 29   | 55   | Ω     |  |

| Output Impedance                       | Z <sub>OH</sub>     | Measured at 1.65V, output driving high                    | 12   | 37   | 55   | 5.2   |  |

| Tristate Output Current                | I <sub>OZ</sub>     |                                                           | -10  |      | 10   | μΑ    |  |

| Short Circuit Output Source Current    | I <sub>OSH</sub>    | V <sub>O</sub> = 0V; shorted for 30s, max.                |      | -51  |      | mA    |  |

| Short Circuit Output Sink Current      | I <sub>OSL</sub>    | V <sub>O</sub> = 3.3V; shorted for 30s, max.              |      | 62   |      | mA    |  |

### **Motherboard Clock Generator IC**

January 2000

## **Table 9: AC Timing Specifications**

Unless otherwise stated, all power supplies =  $3.3V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Negative currents indicate current flows out of the device. Spread spectrum modulation is disabled except for Rise/Fall time measurements.

| PARAMETER                                 | SYMBOL             | CONDITIONS/DESCRIPTION                                                                                 |      | 133MHz | Z    | 100MHz |      |      | UNITS |

|-------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|------|--------|------|--------|------|------|-------|

| PARAMETER                                 | STWIBUL            | CONDITIONS/DESCRIPTION                                                                                 | MIN. | TYP.   | MAX. | MIN.   | TYP. | MAX. | UNIT  |

| Overall                                   |                    |                                                                                                        |      |        |      |        |      |      |       |

| Spread Spectrum Modulation<br>Frequency * | f <sub>m</sub>     | SS_EN# low                                                                                             |      |        | 31.5 |        |      | 31.5 | kHz   |

| Spread Spectrum Modulation Index*         | $\delta_{m}$       | SS_EN# low                                                                                             |      |        | -0.5 |        |      | -0.5 | %     |

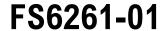

|                                           |                    | CPU @ 1.25V, C <sub>L</sub> =20pF to CK66 @ 1.5V, C <sub>L</sub> =30pF (rising edges)                  | 0    | 0.3    | 1.5  | 0      | 0.4  | 1.5  |       |

| Clock Offset                              | t <sub>pd</sub>    | CK66 @ 1.5V, C <sub>L</sub> =30pF to PCI @ 1.5V, C <sub>L</sub> =30pF (rising edges)                   | 1.5  | 2.9    | 4.0  | 1.5    | 3.1  | 4.0  | ns    |

|                                           |                    | CPU @ 1.25V, C <sub>L</sub> =20pF to APIC @ 1.25V, C <sub>L</sub> =20pF (rising edges)                 | 1.5  | 2.3    | 4.0  | 1.5    | 3.3  | 4.0  |       |

| Tristate Enable Delay *                   | $t_{DZL,}t_{DZH}$  | SEL_0:1 and SEL_133/100#=0                                                                             | 1.0  |        | 10   | 1.0    |      | 10   | ns    |

| Tristate Disable Delay *                  | $t_{DZL,}t_{DZH}$  | SEL_0:1 and SEL_133/100#=0                                                                             | 1.0  |        | 10   | 1.0    |      | 10   | ns    |

| Clock Stabilization (on power-up) *       | t <sub>STB</sub>   | via PWR_DWN#                                                                                           |      |        | 3.0  |        |      | 3.0  | ms    |

| APIC_0:2 Clock Output (2.5V Type 1        | Clock Buffer       | )                                                                                                      |      |        |      |        |      |      | •     |

| Duty Cycle *                              | dt                 | Ratio of high pulse width to one clock period, measured at 1.5V                                        | 45   | 50     | 55   | 45     | 50   | 55   | %     |

| Clock Skew *                              | t <sub>skw</sub>   | APIC to APIC @ 1.25V, C <sub>L</sub> =20pF                                                             |      | -70    |      |        | -70  |      |       |

| Jitter, Long Term $(\sigma_y(\tau))$ *    | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.25V relative to an ideal clock, C <sub>L</sub> =20pF, all PLLs active |      | 204    |      |        | 122  |      | ps    |

| Jitter, Period (peak-peak) *              | $t_{j(\Delta P)}$  | From rising edge to rising edge at 1.25V, C <sub>L</sub> =20pF, all PLLs active                        |      | 82     |      |        | 88   |      | ps    |

| Rise Time *                               | t <sub>r min</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =10pF                                                           |      | 1.2    |      |        | 1.2  |      | ns    |

| Rise Tillle                               | t <sub>r max</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =20pF                                                           |      | 1.5    |      |        | 1.5  |      | 115   |

| Fall Time *                               | t <sub>f min</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =10pF                                                           |      | 1.8    |      |        | 1.5  |      | 20    |

| Faii Time                                 | t <sub>f max</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =20pF                                                           |      | 2.1    |      |        | 1.8  |      | ns    |

| CPU/2_0:1 Clock Outputs (2.5V Type        | •                  | fer)                                                                                                   |      |        |      |        |      |      |       |

| Duty Cycle *                              | d <sub>t</sub>     | Ratio of high pulse width to one clock period, measured at 1.5V                                        | 45   | 52     | 55   | 45     | 52   | 55   | %     |

| Clock Skew *                              | t <sub>skw</sub>   | CPU/2 to CPU/2 @ 1.25V, C <sub>L</sub> =20pF                                                           |      | +10    |      |        | +10  |      |       |

| Jitter, Long Term $(\sigma_y(\tau))$ *    | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.25V relative to an ideal clock, C <sub>L</sub> =20pF, all PLLs active |      | 136    |      |        | 122  |      | ps    |

| Jitter, Period (peak-peak) *              | $t_{j(\Delta P)}$  | From rising edge to rising edge at 1.25V, C <sub>L</sub> =20pF, all PLLs active                        |      | 108    |      |        | 112  |      | ps    |

| Pico Timo *                               | t <sub>r min</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =10pF                                                           |      | 0.9    |      |        | 0.8  |      | 20    |

| Rise Time *                               | t <sub>r max</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =20pF                                                           |      | 1.1    |      |        | 1.1  |      | ns    |

| Fall Time *                               | t <sub>f min</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =10pF                                                           |      | 1.0    |      |        | 1.0  |      | na    |

|                                           | t <sub>f max</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =20pF                                                           |      | 1.2    |      |        | 1.2  |      | ns    |

## **Motherboard Clock Generator IC**

January 2000

## **Table 9: AC Timing Specifications, continued**

Unless otherwise stated, all power supplies = 3.3V, no load on any output, and ambient temperature  $T_A = 25^{\circ}\text{C}$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Spread spectrum modulation is disabled except for Rise/Fall time measurements.

| PARAMETER                              | SYMBOL             | CONDITIONS/DESCRIPTION                                                                                 |      | 133MHz | 2    |      | 100MHz | 2    | UNITS |  |

|----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|------|--------|------|------|--------|------|-------|--|

| PARAMETER                              | STWIBOL            | CONDITIONS/DESCRIPTION                                                                                 | MIN. | TYP.   | MAX. | MIN. | TYP.   | MAX. | UNITS |  |

| CPU_0:3 Clock Outputs (2.5V Ty         | pe 1 Clock Buffe   | r)                                                                                                     |      |        |      |      |        |      |       |  |

| Duty Cycle *                           | dt                 | Ratio of high pulse width to one clock period, measured at 1.5V                                        | 45   | 49     | 55   | 45   | 49     | 55   | %     |  |

| Clock Skew *                           | t <sub>skw</sub>   | CPU to CPU @ 1.25V, C <sub>L</sub> =20pF                                                               |      | +60    |      |      | +60    |      |       |  |

| Jitter, Long Term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.25V relative to an ideal clock, C <sub>L</sub> =20pF, all PLLs active |      | 136    |      |      | 134    |      | ps    |  |

| Jitter, Period (peak-peak) *           | $t_{j(\DeltaP)}$   | From rising edge to rising edge at 1.25V, C <sub>L</sub> =20pF, all PLLs active                        |      | 123    |      |      | 97     |      | ps    |  |

| Rise Time *                            | t <sub>r min</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =10pF                                                           |      | 1.1    |      |      | 0.9    |      | ns    |  |

| Rise fillie                            | t <sub>r max</sub> | Measured @ 0.4V - 2.0V; C <sub>L</sub> =20pF                                                           |      | 1.4    |      |      | 1.4    |      | 113   |  |

| Fall Time *                            | t <sub>f min</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =10pF                                                           |      | 1.0    |      |      | 0.9    |      |       |  |

| raii Time                              | t <sub>f max</sub> | Measured @ 2.0V - 0.4V; C <sub>L</sub> =20pF                                                           |      | 1.1    |      |      | 1.2    |      | ns    |  |

| Enable Delay *                         | t <sub>DLH</sub>   | via CPU_STOP#                                                                                          | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

| Disable Delay *                        | t <sub>DHL</sub>   | via CPU_STOP#                                                                                          | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

| REF_0:1 Clock Outputs (3.3V Ty         | pe 3 Clock Buffe   | r)                                                                                                     |      |        |      | •    |        |      |       |  |

| Duty Cycle *                           | dt                 | Ratio of high pulse width to one clock period, measured at 1.5V                                        | 45   | 50     | 55   | 45   | 50     | 55   | %     |  |

| Jitter, Long Term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.5V relative to an ideal clock, C <sub>L</sub> =20pF, all PLLs active  |      | 27     |      |      | 23     |      | ps    |  |

| Jitter, Period (peak-peak) *           | $t_{j(\DeltaP)}$   | From rising edge to rising edge at 1.5V, C <sub>L</sub> =20pF, all PLLs active                         |      | 177    |      |      | 111    |      | ps    |  |

| Rise Time *                            | t <sub>r min</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =10pF                                                           |      | 0.9    |      |      | 0.9    |      | ns    |  |

| Nise Time                              | t <sub>r max</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =20pF                                                           |      | 1.4    |      |      | 1.4    |      | 115   |  |

| Fall Time *                            | t <sub>f min</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =10pF                                                           |      | 1.0    |      |      | 1.0    |      | ns    |  |

| i all tillie                           | t <sub>f max</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =20pF                                                           |      | 1.6    |      |      | 1.6    |      | 115   |  |

| CK48 Clock Output (3.3V Type 3         | Clock Buffer)      |                                                                                                        |      |        |      |      |        |      |       |  |

| Duty Cycle *                           | d <sub>t</sub>     | Ratio of high pulse width to one clock period, measured at 1.5V                                        | 45   | 51     | 55   | 45   | 51     | 55   | %     |  |

| Jitter, Long Term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.5V relative to an ideal clock, C <sub>L</sub> =20pF, all PLLs active  |      | 244    |      |      | 246    |      | ps    |  |

| Jitter, Period (peak-peak) *           | $t_{j(\DeltaP)}$   | From rising edge to rising edge at 1.5V, C <sub>L</sub> =20pF, all PLLs active                         |      | 143    |      |      | 202    |      | ps    |  |

| Dica Time *                            | t <sub>r min</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =10pF                                                           |      | 0.8    |      |      | 0.8    |      |       |  |

| Rise Time *                            | t <sub>r max</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =20pF                                                           |      | 1.3    |      |      | 1.3    |      | ns    |  |

| Fall Time *                            | t <sub>f min</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =10pF                                                           |      | 0.9    |      |      | 0.9    |      |       |  |

|                                        | t <sub>f max</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =20pF                                                           |      | 1.4    |      |      | 1.4    |      | ns    |  |

### **Table 9: AC Timing Specifications, continued**

Unless otherwise stated, all power supplies = 3.3V, no load on any output, and ambient temperature  $T_A = 25^{\circ}\text{C}$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Spread spectrum modulation is disabled except for Rise/Fall time measurements.

| PARAMETER                              | SYMBOL             | CONDITIONS/DESCRIPTION                                                                                |      | 133MHz | !    |      | 100MHz | :    | UNITS |  |

|----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|------|--------|------|------|--------|------|-------|--|

| PARAMETER                              | STWBOL             | CONDITIONS/DESCRIPTION                                                                                | MIN. | TYP.   | MAX. | MIN. | TYP.   | MAX. | UNITS |  |

| PCI_1:7, PCI_F Clock Outputs (3.3      | V Type 5 Clock     | Buffer)                                                                                               |      |        |      |      |        |      |       |  |

| Duty Cycle *                           | d <sub>t</sub>     | Ratio of high pulse width to one clock period, measured at 1.5V                                       | 45   | 47     | 55   | 45   | 50     | 55   | %     |  |

| Clark Chau *                           |                    | PCI_F to PCI @ 1.5V, C <sub>L</sub> =30pF                                                             |      | +660   |      |      | +660   |      |       |  |

| Clock Skew *                           | t <sub>skw</sub>   | PCI to PCI @ 1.5V, C <sub>L</sub> =30pF                                                               |      | +60    |      |      | +60    |      | ps    |  |

| Jitter, Long Term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.5V relative to an ideal clock, C <sub>L</sub> =30pF, all PLLs active |      | 220    |      |      | 131    |      | ps    |  |

| Jitter, Period (peak-peak) *           | $t_{j(\Delta P)}$  | From rising edge to rising edge at 1.5V, C <sub>L</sub> =30pF, all PLLs active                        |      | 76     |      |      | 95     |      | ps    |  |

| Rise Time *                            | t <sub>r min</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =10pF                                                          |      | 1.2    |      |      | 1.3    |      | ns    |  |

| Rise Time                              | t <sub>r max</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =30pF                                                          |      | 1.8    |      |      | 1.8    |      | 115   |  |

| Fall Time *                            | t <sub>f min</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =10pF                                                          |      | 1.3    |      |      | 1.2    |      | 20    |  |

|                                        | t <sub>f max</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =30pF                                                          |      | 1.6    |      |      | 1.5    |      | ns    |  |

| Enable Delay *                         | t <sub>DLH</sub>   | via PCI_STOP#                                                                                         | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

| Disable Delay *                        | t <sub>DHL</sub>   | via PCI_STOP#                                                                                         | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

| CK66_0:3 Clock Outputs (3.3V Typ       | e 5 Clock Buffe    | er)                                                                                                   |      |        |      |      |        |      |       |  |

| Duty Cycle *                           | d <sub>t</sub>     | Ratio of high pulse width to one clock period, measured at 1.5V                                       | 45   | 52     | 55   | 45   | 51     | 55   | %     |  |

| Clock Skew *                           | t <sub>skw</sub>   | CK66 to CK66 @ 1.5V, C <sub>L</sub> =30pF                                                             |      | 120    |      |      | 120    |      | ps    |  |

| Jitter, Long Term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub> | On rising edges 500µs apart at 1.5V relative to an ideal clock, C <sub>L</sub> =30pF, all PLLs on     |      | 137    |      |      | 123    |      | ps    |  |

| Jitter, Period (peak-peak) *           | $t_{j(\DeltaP)}$   | From rising edge to rising edge at 1.5V, C <sub>L</sub> =30pF, all PLLs active                        |      | 75     |      |      | 79     |      | ps    |  |

| Rise Time *                            | t <sub>r min</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =10pF                                                          |      | 0.9    |      |      | 0.9    |      | 20    |  |

| KISE TIME                              | t <sub>r max</sub> | Measured @ 0.4V - 2.4V; C <sub>L</sub> =30pF                                                          |      | 1.5    |      |      | 1.5    |      | ns    |  |

| Fall Time *                            | t <sub>f min</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =10pF                                                          |      | 1.0    |      |      | 1.0    |      | nc    |  |

| i aii i iiii c                         | t <sub>f max</sub> | Measured @ 2.4V - 0.4V; C <sub>L</sub> =30pF                                                          |      | 1.4    |      |      | 1.4    |      | ns    |  |

| Enable Delay *                         | t <sub>DLH</sub>   | via CPU_STOP#                                                                                         | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

| Disable Delay *                        | t <sub>DHL</sub>   | via CPU_STOP#                                                                                         | 1.0  |        | 8.0  | 1.0  |        | 8.0  | ns    |  |

Figure 9: Clock Skew Diagrams

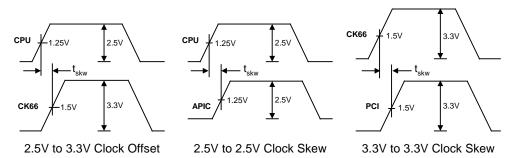

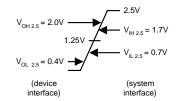

**Figure 10: DC Measurement Points**

A. 3.3V Clock Interface

B. 2.5V Clock Interface

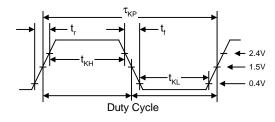

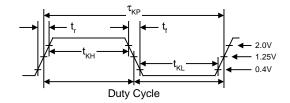

**Figure 11: Timing Diagrams**

A. 3.3V Clock Interface

B. 2.5V Clock Interface

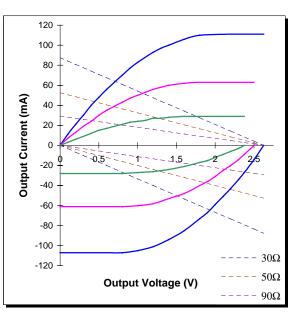

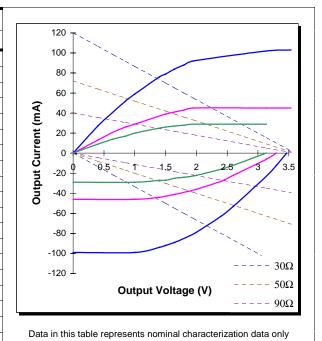

Table 10: CPU\_0:3, CPU/2\_0:1, APIC\_0:2 Clock Outputs

| Voltage | High Drive Current (mA) |      |      | Voltage | Low Drive Current (mA) |      |      |

|---------|-------------------------|------|------|---------|------------------------|------|------|

| (V)     | MIN.                    | TYP. | MAX. | (V)     | MIN.                   | TYP. | MAX. |

| 0       | 0                       | 0    | 0    | 0       | -28                    | -61  | -107 |

| 0.1     | 3                       | 7    | 11   | 0.4     | -28                    | -61  | -107 |

| 0.2     | 6                       | 13   | 21   | 0.6     | -28                    | -61  | -107 |

| 0.3     | 9                       | 19   | 30   | 0.8     | -28                    | -61  | -107 |

| 0.4     | 12                      | 24   | 40   | 1       | -27                    | -60  | -105 |

| 0.5     | 15                      | 30   | 48   | 1.2     | -26                    | -58  | -101 |

| 0.6     | 17                      | 35   | 56   | 1.4     | -24                    | -53  | -94  |

| 0.7     | 19                      | 39   | 63   | 1.6     | -21                    | -48  | -85  |

| 0.8     | 21                      | 43   | 70   | 1.8     | -17                    | -40  | -73  |

| 0.9     | 23                      | 47   | 77   | 1.9     | -15                    | -36  | -67  |

| 1       | 24                      | 50   | 83   | 2       | -12                    | -31  | -59  |

| 1.1     | 25                      | 53   | 88   | 2.1     | -9                     | -25  | -51  |

| 1.2     | 27                      | 56   | 93   | 2.2     | -6                     | -20  | -43  |

| 1.3     | 27                      | 58   | 97   | 2.3     | -3                     | -14  | -34  |

| 1.4     | 28                      | 60   | 100  | 2.375   | 0                      | -9   | -27  |

| 1.6     | 29                      | 62   | 106  | 2.5     |                        | 0    | -14  |

| 1.8     | 29                      | 63   | 110  | 2.625   |                        |      | 0    |

| 2.2     | 29                      | 63   | 111  |         |                        |      |      |

| 2.375   | 29                      | 63   | 111  |         |                        |      |      |

| 2.5     |                         | 63   | 111  |         |                        |      |      |

| 2 625   |                         |      | 111  |         |                        |      |      |

Data in this table represents nominal characterization data only

**ISC9001**

Table 11: REF\_0:1, CK48 Clock Outputs

| Voltage<br>(V) | High Drive Current (mA) |      |      | Voltage | Low Drive Current (mA) |      |      |

|----------------|-------------------------|------|------|---------|------------------------|------|------|

|                | MIN.                    | TYP. | MAX. | (V)     | MIN.                   | TYP. | MAX. |

| 0              | 0                       | 0    | 0    | 0       | -29                    | -46  | -99  |

| 0.4            | 9                       | 13   | 27   | 1       | -29                    | -46  | -99  |

| 0.65           | 14                      | 21   | 41   | 1.4     | -27                    | -44  | -94  |

| 0.85           | 17                      | 26   | 52   | 1.5     | -27                    | -43  | -92  |

| 1              | 20                      | 29   | 59   | 1.65    | -25                    | -41  | -89  |

| 1.4            | 25                      | 37   | 76   | 1.8     | -24                    | -39  | -85  |

| 1.5            | 26                      | 39   | 79   | 2       | -22                    | -36  | -79  |

| 1.65           | 27                      | 41   | 84   | 2.4     | -16                    | -28  | -63  |

| 1.8            | 28                      | 43   | 88   | 2.6     | -12                    | -22  | -53  |

| 1.95           | 29                      | 45   | 92   | 3.135   | 0                      | -6   | -23  |

| 3.135          | 29                      | 45   | 102  | 3.3     |                        | 0    | -12  |

| 3.6            |                         | 45   | 102  | 3.465   |                        |      | 0    |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

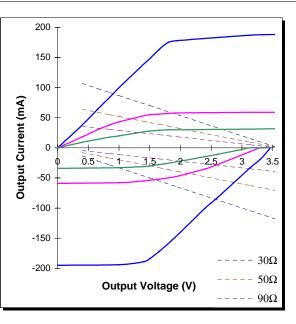

Table 12: PCI\_1:7, PCI\_F, CK66\_0:3 Clock Outputs

| Voltage<br>(V) | High Drive Current (mA) |      |      | Voltage | Low Drive Current (mA) |      |      |

|----------------|-------------------------|------|------|---------|------------------------|------|------|

|                | MIN.                    | TYP. | MAX. | (V)     | MIN.                   | TYP. | MAX. |

| 0              | 0                       | 0    | 0    | 0       | -34                    | -59  | -195 |

| 0.4            | 9.4                     | 18   | 38   | 1       | -33                    | -58  | -194 |

| 0.65           | 14                      | 30   | 64   | 1.4     | -31                    | -55  | -189 |

| 0.85           | 17.7                    | 38   | 84   | 1.5     | -30                    | -54  | -184 |

| 1              | 20                      | 43   | 100  | 1.65    | -28                    | -52  | -172 |

| 1.4            | 26.5                    | 53   | 139  | 1.8     | -25.5                  | -50  | -159 |

| 1.5            | 28                      | 55   | 148  | 2       | -22                    | -46  | -140 |

| 1.65           | 29                      | 56   | 163  | 2.4     | -14.5                  | -35  | -100 |

| 1.8            | 30                      | 57   | 175  | 2.6     | -11                    | -28  | -83  |

| 1.95           | 30                      | 58   | 178  | 3.135   | 0                      | -6   | -33  |

| 3.135          | 31                      | 59   | 187  | 3.3     |                        | 0    | -19  |

| 3.6            | 32                      | 59   | 188  | 3.465   |                        |      | 0    |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

|                |                         |      |      |         |                        |      |      |

Data in this table represents nominal characterization data only

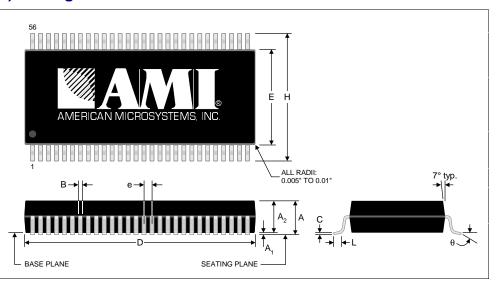

## 7.0 Package Information

Table 13: 56-pin SSOP (0.300") Package Dimensions

|                | DIMENSIONS |        |             |       |  |  |

|----------------|------------|--------|-------------|-------|--|--|

|                | INC        | HES    | MILLIMETERS |       |  |  |

|                | MIN. MAX.  |        | MIN.        | MAX.  |  |  |

| Α              | 0.095      | 0.110  | 2.41        | 2.79  |  |  |

| A <sub>1</sub> | 0.008      | 0.016  | 0.203       | 0.406 |  |  |

| A <sub>2</sub> | 0.088      | 0.092  | 2.24        | 2.34  |  |  |

| В              | 0.008      | 0.0135 | 0.203       | 0.343 |  |  |

| С              | 0.005      | 0.010  | 0.127       | 0.254 |  |  |

| D              | 0.720      | 0.730  | 18.29       | 18.54 |  |  |

| Е              | 0.292      | 0.299  | 7.42        | 7.59  |  |  |

| е              | 0.025      | BSC    | 0.64        | BSC   |  |  |

| Н              | 0.400      | 0.410  | 10.16       | 10.41 |  |  |

| L              | 0.024      | 0.040  | 0.610       | 1.02  |  |  |

| Θ              | 0°         | 8°     | 0°          | 8°    |  |  |

Table 14: 56-pin SSOP (0.300") Package Characteristics

| PARAMETER                               | SYMBOL          | CONDITIONS/DESCRIPTION                        | TYP. | UNITS   |  |

|-----------------------------------------|-----------------|-----------------------------------------------|------|---------|--|

| Thermal Impedance, Junction to Free-Air | $\Theta_{JA}$   | Air flow = 0 m/s                              | 81   | °C/W    |  |

| Lood Industrance Colf                   |                 | Longest trace + wire                          | 6.41 | 6.41 nH |  |

| Lead Inductance, Self                   | L <sub>11</sub> | Shortest trace + wire                         | 2.49 | nn      |  |

|                                         |                 | Longest trace + wire to first adjacent trace  | 3.65 |         |  |

| Lood Industry of Mutual                 | L <sub>12</sub> | Shortest trace + wire to first adjacent trace | 1.35 | nH      |  |

| Lead Inductance, Mutual                 |                 | Longest trace + wire to next adjacent trace   | 2.50 |         |  |

|                                         | L <sub>13</sub> | Shortest trace + wire to next adjacent trace  | 0.90 |         |  |

| Lond Conneitance Bulk                   | 6               | Longest trace + wire to V <sub>SS</sub>       | 0.94 | , r     |  |

| Lead Capacitance, Bulk                  | C <sub>11</sub> | Shortest trace + wire to V <sub>SS</sub>      | 0.49 | pF      |  |

|                                         |                 | Longest trace + wire to first adjacent trace  | 0.48 |         |  |

| Lood Considered Matrial                 | C <sub>12</sub> | Shortest trace + wire to first adjacent trace | 0.20 |         |  |

| Lead Capacitance, Mutual                | 0               | Longest trace + wire to next adjacent trace   | 0.04 | pF      |  |

|                                         | C <sub>13</sub> | Shortest trace + wire to next adjacent trace  | 0.01 | 7       |  |

## 8.0 Ordering Information

### **Table 15: Device Ordering Codes**

| DEVICE NUMBER | ORDERING CODE | PACKAGE TYPE                                                 | OPERATING<br>TEMPERATURE RANGE | SHIPPING<br>CONFIGURATION |  |

|---------------|---------------|--------------------------------------------------------------|--------------------------------|---------------------------|--|

| FS6261-01     | 11565-801     | 48-pin (7.5mm/0.300") SSOP<br>(Shrink Small Outline Package) | 0°C to 70°C (Commercial)       | Tape and Reel             |  |

| F30201-U1     | 11565-811     | 48-pin (7.5mm/0.300") SSOP<br>(Shrink Small Outline Package) | 0°C to 70°C (Commercial)       | Tubes                     |  |

### 9.0 Revision Information

| DATE    | PAGE  | DESCRIPTION                   |

|---------|-------|-------------------------------|

| 1/31/00 | 11-13 | Updated characterization data |

#### Copyright © 1999, 2000 American Microsystems, Inc.

Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMI makes no warranty, express, statutory implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI makes no warranty of merchantability or fitness for any purposes. AMI reserves the right to discontinue production and change specifications and prices at any time and without notice. AMI's products are intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, are specifically not recommended without additional processing by AMI for such applications.

American Microsystems, Inc., 2300 Buckskin Rd., Pocatello, ID 83201, (208) 233-4690, FAX (208) 234-6796, WWW Address: http://www.amis.com E-mail: tgp@amis.com