# ANALOG 4-Channel, 12-/10-Bit ADCs with I<sup>2</sup>C Compatible **Interface in 16-Lead TSSOP**

# **Preliminary Technical Data**

# AD7994/AD7993

#### **FEATURES**

12-Bit ADC with Fast Conversion Time: 2 µs Four Single-Ended Analog Input Channels Specified for V<sub>DD</sub> of 2.7 V to 5.5 V **Low Power Consumption** Fast Throughput Rate: - 188 KSPS **Sequencer Operation Automatic Cycle Mode** I<sup>2</sup>C<sup>R</sup> Compatible Serial Interface I<sup>2</sup>C<sup>R</sup> Interface supports: Standard, Fast, and High-Speed Modes Out of Range Indicator/Alert Function

Pin-Selectable Addressing via AS Two Versions Allow Five I<sup>2</sup>C Addresses Shutdown Mode: 1µA max 16-Lead TSSOP Package

#### **GENERAL DESCRIPTION**

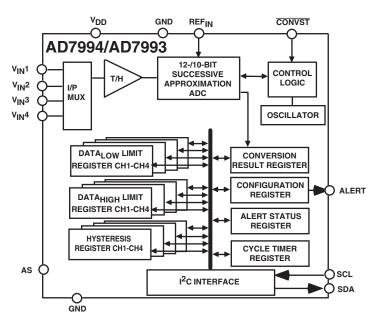

The AD7994/AD7993 are 4 channel, 12-/10-bit, high speed, low power, successive-approximation ADCs respectively. They operate from a single 2.7 V to 5.5 V power supply and feature a conversion time of 2 µs. The parts contain a four channel multiplexer and track/hold amplifier which can handle input frequencies in excess of TBD kHz.

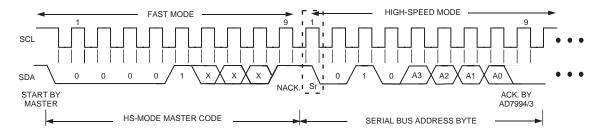

The AD7994/AD7993 provide a two-wire serial interface which is compatible with I<sup>2</sup>C interfaces. The parts come in two versions, AD7994-0/AD7993-0 to AD7994-1/ AD7993-1. Each version allows for a minimum of two different I<sup>2</sup>C addresses. The I<sup>2</sup>C interface on the AD7994-0/AD7993-0 supports Standard and Fast I<sup>2</sup>C Interface Modes. The I<sup>2</sup>C interface on the AD7994-1/AD7993-1 supports Standard, Fast and two High-Speed I<sup>2</sup>C Interface Modes.

The AD7994/AD7993 normally remain in a shutdown state while not converting, powering up only for conversions. The conversion process can be controlled using the CONVST pin, an Automatic Conversion Cycle selected through software control, or a mode where conversions occur across Write operations. There are no pipeline delays associated with the part.

The reference for the part is applied externally to the REF<sub>IN</sub> pin and can be in the range of 1.2V to V<sub>DD</sub>. This allows the widest dynamic input range to the ADC.

#### FUNCTIONAL BLOCK DIAGRAM

On-chip registers can be programmed with high and low limits for the conversion result, and an open drain Out of Range Indicator output (ALERT), becomes active when the programmed high or low limits are violated by the conversion result. This output can be used as an interrupt.

#### PRODUCT HIGHLIGHTS

- 1. 2 us Conversion time with low power consumption.

- 2. I<sup>2</sup>C Compatible Serial Interface with pin selectable addresses. Two AD7994/AD7993 versions allow five AD7994/AD7993 devices to be connected to the same serial bus.

- 3. The parts feature automatic shutdown while not converting to maximize power efficiency. Current consumption is 1µA max when in shutdown.

- 4. Reference can be driven up to the power supply.

- 5. Out of Range Indicator which can be software disabled/ enabled.

- 6. Oneshot and automatic conversion rates.

- 7. No Pipeline Delay The part features a standard successive-approximation ADC.

SMBus is a trademark and I<sup>2</sup>C is a registered trademark of Philips Corporation

#### REV. PrF 09/03

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. World Wide Web Site: http://www.analog.com Tel: 781/329-4700 Fax: 781/326-8703 Analog Devices, Inc., 2003

# $\begin{array}{c} \textbf{PRELIMINARYTECHNICAL DATA} \\ \textbf{AD7994-SPECIFICATIONS}^{1} \text{ ($V_{DD} = +2.7$ V to $+5.5$ V, unless otherwise noted; REF_{IN} = 2.5 V; f_{SCL} = 3.4 \text{ MHz unless}} \\ \textbf{otherwise noted; T}_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.)} \end{array}$

| Parameter                                           | B Version <sup>1</sup> | Units        | Test Conditions/Comments              |

|-----------------------------------------------------|------------------------|--------------|---------------------------------------|

| DYNAMIC PERFORMANCE                                 |                        |              | F <sub>IN</sub> = 10kHz Sine Wave     |

| Signal to Noise + Distortion (SINAD) <sup>2</sup>   | 70                     | dB min       | IN TORRES SING WAVE                   |

| Signal to Noise Ratio (SNR) <sup>2</sup>            | 71                     | dB min       |                                       |

| Total Harmonic Distortion (THD) <sup>2</sup>        | -78                    | dB typ       |                                       |

| Peak Harmonic or Spurious Noise (SFDR) <sup>2</sup> | -80                    |              |                                       |

| Intermodulation Distortion (IMD) <sup>2</sup>       | -00                    | dB typ       | for TDD LILE for TDD LILE             |

| · · · · · · · · · · · · · · · · · · ·               | 7.0                    | ID .         | fa = TBD kHz, fb = TBD kHz            |

| Second Order Terms                                  | -78                    | dB typ       |                                       |

| Third Order Terms                                   | -78                    | dB typ       |                                       |

| Aperture Delay                                      | 10                     | ns max       |                                       |

| Aperture Jitter                                     | 10                     | ps typ       |                                       |

| Channel-to-Channel Isolation                        | TBD                    | dB typ       | $F_{IN} = TBD kHz$                    |

| Full Power Bandwidth                                | TBD                    | kHz typ      | @ 3 dB                                |

|                                                     | TBD                    | kHz typ      | @ 0.1 dB                              |

| DC ACCURACY                                         |                        |              |                                       |

| Resolution                                          | 12                     | Bits         |                                       |

| Integral Nonlinearity <sup>2</sup>                  | ±1                     | LSB max      |                                       |

| <del>0. m.                                 </del>   | ±0.6                   | LSB typ      |                                       |

| Differential Nonlinearity <sup>2</sup>              | +1.5/-0.9              | LSB typ      | Guaranteed No Missed Codes to 12      |

| Differential information                            | ±0.75                  | LSB typ      | Bits.                                 |

| Offset Error <sup>2</sup>                           | ±1.5                   | LSB typ      | Dits.                                 |

|                                                     |                        |              |                                       |

| Offset Error Match <sup>2</sup>                     | ±0.5                   | LSB max      |                                       |

| Gain Error <sup>2</sup>                             | ±1.5                   | LSB max      |                                       |

| Gain Error Match <sup>2</sup>                       | ±0.5                   | LSB max      |                                       |

| ANALOG INPUT                                        |                        |              |                                       |

| Input Voltage Ranges                                | 0 to REF <sub>IN</sub> | Volts        |                                       |

| DC Leakage Current                                  | ±1                     | μA max       |                                       |

| Input Capacitance                                   | 30                     | pF typ       |                                       |

| REFERENCE INPUT                                     |                        |              |                                       |

| REF <sub>IN</sub> Input Voltage Range               | $1.2$ to $V_{\rm DD}$  | V min/Vmax   |                                       |

| DC Leakage Current                                  | ±1                     | μA max       |                                       |

| Input Capacitance                                   | TBD                    | pF max       |                                       |

| Input Impedance                                     | TBD                    | kΩ typ       |                                       |

|                                                     | TBD                    | Kaz typ      |                                       |

| LOGIC INPUTS (SDA, SCL)                             | 0.5(11)                |              |                                       |

| Input High Voltage, V <sub>INH</sub>                | $0.7(V_{DD})$          | V min        |                                       |

| Input Low Voltage, V <sub>INL</sub>                 | $0.3(V_{DD})$          | V max        |                                       |

| Input Leakage Current, I <sub>IN</sub>              | ±1                     | μA max       | $V_{IN} = 0 V \text{ or } V_{DD}$     |

| Input Capacitance, $C_{IN}^{2,3}$                   | 10                     | pF max       |                                       |

| Input Hysteresis, V <sub>HYST</sub>                 | TBD                    | V min        |                                       |

| LOGIC INPUT $(\overline{CONVST})$                   |                        |              |                                       |

| Input High Voltage, V <sub>INH</sub>                | 2.4                    | V min        | $V_{\rm DD} = 5V$                     |

|                                                     | 2.0                    | V min        | $V_{DD} = 3 \text{ V}$                |

| Input Low Voltage, V <sub>INL</sub>                 | 0.8                    | V max        | $V_{DD} = 5V$                         |

| 2 O / INL                                           | 0.4                    | V max        | $V_{DD} = 3V$                         |

| Input Leakage Current, I <sub>IN</sub>              | ±1                     | μA max       | $V_{IN} = 0 \text{ V or } V_{DD}$     |

| Input Capacitance, $C_{IN}^{2,3}$                   | 10                     | pF max       | VIIV O V OI VDD                       |

| LOGIC OUTPUTS (OPEN DRAIN)                          |                        |              |                                       |

| Output Low Voltage, $V_{OL}$                        | 0.4                    | V max        | $I_{SINK} = 3mA$                      |

| Calput Don Foliage, FOL                             | 0.6                    | V max        | $I_{SINK} = SIMY$<br>$I_{SINK} = 6mA$ |

| Floating State Legitoge Comment                     | ±1                     |              | ISINK - UIIIA                         |

| Floating State Current Consistence <sup>2,3</sup>   |                        | μA max       |                                       |

| Floating-State Output Capacitance <sup>2,3</sup>    | TBD                    | pF max       |                                       |

| Output Coding                                       | Straight (Natu         | prai) Binary |                                       |

-2-

REV. PrF

$\begin{array}{c} \textbf{PRELIMINARY TECHNICAL DATA} \\ \textbf{AD7994-SPECIFICATIONS}^1 \text{ ($V_{DD}=+2.7$ V to $+5.5$ V, unless otherwise noted; $REF_{IN}=2.5$ V; $f_{SCL}=3.4$ MHz unless otherwise noted.)} \end{array}$

| Parameter                           | B Version <sup>1</sup> | Units    | Test Conditions/Comments                             |

|-------------------------------------|------------------------|----------|------------------------------------------------------|

| CONVERSION RATE                     |                        |          | See Interface Section                                |

| Conversion Time                     | 2                      | μs typ   |                                                      |

| Track/Hold Acquisition Time         | TBD                    | ns max   | Full-Scale step input                                |

|                                     | TBD                    | ns max   | Sine wave input <= 30 KHz                            |

| Throughput Rate                     | 3.4                    | KSPS max | Standard mode SCL = 100 kHz                          |

|                                     | 13                     | KSPS max | Fast Mode SCL = 400 kHz                              |

|                                     | 79                     | KSPS max | High-Speed Mode SCL = 3.4 MHz                        |

| POWER REQUIREMENTS                  |                        |          |                                                      |

| $ m V_{DD}$                         | 2.7/5.5 V              | min/max  |                                                      |

| ${ m I}_{ m DD}$                    |                        |          | Digital Inputs = 0 V or $V_{DD}$                     |

| Peak Current                        | TBD                    | μA max   | Peak Current during conversion                       |

| Power Down Mode, Interface Inactive | 0.2/0.6                | μA max   | $V_{DD} = 3 \text{ V/5 V}.$                          |

| Interface Active                    | 0.05/0.2               | mA max   | $V_{\rm DD} = 3 \text{ V/5 V } 400 \text{ kHz SCL}.$ |

|                                     | 0.3/0.8                | mA max   | $V_{\rm DD}$ = 3 V/5 V 3.4 MHz SCL.                  |

| Operating, Interface Inactive       | 0.06/0.15              | mA max   | $V_{\rm DD} = 3 \text{ V/5 V } 400 \text{ kHz SCL}.$ |

| - F                                 | 0.3/0.6                | mA max   | $V_{DD} = 3 \text{ V/5 V } 3.4 \text{ MHz SCL}.$     |

| Interface Active                    | 0.15/0.35              | mA max   | $V_{DD} = 3 \text{ V/5 V } 400 \text{ kHz SCL}.$     |

|                                     | 0.6/1.4                | mA max   | $V_{DD} = 3 \text{ V/5 V } 3.4 \text{ MHz SCL}.$     |

#### NOTES

<sup>&</sup>lt;sup>1</sup>Temperature ranges as follows: B Version: -40°C to +85°C.

$<sup>^2</sup>$ See Terminology.

<sup>&</sup>lt;sup>3</sup>Sample tested @ +25°C to ensure compliance.

<sup>&</sup>lt;sup>4</sup>See POWER VERSUS THROUGHPUT RATE section.

Specifications subject to change without notice.

$\begin{array}{c} \textbf{PRELIMINARYTECHNICAL DATA} \\ \textbf{AD7993-SPECIFICATIONS}^1 \text{ ($V_{DD} = +2.7$ V to +5.5$ V, unless otherwise noted; REF_{IN} = 2.5$ V; f_{SCL} = 3.4$ MHz unless otherwise noted.)} \end{array}$

| Parameter                                                                  | B Version <sup>1</sup>         | Units      | Test Conditions/Comments          |

|----------------------------------------------------------------------------|--------------------------------|------------|-----------------------------------|

| DYNAMIC PERFORMANCE                                                        |                                |            | $F_{IN} = 10$ kHz Sine Wave       |

| Signal to Noise + Distortion (SINAD) <sup>2</sup>                          | 61                             | dB min     |                                   |

| Signal to Noise Ratio (SNR) <sup>2</sup>                                   | TBD                            | dB min     |                                   |

| Total Harmonic Distortion (THD) <sup>2</sup>                               | -73                            | dB typ     |                                   |

| Peak Harmonic or Spurious Noise (SFDR) <sup>2</sup>                        | -74                            | dB typ     |                                   |

| Intermodulation Distortion (IMD) <sup>2</sup>                              | ' '                            | ab typ     | fa = TBD kHz, fb = TBD kHz        |

| Second Order Terms                                                         | -78                            | dB typ     |                                   |

| Third Order Terms                                                          | -78                            | dB typ     |                                   |

| Aperture Delay                                                             | 10                             | ns max     |                                   |

| Aperture Jitter                                                            | 10                             | ps typ     |                                   |

| Channel-to-Channel Isolation                                               | TBD                            | dB typ     | $F_{IN} = TBD kHz$                |

| Full Power Bandwidth                                                       | TBD                            | kHz typ    | @ 3 dB                            |

| Tun Tower Bandwidth                                                        | TBD                            | kHz typ    | @ 0.1 dB                          |

|                                                                            | TBD                            | KIIZ typ   | (ii) 0.1 UD                       |

| DC ACCURACY                                                                | 1.0                            | D.         |                                   |

| Resolution                                                                 | 10                             | Bits       |                                   |

| Integral Nonlinearity <sup>2</sup>                                         | ±1                             | LSB max    |                                   |

| D:00                                                                       | ±0.6                           | LSB typ    |                                   |

| Differential Nonlinearity <sup>2</sup>                                     | ±0.9                           | LSB max    | Guaranteed No Missed Codes to 10  |

| Offset Error <sup>2</sup>                                                  | +1                             | LSB max    | Bits.                             |

|                                                                            | ±1                             |            |                                   |

| Offset Error Match <sup>2</sup>                                            | ±0.5                           | LSB max    |                                   |

| Gain Error <sup>2</sup>                                                    | ±1                             | LSB max    |                                   |

| Gain Error Match <sup>2</sup>                                              | ±0.5                           | LSB max    |                                   |

| Total Unadjusted Error (TUE) <sup>2</sup>                                  | ±1                             | LSB max    |                                   |

| ANALOG INPUT                                                               |                                |            |                                   |

| Input Voltage Ranges                                                       | 0 to REF <sub>IN</sub>         | Volts      |                                   |

| DC Leakage Current                                                         | ±1                             | μA max     |                                   |

| Input Capacitance                                                          | 30                             | pF typ     |                                   |

| REFERENCE INPUT                                                            |                                |            |                                   |

| REF <sub>IN</sub> Input Voltage Range                                      | TBD/TBD                        | V min/Vmax |                                   |

| DC Leakage Current                                                         | ±1                             | μA max     |                                   |

| Input Capacitance                                                          | TBD                            | pF max     |                                   |

| Input Impedance                                                            | TBD                            | kΩ typ     |                                   |

| LOGIC INPUTS (SDA, SCL, $\overline{\text{CONVST}}$ )                       |                                |            |                                   |

| Input High Voltage, V <sub>INH</sub>                                       | $0.7(V_{DD})$                  | V min      |                                   |

| Input Low Voltage, $V_{INL}$                                               | $0.7(V_{DD})$<br>$0.3(V_{DD})$ | V max      |                                   |

| Input Low Voltage, V <sub>INL</sub> Input Leakage Current, I <sub>IN</sub> | ±1                             | μA max     | $V_{IN} = 0 V \text{ or } V_{DD}$ |

| Input Capacitance, $C_{IN}^{2,3}$                                          | 10                             | pF max     | VIN = 0 V OI VDD                  |

| Input Hysteresis, $V_{HYST}$                                               | TBD                            | V min      |                                   |

|                                                                            | TBD                            | V 111111   |                                   |

| LOGIC INPUT $(\overline{CONVST})$                                          |                                |            |                                   |

| Input High Voltage, V <sub>INH</sub>                                       | 2.4                            | V min      | $V_{DD} = 5V$                     |

|                                                                            | 2.0                            | V min      | $V_{DD} = 3 V$                    |

| Input Low Voltage, V <sub>INL</sub>                                        | 0.8                            | V max      | $V_{DD} = 5V$                     |

|                                                                            | 0.4                            | V max      | $V_{DD} = 3V$                     |

| Input Leakage Current, I <sub>IN</sub>                                     | ±1                             | μA max     | $V_{IN} = 0 V \text{ or } V_{DD}$ |

| Input Capacitance, $C_{IN}^{2,3}$                                          | 10                             | pF max     |                                   |

| LOGIC OUTPUTS (OPEN DRAIN)                                                 |                                |            |                                   |

| Output Low Voltage, Vol.                                                   | 0.4                            | V max      | $I_{SINK} = 3mA$                  |

| <del>-</del>                                                               | 0.6                            | V max      | $I_{SINK} = 6mA$                  |

| Floating-State Leakage Current                                             | ±1                             | μA max     |                                   |

|                                                                            |                                | 1 5        | 1                                 |

| Floating-State Output Capacitance <sup>2,3</sup>                           | TBD                            | pF max     |                                   |

-4-

REV. PrF

# $\begin{array}{c} \textbf{PRELIMINARY TECHNICAL DATA} \\ \textbf{AD7993-SPECIFICATIONS}^{1 \ (V_{DD} \ = +2.7 \ V \ to \ +5.5 \ V, \ unless \ otherwise \ noted; \ \textbf{REF}_{IN} = 2.5 \ V; \ \textbf{f}_{SCL} = 3.4 \ \text{MHz unless} \\ \textbf{otherwise noted}; \ \textbf{T}_{A} = \textbf{T}_{MIN} \ to \ \textbf{T}_{MAX}, \ unless \ otherwise \ noted.) \end{array}$

| Parameter                           | B Version <sup>1</sup> | Units    | Test Conditions/Comments                             |

|-------------------------------------|------------------------|----------|------------------------------------------------------|

| CONVERSION RATE                     |                        |          | See Interface Section                                |

| Conversion Time                     | 2                      | μs typ   |                                                      |

| Track/Hold Acquisition Time         | TBD                    | ns max   | Full-Scale step input                                |

|                                     | TBD                    | ns max   | Sine wave input <= 30 KHz                            |

| Throughput Rate                     | 3.4                    | KSPS max | Standard mode 100 kHz                                |

|                                     | 13                     | KSPS max | Fast Mode 400 kHz                                    |

|                                     | 79                     | KSPS max | High-Speed Mode 3.4 MHz                              |

| POWER REQUIREMENTS                  |                        |          |                                                      |

| $ m V_{DD}$                         | 2.7/5.5 V              | min/max  |                                                      |

| ${ m I}_{ m DD}$                    |                        |          | Digital Inputs = $0 \text{ V or V}_{DD}$             |

| Peak Current                        | TBD                    | mA max   | Peak Current during conversion                       |

| Power Down Mode, Interface Inactive | 0.2/0.6                | μA max   | $V_{DD} = 3 \text{ V/5 V}.$                          |

| Interface Active                    | 0.05/0.2               | mA max   | $V_{\rm DD}$ = 3 V/5 V 400 kHz SCL.                  |

|                                     | 0.3/0.8                | mA max   | $V_{\rm DD}$ = 3 V/5 V 3.4 MHz SCL.                  |

|                                     |                        |          |                                                      |

| Operating, Interface Inactive       | 0.06/0.15              | mA max   | $V_{\rm DD} = 3 \text{ V/5 V } 400 \text{ kHz SCL}.$ |

| <u>-</u>                            | 0.3/0.6                | mA max   | $V_{\rm DD} = 3 \text{ V/5 V } 3.4 \text{ MHz SCL}.$ |

| Interface Active                    | 0.15/0.35              | mA max   | $V_{\rm DD} = 3 \text{ V/5 V } 400 \text{ kHz SCL}.$ |

|                                     | 0.6/1.4                | mA max   | $V_{DD} = 3 \text{ V/5 V } 3.4 \text{ MHz SCL}.$     |

#### NOTES

Specifications subject to change without notice.

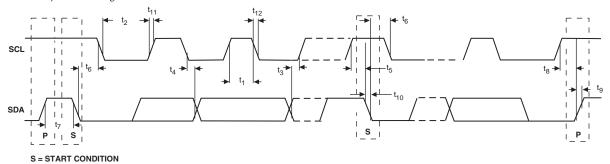

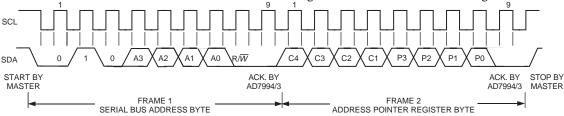

P = STOP CONDITION

Figure 1. Two-Wire Serial Interface Timing Diagram

$\textbf{I}^{2}\textbf{C} \quad \textbf{TIMING} \quad \textbf{SPECIFICATIONS}^{1} \quad \substack{(V_{DD} = +2.7 \text{ V to } +5.5 \text{ V, unless otherwise noted }; \text{ REF}_{IN} = 2.5 \text{ V; unless otherwise noted; } \\ \textbf{T}_{MIN} \text{ to } \textbf{T}_{MAX}, \quad \text{unless otherwise noted...}$

| Parameter                     | Conditions                          | AD7994/A<br>Limit at T <sub>N</sub><br>MIN |     | Unit | Description                           |

|-------------------------------|-------------------------------------|--------------------------------------------|-----|------|---------------------------------------|

| f <sub>SCL</sub> <sup>2</sup> | Standard Mode                       |                                            | 100 | kHz  | Serial Clock Frequency                |

|                               | Fast Mode                           |                                            | 400 | kHz  |                                       |

|                               | High-Speed Mode, $C_B = 100pF$ max  |                                            | 3.4 | MHz  |                                       |

|                               | High-Speed Mode, $C_B = 400 pF max$ |                                            | 1.7 | MHz  |                                       |

| $\overline{t_1}$              | Standard Mode                       | 4                                          |     | μs   | t <sub>HIGH</sub> , SCL High Time     |

|                               | Fast Mode                           | 0.6                                        |     | μs   |                                       |

|                               | High-Speed Mode, $C_B = 100pF$ max  | 60                                         |     | ns   |                                       |

|                               | High-Speed Mode, $C_B = 400pF$ max  | 120                                        |     | ns   |                                       |

| $\overline{t_2}$              | Standard Mode                       | 4.7                                        |     | μs   | t <sub>LOW</sub> , SCL Low Time       |

|                               | Fast Mode                           | 1.3                                        |     | μs   |                                       |

|                               | High-Speed Mode, $C_B = 100pF$ max  | 160                                        |     | ns   |                                       |

|                               | High-Speed Mode, $C_B = 400 pF max$ | 320                                        |     | ns   |                                       |

| $\overline{t_3}$              | Standard Mode                       | 250                                        | -   | ns   | t <sub>SU;DAT</sub> , Data Setup Time |

|                               | Fast Mode                           | 100                                        | -   | ns   |                                       |

|                               | High-Speed Mode                     | 10                                         | -   | ns   |                                       |

<sup>&</sup>lt;sup>1</sup>Temperature ranges as follows: B Version: -40°C to +85°C.

<sup>&</sup>lt;sup>2</sup>See Terminology.

<sup>&</sup>lt;sup>3</sup>Sample tested @ +25°C to ensure compliance.

<sup>&</sup>lt;sup>4</sup>See POWER VERSUS THROUGHPUT RATE section.

# AD7994/AD7993

# $\underline{I^2C\ TIMING\ SPECIFICATIONS^1\ (\texttt{Continued.})}$

|                       |                                             | AD7994/Al               | D7993                             |      |                                                         |

|-----------------------|---------------------------------------------|-------------------------|-----------------------------------|------|---------------------------------------------------------|

|                       |                                             | Limit at T <sub>M</sub> | $_{\rm IN}$ , ${\rm T}_{\rm MAX}$ |      |                                                         |

| Parameter             | Conditions                                  | MIN                     | MAX                               | Unit | Description                                             |

| $\overline{t_4}$      | Standard Mode                               | 0                       | 3.45                              | μs   | t <sub>HD;DAT</sub> , Data Hold Time                    |

| -                     | Fast Mode                                   | 0                       | 0.9                               | μs   | ,                                                       |

|                       | High-Speed Mode, C <sub>B</sub> = 100pF max | 0                       | 70                                | ns   |                                                         |

|                       | High-Speed Mode, $C_B = 400 pF max$         |                         | 150                               | ns   |                                                         |

| t <sub>5</sub>        | Standard Mode                               | 4.7                     |                                   | μs   | t <sub>SU;STA</sub> , Set-up Time for a repeated START  |

|                       | Fast Mode                                   | 0.6                     |                                   | μs   | Condition                                               |

|                       | High-Speed Mode                             | 160                     |                                   | ns   |                                                         |

| $\overline{t_6}$      | Standard Mode                               | 4                       |                                   | μs   | t <sub>HD;STA</sub> , Hold Time (repeated) START        |

| · ·                   | Fast Mode                                   | 0.6                     |                                   | μs   | Condition                                               |

|                       | High-Speed Mode                             | 160                     |                                   | ns   |                                                         |

| $\overline{t_7}$      | Standard Mode                               | 4.7                     |                                   | μs   | t <sub>BUF</sub> , Bus Free Time Between a STOP and a   |

| •                     | Fast Mode                                   | 1.3                     |                                   | μs   | START Condition.                                        |

|                       | Standard Mode                               | 4                       |                                   | μs   | t <sub>SU;STO</sub> , Set-up Time for STOP Condition    |

| · ·                   | Fast Mode                                   | 0.6                     |                                   | μs   | 20,010                                                  |

|                       | High-Speed Mode                             | 160                     |                                   | ns   |                                                         |

| $\overline{t_9}$      | Standard Mode                               | _                       | 1000                              | ns   | t <sub>RDA</sub> , Rise time of SDA signal              |

|                       | Fast Mode                                   | $20 + 0.1C_{B}$         | 300                               | ns   |                                                         |

|                       | High-Speed Mode, C <sub>B</sub> = 100pF max |                         | 80                                | ns   |                                                         |

|                       | High-Speed Mode, $C_B = 400 pF max$         |                         | 160                               | ns   |                                                         |

| t <sub>10</sub>       | Standard Mode                               | -                       | 300                               | ns   | t <sub>FDA</sub> , Fall time of SDA signal              |

|                       | Fast Mode                                   | $20 + 0.1C_{B}$         | 300                               | ns   |                                                         |

|                       | High-Speed Mode, C <sub>B</sub> = 100pF max | 10                      | 80                                | ns   |                                                         |

|                       | High-Speed Mode, $C_B = 400pF$ max          |                         | 160                               | ns   |                                                         |

| t <sub>11</sub>       | Standard Mode                               | _                       | 1000                              | ns   | t <sub>RCL</sub> , Rise time of SCL signal              |

|                       | Fast Mode                                   | $20 + 0.1C_{B}$         | 300                               | ns   |                                                         |

|                       | High-Speed Mode, C <sub>B</sub> = 100pF max | 10                      | 40                                | ns   |                                                         |

|                       | High-Speed Mode, $C_B = 400 pF max$         |                         | 80                                | ns   |                                                         |

| $\overline{t_{11A}}$  | Standard Mode                               | -                       | 1000                              | ns   | t <sub>RCL1</sub> , Rise time of SCL signal after a re- |

|                       | Fast Mode                                   | $20 + 0.1C_{B}$         | 300                               | ns   | peated START Condition and after an                     |

|                       | High-Speed Mode, $C_B = 100pF$ max          |                         | 80                                | ns   | Acknowledge bit.                                        |

|                       | High-Speed Mode, $C_B = 400 pF max$         | 20                      | 160                               | ns   | _                                                       |

| $\overline{t_{12}}$   | Standard Mode                               | _                       | 300                               | ns   | t <sub>FCL</sub> , Fall Time of SCL signal              |

|                       | Fast Mode                                   | $20 + 0.1C_{B}$         | 300                               | ns   | 132                                                     |

|                       | High-Speed Mode, C <sub>B</sub> = 100pF max | _                       | 40                                | ns   |                                                         |

|                       | High-Speed Mode, C <sub>B</sub> = 400pF max |                         | 80                                | ns   |                                                         |

| $t_{SP}^4$            | Fast Mode                                   | 0                       | 50                                | ns   | Pulsewidth of Spike Suppressed.                         |

| ~-                    | High-Speed Mode                             | 0                       | 10                                | ns   |                                                         |

| t <sub>POWER-UP</sub> |                                             |                         | 1                                 | μs   | Power-up Time                                           |

|                       |                                             |                         |                                   | ı .  | <u> </u>                                                |

#### NOTES

Specifications subject to change without notice.

-6- REV. PrF

<sup>&</sup>lt;sup>1</sup>See Figure 1. C<sub>B</sub> refers to the capacitance load on the bus line. Hs-Mode timing specifications apply to the AD7994-1/AD7993-1 only. Standard and Fast Mode timing specifications apply to both the AD7994-0/AD7993-0 and the AD7994-1/AD7993-1.

<sup>&</sup>lt;sup>2</sup>The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate but has a negative effect on EMC behavior of the part.

<sup>&</sup>lt;sup>4</sup>Input filtering on both the SCL and SDA inputs suppress noise spikes that are less than 50ns or 10ns for Fast Mode or High-Speed mode respectivley.

# AD7994/AD7993

#### ABSOLUTE MAXIMUM RATINGS1

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

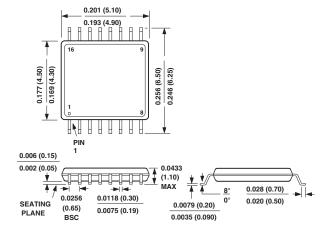

-0.3~V to 7~VV<sub>DD</sub> to GND -0.3 V to  $V_{\rm DD}$  + 0.3 V Analog Input Voltage to GND Reference Input Voltage to GND  $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ -0.3 V to 7 V Digital Input Voltage to GND Digital Output Voltage to GND -0.3 V to  $V_{DD}$  + 0.3 VInput Current to Any Pin Except Supplies<sup>2</sup> ±10 mA Operating Temperature Range Commercial (B Version) -40°C to +85°C Storage Temperature Range -65°C to +150°C

| Junction Temperature                | +150°C            |

|-------------------------------------|-------------------|

| 16-ld TSSOP Package                 |                   |

| $\theta_{IA}$ Thermal Impedance     | 150.4°C/W (TSSOP) |

| $\theta_{\rm IC}$ Thermal Impedance | 27.6°C/W (TSSOP)  |

| Lead Temperature, Soldering         |                   |

| Vapor Phase (60 secs)               | +215°C            |

| Infared (15 secs)                   | +220°C            |

#### NOTES

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range                  | Linearity Error <sup>2</sup> ( | max) Package Option <sup>3</sup> |  |

|--------------------|------------------------------------|--------------------------------|----------------------------------|--|

| AD7994BRU-0        | -40°C to +85°C                     | ±1 LSB                         | RU-16                            |  |

| AD7994BRU-1        | $-40^{\circ}$ C to $+85^{\circ}$ C | ±1 LSB                         | RU-16                            |  |

| AD7993BRU-0        | $-40^{\circ}$ C to $+85^{\circ}$ C | ±1 LSB                         | RU-16                            |  |

| AD7993BRU-1        | $-40^{\circ}$ C to $+85^{\circ}$ C | ±1 LSB                         | RU-16                            |  |

|                    |                                    |                                |                                  |  |

#### NOTES

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7994/AD7993 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. PrF -7-

<sup>&</sup>lt;sup>2</sup>Transient currents of up to 100 mA will not cause SCR latch up.

<sup>&</sup>lt;sup>1</sup> The AD7994-0/AD7993-0 supports Standard and Fast I<sup>2</sup>C interface modes. The AD7994-1/AD7993-1 supports Standard, Fast and Highspeed I<sup>2</sup>C Interface Modes.

<sup>&</sup>lt;sup>2</sup>Linearity error here refers to Integral Nonlinearity

$<sup>{}^{3}</sup>RU = TSSOP.$

# AD7994/AD7993

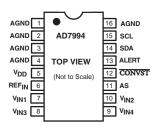

#### PIN FUNCTION DESCRIPTION

| Pin<br>Mnemonic   | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND              | Analog Ground. Ground reference point for all circuitry on the AD7994/AD7993. All analog input signals should be referred to this GND voltage.                                                                                                                                                                                                                                                                                      |

| $V_{\mathrm{DD}}$ | Power Supply Input. The $V_{\rm DD}$ range for the AD7994/AD7993 is from +2.7V to +5.5V.                                                                                                                                                                                                                                                                                                                                            |

| $REF_{IN}$        | Voltage Reference Input. The External Reference for the AD7994/AD7993 should 0.1 $\mu F$ capacitor should be placed between the REF <sub>IN</sub> pin and AGND.                                                                                                                                                                                                                                                                     |

| $V_{IN}1$         | Analog Input 1. Single-ended analog input channel. The input range is 0V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                     |

| $V_{IN}3$         | Analog Input 3. Single-ended analog input channel. The input range is 0V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                     |

| $V_{IN}4$         | Analog Input 4. Single-ended analog input channel. The input range is 0V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                     |

| $V_{IN}2$         | Analog Input 2. Single-ended analog input channel. The input range is 0V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                     |

| AS                | Logic Input. Address Select Input which selects one of three I <sup>2</sup> C addresses for the AD7994/AD7993 as shown in Table I.                                                                                                                                                                                                                                                                                                  |

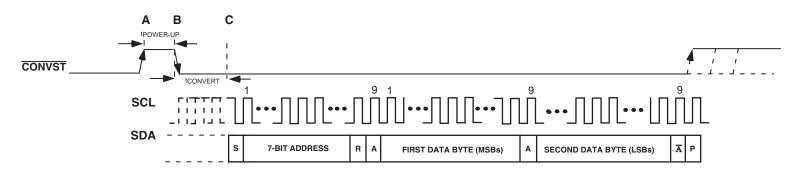

| CONVST            | Logic Input Signal. Convert Start Signal. This is an edge triggered logic input. The rising edge of this signal powers up the part. The power up time for the part is 1µs. The falling edge of CONVST places the track/hold into hold mode and initiates a conversion. A power up time of at least 1µs must be allowed for the CONVST high pulse, otherwise the conversion result will be invalid. (See Modes of Operation Section) |

| ALERT/BUSY        | Digital Output, selectable as an ALERT or BUSY output function. When configured as an ALERT output, this pin acts as an Out of Range Indicator, and if enabled becomes active when the conversion result violates the DATA <sub>HIGH</sub> or DATA <sub>LOW</sub> values. See Limit Registers section. When configured as a BUSY output, this pin becomes active when a conversion is in progress.                                  |

| SDA               | Digital I/O. Serial Bus Bi-directional Data. Open-drain output. External pull-up resistor required.                                                                                                                                                                                                                                                                                                                                 |

| SCL               | Digital Input. Serial Bus Clock. External pull-up resistor required.                                                                                                                                                                                                                                                                                                                                                                |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### AD7994/AD7993 PIN CONFIGURATION TSSOP

-8- REV. PrF

Table I. I<sup>2</sup>C Address Selection

| Part Number           | AS Pin   | I <sup>2</sup> C Address |

|-----------------------|----------|--------------------------|

| AD7993-0              | GND      | 010 0001                 |

| AD7993-0              | $V_{DD}$ | 010 0010                 |

| AD7993-1              | GND      | 010 0011                 |

| AD7993-1              | $V_{DD}$ | 010 0100                 |

| AD7993-X <sup>1</sup> | Float    | 010 0000                 |

### Note:-

<sup>1.</sup> If the AS pin is left floating on any of the AD7993 parts the device address will be 010 0000

| Part Number           | AS Pin   | I <sup>2</sup> C Address |

|-----------------------|----------|--------------------------|

| AD7994-0              | GND      | 010 0001                 |

| AD7994-0              | $V_{DD}$ | 010 0010                 |

| AD7994-1              | GND      | 010 0011                 |

| AD7994-1              | $V_{DD}$ | 010 0100                 |

| AD7994-X <sup>1</sup> | Float    | 010 0000                 |

REV. PrF -9-

Note :-  $^{1.}$  If the AS pin is left floating on any of the AD7994 parts the device address will be 010 0000

# AD7994/AD7993

#### **TERMINOLOGY**

#### Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02 N + 1.76) dB

Thus for a 12-bit converter, this is 74 dB

#### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the rms sum of harmonics to the fundamental. For the AD7994/AD7993, it is defined as:

THD (dB) = 20 log

$$\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

#### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_{\rm S}/2$  and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it will be a noise peak.

#### Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products at sum and difference frequencies of mfa  $\pm$  nfb where m, n = 0, 1, 2, 3, etc. Intermodulation distortion terms are those for which neither m nor n are equal to zero. For example, the second order terms include (fa + fb) and (fa - fb), while the third order terms include (2fa + fb), (2fa - fb), (fa + 2fb) and (fa - 2fb).

The AD7994/AD7993 is tested using the CCIF standard where two input frequencies near the top end of the input bandwidth are used. In this case, the second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the sum of the fundamentals expressed in dBs.

#### Channel-to-Channel Isolation

Channel-to-Channel Isolation is a measure of the level of crosstalk between channels. It is measured by applying a fullscale TBD kHz sine wave signal to the nonselected input channels and determining how much the TBD kHz signal is attenuated in the selected channel. This figure is given worse case across all channels.

#### Aperture Delay

This is the measured interval between the leading edge of the sampling clock and the point at which the ADC actually takes the sample.

#### Aperture Jitter

This is the sample-to-sample variation in the effective point in time at which the sample is taken.

#### Full Power Bandwidth

The Full Power Bandwidth of an ADC is that input frequency at which the amplitude of the reconstructed Fundamental is reduced by 0.1 dB or 3 dB for a full-scale input

#### PSRR (Power Supply Rejection)

The power supply rejection ratio is defined as the ratio of the power in the ADC output at full-scale frequency, f, to the power of a 200 mV p-p sine wave applied to the ADC  $V_{\rm DD}$  supply of frequency  $f_{\rm s}$ .

$$PSRR (dB) = 10 log (Pf/Pfs)$$

Pf is the power at frequency f in the ADC output; Pfs is the power at frequency fs coupled into the ADC  $V_{DD}$  supply.

#### Integral Nonlinearity

This is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1 LSB below the first code transition, and full scale, a point 1 LSB above the last code transition.

#### Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### Offset Error

This is the deviation of the first code transition (00 . . . 000) to (00 . . . 001) from the ideal, i.e AGND + 1LSB Offset Error Match

This is the difference in offset error between any two channels.

#### Gain Error

This is the deviation of the last code transition (111 . . . 110) to (111 . . . 111) from the ideal (i.e.,  $REF_{IN}$  – 1 LSB) after the offset error has been adjusted out.

#### Gain Error Match

This is the difference in Gain error between any two channels.

-10- REV. PrF

# AD7994/AD7993 TYPICAL PERFORMANCE CURVES TPC 1 shows a typical FFT plot for the AD7994 at TBD kSPS sample rate and TBD kHz input frequency. TPC 2. AD7993 Dynamic Perfor-TPC 3. PSRR vs Supply Ripple Fre-TPC 1. AD7994 Dynamic Performance at TBD ksps. quency. mance at TBD ksps. TPC 4. AD7994 SINAD vs Analog TPC 5. AD7994 Typical INL $V_{DD}$ = TPC 6. AD7994 Typical DNL $V_{DD}$ = Input Frequency for Various Sup-5V. ply Voltages at TBD ksps. TPC 9. AD7994 Change in INLvs

TPC 8. AD7994 Typical DNL  $V_{DD}$  =

Reference Voltage  $V_{DD} = 5V$ .

REV. PrF -11-

3V.

TPC 7. AD7994 Typical INL  $V_{DD}$  =

3V.

# AD7994/AD7993

| TPC 10. AD7994 Change in DNL vs<br>Reference Voltage. | TPC 11. AD7994 Shutdown Current vs Supply Voltage, -40 , 25 and 85 °C. | TPC 12. AD7994 Supply Current vs ${}^{2}C$ Bus Rate for $V_{DD}$ = 3V and 5V. |

|-------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|                                                       |                                                                        |                                                                               |

|                                                       |                                                                        |                                                                               |

|                                                       |                                                                        |                                                                               |

| TPC 13. AD7994 Supply Current                         | TPC 14. AD7994 ENOB vs Refer-                                          |                                                                               |

| vs Supply Voltage for Various<br>Temperatures.        | ence Voltage, $V_{DD} = 3V$ and $V_{DD} = 5V$ .                        |                                                                               |

-12-REV. PrF

#### CIRCUIT INFORMATION

The AD7994/AD7993 are fast, low-power, 12-/10-bit, single supply, 4 Channel A/D converters respectively. The parts can be operated from a 2.7 V to 5.5 V supply.

The AD7994/AD7993 provide the user with a 4-channel multiplexer, an on-chip track/hold, A/D converter, an on-chip oscillator, internal data registers and an  $\rm I^2C$  compatible serial interface, all housed in a 16-lead TSSOP package, which offers the user considerable space saving advantages over alternative solutions. An external reference is required by the AD7994/AD7993, and this reference can be in the range of 1.2 V to  $\rm V_{DD}$ .

The AD7994/AD7993 will normally remain in a power-down state while not converting. When supplies are first applied the part will come up in a shutdown state. Power-up is intitiated prior to a conversion and the device returns to power-down upon completion of the conversion. Conversions can be initiated on the AD7994/AD7993 by either pulsing the CONVST signal, using an automatic cycling mode or using a mode where wake-up and conversion occur during the write function ( see modes of Operation section). On completion of a conversion the AD7994/AD7993 will enter shutdown mode again. This automatic shutdown feature allows power saving between conversions. This means any read or write operations across the I<sup>2</sup>C interface can occur while the device is in shut-down.

#### **CONVERTER OPERATION**

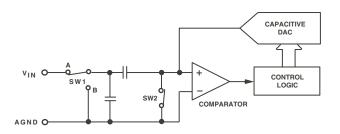

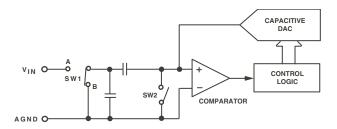

The AD7994/AD7993 are successive approximation analog-to-digital converters based around a capacitive DAC. Figures 2 and 3 show simplified schematics of the ADC during its acquisition and conversion phase respectively. Figure 2 shows the ADC during its acquisition phase. SW2 is closed and SW1 is in position A, the comparator is held in a balanced condition and the sampling capacitor acquires the signal on  $V_{\rm IN}X$ .

Figure 2. ADC Acquisition Phase

When the ADC starts a conversion, see Figure 3, SW2 will open and SW1 will move to position B causing the comparator to become unbalanced. The input is disconnected once the conversion begins. The Control Logic and the Capacitive DAC are used to add and subtract fixed amounts of charge from the sampling capacitor to bring the comparator back into a balanced condition. When the comparator is rebalanced the conversion is complete. The Control Logic generates the ADC output code. Figure 4 shows the ADC transfer function.

Figure 3. ADC Conversion Phase

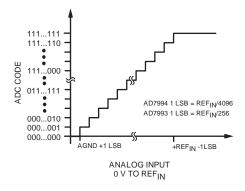

#### ADC TRANSFER FUNCTION

The output coding of the AD7994/AD7993 is straight binary. The designed code transitions occur at successive integer LSB values (i.e., 1LSB, 2LSBs, etc.). The LSB size for the AD7994 is = REF<sub>IN</sub>/4096 and REF<sub>IN</sub>/256 for the AD7993 . The ideal transfer characteristic for the AD7994/AD7993 is shown in Figure 4 below.

Figure 4. AD7994/AD7993 Transfer Characteristic

#### TYPICAL CONNECTION DIAGRAM

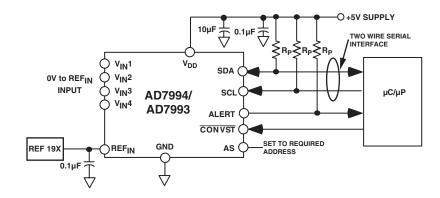

Figure 5 shows the typical connection diagram for the AD7994/AD7993. In Figure 5 the Address Select pin, AS, is tied to  $V_{\rm DD}$ , however AS can also be either tied to GND or left floating, allowing the user to select up to three AD7994/AD7993 devices on the same serial bus. An external reference must be applied to the AD7994/AD7993. This reference can be in the range of 1.2 V to  $V_{\rm DD}$ . A precision reference like the REF 19X family, ADR421, ADR03, ADR381 can be used to supply the Reference Voltage to the ADC.

SDA and SCL form the two-wire I<sup>2</sup>C/SMBus compatible interface. External Pull-up resistors should be added to the SDA and SCL bus lines.

The AD7994-0/AD7993-0 support Standard and Fast I<sup>2</sup>C Interface Modes. While the AD7994-1/AD7993-1 support Standard, Fast and High-speed I<sup>2</sup>C Interface Modes. Therefore if operating the AD7994/AD7993 in either Standard or Fast Mode, up to five AD7994/AD7993 devices (3 x AD7994-0/AD7993-0 and 2 x AD7994-1/AD7993-1 or 3 x AD7994-1/AD7993-1 and 2 x AD7994-0/AD7993-0) can be connected to the bus. When operating in Hs-Mode then up to three AD7994-1/AD7993-1 devices can be connected to the bus.

Wake-up from power-down prior to a conversion is approximately  $1\mu s$  while conversion time is approximately  $2\mu s$ . The AD7994/AD7993 enters power-down mode again after each conversion, this will be useful in applications where power consumption is of concern.

REV. PrF -13-

# AD7994/AD7993

Figure 5 AD7994/AD7993 Typical Connection Diagram

#### Analog Input

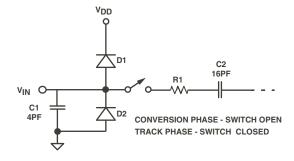

Figure 6 shows an equivalent circuit of the analog input sturcture of the AD7994/AD7993. The two diodes D1 and D2 provide ESD protection for the analog inputs. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 300mV. This will cause these diodes to become forward biased and start conducting current into the substrate. 10 mA is the maximum current these diodes can conduct without causing irreversable damage to the part.

The capacitor C1 in Figure 6 is typically about 4pF and can primarily be attributed to pin capacitance. The resistor R1 is a lumped component made up of the on resistance ( $R_{ON}$ ) of a switch(track and hold switch) and also includes the  $R_{ON}$  of the input multiplexer. The total resistance is typically about  $400\Omega$ . The capacitor C2 is the ADC sampling capacitor and has a capacitance of 30 pF typically.

For ac applications, removing high frequency components from the analog input signal is recommended by use of an RC band-pass filter on the relevant analog input pin. In applications where harmonic distortion and signal to noise ratio are critical the analog input should be driven from a low impedance source. Large source impedances will significantly affect the ac performance of the ADC. This may necessitate the use of an input buffer amplifier. The choice of the op amp will be a function of the particular application.

When no amplifier is used to drive the analog input the source impedance should be limited to low values. The

Figure 6. Equivalent Analog Input Circuit

maximum source impedance will depend on the amount of total harmonic distortion (THD) that can be tolerated. The THD will increase as the source impedance increases and performance will degrade. Figure 7 shows a graph of the Total Harmonic Distortion vs. analog input signal frequency for different source impedances when using a supply voltage of  $3V\pm10\%$  and  $5V\pm10\%$  and sampling at a rate of xkSPS. Figure 8 shows a graph of the total harmonic distortion versus analog input signal frequency for various supply voltages while sampling at xkSPS.

Figure 7. THD vs. Analog Input Frequency for Various Source Impedance for  $V_{DD}$ = 3V and 5V

Figure 8. THD vs. Analog Input Frequency, Fs = xkSPS

–14– REV. PrF

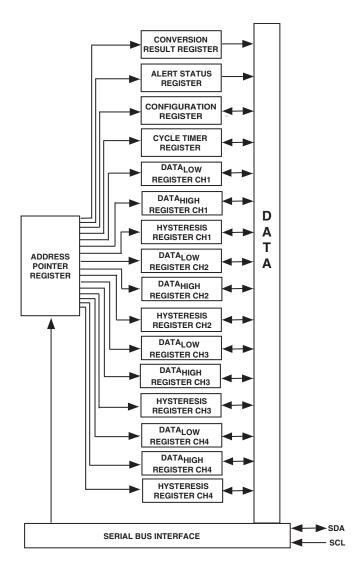

#### INTERNAL REGISTER STRUCTURE

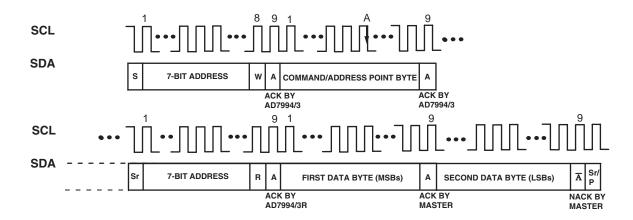

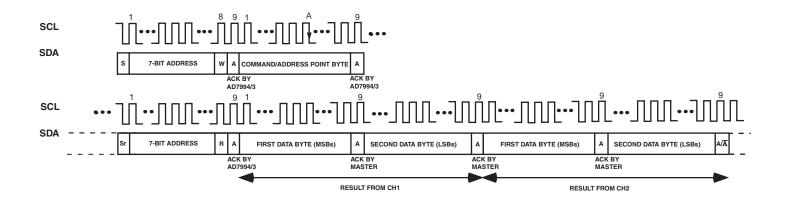

The AD7994/AD7993 contains seventeen internal registers, as shown in Figure 9, that are used to store conversion results, high and low conversion limits, and to configure and control the device. Sixteen are data registers and one is an address pointer register.

Figure 9. AD7994/AD7993 Register Structure

Each data register has an address which is pointed to by the Address Pointer register when communicating with it. The Conversion Result Register is the only data register that is read only.

#### ADDRESS POINTER REGISTER

The Address Pointer register itself does not have, nor does it require, an address, as it is the register to which the first data byte of every Write operation is written automatically. The Address Pointer Register is an 8-bit register in which the four LSBs are used as pointer bits to store an address that points to one of the data registers of the AD7994/AD7993, while the four MSBs are used as command bits when operating in Mode 2 (see Modes of Operation section). The first byte following each write address is the address of one of the data registers, which is stored in the Address Pointer Register, and selects the data register to which subsequent data bytes are written. Only the four LSBs of this register are used to select a data register. On Power up the Address Point register contains all 0's, pointing to the Conversion Result Register.

Table II. Address Pointer Register

| <b>C</b> 4 | С3 | C2 | C1 | P3 | P2       | P1     | P0 |

|------------|----|----|----|----|----------|--------|----|

| 0          | 0  | 0  | 0  | I  | Register | Select |    |

Table III. AD7994/AD7993 Register Addresses

| P3 | P2 | <b>P</b> 1 | <b>P</b> 0 | Registers                                 |

|----|----|------------|------------|-------------------------------------------|

| 0  | 0  | 0          | 0          | Conversion Result Register (Read)         |

| 0  | 0  | 0          | 1          | Alert Status Register (Read/Write)        |

| 0  | 0  | 1          | 0          | Configuration Register (Read/Write)       |

| 0  | 0  | 1          | 1          | Cycle Timer Register (Read/Write)         |

| 0  | 1  | 0          | 0          | DATA <sub>LOW</sub> Reg CH1 (Read/Write)  |

| 0  | 1  | 0          | 1          | DATA <sub>HIGH</sub> Reg CH1 (Read/Write) |

| 0  | 1  | 1          | 0          | Hysteresis Reg CH1 (Read/Write)           |

| 0  | 1  | 1          | 1          | DATA <sub>LOW</sub> Reg CH2 (Read/Write)  |

| 1  | 0  | 0          | 0          | DATA <sub>HIGH</sub> Reg CH2 (Read/Write) |

| 1  | 0  | 0          | 1          | Hysteresis Reg CH2 (Read/Write)           |

| 1  | 0  | 1          | 0          | DATA <sub>LOW</sub> Reg CH3 (Read/Write)  |

| 1  | 0  | 1          | 1          | DATA <sub>HIGH</sub> Reg CH3 (Read/Write) |

| 1  | 1  | 0          | 0          | Hysteresis Reg CH3 (Read/Write)           |

| 1  | 1  | 0          | 1          | DATA <sub>LOW</sub> Reg CH4 (Read/Write)  |

| 1  | 1  | 1          | 0          | DATA <sub>HIGH</sub> Reg CH4 (Read/Write) |

| 1  | 1  | 1          | 1          | Hysteresis Reg CH4 (Read/Write)           |

REV. PrF –15–

# AD7994/AD7993

### **CONFIGURATION REGISTER**

The Configuration Register is an 8-bit read/write register that is used to set the operating modes of the AD7994/AD7993. The bit functions of all 8 bits of the Configuration Register are outlined in Table IV.

Table IV. Configuration Register Bit Function Description

| <b>D</b> 7 | D6  | D5  | D4  | <b>D</b> 3 | D2       | D1         | D0                  |

|------------|-----|-----|-----|------------|----------|------------|---------------------|

| CH4        | CH3 | CH2 | CH1 | FLTR       | ALERT EN | BUSY/ALERT | ALERT/BUSY POLARITY |

| 0*         | 0*  | 0*  | 0*  | 1*         | 0*       | 0*         | 0*                  |

<sup>\*</sup>Default settings at Power-up

| Bit   | Mnemonic   | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D4 | CH4-CH1    | These four channel address bits select the analog input channel(s) to be converted on. A 1 in any of bits D7 to D4 selects a channel for conversion. If more than one channel bit is set to 1 then the AD7994/AD7993 will sequence through the selected channels, starting with the lowest channel. All unused channels should be set to zero. Table V shows how these four channel address bits are decoded. <i>Prior to initiating a conversion a channel(s) must be selected in the Configuration Register</i> . |

| D3    | FLTR       | The value written to this bit of the Control Register determines whether the filtering on SDA and SCL is enabled or to be bypassed. If this bit is a 1 then the filtering is enabled, if it is a 0, then the filtering is bypassed.                                                                                                                                                                                                                                                                                 |

| D2    | ALERT EN   | The hardware ALERT function is enabled if this bit is set to 1 and disabled if set to 0. This bit is used in conjunction with the BUSY/ALERT bit to determine if the ALERT/BUSY pin will act as an ALERT or a BUSY output. (See Table VI.)                                                                                                                                                                                                                                                                          |

| D1    | BUSY/ALERT | This bit is used in conjunction with the ALERT EN bit to determine if the ALERT/BUSY output, pin 13, will act as an ALERT or BUSY output (see TABLE V1), or if pin 13 is configured as an ALERT output pin, if it is to be reset. When reading the Configuration registerD1 will always be a 0 when D2 is a 1.                                                                                                                                                                                                      |

| D0    | BUSY/ALERT | This bit determines the active polarity of the ALERT/BUSY pin regardless of whether it is                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | POLARITY   | configured as an ALERT or BUSY output. It is active low if this bit is set to 0, and it is active high if set to 1.                                                                                                                                                                                                                                                                                                                                                                                                 |

-16- REV. PrF

Table V. Channel Selection

| <b>D</b> 7 | D6 | D5 | D4 | Analog Input Channel                                                        |

|------------|----|----|----|-----------------------------------------------------------------------------|

| 0          | 0  | 0  | 0  | No channel selected, see Address Pointer Byte, Mode 2                       |

| 0          | 0  | 0  | 1  | Convert on V <sub>IN</sub> 1                                                |

| 0          | 0  | 1  | 0  | Convert on V <sub>IN</sub> 2                                                |

| 0          | 0  | 1  | 1  | Sequence between $V_{\rm IN}1$ and $V_{\rm IN}2$                            |

| 0          | 1  | 0  | 0  | Convert on V <sub>IN</sub> 3                                                |

| 0          | 1  | 0  | 1  | Sequence between $V_{\rm IN}1$ and $V_{\rm IN}3$                            |

| 0          | 1  | 1  | 0  | Sequence between V <sub>IN</sub> 2 and V <sub>IN</sub> 3                    |

| 0          | 1  | 1  | 1  | Sequence between V <sub>IN</sub> 1, V <sub>IN</sub> 2 and V <sub>IN</sub> 3 |

| 1          | 0  | 0  | 0  | Convert on V <sub>IN</sub> 4                                                |

| 1          | 0  | 0  | 1  | Sequence between $V_{\rm IN}1$ and $V_{\rm IN}4$                            |

| 1          | 0  | 1  | 0  | Sequence between $V_{\rm IN}2$ and $V_{\rm IN}4$                            |

| 1          | 0  | 1  | 1  | Sequence between $V_{\rm IN}1,~V_{\rm IN}2$ and $V_{\rm IN}4$               |

| 1          | 1  | 0  | 0  | Sequence between $V_{\rm IN}3$ and $V_{\rm IN}4$                            |

| 1          | 1  | 0  | 1  | Sequence between $V_{\rm IN}1,~V_{\rm IN}3$ and $V_{\rm IN}4$               |

| l          | 1  | 1  | 0  | Sequence between $V_{\rm IN}2,~V_{\rm IN}3$ and $V_{\rm IN}4$               |

| l          | 1  | 1  | 1  | Sequence between $V_{\rm IN}1,~V_{\rm IN}2,~V_{\rm IN}3$ and $V_{\rm IN}4$  |

**Note 1:-** The AD7994/AD7994 converts on the selected channel in the Sequence in ascending order, starting with the lowest channel in the sequence.

Table VI. ALERT/BUSY Function

| D2 | D1 | ALERT/BUSY Pin Configuration                                                                                    |

|----|----|-----------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Pin does not provide any interrupt signal.                                                                      |

| 0  | 1  | Pin configured as a BUSY output.                                                                                |

| 1  | 0  | Pin configured as an ALERT output.                                                                              |

| 1  | 1  | Resets ALERT output pin, Alert_Flag bit in Conversion Result Reg, and entire Alert Status Reg ( if any active). |

If 1/1 is written to bits D2/D1 in the configuration Register to reset the ALERT pin, the Alert Flag bit and the Alert Status Register; the contents of the Configuration Register will read 1/0 for D2/D1 respectively if read back.

#### **CONVERSION RESULT REGISTER**

The Conversion Result Register is a 16-bit read-only register which stores the conversion result from the ADC in Straight Binary format. A Two Byte read is necessary to read data from this register. Table VIIa shows the contents of the first byte to be read while Table VIIb show the contents of the second byte to be read from AD7994/AD7993.

Table VIIa. Conversion Value Register (First Read)

| D15        | D14  | <b>D</b> 13 | D12               | <b>D</b> 11 | <b>D</b> 10 | D9 | <b>D</b> 8 |

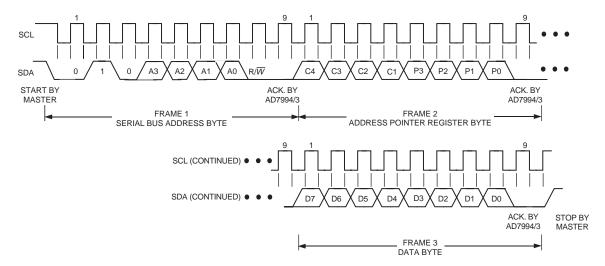

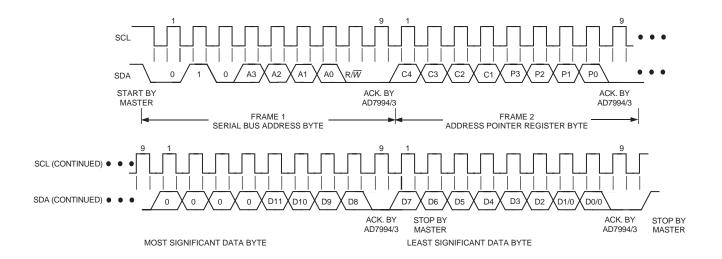

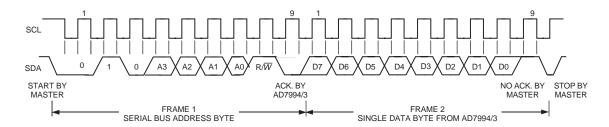

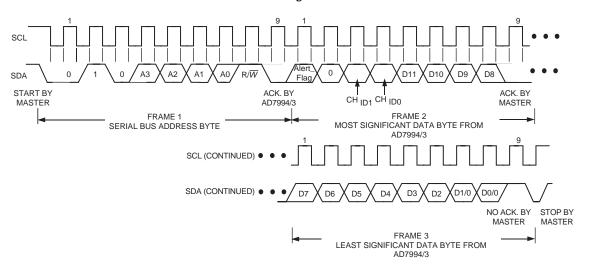

|------------|------|-------------|-------------------|-------------|-------------|----|------------|