### 1 MHz - 3 GHz VGA with 60dB Gain Control Range

ADL5330

### **Preliminary Technical Data**

#### **FEATURES**

Voltage-Controlled Amplifier/Attenuator Operating Frequency 1 MHz to 3 GHz Optimized for Controlling Output Power High Linearity: OIP3 31 dBm @ 900 MHz Output Noise Floor -150 dBm/Hz @ 900 MHz Fully-Balanced Differential Signal Path Differential Input at 50 Ω Wide Gain-Control Range: -34 dB to +22 dB @ 900 MHz Linear-in-dB Gain Control Function, 20 mV/dB Single Supply 4.75 – 6 V

#### **APPLICATIONS**

**Output Power Control for Wireless Infrastructure**

#### VPS2 VPS2 GATN VBT. VPS2 VPS2 VPS GAIN CONTRO INHI Input Continuously O/P OPH: RF I/P gm Stage Variable (TZ) RF to PA Attenuato INLO Stade OPLO BALUN BIAS & VREF IPBS OPBS COM2

Figure 1. Functional Block Diagram

#### **PRODUCT DESCRIPTION**

The ADL5330 is a high-performance voltage-controlled variablegain amplifier/attenuator, for use up to 3 GHz. The signal path is fully differential; the balanced structure minimizes distortion, and reduces the risk of spurious feed-forward at low gains and high frequencies due to substrate coupling. While operation between a balanced source and load is recommended, a single-sided input is internally converted to differential from. The input impedance is  $50-\Omega$  from **INHI** to **INLO**. The outputs will usually be coupled into a  $50-\Omega$  grounded load via a 1:1 balun. However, the output pins, **OPHI** and **OPLO**, may also be used separately, with some noise degradation. A single supply of 4.75 to 6 V is required.

With a 2140 MHz W-CDMA 3GPP forward path signal, the ADL5330 is capable of producing greater than -3 dBm output power while maintaining ACPR greater than 55 dB, and an output noise floor less than -144 dBm/Hz.

Three cascaded sections are used. The  $50-\Omega$  input system converts the applied voltage to a pair of differential currents with high linearity and good common rejection if driven by a single-sided source. The signal currents are then applied to a proprietary voltage-controlled attenuator, which provides precise definition of the overall gain, under the control of the Linear-in-dB interface. Pin **GAIN** accepts a voltage from 0 V at minimum gain to 1.4 V at full gain. The scaling factor is 20 mV/dB. Optional external control of the input-stage and/or output-stage biasing is provided using pins **IPBS** and **OPBS** respectively.

The output of the high-accuracy wideband attenuator is applied to a differential trans-impedance output stage. Higher output power is attainable at the lower operating frequencies by raising the supply voltage to 6 V. When powered-down by a logic LO input on the **ENBL** pin, the current consumption is < TBD  $\mu$ A.

The ADL5330 is available in a 24-lead (4 x 4mm) CSP package and is specified for operation from ambient temperatures of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Multiple Patents Pending

#### Rev. PrK

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.Tel: 781/329-4700World Wide Web Site: http://www.analog.comFax: 781/326-8703©2004 Analog Devices, Inc. All Rights Reserved

### ADL5330 SPECIFICATIONS

### Table 1. V<sub>S</sub> = 5 V; T<sub>A</sub> = 25°C; 800 MHz < f < 2.2GHz.1:1 balun at input and output for single-ended 50 $\Omega$ match

| Parameter                       | Conditions                                       | Min   | Тур  | Max | Unit   |

|---------------------------------|--------------------------------------------------|-------|------|-----|--------|

| General                         |                                                  |       |      |     |        |

| Usable Frequency Range          |                                                  | 0.001 |      | 3   | GHz    |

| Nominal Input Impedance         | via 1:1 Single-Sided to Differential Balun       |       | 50   |     | Ω      |

| Nominal Output Impedance        | via 1:1 Differential to Single-Sided Balun       |       | 50   |     | Ω      |

| 100 MHz                         |                                                  |       |      |     |        |

| Gain Control Span               | +/-3 dB Gain Law Conformance                     |       | 58   |     | dB     |

| Max Gain                        | $V_{GAIN} = 1.4 \text{ V}$                       |       | +23  |     | dB     |

| Min Gain                        | $V_{GAIN} = 0.1 \text{ V}$                       |       | -35  |     | dB     |

| Gain Control Slope              |                                                  |       | 21   |     | mV/dB  |

| Input Compression Point         | $V_{GAIN} = 1.3 V$                               |       | +2   |     | dBm    |

| Output Compression Point - P1dB | $V_{GAIN} = 1.3 V$                               |       | +22  |     | dBm    |

| Third-Order Intercept - OIP3    | $V_{GAIN} = 1.3 V$                               |       | +36  |     | dBm    |

| 900 MHz                         |                                                  |       |      |     |        |

| Gain Control Span               | +/-3 dB Gain Law Conformance                     |       | 52   |     | dB     |

| Max Gain                        | $V_{GAIN} = 1.4 \text{ V}$                       |       | 22   |     | dB     |

| Min Gain                        | $V_{GAIN} = 0.1 \text{ V}$                       |       | -34  |     | dB     |

| Gain Control Slope              |                                                  |       | 20   |     | mV/dB  |

| Input Compression Point         | $V_{GAIN} = 1.3 V$                               |       | +3   |     | dBm    |

| Output Compression Point - P1dB | $V_{GAIN} = 1.3 V$                               |       | +22  |     | dBm    |

| Third-Order Intercept - OIP3    | $V_{GAIN} = 1.3 V$                               |       | +31  |     | dBm    |

| Output Noise Floor              | 20 MHz Carrier Offset, $V_{GAIN} = 1.3 V$ ,      |       | -144 |     | dBm/Hz |

|                                 | Pout = $-2 \text{ dBm}$                          |       |      |     |        |

| 1900 MHz                        |                                                  |       |      |     |        |

| Gain Control Span               | +/-3 dB Gain Law Conformance                     |       | 47   |     | dB     |

| Max Gain                        | $V_{GAIN} = 1.4 \text{ V}$                       |       | 19   |     | dB     |

| Min Gain                        | $V_{GAIN} = 0.5 \text{ V}$                       |       | -27  |     | dB     |

| Gain Control Slope              |                                                  |       | 18   |     | mV/dB  |

| Input Compression Point         | $V_{GAIN} = 1.3 V$                               |       | +1   |     | dBm    |

| Output Compression Point - P1dB | $V_{GAIN} = 1.3 V$                               |       | +17  |     | dBm    |

| Third-Order Intercept - OIP3    | $V_{GAIN} = 1.3 V$                               |       | +24  |     | dBm    |

| Output Noise Floor              | 20 MHz Carrier Offset, $V_{GAIN} = 1.3 V$ ,      |       | -148 |     | dBm/Hz |

|                                 | Pout = $-7 \text{ dBm}$                          |       |      |     |        |

| 2200 MHz                        |                                                  |       |      |     |        |

| Gain Control Span               | +/-3 dB Gain Law Conformance                     |       | 48   |     | dB     |

| Max Gain                        | $V_{GAIN} = 1.4 \text{ V}$                       |       | 17   |     | dB     |

| Min Gain                        | $V_{GAIN} = 0.5 \text{ V}$                       |       | -31  |     | dB     |

| Gain Control Slope              |                                                  |       | 17   |     | mV/dB  |

| Input Compression Point         | $V_{GAIN} = 1.3 V$                               |       | +1   |     | dBm    |

| Output Compression Point - P1dB | $V_{GAIN} = 1.3 V$                               |       | +14  |     | dBm    |

| Third-Order Intercept - OIP3    | V <sub>GAIN</sub> = 1.3 V                        |       | +20  |     | dBm    |

| GAIN CONTROL INPUT              | Pin GAIN                                         | 0     |      | 1.4 | V      |

| Gain Control Voltage Range      | <b>D</b> :                                       | 0     |      | 1.4 |        |

| Incremental Input Resistance    | Pin GAIN to COM1                                 | TBD   | 500  |     | MΩ     |

| Full-Scale Response Time        | $V_{GN}$ 0-1.6V, to within 0.25 dB of final gain |       | 500  |     | ns     |

| POWER SUPPLIES                  | Pins VPS1, VPS2, COM1, COM2, ENBL                | 4 77  | _    | -   | V      |

| Voltage                         |                                                  | 4.75  | 5    | 6   | V      |

| Current, Nominal Active         | $V_{GN} = 0 \text{ V}$                           |       | TBD  |     | mA     |

|                                 | $V_{GN} = 1.4 \text{ V}$                         |       | 240  |     | mA     |

| Current, Disabled               | $\mathbf{ENBL} = \mathbf{LO}$                    |       | TBD  | TBD | μΑ     |

## **Preliminary Technical Data**

| Pin          | Name       | Description                                                                              |  |

|--------------|------------|------------------------------------------------------------------------------------------|--|

| 1,6          | VPS1       | Positive Supply for input stage. Nominally equal to 5 V                                  |  |

| 2,5          | COM1       | Common for input stage                                                                   |  |

| 3, 4         | INHI, INLO | Differential inputs                                                                      |  |

| 7            | VREF       | Voltage reference output of 1.5 volts                                                    |  |

| 8            | IPBS       | Input bias, normally no connection. This function is subject to change. PCB              |  |

|              |            | designs should include the possibility to connect a capacitor between Pin 8 and          |  |

|              |            | Pin 9.                                                                                   |  |

| 9            | OPBS       | Output bias, normally no connection. This function is subject to change. PCB             |  |

|              |            | designs should include the possibility to connect a capacitor between Pin 8 and          |  |

|              |            | Pin 9.                                                                                   |  |

| 10,11,12,14, | COM2       | Common for output stage                                                                  |  |

| 17           |            |                                                                                          |  |

| 13,18,19,20, | VPS2       | Positive Supply for output stage. Nominally equal to 5 V                                 |  |

| 21,22        |            |                                                                                          |  |

| 15           | OPLO       | Low side of differential output, bias to $V_P$ with RF chokes                            |  |

| 16           | OPHI       | High side of differential output, bias to V <sub>P</sub> with RF chokes                  |  |

| 23           | ENBL       | Device enable, apply logic high for normal operation. Enable Threshold = $1.6 \text{ V}$ |  |

| 24           | GAIN       | Gain-control voltage input. Nominal Range 0 to 1.4 V.                                    |  |

**Table 2. Pin Function Description**

ADL5330

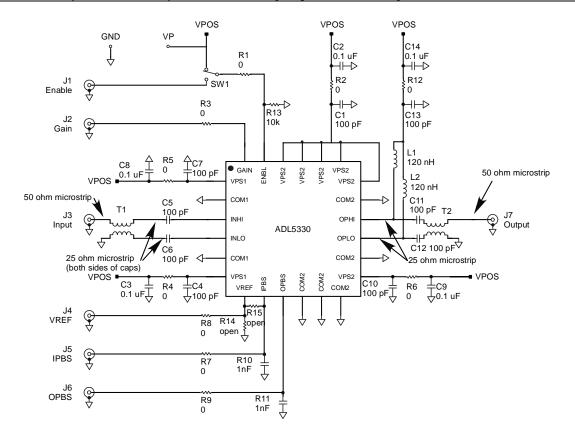

Figure 2. ADL5330 Evaluation Board Schematic

#### 20.00 40 30 15.00 20 10.00 10 5.00 Bb Gain - dB 0 0.00 Error -10 -5.00 Gain 900 MHz Gain 1900 MHz 2200 MHz -20 -10.00 Error 100 MHz Gain Error 900 MH -30 -15.00 Error 1900 Error 2200 MHz -40 -20.00 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 Vgain - Volts

# **Typical Performance Characteristics**

Figure 3. Gain and Gain Law Conformance vs. Vgain

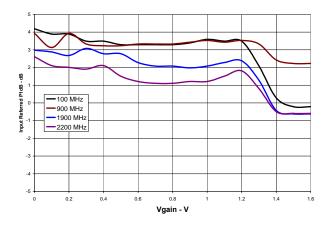

Figure 4. Input Referred Compression Point vs. Gain

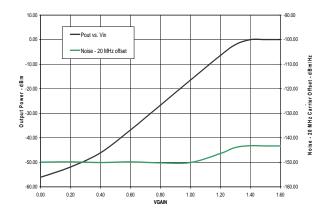

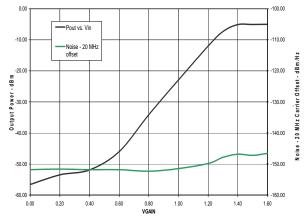

Figure 8. Pout and Noise Floor vs. Gain, 900 MHz. Pin = -21 dBm

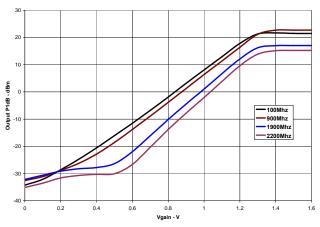

30 20 •100 MHz OIP3 10 900 MHz 1900 MHz 2200 MHz -10 -30 0.2 0.4 0.6 0.8 1.2 1.4

Vgain - V

Figure 5. OIP3 vs. Gain

50

40

Figure 7. Output Referred Compression Point vs. Gain

*Figure 8. Pout and Noise Floor vs. Gain 1.9 GHz. Pin = -22 dBm*

ADL5330

1.6

## **Preliminary Technical Data**

### ADL5330

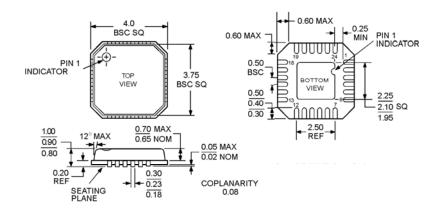

### **OUTLINE DIMENSIONS**

### 24-Lead Chip Scale Package [LFCSP] 4 mm x 4 mm Body

(CP-24)

Dimensions shown in millimeters