**AK7750**

# AKM

# Audio DSP with Built-in Hands-Free Phone Features

#### General Description

The AK7750 is a highly integrated Audio Digital Signal Processor with a stereo audio codec in one chip. The AK7750 combines an on-chip DSP and an ARM7 processor that can be used to create Echo Cancellation (EC) and Noise Cancellation (NC) functions. These functions make the AK7750 a perfect choice for hands-free phones that require suppressing acoustic echo and noise. Voice quality and noise suppression levels can be precisely adjusted by externally setting various parameters. Additionally, no external Flash, ROM, or RAM is required as memories for Echo and Noise Cancellation are integrated on-chip.

By using an external microprocessor to change algorithms, the AK7750 can be used in other audio applications including sound field enhancements like surround, volume control, parametric equalizer and speaker compensation. These functions are simplified by the AK7750 through the integration of 64K bit delay data RAM, a high-performance audio Codec with sample rates from 8 KHz ~ 48 KHz, and 8-channels of Digital Audio input / output.

What's more, the latest Surround Decoders can be also be implemented by using the certified algorithms from various technology partners.

Features

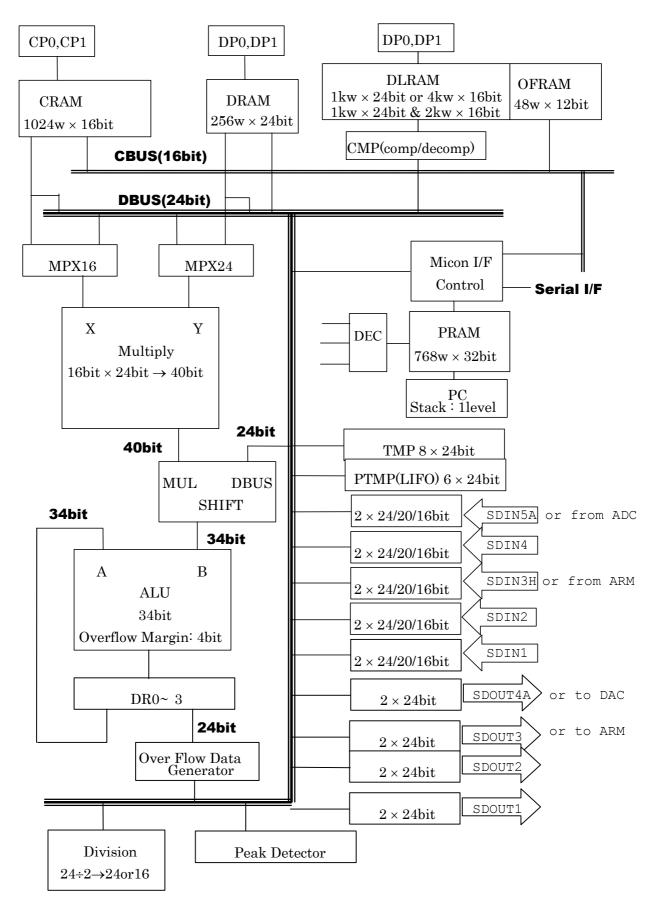

# [DSP Block]

- Data Word Length: 24 bit

- Machine Cycle: 27.1 ns (fastest) (768fs at 48 KHz)

- Number of Steps: 768 steps max. at fs = 48 KHz

- 4608 steps max. at fs = 8 KHz

- 192 steps max. at fs = 192 KHz

- Multiply: 24 x 16 -> 40 bit (enables double precision operation)

- Division: 24 / 24 -> 24 bit or 16 bit

- ALU: 34 bit arithmetic operation (overflow margin 4 bits) 24 bit arithmetic & logic operations

- Shift: 1,2,3,4,6,8,15 Bit Left Shift with indirect shift function 1,2,3,4,8,14,15 bit Right Shift with indirect shift function

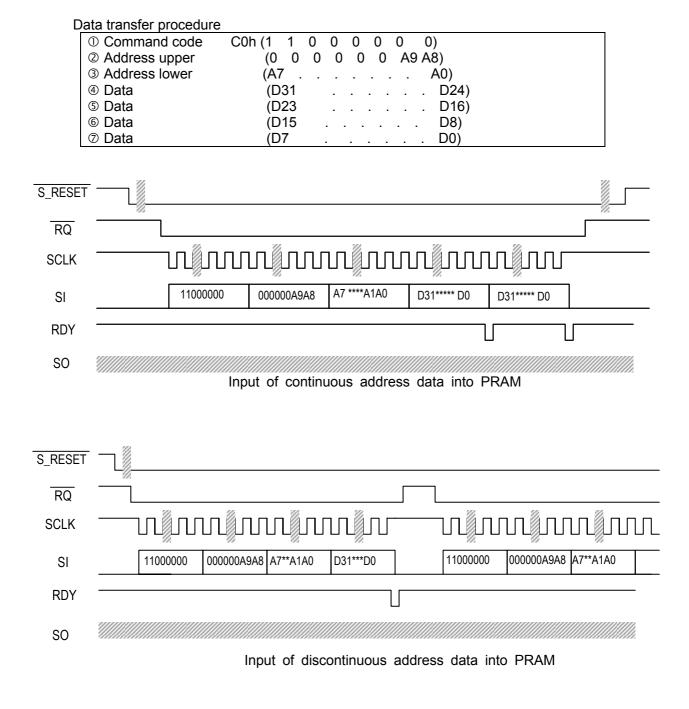

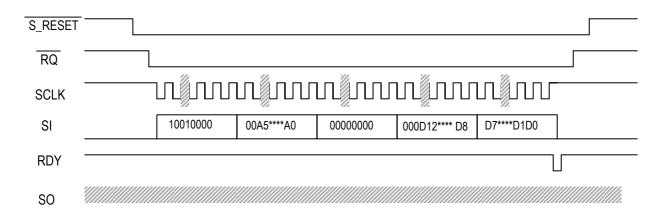

- Program RAM (PRAM): 768 words x 32 bit

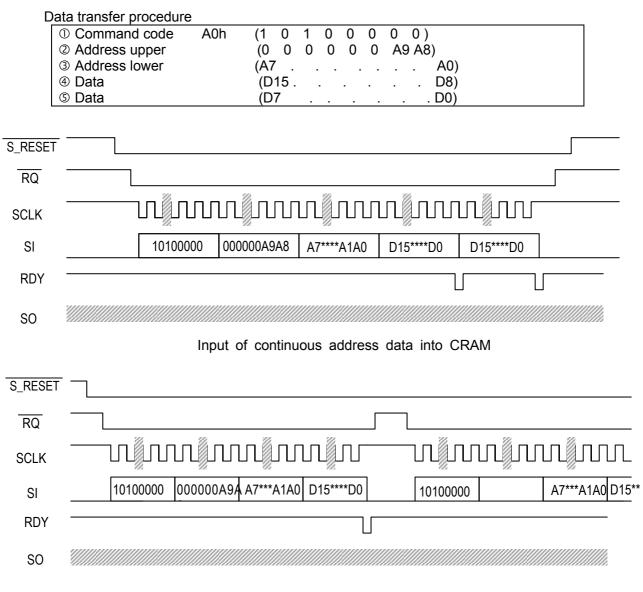

- Coefficient RAM (CRAM): 1024 words x 16 bit

- Data RAM (DRAM): 256 words x 24 bit

- Offset RAM (OFRAM): 48 words x 12 bit

- Delay RAM (DLRAM): 64K bits (following 3 types are selectable):

- 1K words 24 bit

- 1K words 24 bit & 2K words 16 bit (limited pointer capability)

- 4kword 16bit

- Data Compression/Expansion circuits for 16 bit data handling are integrated on-chip (Dynamic-range: 23 bit equivalent, S/N+D: 15 bit equivalent (FS)).

- In Hands-free mode, Delay RAM cannot be used.

- Registers: 34 bits x 4 (ACC) [for ALU]

- 24 bit x 8 (TMP) [for DBUS Interface]

- 24 bit x 6 stage stacks (PTMP) [for DBUS Interface]

- On-chip ARM7TDMI Processor:

1

[ADC Block]

- 24 Bit 2 Channels (fs: 8 KHz ~ 48 KHz)

- S/N+D: 91 dB (fs = 48 KHz)

- Dynamic Range & S/N: 98 dBA (fs = 48 KHz)

- On-chip DC offset canceling High Pass Filter

[DAC Block]

- 24 Bit 2 Channels

- S/N+D: 86 dB (fs = 48 KHz)

- Dynamic Range & S/N: 98 dBA (fs = 48 KHz)

[Input/Output Digital Interface]

- Serial Data Input 8 channels (10 channels with on-board codec.)

- Serial Data Output 6 channels (8 channels with on-board codec.)

- Microprocessor Interface: 1 set of inputs and outputs

[General]

- On-chip PLL

- On-chip EEPROM (AK6512C, AK6514C) Interface

- Single 3.3 V +/- 0.3 V Power Supply

- Operating Temperature Range: -40°C to +85°C

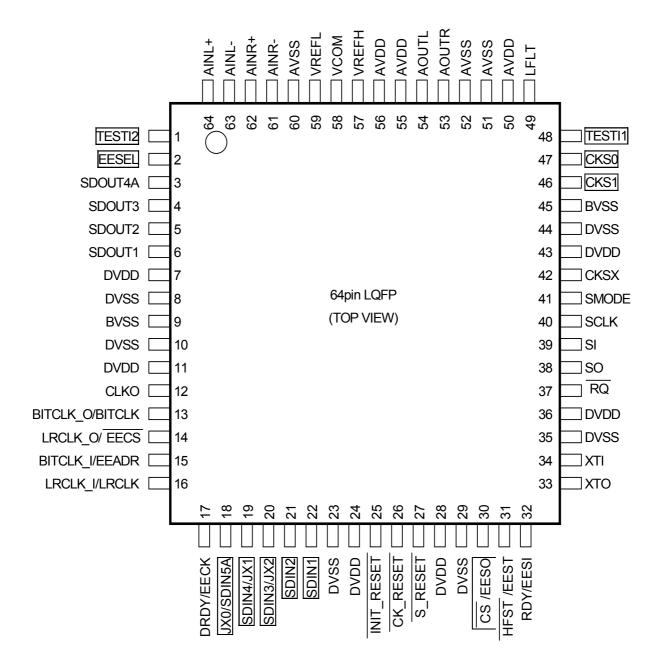

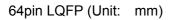

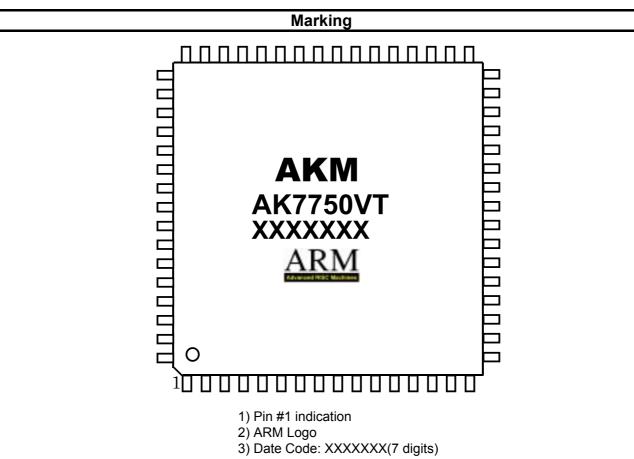

- 64-Pin LQFP

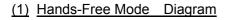

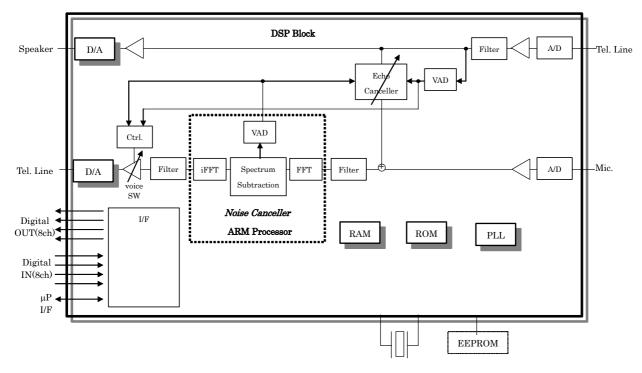

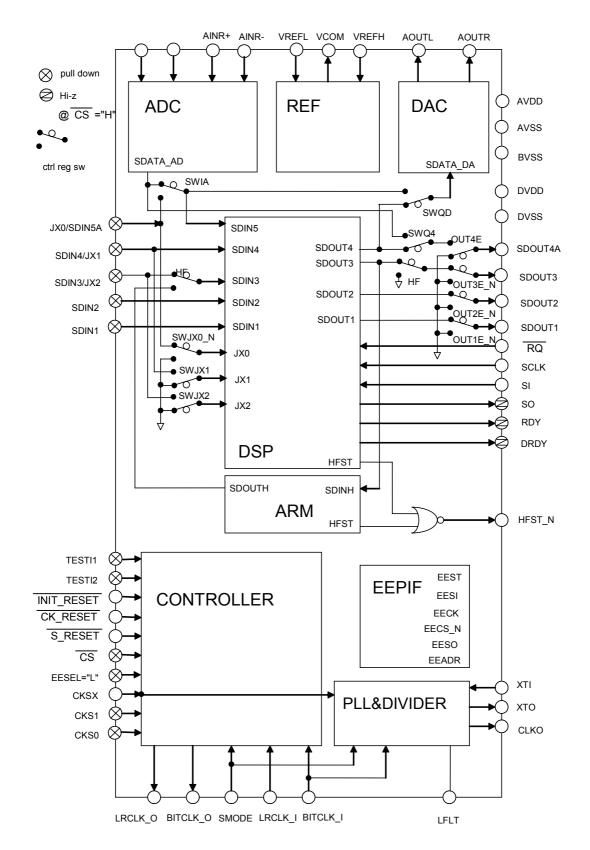

# Block Diagram

Block Diagram

# (2) Total Block Diagram

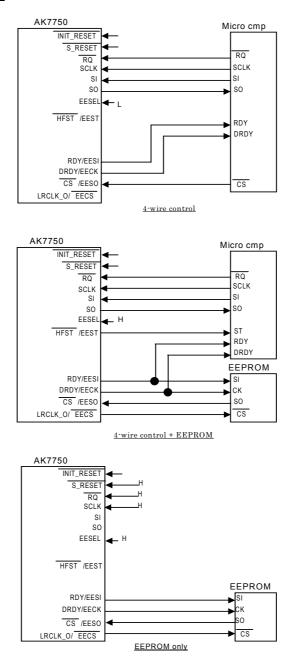

1) EESEL = " L "

The above shows a simplified AK 7750 block diagram. It does not necessarily show the circuit diagram.

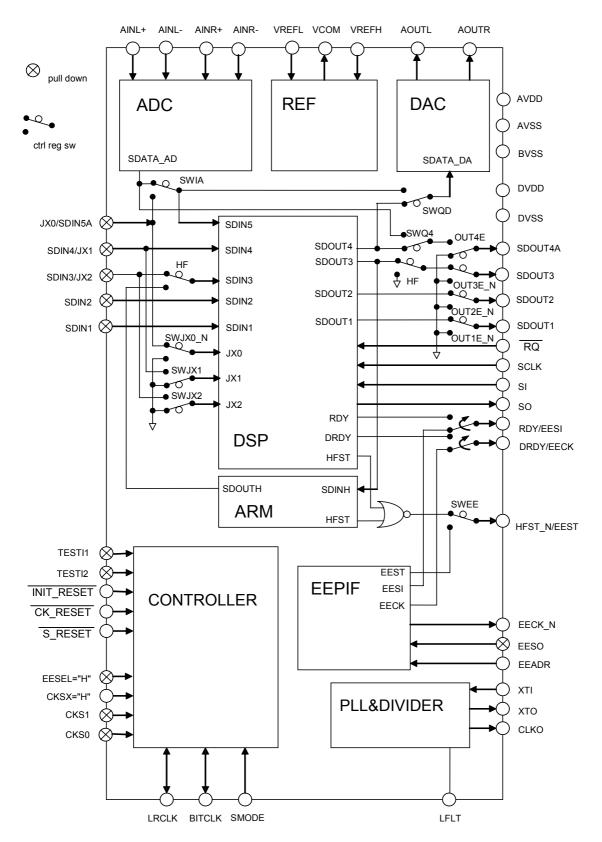

# 2) EESEL = " H "

The above shows a simplified AK 7750 block diagram. It does not necessarily show the circuit diagram.

#### (3) DSP Block Diagram

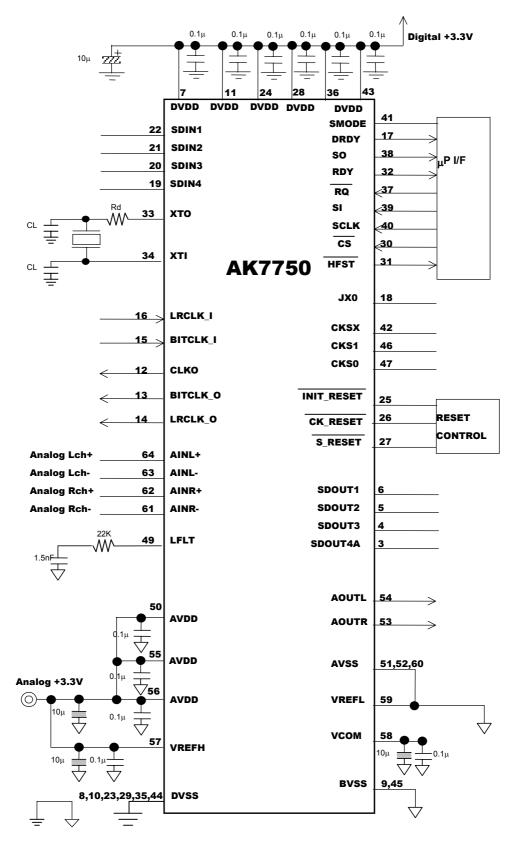

# Input/Output Pin Description

(1) Pin Assignment

Note) **\*\*\*** indicates *Pulled-down* pins ( xxx : pin name)

\*\*\* pins (\*\*\* is pin name) are pulled down to the digital ground of the device INTERNALLY. The words, *"pulled-down*" with italic type characters in the following "Pin Functional Description" are used to clarify this function.

7

# (3) Pin Functional Description

| Pin | Pin Name                | I/O | Function                                                                                                                                                                                                                       | Pin Classification            |

|-----|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| NO. |                         | "   |                                                                                                                                                                                                                                |                               |

| 1   | TESTI2                  | Ι   | Test pin (pulled-down). Connect to DVSS                                                                                                                                                                                        | Test                          |

| 2   | EESEL                   |     | Control mode select pin ( <i>pulled-down</i> )<br>EESEL="L": for general use<br>EESEL="H": program can be downloaded to the AKM's<br>EEPROMs, AK6512C, AK6514C.<br>EESEL pin must be fixed to either "L" or "H" level.         | Control                       |

| 3   | SDOUT4A                 |     | <ul> <li>DSP Serial Data Output pin</li> <li>- MSB-justified 24 Bit data is output.</li> <li>- ADC Data output, selected by Control Register setting.</li> </ul>                                                               | Digital<br>Serial data output |

| 4   | SDOUT3                  |     | <ul> <li>DSP Serial Data Output pin</li> <li>- MSB-justified 24 Bit data is output.</li> <li>- "L" is output during the hands-free operation.</li> </ul>                                                                       |                               |

| 5   | SDOUT2                  |     | DSP Serial Data Output pin<br>- MSB-justified 24 Bit data is output.                                                                                                                                                           |                               |

| 6   | SDOUT1                  | 0   | DSP Serial Data Output pin<br>- MSB-justified 24 Bit data is output.                                                                                                                                                           |                               |

| 7   | DVDD                    | 1   | Digital Power Supply pin 3.3 V (typ)                                                                                                                                                                                           | Digital Power Supply          |

| 8   | DVSS                    | 1   | Digital Ground pin 0 V                                                                                                                                                                                                         | Digital Power Supply          |

| 9   | BVSS                    | -   | Ground pin (silicon substrate potential)<br>Connect to AVSS.                                                                                                                                                                   | Analog Power Supply           |

| 10  | DVSS                    | -   | Digital Ground pin 0 V                                                                                                                                                                                                         | Digital Power Supply          |

| 11  | DVDD                    |     | Digital Power Supply pin 3.3 V (typ)                                                                                                                                                                                           | Digital Power Supply          |

| 12  | CLKO                    |     | Clock Output pin<br>Set by Control Register                                                                                                                                                                                    | Clock Output                  |

| 13  | BITCLK_O<br>(EESEL="L") |     | Serial Bit Clock Output pin<br>SMODE="H": 64fs clock is output during master mode<br>operation.<br>SMODE="L": BITCLK-I clock is output during slave mode<br>operation (except for DIF mode 5 and 6)                            |                               |

|     | BITCLK<br>(EESEL="H")   | I/O | Serial Bit Clock Input/Output pin<br>SMODE="H": 64fs clock is output during master mode<br>operation.<br>SMODE="L": 64fs clock is input during slave mode operation<br>(48fs clock can be output, except when using<br>CKSX=L) |                               |

| 14  | LRCLK_O<br>(EESEL="L")  | 0   | L/R Channel Select Output pin<br>SMODE="H": 1fs clock is output during master mode<br>operation.<br>SMODE="L": LRCLK-I clock is output during slave mode<br>operation (except for DIF mode 5 and 6).                           |                               |

|     | EECS<br>(EESEL="H")     |     | EEPROM Chip Select Output pin<br>Connect to CS pin of AK6512C/14C.                                                                                                                                                             | EEP                           |

| Pin       | Pin Name                 | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                       | Pin Classification                       |

|-----------|--------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| NO.<br>15 | BITCLK I                 | I   | Serial Bit Clock Input pin                                                                                                                                                                                                                                                                                                                                                                                     | Sytem Clock                              |

| 10        | (EESEL="L")              |     | SMODE="H": When master mode is used, connect this pin to<br>DVSS.<br>SMODE="L": 64fs clock is input during slave mode operation.<br>(48fs clock can be input except for CKSX="L").<br>BITCLK-I (64fs) can be used as master clock                                                                                                                                                                              |                                          |

|           |                          |     | (CKSX="L") during slave mode operation                                                                                                                                                                                                                                                                                                                                                                         |                                          |

|           | EEADR<br>(EESEL="H")     |     | EEP Address Select pin<br>AK6512C: used at EEADR="L".<br>AK6514C: read data starting at 0000h when EEADR="L".<br>Read data starting at 2000h when EEADR="H".                                                                                                                                                                                                                                                   | EEP                                      |

| 16        | LRCLK_I<br>(EESEL="L")   | I   | L/R Channel Select Input pin<br>SMODE="H": When master mode is used, connect this pin to<br>DVSS.<br>SMODE="L": 1fs clock is input during slave mode operation.                                                                                                                                                                                                                                                | System Clock                             |

|           | LRCLK<br>(EESEL="H")     | I/O | L/R Channel Select Input/Output pin<br>SMODE="H": 1fs clock is output during master mode operation<br>SMODE="L": 1fs clock is input during slave mode operation                                                                                                                                                                                                                                                | System Clock                             |

| 17        | DRDY<br>(EESEL="H")      | 0   | Output Data Ready pin (Hi-Z)<br>For microprocessor interface<br>Hi-Z state when CS ="H".                                                                                                                                                                                                                                                                                                                       | μC                                       |

|           | DRDY/EECK<br>(EESEL="H") | 0   | Output Data Ready pin for μC interface /<br>EEPROM Serial Data Output pin.<br>Connect this pin to SCK pin of AK6512C/14C.<br>After an EEPROM data read, (EEST transition from "L" to "H"),<br>this pin is automatically switched to DRDY pin.                                                                                                                                                                  | EEP/μC                                   |

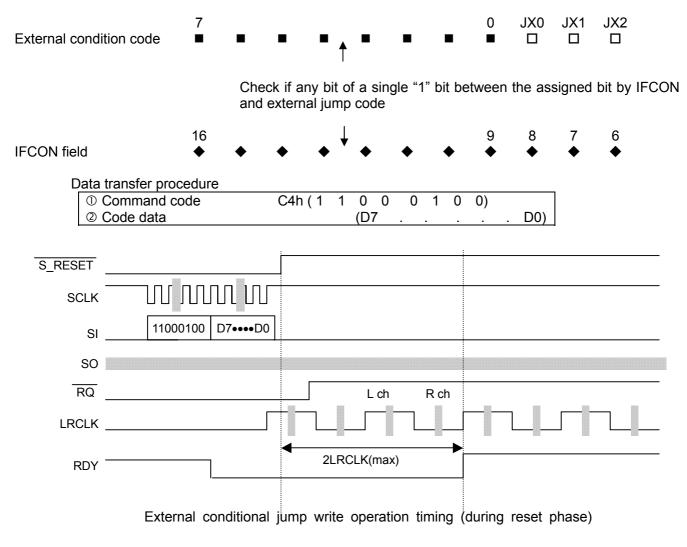

| 18        | JX0/SDIN5A               |     | <ul> <li>External Conditional pin/DSP Serial Data Input pin (pulled-down).</li> <li>For normal use, this is the external conditional jump pin (JXO).</li> <li>Input to the DSP's SDIN5 port is possible by setting a Control Register (normally SDIN5 is connected to ADC Serial Output, refer to block diagram). Supports MSB-justified 24 Bit /LSB-justified 24 Bit, 20 Bit, 16 Bit data formats.</li> </ul> | Conditional input /<br>Serial data input |

| 19        | SDIN4/JX1                | I   | <ul> <li>DSP Serial Data Input pin/External Conditional pin (pulled-<br/>down)</li> <li>Supports MSB-justified 24Bit /LSB-justified 24Bit, 20Bit,<br/>16bit formats</li> <li>This pin can be used as external conditional jump pin JX1<br/>by setting a control register</li> </ul>                                                                                                                            | Serial data input<br>/conditional input  |

| Pin<br>NO. | Pin Name                    | I/O | Function                                                                                                                                                                                                                                                                                                                                         | Pin Classification           |

|------------|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 20         | SDIN3/JX2                   | I   | DSP Serial Data Input pin/External Conditional pin ( <i>pulled-down</i> )<br>- Supports MSB-justified 24 Bit/LSB-justified 24 Bit, 20 Bit,                                                                                                                                                                                                       | Serial data input            |

|            |                             |     | <ul> <li>and 16 Bit data formats.</li> <li>This pin can be used as external conditional jump pin JX2 by setting a control register.</li> <li>This pin cannot be used as a Serial Data input pin nor external conditional pin during hands-free mode.</li> </ul>                                                                                  |                              |

| 21         | SDIN2                       | I   | DSP Serial Data Input pin ( <i>pulled-down</i> )<br>Supports MSB-justified 24 Bit/ LSB-justified 24 Bit, 20 Bit, and<br>16 Bit data format.                                                                                                                                                                                                      | Digital<br>Serial Data Input |

| 22         | SDIN1                       | I   | DSP Serial Data Input pin ( <i>pulled-down</i> )<br>Supports MSB-justified 24 Bit/ LSB-justified 24 Bit, 20 Bit, and<br>16 Bit data format.                                                                                                                                                                                                      |                              |

| 23<br>24   | DVSS<br>DVDD                |     | Digital Ground pin 0 V<br>Digital Power Supply pin 3.3 V (typ)                                                                                                                                                                                                                                                                                   | Digital Power Supply         |

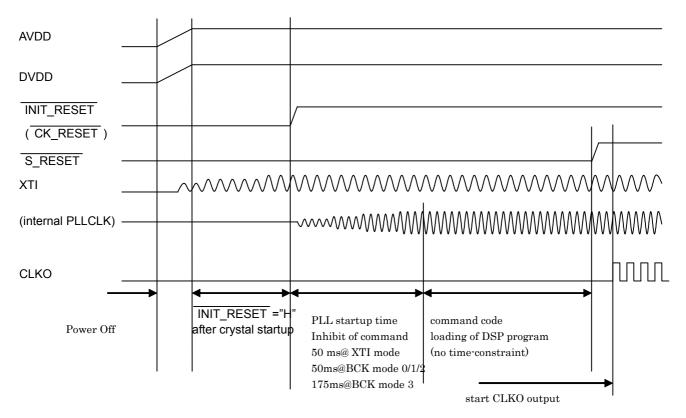

| 25         | INIT_RESET                  |     | Initial Reset N pin (for initialization)<br>This is used to initialize the AK7750.This is also used to<br>change CKS1 and CKS0 pin settings and to change XTI input<br>frequency.                                                                                                                                                                |                              |

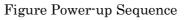

| 26         | CK_RESET                    |     | CK Reset N pin<br>This pin is used while S_RESET is at "low" to change XTI<br>input frequency and to change CKS2, CKS1, CKS0 settings.<br>CK_RESET bit in control register has similar function.<br>When CK_RESET bit is used, CK_RESET pin must be<br>commonly controlled with INIT_RESET pin or it must be set<br>to "high".                   |                              |

| 27         | S_RESET                     | I   | System Reset N pin                                                                                                                                                                                                                                                                                                                               |                              |

| 28         | DVDD                        | -   | Digital Power Supply pin 3.3 V (typ)                                                                                                                                                                                                                                                                                                             | Digital Power Supply         |

| 29         | DVSS                        | -   | Digital Ground pin 0 V                                                                                                                                                                                                                                                                                                                           | Digital Power Supply         |

| 30         | CS<br>(EESEL="L")           | I   | Chip Select pin for μC interface (pulled-down)<br>Leave open or connect to DVSS for normal operation<br>When CS = "H", data on SI pin is not written and SO, RDY,<br>DRDY pins become Hi-Z state.<br>This function is not available at EESEL="H".                                                                                                | μC                           |

|            | EESO<br>(EESEL="H")         |     | EEPROM Serial Data Output pin ( <i>pulled-down</i> )<br>Connect this pin to SO pin of AK6512C / 14C.                                                                                                                                                                                                                                             | EEP                          |

| 31         | HFST<br>(EESEL="L")         |     | Hands-Free Status pin<br>Normally at "H" but when an error occurs, it switches to "L"<br>level.                                                                                                                                                                                                                                                  | μC                           |

|            | HFST<br>EEST<br>(EESEL="H") | 0   | <ul> <li>Hands-Free Status pin / EEPROM write status pin<br/>Normally at "H" but when an error occurs, it switches to "L".<br/>Level (SWEE bit = 0 in control register).</li> <li>When data read from EEPROM is complete, EEST changes<br/>from "L" to "H". The μC input interface is enabled (SWEE bit =<br/>1 in control register).</li> </ul> |                              |

| Pin<br>NO. | Pin Name    | I/O | Function                                                                  | Pin Classification   |

|------------|-------------|-----|---------------------------------------------------------------------------|----------------------|

| NO.<br>32  | RDY         | 0   | Data Write Ready pin for μC Interface (Hi-Z)                              | μC                   |

| 52         | (EESEL="L") |     | This pin becomes Hi-Z when $\overline{CS} = $ "H".                        | μΟ                   |

|            | RDY/EESI    | 0   | Data Write Ready pin for uC interface/                                    | EEP/μC               |

|            | (EESEL="H") |     | EEPROM Serial Data Input Pin                                              |                      |

|            |             |     | Connect this pin to SI pin of AK6512C/14C.                                |                      |

|            |             |     | When data read from EEPROM is complete (EEST changes                      |                      |

|            |             |     | from "L" to "H"), this pin is automatically switched to the RDY           |                      |

|            |             |     | pin function.                                                             |                      |

| 33         | хто         | 0   | Oscillator Circuit Output pin                                             | System Clock         |

| 00         |             |     | When a quartz crystal oscillator is used, it is connected                 | -                    |

|            |             |     | between XTI pin and XTO pin.                                              |                      |

|            |             |     | When an external clock is used, keep this pin open.                       |                      |

| 34         | ХТІ         | 1   | Oscillator Circuit Output pin                                             |                      |

| <b>.</b>   |             | ·   | When a quartz crystal oscillator is used, it is connected                 |                      |

|            |             |     | between XTI pin and XTO pin.                                              |                      |

|            |             |     | An external clock should be fed to this pin when no quartz                |                      |

|            |             |     | crystal oscillator is used.                                               |                      |

| 35         | DVSS        | -   | Digital Ground pin 0 V                                                    | Digital Power Supply |

| 36         | DVDD        | -   | Digital Power Supply pin 3.3 V (typ)                                      |                      |

| 37         | RQ          | 1   | Request N pin for $\mu$ C Interface                                       | μC                   |

|            |             |     | $\mu$ C interface is enabled when $\overline{RQ}$ ="L". Read operations   | •                    |

|            |             |     | during RUN mode should be made when $\overline{RQ} = "H"$ .               |                      |

|            |             |     | RQ should be kept "H" during the reset operation and when                 |                      |

|            |             |     | an external $\mu$ C is not used.                                          |                      |

| 38         | SO          | 0   | Serial Data Output pin for μC interface                                   | μC                   |

|            |             |     | This pin becomes Hi-Z state at $\overline{CS}$ ="H" when EESEL is at "L". |                      |

| 39         | SI          | 1   | Serial Data Input/Serial Data Output Control pin for μC                   | C                    |

| 00         | 01          | · · | interface                                                                 | μΟ                   |

|            |             |     | If no data is input to this pin or it is not used as Serial Data          |                      |

|            |             |     | Output Control pin, set SI at "L".                                        |                      |

| 40         | SCLK        | 1   | Serial Data Clock pin for µC interface                                    | μC                   |

|            | 00LIX       | ·   | If no clock is used, set SCLK at "H".                                     | μe                   |

| 41         | SMODE       | 1   | Slave / Master Mode Select pin                                            | Control              |

|            |             |     | SMODE="L": Slave mode                                                     |                      |

|            |             |     | SMODE="H": Master mode                                                    |                      |

| 42         | CKSX        | I   | Master Clock Select pin                                                   | 1                    |

|            | _           |     | CKSX="H":XTI, CKSX="L":BITCLK                                             |                      |

|            |             |     | For normal operation, CKSX is set to "H".                                 |                      |

| 43         | DVDD        | -   | Digital Power Supply pin 3.3 V (typ)                                      | Digital Power Supply |

| 44         | DVSS        | -   | Digital Ground pin 0 V                                                    |                      |

| 45         | BVSS        | -   | Ground pin (silicon substrate potential)                                  | Analog Power Supply  |

|            |             |     | Tie this pin to AVSS.                                                     | U                    |

| Pin | Pin Name | I/O | Function                                                      | Pin Classification |

|-----|----------|-----|---------------------------------------------------------------|--------------------|

| NO. |          |     |                                                               |                    |

| 46  | CKS1     | I   | Master Clock Set pin ( <i>pulled-down</i> )                   | Control            |

| 47  | CKS0     | I   | Master Clock Set pin ( <i>pulled-down</i> )                   |                    |

| 48  | TESTI1   | I   | Test pin ( <i>pulled-down</i> )                               | Test               |

|     |          |     | Tie this pin to DVSS.                                         |                    |

| 49  | LFLT     | -   | PLL RC component connect pin                                  | Analog Block       |

|     |          |     | A serially connected resistor (R=22k $\Omega$ ) and capacitor |                    |

|     |          |     | (C=1.5nF) pair is connected to this pin (when PLL is not used |                    |

|     |          |     | at all, tie this pin to AVSS).                                |                    |

| 50  | AVDD     |     | Analog Power Supply pin 3.3 V ( typ ).                        |                    |

| 51  | AVSS     |     | Analog Ground pin 0 V (silicon substrate potential)           |                    |

| 52  | AVSS     | -   | Analog Ground pin 0 V (silicon substrate potential)           |                    |

| 53  | AOUTR    |     | DAC R-ch Analog Output pin                                    |                    |

| 54  | AOUTL    | 0   | DAC L-ch Analog Output pin                                    |                    |

| 55  | AVDD     | -   | Analog Power Supply pin 3.3 V (typ).                          |                    |

| 56  | AVDD     | -   | Analog Power Supply pin 3.3 V (typ).                          |                    |

| 57  | VREFH    |     | Analog Reference Voltage Input pin                            |                    |

|     |          |     | This pin is normally tied to AVDD. Connect Capacitors of 0.1  |                    |

|     |          |     | uF and 10 uF between this pin and VSS.                        |                    |

| 58  | VCOM     | 0   | Analog Common Voltage Output pin                              |                    |

|     |          |     | Connect Capacitors of 0.1 uF and 10 uF between this pin and   |                    |

|     |          |     | VSS. No external circuits should be connected to this pin.    |                    |

| 59  | VREFL    | Ι   | Analog Reference Voltage Input pin                            |                    |

|     |          |     | Tie this pin to AVSS for normal operation.                    |                    |

| 60  | AVSS     |     | Analog Ground pin 0 V (silicon substrate potential)           |                    |

| 61  | AINR-    |     | ADC R-ch Analog Inverted Input pin                            |                    |

| 62  | AINR+    |     | ADC R-ch Analog Non-Inverted Input pin                        |                    |

| 63  | AINL-    |     | ADC L-ch Analog Inverted Input pin                            |                    |

| 64  | AINL+    |     | ADC L-ch Analog Non-Inverted Input pin                        |                    |

Note) Digital input pins should not be kept open, except for pulled-down pins and BITCLK-I and LRCLK-I (EESEL="L") pins in master mode (pulled-down pins are kept open or connected to DVSS when they are not used).

# Absolute maximum rating

| ( | AVSS BVSS       | , DVSS = 0 V: All      | voltages i | indicated are | relative to the | around)    |

|---|-----------------|------------------------|------------|---------------|-----------------|------------|

|   | / v 00, D v 00, | , D = 0 = 0 = 0 = 7  m | voltages i |               |                 | , grouna.) |

| Item                          | Symbol              | Min  | Max    | Units |

|-------------------------------|---------------------|------|--------|-------|

| Power supply voltage          |                     |      |        |       |

| Analog (AVDD)                 | VA                  | -0.3 | 4.6    | V     |

| Digital (DVDD)                | VD                  | -0.3 | 4.6    | V     |

| AVSS(BVSS) – DVSS  Note1      | $\Delta \text{GND}$ |      | 0.3    | V     |

| Input current                 | IIN                 | -    | ±10    | mA    |

| (Except for power supply pin) |                     |      |        |       |

| Analog input voltage          | VINA                |      |        | V     |

| AINL+, AINL-, AINR+, AINR-,   |                     | -0.3 | VA+0.3 |       |

| VRADH, VRADL, VRDAH, VRDAL    |                     |      |        |       |

| Digital input voltage         | VIND                | -0.3 | VA+0.3 | V     |

| Operating ambient temperature | Та                  | -40  | 85     | °C    |

| Storage temperature           | Tstg                | -65  | 150    | °C    |

Note1) AVSS, BVSS, and DVSS must be same potential.

WARNING: Operation at or beyond these limits may result in permanent damage of the device. Normal operations are not guaranteed under these critical conditions in principle.

# **Recommended operating conditions**

(AVSS, BVSS, DVSS = 0 V: All voltages indicated are relative to the ground.)

| <u>(</u>                                                   |            |            |            |            | <u>g. e a a.</u> |

|------------------------------------------------------------|------------|------------|------------|------------|------------------|

| Items                                                      |            | Min        | Тур        | Max        | Units            |

| Power supply voltage<br>AVDD<br>DVDD                       | VA<br>VD   | 3.0<br>3.0 | 3.3<br>3.3 | 3.6<br>3.6 | >>               |

| Reference voltage (VREF)<br>VREFH Note 1)<br>VREFL Note 2) | VRH<br>VRL |            | VA<br>0.0  |            | V<br>V           |

Note 1) VREFH normally connect with AVDD. Note 2) VREFLnormally connect with AVSS.

Note: The analog input voltage and output voltage are proportional to the VREFL and VREFH voltages.

\*) AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

# Electric characteristics

# (1) Analog characteristics

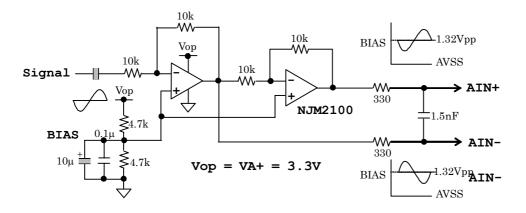

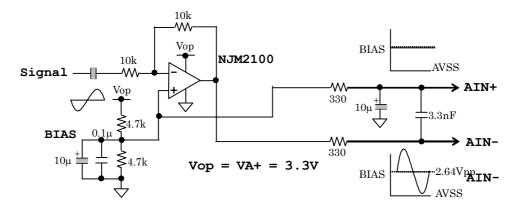

(Unless otherwise specified, Ta = 25°C; AVDD, DVDD = 3.3V; VREF=AVDD, VREFL=AVSS, BITCLK = 64 fs; Signal frequency 1 kHz; measuring frequency = 20 Hz to 20 kHz @48kHz; ADC with all differential inputs XTI=12.288MHz; CKSX="H"; SMODE="H");

|         | Parameter                                  | Min   | Тур   | Max   | Units |  |  |  |  |

|---------|--------------------------------------------|-------|-------|-------|-------|--|--|--|--|

| ADC     | Resolution                                 |       |       | 24    | Bits  |  |  |  |  |

| Section | Dynamic characteristics                    |       |       |       | •     |  |  |  |  |

|         | S/(N+D) fs = 48kHz (-1dBFS) (note1)        | 80    | 91    |       | dB    |  |  |  |  |

|         | Dynamic range                              |       |       |       |       |  |  |  |  |

|         | fs = 48kHz (A filter) (note2)              | 90    | 98    |       | dB    |  |  |  |  |

|         | S/N fs = 48kHz (A filter)                  | 90    | 98    |       | dB    |  |  |  |  |

|         | Inter-channel isolation (f =1 kHz) (note3) | 90    | 105   |       | dB    |  |  |  |  |

|         | DC accuracy                                |       |       |       |       |  |  |  |  |

|         | Inter-channel gain mismatching             |       | 0.1   | 0.3   | dB    |  |  |  |  |

|         | Analog input                               |       |       |       |       |  |  |  |  |

|         | Input voltage (Note 4)                     | ±1.22 | ±1.32 | ±1.42 | Vp-p  |  |  |  |  |

|         | Input impedance (Note 5)                   |       | 95    |       | kΩ    |  |  |  |  |

| DAC     | Resolution                                 |       |       | 24    | Bits  |  |  |  |  |

| section | Dynamic characteristics                    |       |       |       |       |  |  |  |  |

|         | S/(N+D) fs = 48kHz (0 dB)                  | 78    | 86    |       | dB    |  |  |  |  |

|         | Dynamic range fs = 48kHz(-60 dB)           | 90    | 98    |       | dB    |  |  |  |  |

|         | (A filter) (Note 2)                        |       |       |       |       |  |  |  |  |

|         | S/N fs = 48kHz (A filter)                  | 90    | 98    |       | dB    |  |  |  |  |

|         | Inter-channel isolation (f = 1 kHz)        | 90    | 105   |       | dB    |  |  |  |  |

|         | DC accuracy                                | 1     |       | ,     | 1     |  |  |  |  |

|         | Inter-channel gain mismatching             |       | 0.2   | 0.5   | dB    |  |  |  |  |

|         | Analog output                              | 1     |       | 1     | 1     |  |  |  |  |

|         | Output voltage (Note 6)                    | 1.85  | 2.00  | 2.15  | Vp-р  |  |  |  |  |

|         | Load resistance                            | 10    |       |       | kΩ    |  |  |  |  |

|         | Load capacitance                           |       |       | 50    | pF    |  |  |  |  |

Note: 1. When using single-ended inputs, this value is not guaranteed.

- 2. Indicates S/(N+D) when -60 dB signal is applied.

- 3. Inter-channel isolation between L-ch and R-ch at –1 dB FS signal input.

- 4. The full scale for analog input voltage ( $\triangle$ AIN = (AIN+) (AIN-)) can be represented by (±FS = ±(VREFH-VREFL) × 0.4).

- 5. Impedance is in inverse proportion to fs.

- 6. Full scale output voltage at VREFH = AVDD, VREFL = AVSS

# (2) DC characteristics

(VDD=AVDD=DVDD=3.0~3.6V,Ta=-40°C~85°C)

| Parameter                                 | Symbol | Min     | Тур | Max    | Units |

|-------------------------------------------|--------|---------|-----|--------|-------|

| High level input voltage                  | VIH    | 80%VDD  |     |        | V     |

| Low level input voltage                   | VIL    |         |     | 20%VDD | V     |

| High level output voltage lout=-100µA     | VOH    | VDD-0.5 |     |        | V     |

| Low level output voltage lout=100µA       | VOL    |         |     | 0.5    | V     |

| Input leak current Note 1)                | lin    |         |     | ±10    | μA    |

| Input leak current(Pull down pin) Note 1) | lid    |         | 22  |        | μA    |

| Input leak current XTI pin                | lix    |         | 50  |        | μA    |

Note:

1. The pull down pins and XTI are not included.

2. The pull down pins (typ. 150kΩ) is as follows: 1, 2, 18, 19, 20, 21, 22, 30, 46, 47, and 48.

Note: Regarding the input/output levels in the text, the low level will be represented as "L" or 0, and the high level as "H" or 1.

In principle, "0" and "1" will be used to represent the bus functions (serial/parallel) such as registers.

# (3) Current consumption

(AVDD=DVDD=3.0~3.6V, Ta=25°C; master clock (XTI)=12.288MHz=256fs[fs=48kHz], with PLL mode;

| Parameter                                                          | Min | Тур      | Max       | Units    |

|--------------------------------------------------------------------|-----|----------|-----------|----------|

| Power supply current note 1)<br>Normal Speed<br>a) AVDD<br>b) DVDD |     | 25<br>85 | 40<br>100 | mA<br>mA |

note 1) DVDD current value may change, depending on the content of DSP program executed and clock frequency.

[AK7750]

# (4) Digital filter characteristics

Listed values are copied as reference data from the designed values and are not the guaranteed values. They are guaranteed-by-design after passing the IC tester's digital functional test..

#### 4-1) ADC Section :

(Ta=25°C; AVDD,DVDD =3.0~3.6V; fs=48kHz; HPF=off Note 1)

| parameter                        |     | Min  | Тур  | Max    | Units |

|----------------------------------|-----|------|------|--------|-------|

| Pass band (±0.005dB) note2)      | PB  | 0    |      | 21.5   | kHz   |

| (-6dB)                           |     | -    | 24.0 | -      | kHz   |

|                                  |     |      |      |        | kHz   |

| Stop band                        | SB  | 26.5 |      |        | kHz   |

| Pass band ripple Note 2)         | PR  |      |      | ±0.005 | dB    |

| Stop band attenuation Note 3, 4) | SA  | 80   |      |        | dB    |

| Group delay distortion           | ∆GD |      |      | 0      | μS    |

| Group delay (Ts=1/fs)            | GD  |      | 29.3 |        | Ts    |

Note:

1. These frequencies scale with sampling frequency (fs). Not include HPF response.

2. The pass band is from DC to 21.5kHz when fs = 48kHz.

3. The stop band is from 26.5kHz to 3.0455MHz when fs = 48kHz.

4. When fs = 48kHz, the analog modulator samples analog input at 3.072MHz. The digital filter does not attenuate the input signal in the multiple bands (n x 3.072MHz ± 21.99kHz; n=0, 1, 2, 3...) of the sampling frequency.

#### 4-2) DAC section a) DAF bit = '0' (CONT6 D6)

| Parameter                                 | Symbol | min  | typ  | max   | Units |

|-------------------------------------------|--------|------|------|-------|-------|

| Digital filter                            |        |      |      |       |       |

| Pass band ±0.08dB                         | PB     | 0    |      | 21.2  | kHz   |

| (-0.28dB) (Note 1)                        |        | -    | 21.7 | -     | kHz   |

| (-6.0dB)                                  |        | -    | 24.0 | -     | kHz   |

| Stop band (Note 1)                        | SB     | 26.5 |      |       | kHz   |

| Pass band ripple                          | PR     |      |      | ±0.04 | dB    |

| Stop band attenuation                     | SA     | 47   |      |       | dB    |

| Group delay (Ts=1/fs) (Note 2)            | GD     | -    | 15   |       | Ts    |

| Digital filter+SCF                        |        |      |      |       |       |

| Amplitude characteristics<br>0 to 20.0kHz |        |      | ±0.5 |       | dB    |

Note:

1. The pass band and stop band frequencies are proportional to "fs" (system sampling rate), and represents PB=0.4535fs(@-0.06dB) and SB=0.546fs, respectively.

2. The digital filter's delay is calculated as the time from setting 24 Bit data into the input register until an analog signal is output.

# b) DAF bit = '1' (CONT6 D6)

(Ta=25°C; AVDD,DVDD =3.0~3.6V; fs=48kHz)

| Parameter                                 | Symbol | min  | typ  | max   | Units |

|-------------------------------------------|--------|------|------|-------|-------|

| Digital filter                            |        |      |      |       |       |

| Pass band ±0.02dB                         | PB     | 0    |      | 20.6  | kHz   |

| (-0.48dB) (Note 1)                        |        | -    | 21.7 | -     | kHz   |

| (-6.0dB)                                  |        | -    | 24.0 | -     | kHz   |

| Stop band (Note 1)                        | SB     | 27.4 |      |       | kHz   |

| Pass band ripple                          | PR     |      |      | ±0.01 | dB    |

| Stop band attenuation                     | SA     | 59   |      |       | dB    |

| Group delay (Ts=1/fs) (Note 2)            | GD     | -    | 15   |       | Ts    |

| Digital filter+SCF                        |        |      |      |       |       |

| Amplitude characteristics<br>0 to 20.0kHz |        |      | ±0.5 |       | dB    |

Note:

1. The pass band and stop band frequencies are proportional to "fs" (system sampling rate), and represents PB=0.4292fs(@-0.06dB) and SB=0.571fs, respectively.

2. The digital filter's delay is calculated as the time from setting 24 Bit data into the input register until an analog signal is output.

# (5) Switching characteristics

#### 1) System clock

(AVDD=DVDD=3.0 to 3.6V.Ta= -40°C to 85°C)

| Parameter                                                          | Symbol           | min      | typ               | max      | Units    |

|--------------------------------------------------------------------|------------------|----------|-------------------|----------|----------|

| Maser clock(XTI) @CKSX="H"                                         |                  |          |                   |          |          |

| a) when a crystal oscillator is used (note 1)                      |                  |          |                   |          |          |

| CKS[1:0]=0h                                                        | fXTI             | _        | 11.2896<br>12.288 | -        | MHz      |

| CKS[1:0]=1h                                                        | fXTI             | -        | 16.9344<br>18.432 | -        | MHz      |

| CKS[1:0]=2h                                                        | fXTI             | -        | 22.5792<br>24.576 | -        | MHz      |

| b)when an external clock is used<br>(note 1)                       |                  |          |                   |          |          |

| Duty factor (≤18.5MHz)<br>(>18.5MHz)                               |                  | 40<br>45 | 50<br>50          | 60<br>55 | %<br>%   |

| CKS[1:0]=0h (PLL operation range)                                  | fXTI             | 11.0     |                   | 12.33    | MHz      |

| CKS[1:0]=1h (PLL operation range)                                  | fXTI             | 16.5     |                   | 18.6     | MHz      |

| CKS[1:0]=2h (PLL operation range)                                  | fXTI             | 22.0     |                   | 24.66    | MHz      |

| CKS[1:0]=3h (PLL is not used)                                      | fXTI             | 33.0     |                   | 37.0     | MHz      |

| Clock rise time                                                    | tCR              |          |                   | 6        | ns       |

| Clock fall time                                                    | tCF              |          |                   | 6        | ns       |

| LRCLK_I,LRCLK frequency note2)                                     | fs               | 8        | 48                | 192      | kHz      |

| Slave mode: Clock rise time                                        | tLR              |          |                   | 6        | ns       |

| Slave mode: Clock fall time                                        | tLF              |          |                   | 6        | ns       |

| BITCLK_I ,BITCLK frequency<br>(@CKSX="H") (note3)                  | fBCLK            | 48       |                   | 64       | fs       |

| Slave mode: high level width<br>Slave mode: high level width       | tBCLKH<br>tBCLKL | 34<br>34 |                   |          | ns<br>ns |

| Slave mode: clock rise time                                        | tBR              |          |                   | 6        | ns       |

| Slave mode: clock fall time                                        | tBF              |          |                   | 6        | ns       |

| <b>BITCLK_I,BITCLK</b> frequency<br>(@CKSX="L",SMODE="L") (note 4) | fBCLK            | -        | 64                | -        | fs       |

| Duty factor                                                        |                  | 40       | 50                | 60       | %        |

| Slave mode: high level width                                       | tBCLKH           | 34       |                   |          | ns       |

| Slave mode: high level width                                       | tBCLKL           | 34       |                   |          | ns       |

| Slave mode: clock rise time                                        | tBR              |          |                   | 6        | ns       |

| Slave mode: clock fall time                                        | tBF              |          |                   | 6        | ns       |

note1) CKS1=CKS[1].CKS[0]=CKS0

note2) LRCLK and sampling rate ( fs ) must be identical. note3) 48 fs is used for slave mode ( only 64 fs is available for hands-free mode )

note4) BITCLK-I or BITCLK is used as clock input. BITCLK must be precisely divided into 64 clocks in 1 fs time.

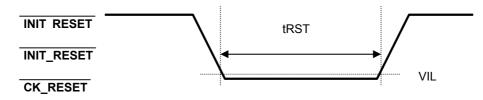

# 2) <u>Reset</u>

(AVDD=DVDD=3.0 to 3.6V,Ta=-40°C to 85°C)

| Paramet    | er      | Symbol | min | typ | max | Units |

|------------|---------|--------|-----|-----|-----|-------|

| INIT_RESET | note 1) | tRST   | 400 |     |     | ns    |

| CK_RESET   |         | tRST   | 400 |     |     | ns    |

| S_RESET    |         | tRST   | 400 |     |     | ns    |

note1) At the power-on, it is OK to keep this pin to "L". "H" transition must be made after the power-on and master clock is full running.

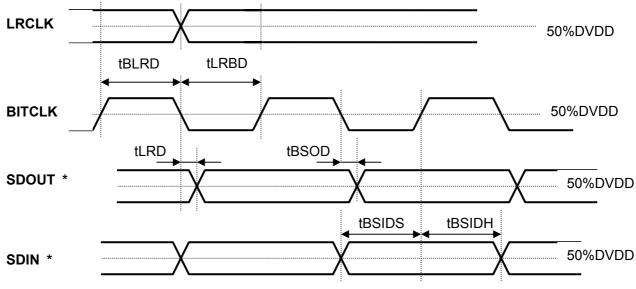

# 3) Audio Interface

(AVDD=DVDD=3.0 to 3.6V,Ta= Ta=-40°C to 85°C, CL=20pF)

| Parameter                                              | Symbol | min  | typ | max | Units |

|--------------------------------------------------------|--------|------|-----|-----|-------|

| Slave mode                                             |        |      |     |     |       |

| BITCLK frequency                                       | fBCLK  | 48   | 64  | 64  | fs    |

| Delay time from BITCLK" <sup>↑</sup> " to LRCLK note1) | tBLRD  | 40   |     |     | ns    |

| Delay time from LRCLK to BITCLK" <sup>↑</sup> " note1) | tLRBD  | 40   |     |     | ns    |

| Delay time from LRCLK to serial data output            | tLRD   |      |     | 80  | ns    |

| Delay time from BITCLK to serial data output           | tBSOD  |      |     | 80  | ns    |

| Serial data input latch hold time                      | tBSIDS | 40   |     |     | ns    |

| Serial data input latch setup time                     | tBSIDH | 40   |     |     | ns    |

| Master mode                                            |        |      |     |     |       |

| BITCLK frequency                                       | fBCLK  |      | 64  |     | fs    |

| BITCLK duty factor                                     |        |      | 50  |     | %     |

| Delay time from BITCLK" <sup>↑</sup> " to LRCLK note1) | tBLRD  | 40   |     |     | ns    |

| Delay time from LRCLK to BITCLK" <sup>↑</sup> " note1) | tLRBD  | 40   |     |     | ns    |

| Delay time from LRCLK to serial data output            | tLRD   |      |     | 80  | ns    |

| Delay time from BITCLK to serial data output           | tBSOD  |      |     | 80  | ns    |

| Serial data input latch hold time                      | tBSIDS | 40   |     |     | ns    |

| Serial data input latch setup time                     | tBSIDH | 40   |     |     | ns    |

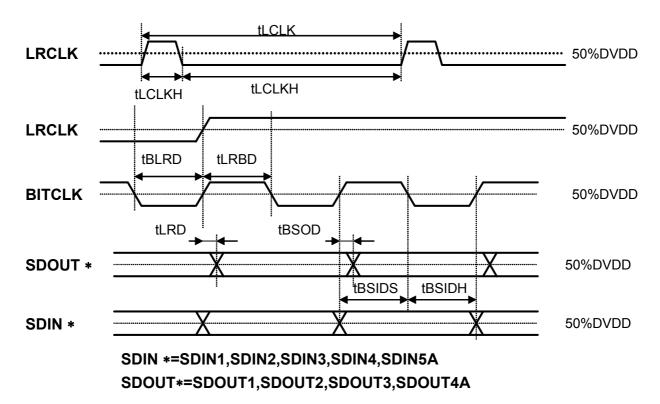

| PCM Interface mode (SF/LF)                             |        |      |     |     |       |

| LRCLK frequency                                        | fLRCK  | 8    |     | 48  | kHz   |

| BITCLK frequency                                       | fBCLK  |      | 64  |     | fs    |

| BITCLK duty factor                                     |        |      | 50  |     | %     |

| Delay time from BITCLK" <sup>↑</sup> " to LRCLK note1) | tBLRD  | 40   |     |     | ns    |

| Delay time from LRCLK to BITCLK"↓" note1)              | tLRBD  | 40   |     |     | ns    |

| Delay time from LRCLK to serial data output            | tLRD   |      |     | 80  | ns    |

| Delay time from BITCLK to serial data output           | tBSOD  |      |     | 80  | ns    |

| Serial data input latch hold time                      | tBSIDS | 40   |     |     | ns    |

| Serial data input latch setup time                     | tBSIDH | 40   |     |     | ns    |

| LRCLK high level width (SF)                            | tLCKKH |      | 64  |     | fs    |

| LRCLK high level width (LF)                            | tLCLKH | 300  |     |     | ns    |

| LRCLK low level width (LF)                             | tLCLKL | 1200 |     |     | ns    |

Note 1) this value is specified such that LRCLK edge and rising edge of BITCLK never overlap

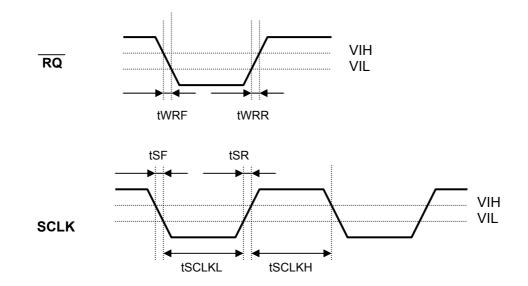

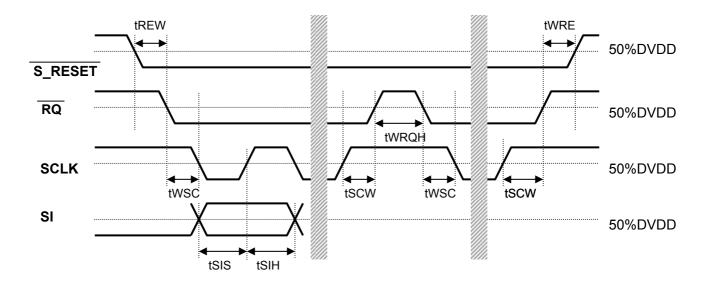

# 4) Microprocessor Interface

(AVDD=DVDD=3.0 to 3.6V,Ta= Ta=-40°C to 85°C, CL=20pF)

| Parameter                                                                      | symbol        | min      | typ | max     | Units |

|--------------------------------------------------------------------------------|---------------|----------|-----|---------|-------|

| μC I/F signal                                                                  |               |          |     |         |       |

| RQ fall time                                                                   | tWRF          |          |     | 8       | ns    |

| RQ rise time                                                                   | tWRR          |          |     | 8       | ns    |

| SCLK fall time                                                                 | tSF           |          |     | 8       | ns    |

| SCLK rise time                                                                 | tSR           |          |     | 8       | ns    |

| SCLK low level width                                                           | tSCLKL        | 100      |     |         | ns    |

| SCLK high level width                                                          | tSCLKH        | 100      |     |         | ns    |

| $\mu C \rightarrow AK7750$                                                     |               |          |     |         |       |

| S_RESET "↓" to RQ "↓"                                                          | tREW          | 200      |     |         | ns    |

| RQ   "↑" to   S_RESET   "↑"   note1)                                           | tWRE          | 200      |     |         | ns    |

| RQ high level width                                                            | tWRQH         | 200      |     |         | ns    |

| Time from $\overline{RQ}$ " $\downarrow$ " to SCLK" $\downarrow$ "             | tWSC          | 200      |     |         | ns    |

| Time from SCLK"↑" to RQ "↑"                                                    | tSCW          | 12×tMCLK |     |         | ns    |

| SI latch setup time                                                            | tSIS          | 100      |     |         | ns    |

| SI latch hold time                                                             | tSIH          | 100      |     |         | ns    |

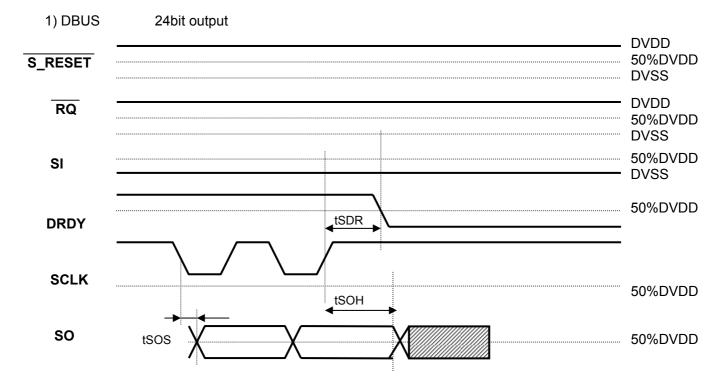

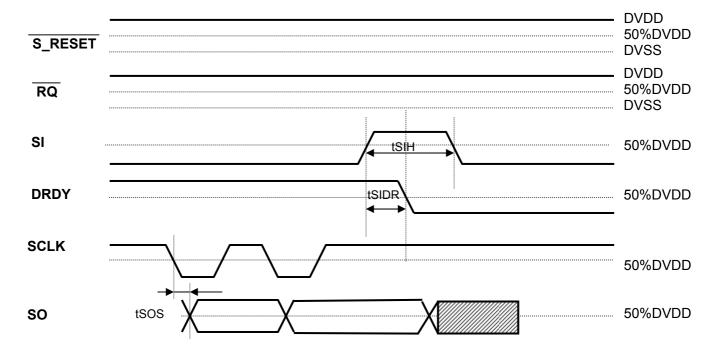

| AK7750 $\rightarrow \mu$ C (DBUS output)                                       |               |          |     |         |       |

| SCLK"↑" to DRDY"↓"                                                             | tSDR          |          |     | 3×tMCLK | ns    |

| Time from SI "↑" to DRDY"↓"                                                    | tSIDR         |          |     | 3×tMCLK | ns    |

| SI high level width                                                            | tSIH          | 3×tMCLK  |     |         | ns    |

| Delay time from SCLK"↓" to SO output                                           | tSOS          |          |     | 100     | ns    |

| Hold time from SCLK " <sup>↑</sup> " to SO outout                              | tSOH          | 100      |     |         | ns    |

| AK7750 $\rightarrow \mu$ C (RAM DATA read-out)                                 |               |          |     |         |       |

| SI latch setup time(SI="H")                                                    | tRSISH        | 30       |     |         | ns    |

| SI latch setup time(SI="L")                                                    | tRSISL        | 30       |     |         | ns    |

| SI latch hold time<br>Delay time from SCLK "↓" to SO output                    | tRSIH<br>tSOD | 30       |     | 100     | ns    |

|                                                                                | 1300          |          |     | 100     | ns    |

| <b>AK7750</b> $\rightarrow \mu C$ (CRC result-out) note2)                      | 40000         |          |     | 000     |       |

| Delay time from RQ "^" to SO output                                            | tRSOC         | 50       |     | 200     | ns    |

| Delay tiem from RQ "↓" to SO output note3)                                     | tFSOD         | 50       |     |         | ns    |

| CS (EESEL="L" or open)                                                         |               |          |     |         |       |

| CS fall time                                                                   | tCSF          |          |     | 8       | ns    |

| CS rise time                                                                   | tCSR          |          |     | 8       | ns    |

| Time from S_RESET " $\downarrow$ " to CS " $\downarrow$ "                      | tWRCS         | 400      |     |         | ns    |

| Time from CS "↑" to S_RESET "↑"                                                | tWCSR         | 400      |     |         | ns    |

| CS high level width                                                            | tWCSH         | 800      |     |         | ns    |

| Time from $\overline{CS}$ " $\downarrow$ " to $\overline{RQ}$ " $\downarrow$ " | tWCSRQ        | 400      |     |         | ns    |

| Time from RQ "↑" to CS "↑"                                                     | tWRQCS        | 400      |     |         | ns    |

| CS " $\downarrow$ " to SO,RDY,DRDY Hi-Z release (RL=10k $\Omega$ )             | tCSHR         |          |     | 600     | ns    |

| CS "↑" to SO,RDY,DRDY Hi-Z (RL=10kΩ)                                           | tCSHS         |          |     | 600     | ns    |

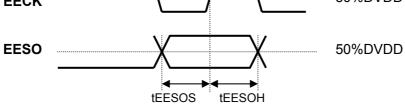

| EEPROM → AK7750(EESEL="H")                                                     |               |          |     |         |       |

| EESO latch setup time                                                          | tEESOS        | 100      |     |         | ns    |

| EESO latch hold time                                                           | tEESOH        | 100      |     |         | ns    |

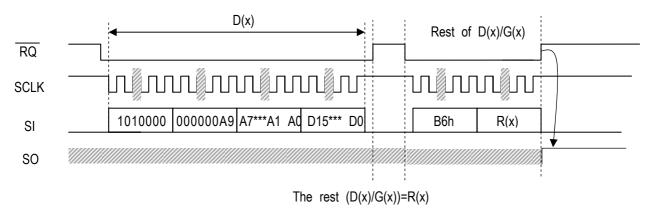

Note1: Excluding an external conditional jump at reset.

Note2: This is a case where the remainder of serial data D(x), divided by the Generator Polynomial G (x) is

equal to R (x). SO becomes "H". Note3: This means that data must be taken into the microprocessor 50 ns earlier than the falling edge of RQ (this applies when no read-out is made during RUN).

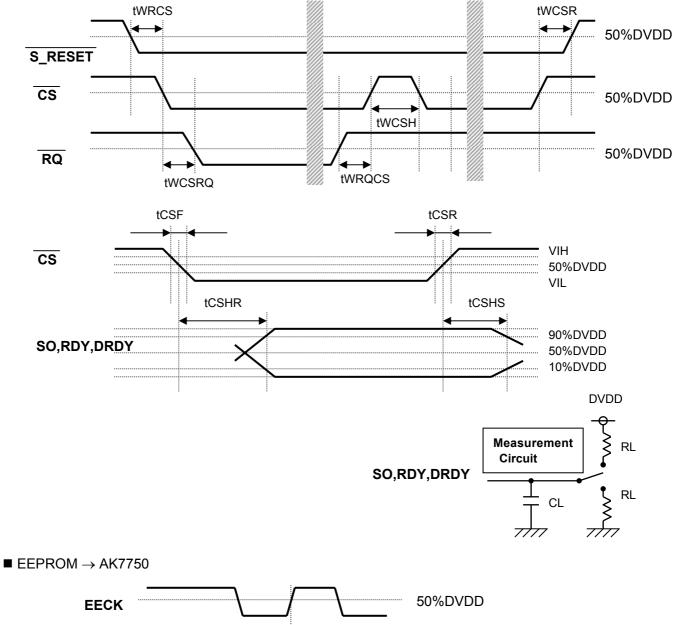

# (6) Timing waveform 6-1) System clock

# 6-2) Reset

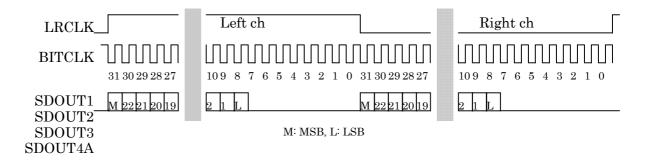

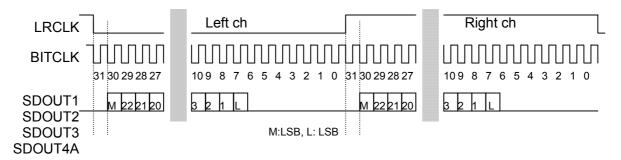

# 6-3) Audio Interface

SDIN \*=SDIN1,SDIN2,SDIN3,SDIN4,SDIN5A

SDOUT \*=SDOUT1,SDOUT2,SDOUT3,SDOUT4

b) PCM Format

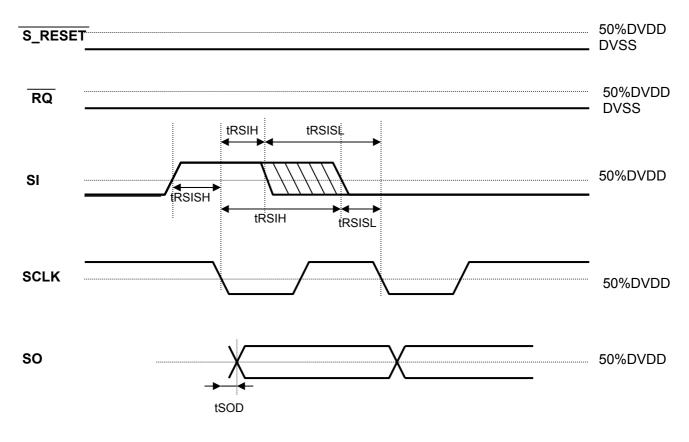

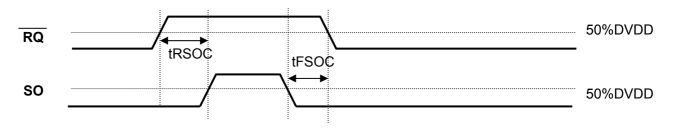

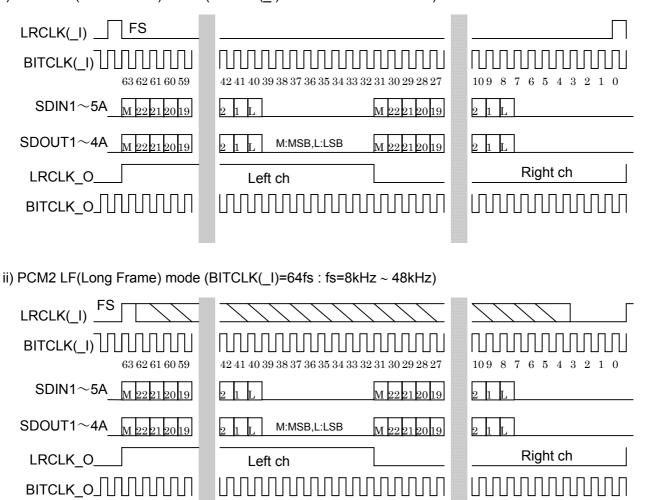

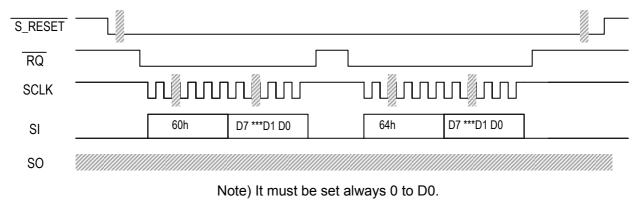

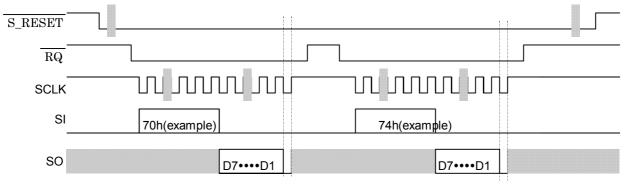

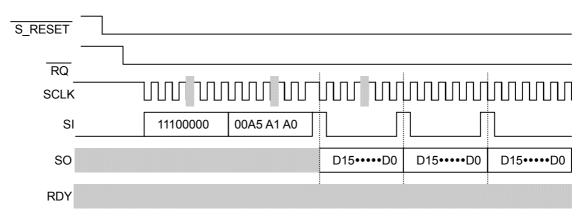

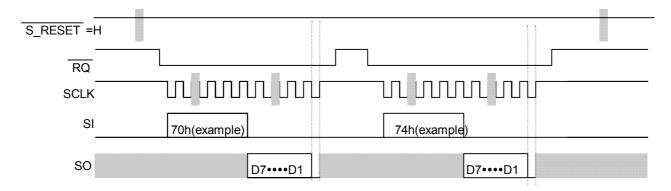

# 6-4) μC Interface

■ µC interface signal

$\blacksquare \ \mu C \rightarrow AK7750$

Note: Timing is identical in RUN mode except that S\_RESET becomes "H.

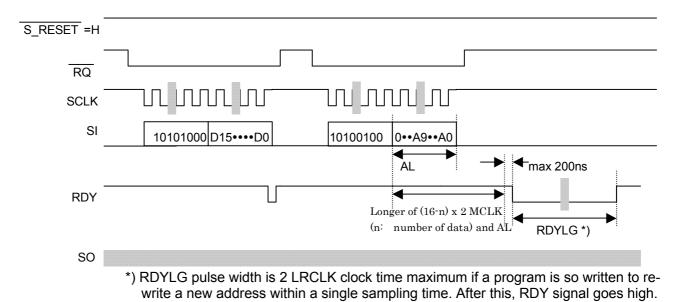

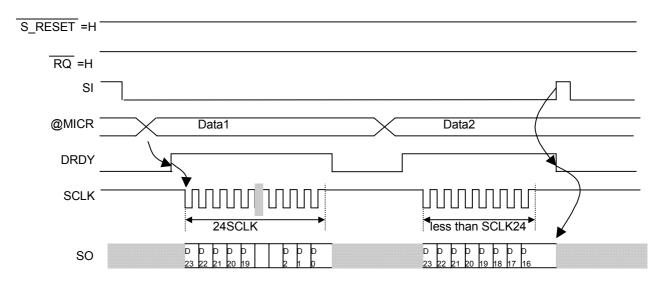

# ■ AK7750 $\rightarrow \mu C(DBUS \text{ output})$

<sup>2)</sup> DBUS under 24 Bit output ( SI is used )

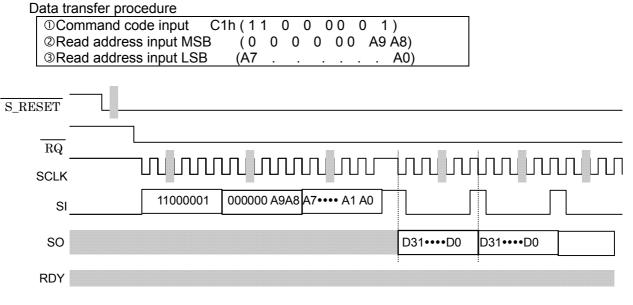

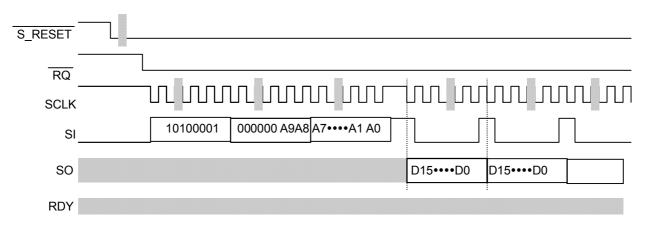

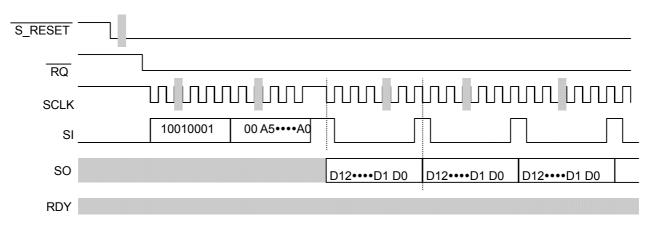

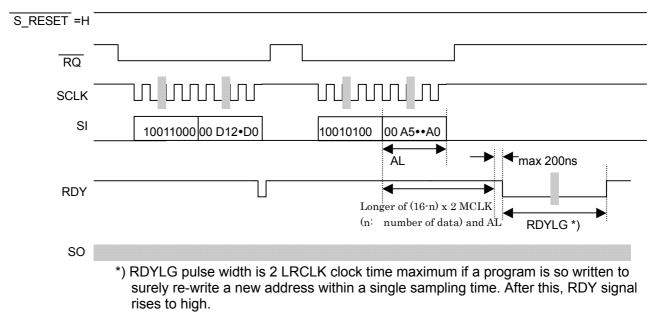

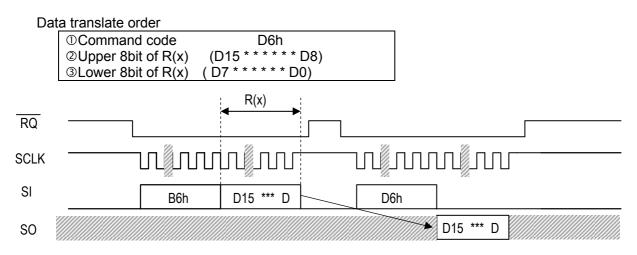

# ■ AK7750 $\rightarrow \mu C(RAM DATA read-out)$

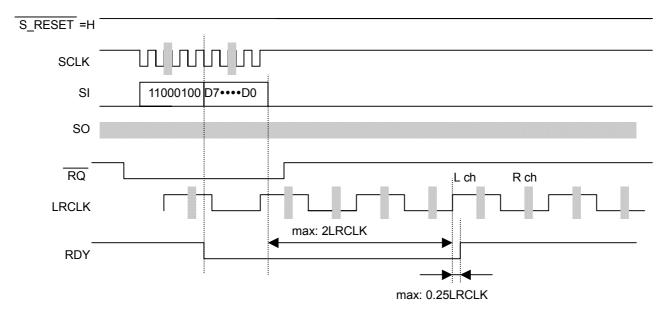

■ AK7750  $\rightarrow \mu C(CRC \text{ check: remainder of D } (x) / G (x) ) = R (x))$

■ CS (EESEL="L" or OPEN)

# Functional Description

#### (1) Various Pin Setting

#### 1) CKS1,CKS0 : Master Clock ( MCLK ) Set pin CKSX : Master Clock Select pin

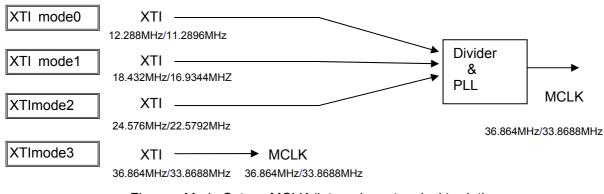

The AK7750 usually operates using a 36.864 MHz Master Clock (MCLK) (or 33.8688 MHz). When CKSX = "H", the XTI input clock is selected by the CKS1 and CKS0 pins.

In addition to the normal use described above, the AK7750 can also operate using BITCLK-I or BITCLK as a master clock input during slave mode operation (SMODE = "L") by setting CKSX = "L". Since the AK7750 is running in slave mode instead of master mode, certain modes may not be available since the AK7750 modes are restricted by the incoming audio clock.

# ■ Mode setting by CKSX, CKS1, CKS0 pins

# a ) XTI selection at CKSX = "H"

|      | ts: sampling frequency |            |                 |                  |         |  |  |  |  |  |  |

|------|------------------------|------------|-----------------|------------------|---------|--|--|--|--|--|--|

| XTI  | CKS                    |            |                 | Internal         |         |  |  |  |  |  |  |

| mode | [1:0]                  | XTI        | Fs:48kHz series | fs:44.1kHzseries | PLL     |  |  |  |  |  |  |

| 0    | 0h                     | MCLK/3     | 12.288MHz       | 11.2896MHz       | use     |  |  |  |  |  |  |

| 1    | 1h                     | MCLK/2     | 18.432MHz       | 16.9344MHz       | use     |  |  |  |  |  |  |

| 2    | 2h                     | MCLK*(2/3) | 24.576MHz       | 22.5792MHz       | use     |  |  |  |  |  |  |

| 3    | 3h                     | MCLK       | 36.864MHz       | 33.8688MHz       | not use |  |  |  |  |  |  |

note) CKS1 = CKS[1],CKS0 = CKS[0]

A crystal oscillator cannot be used in XTI mode 3.

For hands-free mode, use fs = 48 KHz.

Sample-rate setting is performed using the (CONT0) control register.

Usually XTI modes 0 and 1 are used (XTI mode 0 is selected when CKS1 and CKS0 pins are left open). XTI mode 2 is only used when a 512 fs clock is available externally. XTI mode 3 is used when the PLL is not used.

To change clock settings after power on (CKS1, CKS0 and CKSX), an initial reset (INIT\_RESET = "L",  $S_RESET = "L"$ ), or during a clock reset (CK\_RESET = "L", S\_RESET = "L") should be performed. Since the PLL circuit and internal clocks are controlled by CKS1, CKS0 and CKSX pins, an erroneous operation may occur if any pin setting changes occur under any conditions other than those described above (same conditions apply when changing the input for XTI).

A reset can be performed using either the pin CK\_RESET or the CKRST bit (CONT0:D1) in control register. When using the register RESET, the CK\_RESET pin should be set to "H" or should be linked together with INIT\_RESET pin.

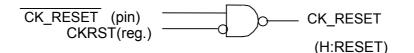

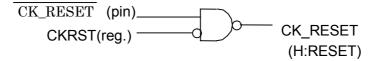

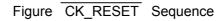

CK\_RESET (pin) and CKRST(reg.) relation

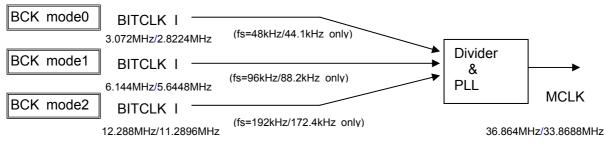

# b) BITCLK(\_I ) Selection at CKSX = "L" ( SMODE = "L" )

| EESEL | ="L"  | fs: sampling frequency |                |                    |                   |     |  |  |  |

|-------|-------|------------------------|----------------|--------------------|-------------------|-----|--|--|--|

| BCK   | CKS   | BITCLK_I               | (64fs)         | 64fs) @SMODE="L" I |                   |     |  |  |  |

| mode  | [1:0] | BITCLK_I               | sample rate    | fs:48kHz series    | fs:44.1kHz series | PLL |  |  |  |

| 0     | 0h    | MCLK/12                | standard speed | 3.072MHz           | 2.8224MHz         | use |  |  |  |

| 1     | 1h    | MCLK/6                 | double speed   | 6.144MHz           | 5.6448MHz         | use |  |  |  |

| 2     | 2h    | MCLK/3                 | 4X speed       | 12.288MHz          | 11.2896MHz        | use |  |  |  |

| 3     | 3h    | MCLK/72                | fs=8kHz        | 512kHz             | -                 | use |  |  |  |

#### EESEL="H"

| BCK  | CKS   | BITCLK  | (64fs)         | @SMODE="L"      |                   | Internal |

|------|-------|---------|----------------|-----------------|-------------------|----------|

| mode | [1:0] | BITCLK  | sample rate    | fs:48kHz series | fs:44.1kHz series | PLL      |

| 0    | 0h    | MCLK/12 | standard speed | 3.072MHz        | 2.8224MHz         | use      |

| 1    | 1h    | MCLK/6  | double speed   | 6.144MHz        | 5.6448MHz         | use      |

| 2    | 2h    | MCLK/3  | 4x speed       | 12.288MHz       | 11.2896MHz        | use      |

| 3    | 3h    | MCLK/72 | fs=8kHz        | 512kHz          | -                 | use      |

note1) CKS1 = CKS[1],CKS0 = CKS[0]

note2)BITCLK\_I clock is selected at EESEL = "L" and BITCLK clock is selected at EESEL = "H". note3) Hands-free mode is available only when BCK mode 3 is selected.

BCK modes are also used to generate internal master clock other than used as a primary bit clock. Therefore some limitations exist when to use BITCLK (\_I) (for details, please refer to item b) of the Clock Source description).

BCK mode is not available when the device operates at master mode.

The sampling rate is fixed by BCK mode that is not affected by the speed setting (standard speed, double speed, and 4x speed) of the control register.

Both of internal ADC and DAC are not available when BCK mode 1or 2 is selected. PSAD(D7) bit in CONT2 register and PSCODEC(D7) bit in the CONT6 register should be set to "1".

Please set XTI = "L" when XTI is not used at all.

When to switch setting of CKS1, CKS0 and CKSX after the power-on, it should be done either during the initial reset ( $\overline{INIT}_{RESET} = "L"$ ,  $\overline{S}_{RESET} = "L"$ ) or during the clock reset ( $\overline{CK}_{RESET} = "L"$ ,  $\overline{S}_{RESET} = "L"$ ). Since PLL circuit and internal clocks are controlled by CKS1, CKS0 and CKSX pins, an erroneous operation may occur if any pin set change is taken place under any conditions other than those described above (same conditions apply when to change input BITCLK(\_1)).

Instead of CK\_RESET, D1 bit in control register (CONT0: D1) can be used. In this case, CK\_RESET pin should be set to "H" or should be linked together with INIT\_RESET pin.

CK\_RESET (pin) and CKRST(reg.) relation

# Clock Sources

# a) XTI selection at CKSX = "H".

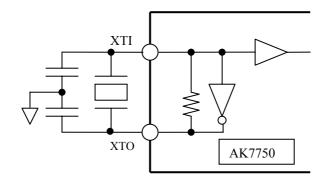

Clocks can be supplied to the AK7750's XTI pin as follows:

When one of the XTI Modes 0,1 and 2 is used, either connect a proper crystal oscillator between XTI and XTO pins or feed a clock of proper frequency to the XTI pin.

When a crystal oscillator is used: XTI Modes 0,1,2

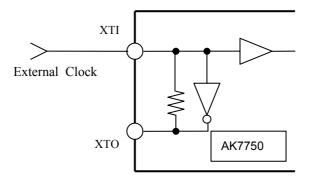

When XTI Mode 3 is used, feed a clock of proper frequency to the XTI pin.

When an external clock is used : XTI Mode 3

# b) BITCLK(\_I) Selection at CKSX = "L" (`SMODE="L")

BCK Modes 0,1,2 are used when bit clock (BITCLK\_I,BITCLK) is used instead of XTI. A clock fed on the BITCLK-I pin is directly frequency-multiplied by the PLL and a master clock (MCLK) is generated.

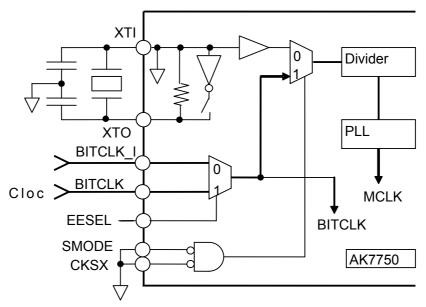

Internal connection image diagram

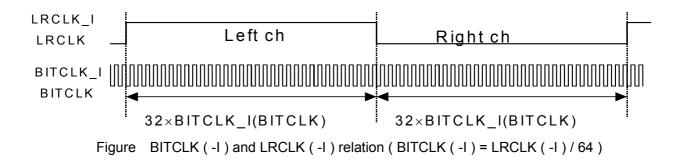

Input on BITCLK(\_I) pin a divided-by-64 clock of the LRCLK(\_I) ( 64fs ). ( BITCLK( \_I) must be in synchronized with LRCLK (\_I)).

# ■ Modes vs. PLL Relation

# a) XTI Selection at CKSX = "H"

In the AK7750, the internal master clock MCLK usually runs at 36.864 MHz max. as shown below.

Figure Mode Set vs. MCLK (internal master clock) relation

# b) BITCLK( \_I) Selection at CKSX = "L" ( @SMODE = "L" )

In the AK7750, the internal master clock MCLK usually runs at 38.864 MHz max. as shown below.

Figure Mode Set vs. MCLK ( internal master clock ) relation

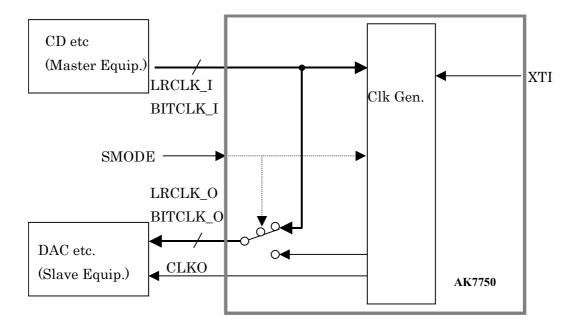

# 2) SMODE: Slave, Master Mode Select pin

Set the input /output of LRCLK and BITCLK.

a) Slave Mode : SMODE = "L "

#### • EESEL = " L "

LRCLK\_I (1fs) & BITCLK\_I (64fs) become inputs.

LRCLK\_I,BITCLK\_I are directly output on LRCLK\_O and BITCLK\_O respectively. Output can be set via a control register.

Note) 48fs can be input on BITCLK\_I pin for modes other than hands-free mode or when CKSX = "L" (64fs corresponds to hands-free mode and CKSX = "L").

At CKSX = "H", XTI and LRCLK\_I must be synchronized, but need not be in phase. At CKSX = "L", BITCLK\_I and LRCLK\_I must be synchronized.

# • EESEL = "H"

LRCLK (1fs) and BITCLK (64fs) become inputs.

At CKSX = "H", XTI and LRCLK must be synchronized, but need not be in phase.

At CKSX = "L", BITCLK and LRCLK must be synchronized.

Note) 48fs can be input on BITCLK pin except in hands-free mode (64fs corresponds to hands-free mode).

# b) Master Mode: SMODE = "H"

Master mode requires a clock input to XTI.

When a clock is applied to the XTI input, LRCLK (LRCLK\_O) and BITCLK (BITCLK\_O) are automatically generated by an XTI-synchronized internal counter.

No output is available on LRCLK (LRCLK\_O) and BITCLK (BITCLK\_O) pins during an initial reset (INIT\_RESET = "L") or a system reset (INIT\_RESET = "H" and S\_RESET = "L").

# • EESEL = "L"

LRCLK\_O(1fs ) and BITCLK\_O( 64fs ) are output.

When LRCLK\_I and BITCLK\_I pins are not connected to any external circuit, these pins should be tied low ( "L" level, (DVSS)).

When the AK7750 is used in Analog-to-Analog fashion and when LRCLK\_O and BITCLK\_O are not required (SDIN and SDOUT pins are not used), BITCLK\_O and LRCLK\_O can be programmed by setting a control register.

#### • EESEL = "H"

LRCLK (1fs) and BITCLK (64fs) are output.

When the AK7750 is used in Analog-to-Analog fashion and when LRCLK and BITCLK are not required (SDIN and SDOUT pins are not used), BITCLK\_O and LRCLK\_O can be programmed by setting a control register.

# c) SMODE Pin Switching

Setting the SMODE pin function after power-on should be performed either during an initial reset ( $INIT\_RESET = "L"$  and  $S\_RESET = "L"$ ), or during a clock reset ( $CK\_RESET = "L"$  and  $S\_RESET = "L"$ ).

Since switching between Slave and Master modes is controlled by the SMODE pin, an erroneous operation may occur if pin set changes take place under any conditions other than those described above.

In Slave mode operation, internal clock phase-synchronization is performed at the release of system reset (from  $S_RESET = "L"$  to "H"). It should be noted that switching to Slave mode in the middle of an operation may cause an erroneous results.

#### d) Corresponding Table of SMODE, CKSX and EESEL pins

| CKSX | SMODE | EESEL | selected CLK | note          |

|------|-------|-------|--------------|---------------|

| "H"  | "L"   | "L"   | XTI          |               |

| "H"  | "H"   | "L"   | XTI          |               |

| "H"  | "L"   | "H"   | XTI          |               |

| "H"  | "H"   | "H"   | XTI          |               |

| "L"  | "L"   | "L"   | BITCLK_I     |               |

| "L"  | "L"   | "H"   | BITCLK       |               |

| "L"  | "H"   | "L"   | N/A          | not available |

| "L"  | "H"   | "H"   | N/A          | not available |

# (2) Control Register Settings

In the AK7750, control registers are programmed via the microprocessor interface. There are 8 registers in total. Each register is configured with 7 bits, but SCLK always requires 16 bit data clocks (8 bits for Command Code and 8 bits for DATA ).

The Register configuration is listed below. Each control register value is set when D0 is written. Control register writes are performed during a system reset ( $S_RESET = "L"$ ), but reads can be performed at any time during normal chip operation.

Control registers are initialized by an  $\overline{INIT}_{RESET} = "L"$ . They are not initialized by a system reset (S\_RESET = "L").

TEST: for testing purpose (set to "0")

X: The value "0" must be set with a write operation. Failure to do say will result in an unknown value during a read operation.

| Comr | nand | Name  | D7       | D6      | D5      | D4      | D3      | D2    | D1        | D0 | Default   |

|------|------|-------|----------|---------|---------|---------|---------|-------|-----------|----|-----------|

| Co   | de   |       |          |         |         |         |         |       |           |    |           |

| W    | R    |       |          |         |         |         |         |       |           |    |           |

| 60h  | 70h  | CONT0 | DFS2     | DFS1]   | DFS0    | DIF2    | DIF1    | DIF0  | CKRST     | Х  | 0000_000x |

| 62h  | 72h  | CONT1 | DATARAM  | RM      | BANK1   | BANK0   | CMP_N   | SS1   | SS0       | Х  | 0000_000x |

| 64h  | 74h  | CONT2 | PSAD     | OUT3E_N | OUT2E_N | OUT1E_N | NRDY    | TEST  | TEST      | Х  | 0000_000x |

| 66h  | 76h  | CONT3 | SWJX2    | SWJX1   | SWJX0_N | SWQ4    | SWIA    | SWQD  | SWEE      | Х  | 0000_000x |

| 68h  | 78h  | CONT4 | TEST     | CLKS1   | CLKS0   | CLKE_N  | BLCKE_N | OUT4E | TEST      | Х  | 0000_000x |

| 6Ah  | 7Ah  | CONT5 | HF_RST_N | HF      | PID     | SSDIN4  | SSDIN3  | OP1   | OP0       | Х  | 0000_000x |

| 6Ch  | 7Ch  | CONT6 | PSCODEC  | DAF     | SF1     | SF0     | SMUTE   | TEST  | TEST      | Х  | 0000_000x |

|      |      |       |          |         |         |         |         |       | (PLLSTBY) |    | _         |

| -    | DCh  | CONT7 | SRRQ     | CRCL    | TEST    | TEST    | TEST    | TEST  | TEST      | Х  | 0000_000x |

Note) Do not write other data values or addresses.

- 1. In order to prevent erroneous operation, write to the CONT0 and CONT5 registers only during a system reset (S\_RESET = "L").

- It is recommended that CONT1 ~ CONT4, CONT6 ~ CONT7 registers are also only written to at a system reset (S\_RESET ="L").

- 3. TEST means for testing, and 0 should be written.

- 4. Default means an initialized value, to which register is initialized by INIT\_RESET = "L".

# 1) CONT0 : Sampling Rate Selection and Interface Types

writing is possible only at a system reset ( $\overline{S}_{RESET} = "L"$ ).

| Comma | nd   | Name  | D7   | D6   | D5   | D4   | D3   | D2   | D1    | D0 | Default   |

|-------|------|-------|------|------|------|------|------|------|-------|----|-----------|

| Code  |      |       |      |      |      |      |      |      |       |    |           |

| Write | Read |       |      |      |      |      |      |      |       |    |           |

| 60h   | 70h  | CONT0 | DFS2 | DFS1 | DFS0 | DIF2 | DIF1 | DIF0 | CKRST | Х  | 0000_000x |

# ① D7, D6, D5: DFS [2:0] Sampling Rate Set

#### fs: sampling frequency

| DFS  | DFS       | fs(kHz)     | DSP  | AD        | DA        |

|------|-----------|-------------|------|-----------|-----------|

| mode | [2:0]     |             | STEP | operation | operation |

| 0    | <u>0h</u> | 48(,44.1)   | 768  | 0         | 0         |

| 1    | 1h        | 96(,88.2)   | 384  | ×         | ×         |

| 2    | 2h        | 192(,176.4) | 192  | ×         | ×         |

| 3    | 3h        | 32(,29.4)   | 1152 | 0         | 0         |

| 4    | 7h        | 8           | 4608 | 0         | 0         |

note1) mode and sampling rate selection are only valid in modes  $0 \sim 4$ .

note2) when selecting modes 1 or 2, "1" must be set at PSAD (D7) bit of CONT2 register and at PSCODEC (D7) bit of CONT6 register. When CKSK is set to "L", operation follows the CSK0 and CSK1 setting.

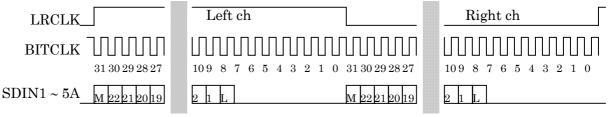

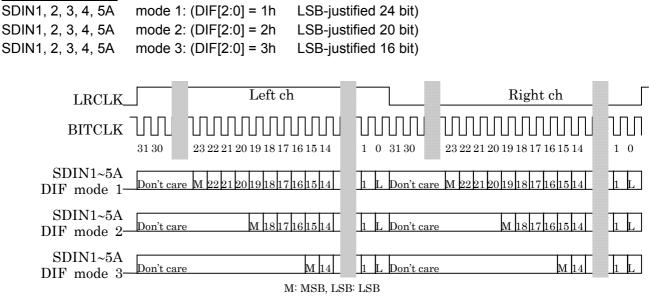

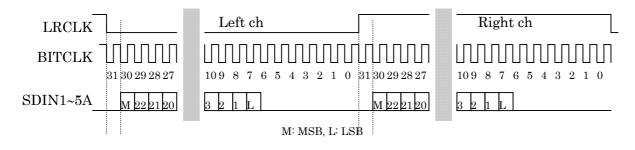

# <sup>(2)</sup> D4, D3, D2: DIF [2:0] Input Mode Selection of SDIN1, SDIN2, SDIN3H, SDIN4, SDIN5A

| DIF mode | SMODE          | DIF[2]   | DIF[1]   | DIF[0] |                             |

|----------|----------------|----------|----------|--------|-----------------------------|

| 0        | <u>"L","H"</u> | <u>0</u> | <u>0</u> | 0      | MSB-justified format(24bit) |

| 1        | "L","H"        | 0        | 0        | 1      | LSB-justified format(24bit  |

| 2        | "L","H"        | 0        | 1        | 0      | LSB-justified format(20bit) |

| 3        | "L","H"        | 0        | 1        | 1      | LSB-justified format(16bit) |

| 4        | "L","H"        | 1        | 0        | 0      | I2S format(24bit)           |

|          | "L"            | 1        | 0        | 1      | PCM1 SF(64fs only)          |

|          | "L"            | 1        | 1        | 0      | PCM2 LF(64fs only)          |

#### ③ D1:CKRST

0: operating condition

1: internal clock reset

When CKS2, CKS1, CKS0 and SMODE pins are switched or when the XTI input clock is changed, the new settings will take effect after toggling the CKRST from "1" to "0" (similar to CK\_RESET pin).

# ④ D1: Set "0"

note) under-lined values in  $\mathbb{O} \sim \mathbb{O}$  above indicate the default values

# 2) CONT1: RAM control

This register should be changed only during a system reset (<u>S\_RESET</u> ="L").

| Comma | ind Code | Name  | D7      | D6 | D5    | D4    | D3    | D2  | D1  | D0 | Default   |

|-------|----------|-------|---------|----|-------|-------|-------|-----|-----|----|-----------|

| Write | Read     |       |         |    |       |       |       |     |     |    |           |

| 62h   | 72h      | CONT1 | DATARAM | RM | BANK1 | BANK0 | CMP_N | SS1 | SS0 | Х  | 0000_000x |

#### ① D7:DATARAM DATARAM addressing mode selector

0: Ring addressing mode

1: Linear addressing mode

DATARAM is 256-words x 24-bits and has 2 addressing pointers (DP0, DP1).

Ring addressing mode: The starting address increments by 1 every sample period.

Linear addressing mode: The starting address is always the same, DP0 = 00h and DP1 = 80h.

#### **② D6:RM: Decompress bit mode**

<u>0: SIGN bit</u>

1: Random data