#### Features

- High Performance Programmable Logic Device 7.5 ns Max Propagation Delay Up to 166 MHz Operation 5 V ± 10% Operation

- Fully Compatible with Standard 22V10 Identical Functionality/Fuse-Map

- TTL Compatible Inputs and Outputs 10 μA Leakage Maximum

- Reprogrammable Tested 100% for Programmability

- High Reliability Proven UV Erasable CMOS Technology 2000 V ESD Protection 200 mA Latch-Up Protection

- Full Military, Commercial and Industrial Temperature Ranges

- Dual-In-Line and Surface Mount Packages with Standard Pinouts

#### OE PRODUCT TERMS PROGRAMMABLE 12 INTERCONNECT LOGIC 10 OUTPUT INPUT PINS AND OPTION I/O PINS OPTION COMBINATORIAL 8 TO 16 LOGIC ARRAY (UP T0 10 PRODUCT FLIP-FLOPS) TERMS

## High Speed UV Erasable Programmable Logic Device

### Description

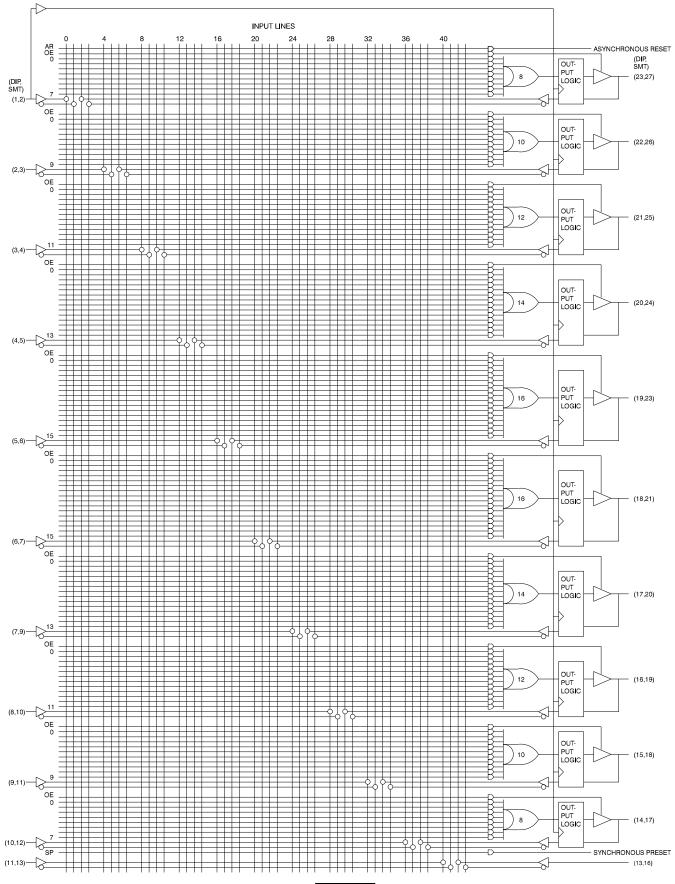

Logic Diagram

The AT22V10B is an ultra-high performance CMOS Programmable Logic Device (PLD). Speeds down to 7.5 ns and operation up to 166 MHz are offered. All pins offer a low $\pm$  10  $\mu$ A leakage.

The AT22V10B logic functionality is fully compatible with the standard 22V10. The 12 dedicated inputs and ten configurable I/O pins allow implementation of logic requiring up to 22 input signals. The AT22V10B also provides individual output enable product terms for each of the ten I/Os.

(continued)

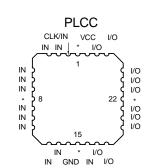

## **Pin Configurations**

| Pin Name | Function               |

|----------|------------------------|

| CLK/IN   | Clock and Logic Input  |

| IN       | Logic Inputs           |

| I/O      | Bidirectional Buffers  |

| *        | No Internal Connection |

| VCC      | +5 V Supply            |

1-110

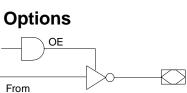

# **Output Options** OE

То

Output

From Output

I/O

$\geq$

I/O

OE

From

Logic

Option

| Temperature Under Bias55°C to +125°C                                                                 |

|------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                    |

| Voltage on Any Pin with Respect to Ground                                                            |

| Voltage on Input Pins<br>with Respect to Ground<br>During Programming2.0 V to +14.0 V <sup>(1)</sup> |

| Programming Voltage with Respect to Ground2.0 V to +14.0 $V^{(1)}$                                   |

| Integrated UV Erase Dose                                                                             |

#### **Absolute Maximum Ratings\***

Register preload simplifies testing. A security fuse prevents unauthorized copying of programmed fuse patterns.

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note:

1. Minimum voltage is -0.6 V dc which may undershoot to -2.0 V for pulses of less than 20 ns. Maximum output pin voltage is V<sub>CC</sub>+0.75 V dc which may overshoot to +7.0 V for pulses of less than 20 ns.

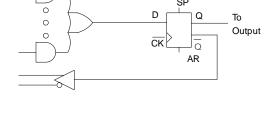

#### **Description** (Continued)

The AT22V10B incorporates a variable product term architecture. Each output is allocated from eight to 16 product terms, which allows highly complex logic functions to be realized.

The AT22V10B includes two additional product terms to provide synchronous preset and asynchronous reset. These terms

**Logic Options**

0

0

0

Logic

Option

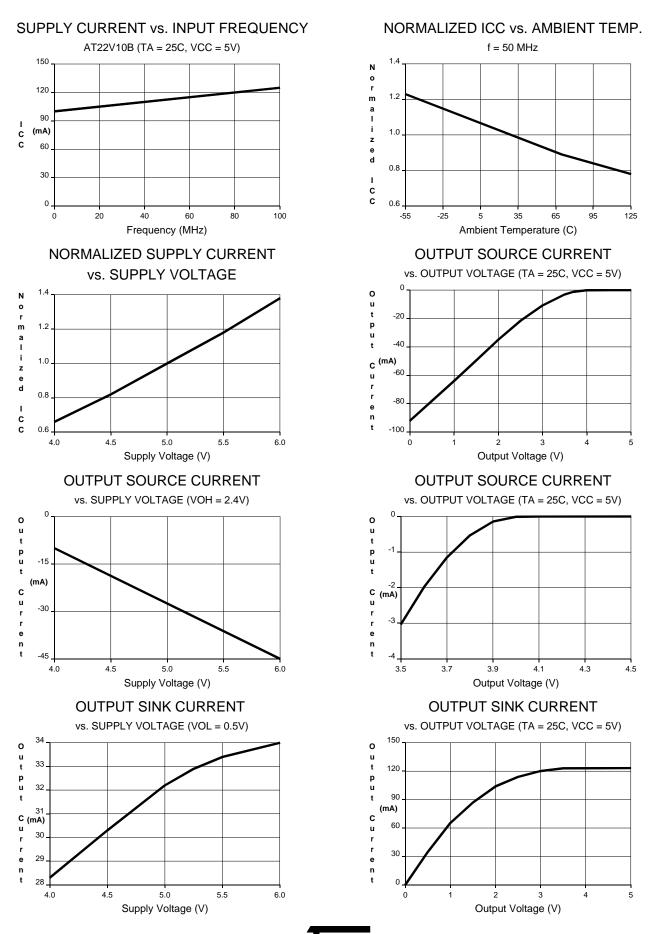

## **D.C. and A.C. Operating Conditions**

|                              | Commercial<br>AT22V10B<br>-7 | Commercial<br>AT22V10B<br>-10 | Industrial<br>AT22V10B<br>-10 | Military<br>AT22V10B<br>-10 |

|------------------------------|------------------------------|-------------------------------|-------------------------------|-----------------------------|

| Operating Temperature (Case) | 0°C - 70°C                   | 0°C - 70°C                    | -40°C - 85°C                  | -55°C - 125°C               |

| V <sub>CC</sub> Power Supply | $5 \text{ V} \pm 5\%$        | $5~V\pm10\%$                  | $5~V\pm10\%$                  | $5~V\pm10\%$                |

#### **D.C.** Characteristics

| Symbol                   | Parameter                    | Condition                                                                       |                                                 |            |      | Max                   | Units |

|--------------------------|------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|------------|------|-----------------------|-------|

| ILI                      | Input Load Current           | $V_{IN} = -0.1 V$ to $V_{CC}$                                                   | $V_{IN} = -0.1 \text{ V to V}_{CC}+1 \text{ V}$ |            |      |                       | μA    |

| Ilo                      | Output Leakage Current       | $V_{OUT} = -0.1 V \text{ to } V_{OUT}$                                          | c+0.1 V                                         |            |      | 10                    | μA    |

| Icc Power Supply Current |                              |                                                                                 |                                                 |            | 140  | mA                    |       |

|                          |                              |                                                                                 |                                                 | Ind., Mil. |      | 160                   | mA    |

| los (1)                  | Output Short Circuit Current | V <sub>OUT</sub> = 0.5 V                                                        |                                                 |            | -30  | -120                  | mA    |

| VIL                      | Input Low Voltage            |                                                                                 |                                                 |            | -0.6 | 0.8                   | V     |

| Vih                      | Input High Voltage           |                                                                                 |                                                 |            | 2.0  | V <sub>CC</sub> +0.75 | V     |

|                          |                              | $V_{IN} = V_{IH} \text{ or } V_{IL},$<br>$V_{CC} = MIN$                         | I <sub>OL</sub> = 16 mA                         | Com.,Ind.  |      | 0.5                   | V     |

| VOL                      | Output Low Voltage           |                                                                                 | I <sub>OL</sub> = 12 mA                         | Mil.       |      | 0.5                   | V     |

|                          |                              |                                                                                 | I <sub>OL</sub> = 24 mA                         | Com.       |      | 0.8                   | V     |

| Vон                      | Output High Voltage          | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> ,<br>V <sub>CC</sub> = MIN | I <sub>OH</sub> = -4.0 mA                       |            | 2.4  |                       | V     |

Notes: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec.

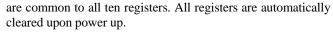

#### A.C. Waveforms<sup>(1)</sup>

Note: 1. Timing measurement reference is 1.5 V. Input AC driving levels are 0.0 V and 3.0 V, unless otherwise specified.

#### A.C. Characteristics

|                    |                                                          | AT22V10B-7 |     | AT22V10B-10 |     |     |     |       |

|--------------------|----------------------------------------------------------|------------|-----|-------------|-----|-----|-----|-------|

| Symbol             | Parameter                                                | Min        | Тур | Max         | Min | Тур | Max | Units |

| tPD                | Input or Feedback to Non-Registered Output               |            | 5   | 7.5         |     | 6   | 10  | ns    |

| t <sub>EA</sub>    | Input to Output Enable                                   |            | 5   | 7.5         |     | 6   | 10  | ns    |

| tER                | Input to Output Disable                                  |            | 5   | 7.5         |     | 6   | 10  | ns    |

| tcr <sup>(1)</sup> | Clock to Feedback                                        | 0          | 1   | 2           | 0   | 1   | 2   | ns    |

| tco                | Clock to Output                                          | 0          | 3.5 | 5.5         | 0   | 4   | 7   | ns    |

| ts                 | Input or Feedback Setup Time                             | 3.5        | 2   |             | 5   | 3   |     | ns    |

| tн                 | Hold Time                                                | 0          |     |             | 0   |     |     | ns    |

| tP                 | Clock Period                                             | 6          |     |             | 7   |     |     | ns    |

| twL <sup>(1)</sup> | Clock Width Low                                          | 3          |     |             | 3.5 |     |     | ns    |

| twn                | Clock Width High                                         | 3          |     |             | 3.5 |     |     | ns    |

|                    | External Feedback 1/(t <sub>S</sub> +t <sub>CO</sub> )   |            |     | 111         |     |     | 83  | MHz   |

| FMAX               | Internal Feedback 1/(ts + tcF)                           |            |     | 166         |     |     | 142 | MHz   |

|                    | No Feedback 1/(tp)                                       |            |     | 166         |     |     | 142 | MHz   |

| taw                | Asynchronous Reset Width                                 | 6          | 3   |             | 7   | 4   |     | ns    |

| t <sub>AR</sub>    | Asynchronous Reset, Synchronous Preset,<br>Recovery Time | 7          | 4   |             | 8   | 5   |     | ns    |

| tap                | Asynchronous Reset to Registered Output<br>Reset         | 6 10       |     |             | 8   | 14  | ns  |       |

Note: 1. This parameter is only sampled and is not 100% tested.

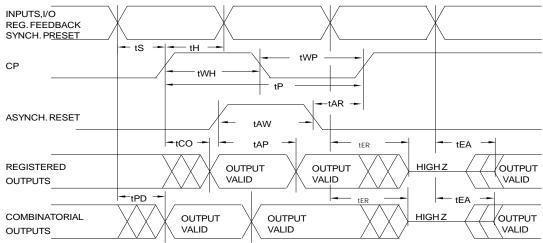

#### Input Test Waveforms and Measurement Levels

AT22V10B

tR, tF  $< 2 \ ns$   $\$  (10% to 90%)

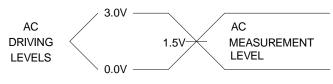

#### Output Test Loads:

AT22V10B

#### Functional Logic Diagram AT22V10B

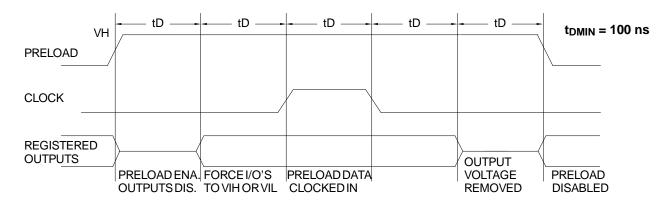

### Preload of Registered Outputs

The registers in the AT22V10B are provided with circuitry to allow loading of each register asynchronously with either a high or a low. This feature will simplify testing since any state can be forced into the registers to control test sequencing. A V<sub>IH</sub> level on the I/O pin will force the register high; a V<sub>IL</sub> will force it low, independent of the polarity bit (C0) setting. The preload state is entered by placing an 10.5-V to 12-V signal on pin 8 on DIPs, and pin 10 on SMPs. When the clock pin is pulsed high, the data on the I/O pins is placed into the ten registers.

| Level forced on<br>registered output pin<br>during preload cycle | Register state<br>after cycle |

|------------------------------------------------------------------|-------------------------------|

| VIH                                                              | High                          |

| VIL                                                              | Low                           |

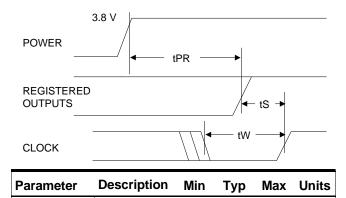

#### **Power Up Reset**

The registers in the AT22V10B are designed to reset during power up. At a point delayed slightly from  $V_{CC}$  crossing 3.8 V, all registers will be reset to the low state. The output state will depend on the polarity of the output buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the uncertainty of how  $V_{CC}$  actually rises in the system, the following conditions are required:

1) The V<sub>CC</sub> rise must be monotonic,

2) After reset occurs, all input and feedback setup times must be met before driving the clock pin high, and

3) The clock must remain stable during tPR.

1000

ns

600

Power-Up

Reset Time

#### **Pin Capacitance** $(f = 1 \text{ MHz}, T = 25^{\circ}\text{C})^{(1)}$

|                 | Тур | Max | Units | Conditions             |

|-----------------|-----|-----|-------|------------------------|

| C <sub>IN</sub> | 5   | 8   | pF    | $V_{IN} = 0 V$         |

| Соит            | 6   | 8   | pF    | V <sub>OUT</sub> = 0 V |

**t**PR

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

#### **Erasure Characteristics**

The entire fuse array of an AT22V10B is erased after exposure to ultraviolet light at a wavelength of 2537 Å. Complete erasure is assured after a minimum of 20 minutes exposure using 12,000  $\mu$ W/cm<sup>2</sup> intensity lamps spaced one inch away from the chip. Minimum erase time for lamps at other intensity ratings can be

AT22V10B

calculated from the minimum integrated erasure dose of 15 W-sec/cm<sup>2</sup>. To prevent unintentional erasure, an opaque label is recommended to cover the clear window on any UV erasable PLD which will be subjected to continuous fluorescent indoor lighting or sunlight.

AT22V10B

## **Ordering Information**

| tPD<br>(ns) | ts<br>(ns) | tco<br>(ns) | Ordering Code                                                                                                              | Package                                             | Operation Range                                               |

|-------------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 7.5         | 3.5        | 5.5         | AT22V10B-7DC<br>AT22V10B-7JC<br>AT22V10B-7PC                                                                               | 24DW3<br>28J<br>24P3                                | Commercial<br>(0°C to 70°C)                                   |

| 10          | 5          | 7           | AT22V10B-10DC<br>AT22V10B-10GC<br>AT22V10B-10JC<br>AT22V10B-10PC<br>AT22V10B-10SC                                          | 24DW3<br>24D3<br>28J<br>24P3<br>24S                 | Commercial<br>(0°C to 70°C)                                   |

|             |            |             | AT22V10B-10DI<br>AT22V10B-10GI<br>AT22V10B-10JI<br>AT22V10B-10PI<br>AT22V10B-10SI                                          | 24DW3<br>24D3<br>28J<br>24P3<br>24S                 | Industrial<br>(-40°C to 85°C)                                 |

|             |            |             | AT22V10B-10DM<br>AT22V10B-10GM<br>AT22V10B-10LM<br>AT22V10B-10NM                                                           | 24DW3<br>24D3<br>28LW<br>28L                        | Military<br>(-55°C to 125°C)                                  |

|             |            |             | AT22V10B-10DM/883<br>AT22V10B-10GM/883<br>AT22V10B-10LM/883<br>AT22V10B-10NM/883<br>AT22V10B-12LM/883<br>AT22V10B-12LM/883 | 24DW3<br>24D3<br>28LW<br>28L<br>28LW<br>28LW<br>28L | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| 10          | 5          | 7           | 5962-87539 06 LA<br>5962-87539 06 3X                                                                                       | 24DW3<br>28L                                        | Military/883C<br>(-55°C to 125°C)<br>Class B, Fully Compliant |

| Package Type |                                                                                |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|--|--|--|--|

| 24DW3        | 24 Lead, 0.300" Wide, Windowed, Ceramic Dual Inline Package (Cerdip)           |  |  |  |  |

| 24D3         | 24 Lead, 0.300" Wide, Non-Windowed (OTP), Ceramic Dual Inline Package (Cerdip) |  |  |  |  |

| 28J          | 28 Lead, Plastic J-Leaded Chip Carrier OTP (PLCC)                              |  |  |  |  |

| 28LW         | 28 Pad, Windowed, Ceramic Leadless Chip Carrier (LCC)                          |  |  |  |  |

| 28L          | 28 Pad, Non-Windowed, Ceramic Leadless Chip Carrier OTP (LCC)                  |  |  |  |  |

| 24P3         | 24 Lead, 0.300" Wide, Plastic Dual Inline Package OTP (PDIP)                   |  |  |  |  |

| 24S          | 24 Lead, 0.300" Wide, Plastic Gull Wing Small Outline OTP (SOIC)               |  |  |  |  |