## COP410C/COP411C/COP310C/COP311C Single-Chip CMOS Microcontrollers

## **General Description**

The COP410C, COP411C, COP310C, and COP311C fully static, single-chip CMOS microcontrollers are members of the COPSTM family, fabricated using double-poly, silicongate CMOS technology. These controller-oriented processors are complete microcomputers containing all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a variety of applications. Features include single supply operation, a variety of output configuration options, with an instruction set, internal architecture, and I/O scheme designed to facilitate keyboard input, display output, and BCD data manipulation. The COP411C is identical to the COP410C but with 16 I/O lines instead of 20. They are an appropriate choice for use in numerous human interface control environments. Standard test procedures and reliable high-density fabrication techniques provide the medium to large volume customers with a customized controller-oriented processor at a low end-

The COP310C/COP311C is the extended temperature range version of the COP410C/COP411C.

The COP404C should be used for exact emulation.

#### Features

- Lowest power dissipation (40 µW typical)

- Low cost

- Power-saving HALT Mode with Continue function

- Powerful instruction set

- 512 x 8 ROM, 32 x 4 RAM

- 20 I/O lines (COP410C)

- Two-level subroutine stack

- DC to 4 µs instruction time

- Single supply operation (2.4V to 5.5V)

- General purpose and TRI-STATE® outputs

- Internal binary counter register with MICROWIRE™ compatible serial I/O

- LSTTL/CMOS compatible in and out

- Software/hardware compatible with other members of the COP400 family

- Extended temperature (-40°C to +85°C) devices available

- The military temperature range devices (-55°C to +125°C) are specified on COP210C/211C data sheet.

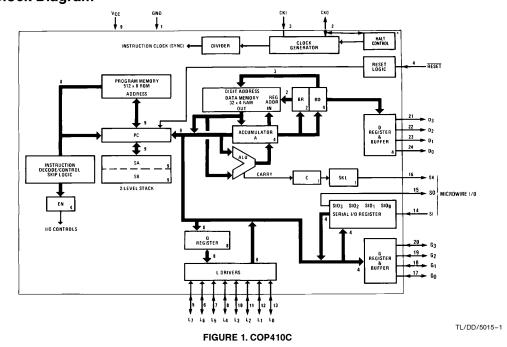

## **Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COPS™ and MICROWIRE™ are trademarks of National Semiconductor Corporation

## COP410C/COP411C

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 6V Voltage at Any Pin -0.3V to  $V_{CC}+0.3V$  Total Allowable Source Current 25 mA Total Allowable Sink Current 25 mA

Operating Temperature Range 0°C to +70°C

Storage Temperature Range -65°C to +150°C

Lead Temperature (Soldering, 10 sec.) 300°C

Note: Absolute maximum ratings indicate limits beyond

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## DC Electrical Characteristics $0^{\circ}C \le T_A \le 70^{\circ}C$ unless otherwise specified

| Parameter                                                                                              | Conditions                                                                                                                                                                                                                                                                                                                   | Min                                       | Max                 | Units                      |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------|----------------------------|

| Operating Voltage                                                                                      |                                                                                                                                                                                                                                                                                                                              | 2.4                                       | 5.5                 | V                          |

| Power Supply Ripple (Notes 5, 6)                                                                       |                                                                                                                                                                                                                                                                                                                              |                                           | 0.1 V <sub>CC</sub> | V                          |

| Supply Current (Note 1)                                                                                | $\begin{array}{c} V_{CC}=2.4V,t_{c}=125\;\mu\text{s}\\ V_{CC}=5.0V,t_{c}=16\;\mu\text{s}\\ V_{CC}=5.0V,t_{c}=4\;\mu\text{s}\\ (t_{c}\text{is instruction cycle time)} \end{array}$                                                                                                                                           |                                           | 80<br>500<br>2000   | μΑ<br>μΑ<br>μΑ             |

| HALT Mode Current (Note 2)                                                                             | $V_{CC}=5.0V, F_{IN}=0 \text{ kHz}$ $V_{CC}=2.4V, F_{IN}=0 \text{ kHz}$                                                                                                                                                                                                                                                      |                                           | 30<br>10            | μA<br>μA                   |

| Input Voltage Levels RESET, CKI Logic High Logic Low All Other Inputs                                  |                                                                                                                                                                                                                                                                                                                              | 0.9 V <sub>CC</sub>                       | 0.1 V <sub>CC</sub> | V<br>V                     |

| Logic High<br>Logic Low                                                                                |                                                                                                                                                                                                                                                                                                                              | 0.7 V <sub>CC</sub>                       | 0.2 V <sub>CC</sub> | V                          |

| Hi-Z Input Leakage                                                                                     |                                                                                                                                                                                                                                                                                                                              | -1                                        | +1                  | μΑ                         |

| Input Capacitance (Note 6)                                                                             |                                                                                                                                                                                                                                                                                                                              |                                           | 7                   | pF                         |

| Output Voltage Levels LSTTL Operation Logic High Logic Low CMOS Operation Logic High                   | Standard Outputs $V_{CC} = 5.0V \pm 10\%$ $I_{OH} = -25 \mu\text{A}$ $I_{OL} = 400 \mu\text{A}$ $I_{OH} = -10 \mu\text{A}$                                                                                                                                                                                                   | 2.7<br>V <sub>CC</sub> -0.2               | 0.4                 | V<br>V                     |

| Logic Low                                                                                              | $I_{OL} = 10 \mu\text{A}$                                                                                                                                                                                                                                                                                                    | V() 0.2                                   | 0.2                 | v                          |

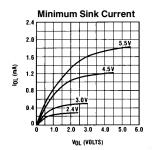

| Output Current Levels (Note 4) (Except CKO) Sink  Source (Standard Option) Source (Low Current Option) | V <sub>CC</sub> = 4.5V, V <sub>OUT</sub> = V <sub>CC</sub><br>V <sub>CC</sub> = 2.4V, V <sub>OUT</sub> = V <sub>CC</sub><br>V <sub>CC</sub> = 4.5V, V <sub>OUT</sub> = 0V<br>V <sub>CC</sub> = 2.4V, V <sub>OUT</sub> = 0V<br>V <sub>CC</sub> = 4.5V, V <sub>OUT</sub> = 0V<br>V <sub>CC</sub> = 2.4V, V <sub>OUT</sub> = 0V | 1.2<br>0.2<br>-0.5<br>-0.1<br>-30<br>-6   | -330<br>-80         | mA<br>mA<br>mA<br>μA<br>μA |

| CKO Current Levels (As Clock Out) Sink                                                                 | $V_{CC} = 4.5V$ , $CKI = V_{CC}$ , $V_{OUT} = V_{CC}$<br>$V_{CC} = 4.5V$ , $CKI = 0V$ , $V_{OUT} = 0V$                                                                                                                                                                                                                       | 0.3<br>0.6<br>1.2<br>-0.3<br>-0.6<br>-1.2 |                     | mA<br>mA<br>mA<br>mA<br>mA |

| Allowable Sink/Source<br>Current Per Pin (Note 4)                                                      |                                                                                                                                                                                                                                                                                                                              |                                           | 5                   | mA                         |

## COP410C/COP411C

## DC Electrical Characteristics (Continued)

| Parameter                                                                 | Conditions                                                                | Min | Max        | Units    |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|------------|----------|

| Allowable Loading on CKO (as HALT I/O pin)                                |                                                                           |     | 100        | pF       |

| Current Needed to<br>Override HALT <sup>3</sup><br>To Continue<br>To Halt | $V_{CC} = 4.5V, V_{IN} = 0.2 V_{CC}$ $V_{CC} = 4.5V, V_{IN} = 0.7 V_{CC}$ |     | 0.6<br>1.6 | mA<br>mA |

| TRI-STATE or Open Drain<br>Leakage Current                                |                                                                           | -2  | +2         | μΑ       |

Note 1: Supply current is measured after running for 2000 cycle times with a square-wave clock on CKI, CKO open, and all other pins pulled up to V<sub>CC</sub> with 5k resistors. See current drain equation on page 13.

Note 2: The Halt mode will stop CKI from oscillating in the RC and crystal configurations.

Note 3: When forcing HALT, current is only needed for a short time (approximately 200 ns) to flip the HALT flip-flop.

Note 4: SO output sink current must be limited to keep V<sub>OL</sub> less than 0.2 V<sub>CC</sub> when part is running in order to prevent entering test mode.

Note 5: Voltage change must be less than 0.5V in a 1 ms period.

Note 6: This parameter is only sampled and not 100% tested.

Note 7: Variation due to the device included.

## COP410C/COP411C

## AC Electrical Characteristics $0^{\circ}C \le T_{A} \le 70^{\circ}C$ unless otherwise specified

| Parameter                                | Conditions                               | Min      | Max | Units |  |

|------------------------------------------|------------------------------------------|----------|-----|-------|--|

| Instruction Cycle Time (t <sub>c</sub> ) | $V_{CC} \ge 4.5V$                        | 4        | DC  | μs    |  |

|                                          | $4.5V > V_{CC} \ge 2.4V$                 | 16       | DC  | μs    |  |

| Operating CKI ÷ 4 mode                   |                                          | DC       | 1.0 | MHz   |  |

| Frequency ÷8 mode                        | } V <sub>CC</sub> ≥ 4.5V                 | DC       | 2.0 | MHz   |  |

| ÷ 16 mode                                | J                                        | DC       | 4.0 | MHz   |  |

| ÷ 4 mode                                 |                                          | DC       | 250 | kHz   |  |

| ÷8 mode                                  | $\{ 4.5V > V_{CC} \ge 2.4V \}$           | DC       | 500 | kHz   |  |

| ÷ 16 mode                                | J                                        | DC       | 1.0 | MHz   |  |

| Instruction Cycle Time                   | $R = 30k \pm 5\%, V_{CC} = 5V$           |          |     |       |  |

| RC Oscillator <sup>7</sup>               | $C = 82 pF \pm 5\% ( \div 4 Mode)$       | 8        | 16  | μs    |  |

| Duty Cycle <sup>6</sup>                  | f <sub>I</sub> = 4 MHz                   |          | 60  | %     |  |

| Rise Time <sup>6</sup>                   | f <sub>I</sub> = 4 MHz External Clock    |          | 60  | ns    |  |

| Fall Time <sup>6</sup>                   | f <sub>I</sub> = 4 MHz External Clock    |          | 40  | ns    |  |

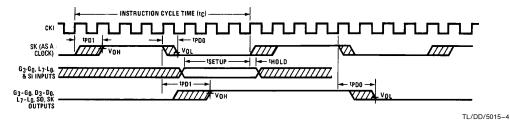

| Inputs (See Figure 3)                    |                                          |          |     |       |  |

| t <sub>SETUP</sub>                       | G Inputs )                               | tc/4+0.7 |     | μs    |  |

|                                          | SI Input $V_{CC} \ge 4.5V$               | 0.3      |     | μs    |  |

|                                          | All Others J                             | 1.7      |     | μs    |  |

| tHOLD                                    | $V_{CC} \ge 4.5V$                        | 0.25     |     | μs    |  |

|                                          | $V_{CC} \ge 2.4V$                        | 1.0      |     | μs    |  |

| Output Propagation                       |                                          |          |     |       |  |

| Delay                                    | $V_{OUT} = 1.5V, C_L = 100 pF, R_L = 5k$ |          |     |       |  |

| $t_{PD1}, t_{PD0}$ $V_{CC} \le 4.5V$     |                                          |          | 1.0 | μs    |  |

| t <sub>PD1</sub> , t <sub>PD0</sub>      | V <sub>CC</sub> ≤ 2.4V                   |          | 4.0 | μs    |  |

## COP310C/COP311C

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 6V Voltage at Any Pin -0.3V to  $V_{CC}+0.3V$  Total Allowable Source Current 25 mA Total Allowable Sink Current 25 mA

Operating Temperature Range  $-40^{\circ}\text{C to} + 85^{\circ}\text{C}$ Storage Temperature Range  $-65^{\circ}\text{C to} + 150^{\circ}\text{C}$ Lead Temperature (Soldering, 10 sec.)  $300^{\circ}\text{C}$

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## DC Electrical Characteristics $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ unless otherwise specified

| Parameter                                                                            | Conditions                                                                                                                                                                                                                                                                                                                                                                                                          | Min                               | Max                 | Units                      |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|----------------------------|

| Operating Voltage                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.0                               | 5.5V                | V                          |

| Power Supply Ripple (Notes 5, 6)                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   | 0.1 V <sub>CC</sub> | V                          |

| Supply Current (Note 1)                                                              | $V_{CC}=3.0$ V, $t_c=125$ μs $V_{CC}=5.0$ V, $t_c=16$ μs $V_{CC}=5.0$ V, $t_c=4$ μs ( $t_c$ is instruction cycle time)                                                                                                                                                                                                                                                                                              |                                   | 100<br>600<br>2500  | μΑ<br>μΑ<br>μΑ             |

| HALT Mode Current (Note 2)                                                           | $V_{CC}=5.0V$ , $F_{IN}=0$ kHz $V_{CC}=3.0V$ , $F_{IN}=0$ kHz                                                                                                                                                                                                                                                                                                                                                       |                                   | 50<br>20            | μA<br>μA                   |

| Input Voltage Levels RESET, CKI Logic High Logic Low All Other Inputs                |                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.9 V <sub>CC</sub>               | 0.1 V <sub>CC</sub> | V                          |

| Logic High<br>Logic Low                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7 V <sub>CC</sub>               | 0.2 V <sub>CC</sub> | V                          |

| Hi-Z Input Leakage                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                     | -2                                | +2                  | μΑ                         |

| Input Capacitance (Note 6)                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   | 7                   | pF                         |

| Output Voltage Levels LSTTL Operation Logic High Logic Low CMOS Operation Logic High | Standard Outputs $V_{CC} = 5.0V \pm 10\%$ $I_{OH} = -25 \ \mu A$ $I_{OL} = 400 \ \mu A$ $I_{OH} = -10 \ \mu A$                                                                                                                                                                                                                                                                                                      | 2.7<br>V <sub>CC</sub> -0.2       | 0.4                 | V<br>V                     |

| Logic Low Output Current Levels (Note 4) (Except CKO) Sink                           | $I_{OL} = 10 \mu A$ $V_{CC} = 4.5V, V_{OUT} = V_{CC}$                                                                                                                                                                                                                                                                                                                                                               | 1.2                               | 0.2                 | mA                         |

| Source (Standard<br>Option)<br>Source (Low<br>Current Option)                        | $\begin{array}{c} \text{V}_{\text{CC}} = 3.0\text{V}, \text{V}_{\text{OUT}} = \text{V}_{\text{CC}} \\ \text{V}_{\text{CC}} = 4.5\text{V}, \text{V}_{\text{OUT}} = 0\text{V} \\ \text{V}_{\text{CC}} = 3.0\text{V}, \text{V}_{\text{OUT}} = 0\text{V} \\ \text{V}_{\text{CC}} = 4.5\text{V}, \text{V}_{\text{OUT}} = 0\text{V} \\ \text{V}_{\text{CC}} = 3.0\text{V}, \text{V}_{\text{OUT}} = 0\text{V} \end{array}$ | 0.2<br>-0.5<br>-0.1<br>-30<br>-8  | -440<br>-200        | mA<br>mA<br>mA<br>μA<br>μA |

| CKO Current Levels (As Clock Out) Sink                                               | $V_{CC}=4.5V$ , CKI = $V_{CC}$ , $V_{OUT}=V_{CC}$ $V_{CC}=4.5V$ , CKI = $0V$ , $V_{OUT}=0V$                                                                                                                                                                                                                                                                                                                         | 0.3<br>0.6<br>1.2<br>-0.3<br>-0.6 |                     | mA<br>mA<br>mA<br>mA       |

| ÷ 16  Allowable Sink/Source Current Per Pin (Note 4)                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     | -1.2                              | 5                   | mA<br>mA                   |

## COP310C/COP311C

## DC Electrical Characteristics (Continued)

| Parameter                                                                 | Conditions                                                                | Min | Max        | Units    |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|------------|----------|

| Allowable Loading on CKO (as HALT I/O pin)                                |                                                                           |     | 100        | pF       |

| Current Needed to<br>Override HALT <sup>3</sup><br>To Continue<br>To Halt | $V_{CC} = 4.5V, V_{IN} = 0.2 V_{CC}$ $V_{CC} = 4.5V, V_{IN} = 0.7 V_{CC}$ |     | 0.8<br>2.0 | mA<br>mA |

| TRI-STATE or Open Drain<br>Leakage Current                                |                                                                           | -4  | +4         | μΑ       |

Note 1: Supply current is measured after running for 2000 cycle times with a square-wave clock on CKI, CKO open, and all other pins pulled up to V<sub>CC</sub> with 5k resistors. See current drain equation on page 13.

Note 2: The Halt mode will stop CKI from oscillating in the RC and crystal configurations.

Note 3: When forcing HALT, current is only needed for a short time (approximately 200 ns) to flip the HALT flip-flop.

Note 4: SO output sink current must be limited to keep V<sub>OL</sub> less than 0.2 V<sub>CC</sub> when part is running in order to prevent entering test mode.

Note 5: Voltage change must be less than 0.5V in a 1 ms period.

Note 6: This parameter is only sampled and not 100% tested.

Note 7: Variation due to the device included.

## COP310C/COP311C

## AC Electrical Characteristics $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ unless otherwise specified

| Parameter                                      | Conditions                                              | Min      | Max | Units |  |

|------------------------------------------------|---------------------------------------------------------|----------|-----|-------|--|

| Instruction Cycle Time (t <sub>c</sub> )       | $V_{CC} \ge 4.5V$                                       | 4        | DC  | μs    |  |

|                                                | $4.5V > V_{CC} \ge 3.0V$                                | 16       | DC  | μs    |  |

| Operating CKI ÷4 mode                          |                                                         | DC       | 1.0 | MHz   |  |

| Frequency ÷8 mode                              | } V <sub>CC</sub> ≥ 4.5V                                | DC       | 2.0 | MHz   |  |

| ÷ 16 mode                                      | J                                                       | DC       | 4.0 | MHz   |  |

| ÷ 4 mode                                       |                                                         | DC       | 250 | kHz   |  |

| ÷8 mode                                        | $\{ 4.5V > V_{CC} \ge 3.0V \}$                          | DC       | 500 | kHz   |  |

| ÷16 mode                                       | J                                                       | DC       | 1.0 | MHz   |  |

| Instruction Cycle Time                         | $R = 30k \pm 5\%, V_{CC} = 5V$                          |          |     |       |  |

| RC Oscillator <sup>7</sup>                     | $C = 82 pF \pm 5\% ( \div 4 Mode)$                      | 8        | 16  | μs    |  |

| Duty Cycle <sup>6</sup> f <sub>I</sub> = 4 MHz |                                                         | 40       | 60  | %     |  |

| Rise Time <sup>6</sup>                         | f <sub>I</sub> = 4 MHz External Clock                   |          | 60  | ns    |  |

| Fall Time <sup>6</sup>                         | f <sub>I</sub> = 4 MHz External Clock                   |          | 40  | ns    |  |

| Inputs (See Figure 3)                          |                                                         |          |     |       |  |

| <sup>t</sup> SETUP                             | G Inputs                                                | tc/4+0.7 |     | μs    |  |

|                                                | SI Input $V_{CC} \ge 4.5V$                              | 0.3      |     | μs    |  |

|                                                | All Others J                                            | 1.7      |     | μs    |  |

| tHOLD                                          | $V_{CC} \ge 4.5V$                                       | 0.25     |     | μs    |  |

|                                                | $V_{CC} \ge 3.0V$                                       | 1.0      |     | μs    |  |

| Output Propagation                             |                                                         |          |     |       |  |

| Delay                                          | $V_{OUT} = 1.5V, C_L = 100 \text{ pF}, R_L = 5\text{k}$ |          |     |       |  |

| t <sub>PD1</sub> , t <sub>PD0</sub>            | $V_{CC} \le 4.5V$                                       |          | 1.0 | μs    |  |

| $t_{PD1}$ , $t_{PD0}$                          | $V_{CC} \le 3.0V$                                       |          | 4.0 | μs    |  |

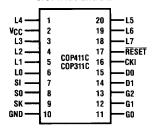

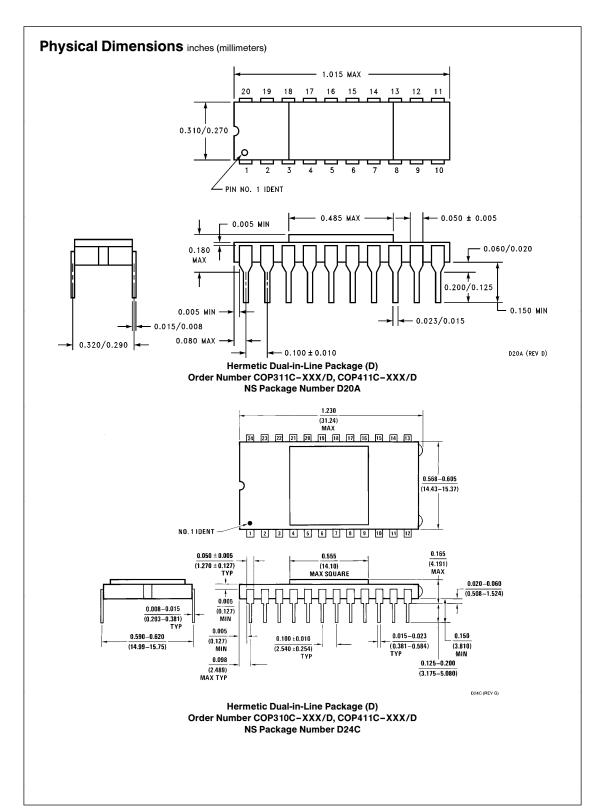

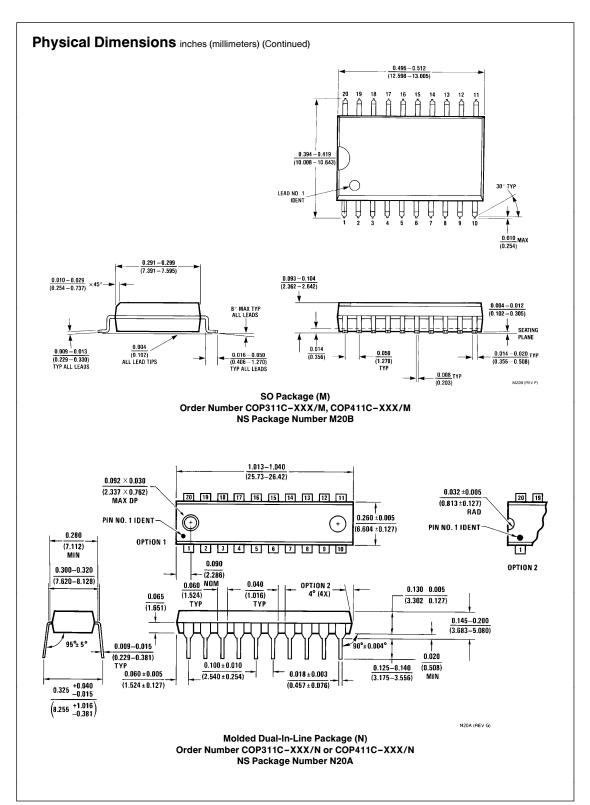

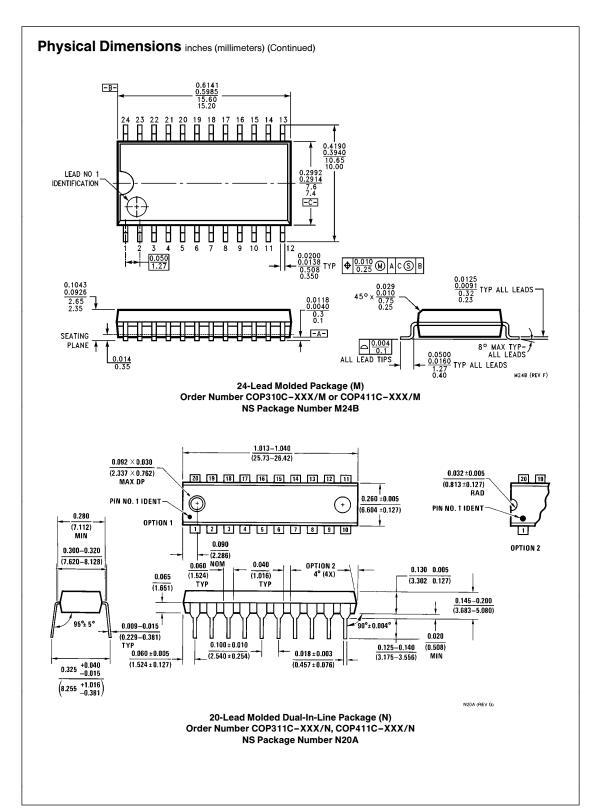

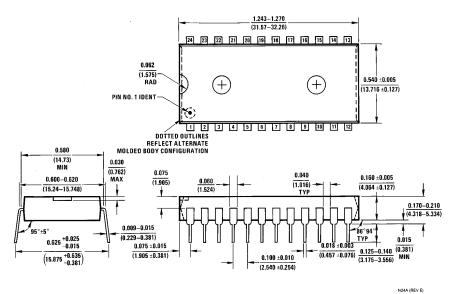

## **Connection Diagrams**

S.O. Wide and DIP

TL/DD/5015-2

Order Number COP311C-XXX/D or COP411C-XXX/D See NS Hermetic Package Number D20A (Prototype Package Only)

**Top View**

Order Number COP311C-XXX/N or COP411C-XXX/N See NS Molded Package Number N20A

Order Number COP311C-XXX/WM or COP411C-XXX/WM

See NS Surface Mount Package Number M20B

GND CKO 23 - D1 CKI -22 - D2 RESET -21 - D3 20 – G3 L7 COP410C COP310C 19 18 – G2 – G1 L6 6 L5 L4 17 - GO – SK VCC L3 - SO 10 15 - SI L2 -

S.O. Wide and DIP

TL/DD/5015-3 **Top View**

Order Number COP310C-XXX/D or COP410C-XXX/D See NS Hermetic Package Number D24C (Prototype Package Only)

Order Number COP310C-XXX/N or COP410C-XXX/N See NS Molded Package Number N24A

Order Number COP310C-XXX/WM or COP410C-XXX/WM See NS Surface Mount Package Number M24B

FIGURE 2

## **Pin Descriptions**

| Pin         | Description                                 | Pin      | Description                             |

|-------------|---------------------------------------------|----------|-----------------------------------------|

| $L_7-L_0$   | 8-bit bidirectional I/O port with TRI-STATE | SK       | Logic-controlled clock                  |

| $G_3-G_0$   | 4-bit bidirectional I/O port                |          | (or general purpose output)             |

|             | $(G_2-G_0$ for 20-pin package)              | CKI      | System oscillator input                 |

| $D_3 - D_0$ | 4-bit general purpose output port           | CKO      | Crystal oscillator output, or HALT mode |

|             | $(D_1 - D_0$ for 20-pin package)            |          | I/O port (24-pin package only)          |

| SI          | Serial input (or counter input)             | RESET    | System reset input                      |

| SO          | Serial output (or general purpose output)   | $V_{CC}$ | System power supply                     |

|             |                                             | GND      | System Ground                           |

## **Timing Diagram**

FIGURE 3. Input/Output (Divide-by-8 Mode)

## **Functional Description**

To ease reading of this description, only COP410C and/or COP411C are referenced; however, all such references apply equally to COP310C and/or COP311C, respectively.

A block diagram of the COP410C is given in *Figure 1*. Data paths are illustrated in simplified form to depict how the various logic elements communicate with each other in implementing the instruction set of the device. Positive logic is used. When a bit is set, it is a logic "1"; when a bit is reset, it is a logic "0".

#### **PROGRAM MEMORY**

Program memory consists of a 512-byte ROM. As can be seen by an examination of the COP410C/411C instruction set, these words may be program instructions, program data, or ROM addressing data. Because of the special characteristics associated with the JP, JSRP, JID, and LQID instructions, ROM must often be thought of as being organized into 8 pages of 64 words (bytes) each.

#### **ROM ADDRESSING**

ROM addressing is accomplished by a 9-bit PC register. Its binary value selects one of the 512 8-bit words contained in ROM. A new address is loaded into the PC register during each instruction cycle. Unless the instruction is a transfer of control instruction, the PC register is loaded with the next sequential 9-bit binary count value. Two levels of subroutine nesting are implemented by two 9-bit subroutine save registers, SA and SB.

ROM instruction words are fetched, decoded, and executed by the instruction decode, control and skip logic circuitry.

#### DATA MEMORY

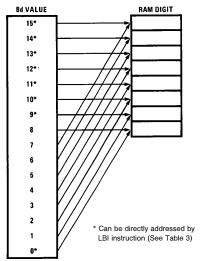

Data Memory consists of a 128-bit RAM, organized as four data registers of 8  $\times$  4-bit digits. RAM addressing is implemented by a 6-bit B register whose upper two bits (Br) selects one of four data registers and lower three bits of the 4-bit Bd select one of eight 4-bit digits in the selected data register. While the 4-bit contents of the selected RAM digit (M) are usually loaded into or from, or exchanged with, the A register (accumulator), they may also be loaded into the Q latches or loaded from the L ports. RAM addressing may also be performed directly by the XAD 3, 15 instruction. The Bd register also serves as a source register for 4-bit data sent directly to the D outputs.

The most significant bit of Bd is not used to select a RAM digit. Hence, each physical digit of RAM may be selected by two different values of Bd as shown in *Figure 4*. The skip condition for XIS and XDS instructions will be true if Bd changes between 0 to 15, but *not* between 7 and 8 (see Table III).

#### INTERNAL LOGIC

The internal logic of the COP410C/411C is designed to ensure fully static operation of the device.

The 4-bit A register (accumulator) is the source and destination register for most I/O, arithmetic, logic and data memory access operations. It can also be used to load the Bd portion of the B register, to load four bits of the 8-bit Q latch data and to perform data exchanges with the SIO register.

The 4-bit adder performs the arithmetic and logic functions of the COP410C/411C, storing its results in A. It also outputs the carry information to a 1-bit carry register, most often employed to indicate arithmetic overflow. The C register, in conjunction with the XAS instruction and the EN register, also serves to control the SK output. C can be outputted directly to SK or can enable SK to be a sync clock each instruction cycle time. (See XAS instruction and EN register description below.)

The G register contents are outputs to four general purpose bidirectional I/O ports.

The Q register is an internal, latched, 8-bit register, used to hold data loaded from RAM and A, as well as 8-bit data from ROM. Its contents are output to the L I/O ports when the L drivers are enabled under program control. (See LEI instruction.)

The eight L drivers, when enabled, output the contents of latched Q data to the L I/O ports. Also, the contents of L may be read directly into A and RAM.

TL/DD/5015-5

FIGURE 4. RAM Digit Address to Physical RAM Digit Mapping

### Functional Description (Continued)

The SIO register functions as a 4-bit serial-in/serial-out shift register or as a binary counter, depending upon the contents of the EN register. (See EN register description below.) Its contents can be exchanged with A, allowing it to input or output a continuous serial data stream. With SIO functioning as a serial-in/serial-out shift register and SK as a sync clock, the COP410C/411C is MICROWIRE compatible.

The D register provides four general purpose outputs and is used as the destination register for the 4-bit contents of Bd. The XAS instruction copies C into the SKL latch. In the counter mode, SK is the output of SKL; in the shift register mode, SK is a sync clock, inhibited when SKL is a logic "0". The EN register is an internal 4-bit register loaded under program control by the LEI instruction. The state of each bit of this register selects or deselects the particular feature associated with each bit of the EN register (EN3–EN0).

- 1. The least significant bit of the enable register, EN0, selects the SIO register as either a 4-bit shift register or as a 4-bit binary counter. With EN0 set, SIO is an asynchronous binary counter, decrementing its value by one upon each low-going pulse ("1" to "0") occurring on the SI input. Each pulse must be at least two instruction cycles wide. SK outputs the value of SKL. The SO output is equal to the value of EN3. With EN0 reset, SIO is a serial shift register, shifting left each instruction cycle time. The data present at SI is shifted into the least significant bit of SIO. SO can be enabled to output the most significant bit of SIO each instruction cycle time. (See 4, below.) The SK output becomes a logic-controlled clock.

- 2. EN 1 is not used, it has no effect on the COP410C/411C.

- With EN2 set, the L drivers are enabled to output the data in Q to the L I/O ports. Resetting EN2 disables the L drivers, placing the L I/O ports in a high impedance input state.

- 4. EN3, in conjunction with EN0, affects the SO output. With EN0 set (binary counter option selected), SO will output the value loaded into EN3. With EN0 reset (serial shift register option selected), setting EN3 enables SO as the output of the SIO shift register, outputting serial shifted data each instruction time. Resetting EN3 with the serial shift register option selected, disables SO as the shift register output; data continues to be shifted through SIO and can be exchanged with A via an XAS instruction but SO remains reset to "0".

#### INITIALIZATION

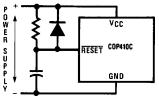

The internal reset logic will initialize the device upon power-up if the power supply rise time is less than 1 ms and if the operating frequency at CKI is greater than 32 kHz, otherwise the external RC network shown in Figure 5 must be connected to the  $\overline{\text{RESET}}$  pin. The  $\overline{\text{RESET}}$  pin is configured as a Schmitt trigger input. If not used, it should be connected to  $V_{CC}$ . Initialization will occur whenever a logic "0" is applied to the  $\overline{\text{RESET}}$  input, providing it stays low for at least three instruction cycle times.

When  $V_{CC}$  power is applied, the internal reset logic will keep the chip in initialization mode for up to 2500 instruction cycles. If the CKI clock is running at a low frequency, this could take a long time, therefore, the internal logic should be disabled by a mask option with initialization controlled solely by  $\overline{\text{RESET}}$  pin.

Note: If CKI clock is less than 32 kHz, the internal reset logic (Option 25 = 1) must be disabled and the external RC network must be present.

Upon initialization, the PC register is cleared to 0 (ROM address 0) and the A, B, C, D, EN, and G registers are cleared. The SK output is enabled as a SYNC output, providing a pulse each instruction cycle time. Data memory (RAM) is not cleared upon initialization. The first instruction at address 0 must be a CLRA (clear A register).

TL/DD/5015-6

$RC \ge 5 \times Power Supply Rise Time$ and  $RC \ge 100 \times CKI Period$

### FIGURE 5. Power-Up Clear Circuit

#### COP411C

If the COP410C is bonded as a 20-pin package, it becomes the COP411C, illustrated in *Figure 2*, COP410C/411C Connection Diagrams. Note that the COP411C does not contain D2, D3, G3, or CKO. Use of this option, of course, precludes use of D2, D3, G3, and CKO options. All other options are available for the COP411C.

TABLE I. Enable Register Modes — Bits EN0 and EN3

| EN0 | EN3 | SIO            | SI               | so     | SK                          |

|-----|-----|----------------|------------------|--------|-----------------------------|

| 0   | 0   | Shift Register | Input to Shift   | 0      | If SKL = 1, SK = clock      |

|     |     |                | Register         |        | If $SKL = 0$ , $SK = 0$     |

| 0   | 1   | Shift Register | Input to Shift   | Serial | If $SKL = 1$ , $SK = clock$ |

|     |     |                | Register         | out    | If $SKL = 0$ , $SK = 0$     |

| 1   | 0   | Binary Counter | Input to Counter | 0      | SK = SKL                    |

| 1   | 1   | Binary Counter | Input to Counter | 1      | SK = SKL                    |

### Functional Description (Continued)

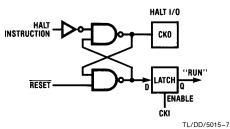

#### **HALT MODE**

The COP410C/411C is a *fully static* circuit; therefore, the user may stop the system oscillator at any time to halt the chip. The chip also may be halted by the HALT instruction or by forcing CKO high when it is used as a HALT I/O port. Once in the HALT mode, the internal circuitry does not receive any clock signal, and is therefore frozen in the exact state it was in when halted. All information is retained until continuing. The HALT mode is the minimum power dissipation state.

The HALT mode has slight differences depending upon the type of oscillator used.

#### a. 1-pin oscillator-RC or external

The HALT mode may be entered into by either program control (HALT instruction) or by forcing CKO to a logic "1" state.

The circuit may be awakened by one of two different methods:

- Continue function. By forcing CKO to a logic "0", the system clock is re-enabled and the circuit continues to operate from the point where it was stopped.

- 2) Restart. Forcing the RESET pin to a logic "0" will restart the chip regardless of HALT or CKO (see initialization)

#### b. 2-pin oscillator-crystal

The HALT mode may be entered into by program control (HALT instruction) which forces CKO to a logic "1" state. The circuit can be awakened only by the RESET function.

Halt I/O Port

#### **CKO Pin Options**

In a crystal-controlled oscillator system, CKO is used as an output to the crystal network. CKO will be forced high during the execution of a HALT instruction, thus inhibiting the crystal network. If a 1-pin oscillator system is chosen (RC or external), CKO will be selected as HALT and is an I/O

flip-flop which is an indicator of the HALT status. An external signal can override this pin to start and stop the chip. By forcing a high level to CKO, the chip will stop as soon as CKI is high and the CKO output will go high to keep the chip stopped. By forcing a low level to CKO, the chip will continue and CKO output will go low.

All features associated with the CKO I/O pin are available with the 24-pin package only.

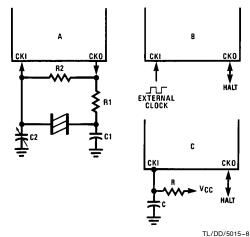

#### **OSCILLATOR OPTIONS**

There are three options available that define the use of CKI and CKO

- a. Crystal-Controlled Oscillator. CKI and CKO are connected to an external crystal. The instruction cycle time equals the crystal frequency divided by 16 (optionally by 8 or 4).

- External Oscillator. CKI is configured as LSTTL-compatible input accepting an external clock signal. The external frequency is divided by 16 (optionally by 8 or 4) to give the instruction cycle time. CKO is the HALT I/O port.

- c. RC-Controlled Oscillator. CKI is configured as a single pin RC-controlled Schmitt trigger oscillator. The instruction cycle equals the oscillation frequency divided by 4. CKO is the HALT I/O port.

The RC oscillator is not recommended in systems that require accurate timing or low current. The RC oscillator draws more current than an external oscillator (typically an additional 100  $\mu$ A at 5V). However, when the part halts, it stops with CKI high and the halt current is at the minimum.

FIGURE 6. COP410C Oscillator

#### **Crystal or Resonator**

#### RC-Controlled Oscillator

| Crystal   |      | Cor | nponent | Value |       |                   | Cycle    |                 |

|-----------|------|-----|---------|-------|-------|-------------------|----------|-----------------|

| Value     | R1   | R2  | C1 pF   | C2 pF | R     | С                 | Time     | V <sub>CC</sub> |

| 32 kHz    | 220k | 20M | 30      | 5-36  | 15k   | 82 pF             | 4-9 μs   | ≥4.5V           |

| 455 kHz   | 5k   | 10M | 80      | 40    | 30k   | 82 pF             | 8-16 μs  | $\geq$ 4.5V     |

| 2.096 MHz | 2k   | 1M  | 30      | 6-36  | 47k   | 100 pF            | 16-32 μs | 2.4 to 4.5      |

| 4.0 MHz   | 1k   | 1M  | 30      | 6-36  | Note: | $15k \le R$ :     | ≤ 150k,  |                 |

|           |      |     |         |       | 50 pf | $\leq C \leq 150$ | 0 pF     |                 |

## **COP410C/COP411C Instruction Set**

Table II is a symbol table providing internal architecture, instruction operand and operational symbols used in the instruction set table.

Table III provides the mnemonic, operand, machine code, data flow, skip conditions and description associated with each instruction in the COP410C/411C instruction set.

TABLE II. COP410C/411C Instruction Set Table Symbols

| Symbol  | Definition                                   | Symbol                      | Definition                                          |  |  |

|---------|----------------------------------------------|-----------------------------|-----------------------------------------------------|--|--|

| INTERNA | AL ARCHITECTURE SYMBOLS                      | INSTRUCTION OPERAND SYMBOLS |                                                     |  |  |

| Α       | 4-bit Accumulator                            | d                           | 4-bit Operand Field, 0-15 binary (RAM Digit Select) |  |  |

| В       | 6-bit RAM Address Register                   | r                           | 2-bit Operand Field, 0-3 binary (RAM Register       |  |  |

| Br      | Upper 2 bits of B (register address)         |                             | Select)                                             |  |  |

| Bd      | Lower 4 bits of B (digit address)            | а                           | 9-bit Operand Field, 0-511 binary (ROM Address)     |  |  |

| С       | 1-bit Carry Register                         | у                           | 4-bit Operand Field, 0-15 binary (Immediate Data)   |  |  |

| D       | 4-bit Data Output Port                       | RAM(s)                      | Contents of RAM location addressed by s             |  |  |

| EN      | 4-bit Enable Register                        | ROM(t)                      | Contents of ROM location addressed by t             |  |  |

| G       | 4-bit Register to latch data for G I/O Port  |                             |                                                     |  |  |

| L       | 8-bit TRI-STATE I/O Port                     | ODEBV.                      | TIONAL SYMBOLS                                      |  |  |

| M       | 4-bit contents of RAM Memory pointed to by B |                             |                                                     |  |  |

|         | Register                                     | +                           | Plus                                                |  |  |

| PC      | 9-bit ROM Address Register (program counter) | _                           | Minus                                               |  |  |

| Q       | 8-bit Register to latch data for L I/O Port  | $\rightarrow$               | Replaces                                            |  |  |

| SA      | 9-bit Subroutine Save Register A             | $\longleftrightarrow$       | Is exchanged with                                   |  |  |

| SB      | 9-bit Subroutine Save Register B             | =                           | Is equal to                                         |  |  |

| SIO     | 4-bit Shift Register and Counter             | Ā                           | The one's complement of A                           |  |  |

| SK      | Logic-Controlled Clock Output                | Φ                           | Exclusive-OR                                        |  |  |

|         |                                              | :                           | Range of values                                     |  |  |

|         |                                              |                             |                                                     |  |  |

### TABLE III. COP410C/411C Instruction Set

| Mnemonic  | Operand   | Hex<br>Code | Machine<br>Language Code<br>(Binary) | Data Flow                                               | Skip Conditions | Description                               |

|-----------|-----------|-------------|--------------------------------------|---------------------------------------------------------|-----------------|-------------------------------------------|

| ARITHMETI | C INSTRUC | TIONS       |                                      |                                                         |                 |                                           |

| ASC       |           | 30          | 0011   0000                          | $A + C + RAM(B) \rightarrow A$<br>Carry $\rightarrow C$ | Carry           | Add with Carry, Skip on Carry             |

| ADD       |           | 31          | 0011   0001                          | $A + RAM(B) \rightarrow A$                              | None            | Add RAM to A                              |

| AISC      | у         | 5-          | 0101 y                               | $A + y \rightarrow A$                                   | Carry           | Add immediate, Skip on Carry (y $\neq$ 0) |

| CLRA      |           | 00          | 0000   0000                          | 0 → A                                                   | None            | Clear A                                   |

| COMP      |           | 40          | 0100   0000                          | $\overline{A} \rightarrow A$                            | None            | One's complement of A to A                |

| NOP       |           | 44          | 0100   0100                          | None                                                    | None            | No Operation                              |

| RC        |           | 32          | 0011 0010                            | "0" → C                                                 | None            | Reset C                                   |

| sc        |           | 22          | 0010   0010                          | "1" → C                                                 | None            | Set C                                     |

| XOR       |           | 02          | 0000   0010                          | A ⊕ RAM(B) → A                                          | None            | Exclusive-OR RAM with A                   |

## Instruction Set (Continued)

TABLE III. COP410C/411C Instruction Set (Continued)

| TABLE III. COP410C/411C Instruction Set (Continued) |          |             |                                        |                                                                                                     |                       |                                             |  |

|-----------------------------------------------------|----------|-------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------|--|

| Mnemonic                                            | Operand  | Hex<br>Code | Machine<br>Language Code<br>(Binary)   | Data Flow                                                                                           | Skip Conditions       | Description                                 |  |

| TRANSFER                                            | OF CONTE | OL INS      | FRUCTIONS                              |                                                                                                     |                       |                                             |  |

| JID                                                 |          | FF          | 1111   1111                            | $PC_{7:0}$ ROM (PC <sub>8</sub> , A,M) $\rightarrow$                                                | None                  | Jump Indirect (Note 2)                      |  |

| JMP                                                 | a        | 6-<br>-     | 0110   000   a <sub>8</sub>            | a → PC                                                                                              | None                  | Jump                                        |  |

| JP                                                  | а        | -           | 1 a <sub>6:0</sub> (pages 2,3 only) or | $a \rightarrow PC_{6:0}$                                                                            | None                  | Jump within Page<br>(Note 1)                |  |

|                                                     |          | -           | 11 a <sub>5:0</sub> (all other pages)  | a → PC <sub>5:0</sub>                                                                               |                       |                                             |  |

| JSRP                                                | a        | -           | 10 a <sub>5:0</sub>                    | $PC + 1 \rightarrow SA \rightarrow SB$                                                              | None                  | Jump to Subroutine Page<br>(Note 2)         |  |

|                                                     |          |             |                                        | $\begin{array}{c} 010 \longrightarrow PC_{8:6} \\ a \longrightarrow PC_{5:0} \end{array}$           |                       |                                             |  |

| JSR                                                 | a        | 6-<br>-     | 0110   100   a <sub>8</sub>            | $\begin{array}{c} PC + 1 \longrightarrow SA \longrightarrow SB \\ a \longrightarrow PC \end{array}$ | None                  | Jump to Subroutine                          |  |

| RET                                                 |          | 48          | 0100   1000                            | $SB \rightarrow SA \rightarrow PC$                                                                  | None                  | Return from Subroutine                      |  |

| RETSK                                               |          | 49          | 0100   10011                           | $SB \rightarrow SA \rightarrow PC$                                                                  | Always Skip on Return | Return from Subroutine then Skip            |  |

| HALT                                                |          | 33<br>38    | 0011 0011                              |                                                                                                     | None                  | Halt processor                              |  |

| MEMORY R                                            | EFERENCE | INSTRU      | JCTIONS                                |                                                                                                     |                       |                                             |  |

| CAMQ                                                |          | 33<br>3C    | 0011 0011<br>0011 1100                 | $A \rightarrow Q_{7:4}$<br>RAM(B) $\rightarrow Q_{3:0}$                                             | None                  | Copy A, RAM to Q                            |  |

| CQMA                                                |          | 33<br>2C    | 0011 0011<br>0010 1100                 | $\begin{array}{c} Q_{7:4} \longrightarrow RAM(B) \\ Q_{3:0} \longrightarrow A \end{array}$          | None                  | Copy Q to RAM, A                            |  |

| LD                                                  | r        | -5          | 00   r   0101                          | $\begin{array}{c} RAM(B)  \longrightarrow  A \\ Br  \oplus  r  \longrightarrow  Br \end{array}$     | None                  | Load RAM into A<br>Exclusive-OR Br with r   |  |

| LQID                                                |          | BF          | 1011   1111                            | $\begin{array}{c} ROM(PC_8,A,M) \to Q \\ SA \to SB \end{array}$                                     | None                  | Load Q Indirect                             |  |

| RMB                                                 | 0        | 4C          | 0100   1100                            | $0 \rightarrow RAM(B)_0$                                                                            | None                  | Reset RAM Bit                               |  |

|                                                     | 1<br>2   | 45<br>42    | 0100 0101<br>0100 0010                 | $\begin{array}{c} 0 \longrightarrow RAM(B)_1 \\ 0 \longrightarrow RAM(B)_2 \end{array}$             |                       |                                             |  |

|                                                     | 3        | 43          | 0100 0011                              | $0 \rightarrow RAM(B)_3$                                                                            |                       |                                             |  |

| SMB                                                 | 0        | 4D          | 0100 1101                              | $1 \rightarrow RAM(B)_0$                                                                            | None                  | Set RAM Bit                                 |  |

|                                                     | 1<br>2   | 47<br>46    | 0100 0111<br>0100 0110                 | $\begin{array}{c} 1 \longrightarrow RAM(B)_1 \\ 1 \longrightarrow RAM(B)_2 \end{array}$             |                       |                                             |  |

|                                                     | 3        | 4B          | 0100 1011                              | $1 \rightarrow RAM(B)_3$                                                                            |                       |                                             |  |

| STII                                                | у        | 7-          | 0111 y                                 | $y \rightarrow RAM(B)$<br>Bd + 1 $\rightarrow$ Bd                                                   | None                  | Store Memory Immediat and Increment Bd      |  |

| X                                                   | r        | -6          | 00   r   0110                          | $\begin{array}{c} RAM(B) \longleftrightarrow A \\ Br \oplus r \longrightarrow Br \end{array}$       | None                  | Exchange RAM with A, Exclusive-OR Br with r |  |

| XAD                                                 | 3,15     | 23<br>BF    | 0010 0011                              | RAM(3,15) ←→ A                                                                                      | None                  | Exchange A with RAM (3,15)                  |  |

## Instruction Set (Continued)

TABLE III. COP410C/411C Instruction Set (Continued)

|                                           |                   |                            |                                                               | 1100/4110 Illistraction oc                                                                                                 | - (                                                                  |                                                             |  |  |  |  |

|-------------------------------------------|-------------------|----------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Mnemonic                                  | Operand           | Hex<br>Code                | Machine<br>Language Code<br>(Binary)                          | Data Flow                                                                                                                  | Skip Conditions                                                      | Description                                                 |  |  |  |  |

| MEMORY REFERENCE INSTRUCTIONS (Continued) |                   |                            |                                                               |                                                                                                                            |                                                                      |                                                             |  |  |  |  |

| XDS                                       | r                 | -7                         | 00   r   0111                                                 | $\begin{array}{c} RAM(B) \longleftrightarrow A \\ Bd - 1 \longrightarrow Bd \\ Br \oplus r \longrightarrow Br \end{array}$ | Bd decrements past 0                                                 | Exchange RAM with A and Decrement Bd Exclusive-OR Br with r |  |  |  |  |

| XIS                                       | r                 | -4                         | 00   r   0100                                                 | $\begin{array}{c} RAM(B) \longleftrightarrow A \\ Bd + 1 \longrightarrow Bd \\ Br \oplus r \longrightarrow Br \end{array}$ | Bd increments past 15                                                | Exchange RAM with A and Increment Bd Exclusive-OR Br with r |  |  |  |  |

| REGISTER REFERENCE INSTRUCTIONS           |                   |                            |                                                               |                                                                                                                            |                                                                      |                                                             |  |  |  |  |

| CAB                                       |                   | 50                         | 0101   0000                                                   | $A \rightarrow Bd$                                                                                                         | None                                                                 | Copy A to Bd                                                |  |  |  |  |

| CBA                                       |                   | 4E                         | 0100 1110                                                     | $Bd \rightarrow A$                                                                                                         | None                                                                 | Copy Bd to A                                                |  |  |  |  |

| LBI                                       | r,d               | -                          | $\frac{ 00   r     (d-1) }{(d=0,9:15)}$                       | $r,d \rightarrow B$                                                                                                        | Skip until not a LBI                                                 | Load B Immediate with r,d                                   |  |  |  |  |

| LEI                                       | у                 | 33<br>6-                   | 0011 0011<br>0010 y                                           | $y \rightarrow EN$                                                                                                         | None                                                                 | Load EN Immediate                                           |  |  |  |  |

| TEST INSTRUCTIONS                         |                   |                            |                                                               |                                                                                                                            |                                                                      |                                                             |  |  |  |  |

| SKC                                       |                   | 20                         | 0010 0000                                                     |                                                                                                                            | C = "1"                                                              | Skip if C is True                                           |  |  |  |  |

| SKE                                       |                   | 21                         | 0010 0001                                                     |                                                                                                                            | A = RAM(B)                                                           | Skip if A Equals RAM                                        |  |  |  |  |

| SKGZ                                      |                   | 33<br>21                   | 0011 0011 0010                                                |                                                                                                                            | $G_{3:0} = 0$                                                        | Skip if G is Zero<br>(all 4 bits)                           |  |  |  |  |

| SKGBZ                                     | 0<br>1<br>2<br>3  | 33<br>01<br>11<br>03<br>13 | 0011 0011<br>0000 0001<br>0001 0001<br>0000 0011<br>0010 0011 | 1st byte 2nd byte                                                                                                          | $G_0 = 0$ $G_1 = 0$ $G_2 = 0$ $G_3 = 0$                              | Skip if G Bit is Zero                                       |  |  |  |  |

| SKMBZ                                     | 0<br>1<br>2<br>3  | 01<br>11<br>03<br>13       | 0000 0001<br>0001 0001<br>0000 0011<br>0001 0011              |                                                                                                                            | $RAM(B)_0 = 0$<br>$RAM(B)_1 = 0$<br>$RAM(B)_2 = 0$<br>$RAM(B)_3 = 0$ | Skip if RAM Bit is Zero                                     |  |  |  |  |

| INPUT/OUT                                 | PUT INSTR         | UCTION                     | IS                                                            |                                                                                                                            |                                                                      |                                                             |  |  |  |  |

| ING                                       |                   | 33<br>2A                   | 0011 0011<br>0010 1010                                        | $G \rightarrow A$                                                                                                          | None                                                                 | Input G Ports to A                                          |  |  |  |  |

| INL                                       |                   | 33<br>2E                   | 0011 0011 0010 1110                                           | $ \begin{array}{c} L_{7:4} \longrightarrow RAM(B) \\ L_{3:0} \longrightarrow A \end{array} $                               | None                                                                 | Input L Ports to RAM, A                                     |  |  |  |  |

| OBD                                       |                   | 33<br>3E                   | 0011 0011                                                     | $Bd \rightarrow D$                                                                                                         | None                                                                 | Output Bd to D Outputs                                      |  |  |  |  |

| OMG                                       |                   | 33<br>3A                   | 0011 0011                                                     | RAM(B) → G                                                                                                                 | None                                                                 | Output RAM to G Ports                                       |  |  |  |  |

| XAS                                       |                   | 4F                         | 0100 1111                                                     | $A \longleftrightarrow SIO, C \to SKL$                                                                                     | None                                                                 | Exchange A with SIO                                         |  |  |  |  |

| Note 1. The                               | ID instruction of | llows a ium                | n while in subrouting pag                                     | on 2 or 2 to any POM location with                                                                                         | sin the two nego boundary of neg                                     | acc 2 or 2. The ID instruction                              |  |  |  |  |

Note 1: The JP instruction allows a jump, while in subroutine pages 2 or 3, to any ROM location within the two-page boundary of pages 2 or 3. The JP instruction, otherwise, permits a jump to a ROM location within the current 64-word page. JP may not jump to the last word of a page.

Note 2: A JSRP transfers program control to subroutine page 2 (0010 is loaded into the upper 4 bits of P). A JSRP may not be used when in pages 2 or 3. JSRP may not jump to the last word in page 2.

# Description of Selected Instructions

The following information is provided to assist the user in understanding the operation of several unique instructions and to provide notes useful to programmers in writing COP410C/411C programs.

#### **XAS INSTRUCTION**

XAS (Exchange A with SIO) exchanges the 4-bit contents of the accumulator with the 4-bit contents of the SIO register. The contents of SIO will contain serial-in/serial-out shift register or binary counter data, depending on the value of the EN register. An XAS instruction will also affect the SK output. (See Functional Description, EN Register). If SIO is selected as a shift register, an XAS instruction must be performed once every four instruction cycle times to effect a continuous data stream.

#### JID INSTRUCTION

JID (Jump Indirect) is an indirect addressing instruction, transferring program control to a new ROM location pointed to indirectly by A and M. It loads the lower eight bits of the ROM address register PC with the contents of ROM addressed by the 9-bit word,  $PC_8$ , A, M.  $PC_8$  is not affected by this instruction.

Note: JID uses two instruction cycles if executed, one if skipped.

#### **LQID INSTRUCTION**

LQID (Load Q Indirect) loads the 8-bit Q register with the contents of ROM pointed to by the 9-bit word PC $_8$ , A, M. LQID can be used for table look-up or code conversion such as BCD to 7-segment. The LQID instruction "pushes" the stack (PC + 1  $\rightarrow$  SA  $\rightarrow$  SB) and replaces the least significant eight bits of the PC as follows: A  $\rightarrow$  PC $_{7:4}$ , RAM(B)  $\rightarrow$  PC $_{3:0}$ , leaving PC $_8$  unchanged. The ROM data pointed to by the new address is fetched and loaded into the Q latches. Next, the stack is "popped" (SB  $\rightarrow$  SA  $\rightarrow$  PC), restoring the saved value of the PC to continue sequential program execution. Since LQID pushes SA  $\rightarrow$  SB, the previous contents of SB are lost.

Note: LQID uses two instruction cycles if executed, one if skipped.

#### **INSTRUCTION SET NOTES**

- a. The first word of a COP410C/411C program (ROM address 0) must be a CLRA (Clear A) instruction.

- Although skipped instructions are not executed, one instruction cycle time is devoted to skipping each byte of the skipped instruction. Thus all program paths take the same number of cycle times whether instructions are skipped or executed (except JID and LQID).

- c. The ROM is organized into eight pages of 64 words each. The program counter is a 9-bit binary counter, and will count through page boundaries. If a JP, JSRP, JID, or LQID instruction is located in the last word of a page, the instruction operates as if it were in the next page. For example: A JP located in the last word of a page will jump to a location in the next page. Also, a LQID or JID located in the last word in page 3 or 7 will access data in the next group of four pages.

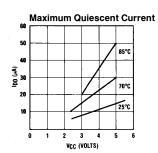

#### **POWER DISSIPATION**

The lowest power drain is when the clock is stopped. As the frequency increases so does current. Current is also lower at lower operating voltages. Therefore, to minimize power consumption, the user should run at the lowest speed and voltage that his application will allow. The user should take care that all pins swing to full supply levels to ensure that outputs are not loaded down and that inputs are not at some intermediate level which may draw current. Any input with a slow rise or fall time will draw additional current. A crystal- or resonator-generated clock will draw additional current. An RC oscillator will draw even more current since the input is a slow rising signal.

If using an external squarewave oscillator, the following equation can be used to calculate the COP410C current drain.

```

\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_

```

For example, at 5V V<sub>CC</sub> and 400 kHz (divide by 4),  $Ic = 10 + (5 \times 20 \times 0.4) + (5 \times 1280 \times 0.4/4)$

$$Ic = 10 + 40 + 640 = 690 \,\mu\text{A}$$

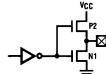

#### I/O OPTIONS

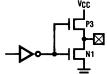

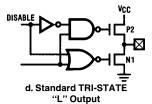

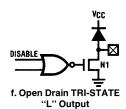

COP410C/411C outputs have the following optional configurations, illustrated in *Figure 7*:

- a. Standard. A CMOS push-pull buffer with an N-channel device to ground in conjunction with a P-channel device to  $V_{CC}$ , compatible with CMOS and LSTTL.

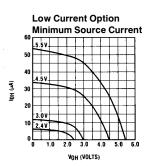

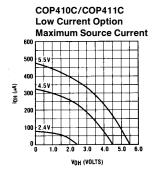

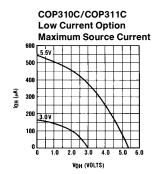

- b. Low Current. This is the same configuration as (a) above except that the sourcing current is much less.

- Open Drain. An N-channel device to ground only, allowing external pull-up as required by the user's application.

- d. Standard TRI-STATE L Output. A CMOS output buffer similar to (a) which may be disabled by program control.

- e. Low-Current TRI-STATE L Output. This is the same as (d) above except that the sourcing current is much less.

- f. Open-Drain TRI-STATE L Output. This has the N-channel device to ground only.

The SI and RESET inputs are Hi-Z inputs (Figure 7g).