# SONY

# **CXN1010**

# Bluetooth® Module

#### **Description**

The CXN1010 is a fully integrated Class 2 radio and baseband module conforming to ver. 1.1 of the Bluetooth<sup>®</sup> specification.

#### **Features**

- UART, USB, PCM codec, PIO, and AIO interfaces, enabling a wide range of applications.

- Small package: 10 × 14 × 1.5mm

- 8M-bit on-module flash memory

- Voltage regulator options: either on-module or external 1.8V regulator supported

- Based on the CXD3251GL, fully compatible with the Bluecore2-EXT from CSR

- Support for up to 7 slaves from a single master

- Channel quality driven data rate

#### **General Specifications**

• Product name: Bluetooth® module

• Antenna connector impedance:  $50\Omega$

• External interfaces: UART, USB, PCM, PIO, AIO

• Supply voltage: 2.3 to 3.6V\*

• Package dimensions: 10.0 × 14.0 × 1.5mm

\* An external 1.75 +0.15 V power supply is required for modules without internal voltage regulator (customer option).

Bluetooth® is a trademark owned by Bluetooth SIG, Inc. and licensed to Sony.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

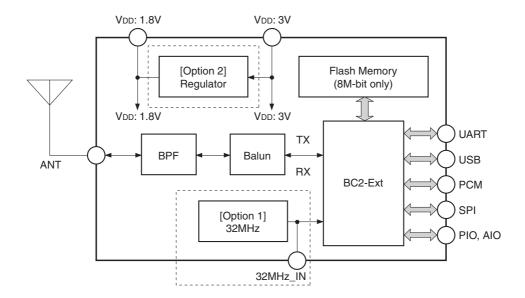

## **Block Diagram**

| Module type  | [Option 1]<br>X'tal | [Option 2]<br>Regulator | Supply VDD |

|--------------|---------------------|-------------------------|------------|

| CXN1010-3AAL | Mount               | Mount                   | 3V only    |

| CXN1010-2BAL | Mount               | No mount                | 1.8V only  |

| CXN1010-3BAL | Mount               | No mount                | 1.8V & 3V  |

| CXN1010-3CAL | No mount            | Mount                   | 3V only    |

| CXN1010-2DAL | No mount            | No mount                | 1.8V only  |

| CXN1010-3DAL | No mount            | No mount                | 1.8V & 3V  |

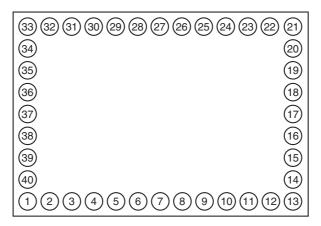

# Pin Configuration (Top View)

## **Pin Description**

| No. | Name                  | Туре                                                        | Description                                                                     |

|-----|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1   | GND                   | GND                                                         | Ground.                                                                         |

| 2   | RF                    | Analog                                                      | RF input/output.                                                                |

| 3   | GND                   | GND                                                         | Ground.                                                                         |

| 4   | PIO_4/<br>USB_ON      | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line or USB on.                                                |

| 5   | PIO_3/<br>USB_WAKE_UP | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line or output goes high to wake up PC when in USB mode.       |

| 6   | PIO_6                 | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                          |

| 7   | PIO_8                 | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                          |

| 8   | 32MHz_IN              | External clock input.<br>(Internal clock type is NC.)       | External clock input. A coupled capacitor is needed.                            |

| 9   | PIO_7                 | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                          |

| 10  | SPI_MISO              | CMOS output, tristatable with weak internal pull-down       | Serial Peripheral Interface data output.                                        |

| 11  | PIO_9                 | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                          |

| 12  | CE                    | CMOS input                                                  | 1.8V regulator control.<br>Regulator on at high.                                |

| 13  | GND                   | GND                                                         | Ground.                                                                         |

| 14  | SPI_CLK               | CMOS input with weak internal pull-down                     | Serial Peripheral Interface clock.                                              |

| 15  | VDD3.0                | Vdd                                                         | Supply voltage 3.0V. This pin need a decoupling capacitor that more than 2.2µF. |

| No. | Name                 | Туре                                                        | Description                                                                                     |

|-----|----------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 16  | PIO_10               | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                                          |

| 17  | AIO_0                | Bi-directional                                              | Programmable I/O line.                                                                          |

| 18  | USB-                 | Bi-directional                                              | USB data minus.                                                                                 |

| 19  | AIO_1                | Bi-directional                                              | Programmable I/O line.                                                                          |

| 20  | USB+                 | Bi-directional                                              | USB data plus.                                                                                  |

| 21  | GND                  | GND                                                         | Ground.                                                                                         |

| 22  | AIO_2                | Bi-directional                                              | Programmable I/O line.                                                                          |

| 23  | PIO_2                | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                                          |

| 24  | PIO_1                | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                                          |

| 25  | PD-RST               | CMOS input with 1kΩ pull-down                               | Reset at high. Input is debounced, so this pin should be high for 5ms or more to cause a reset. |

| 26  | PIO_0                | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                                          |

| 27  | PIO_11               | Bi-directional with programmable weak internal pull-up/down | Programmable I/O line.                                                                          |

| 28  | UART_RTS             | CMOS output, tristatable with weak internal pull-up         | Weak internal pull-up UART request to send, active low.                                         |

| 29  | UART_TX              | CMOS output                                                 | UART data output, active high.                                                                  |

| 30  | UART_RX              | CMOS input with weak internal pull-down                     | UART data input, active high.                                                                   |

| 31  | PCM_IN               | CMOS input with weak internal pull-down                     | PCM data input.                                                                                 |

| 32  | PCM_SYNC             | Bi-directional with 100kΩ pull-down                         | PCM data sync.                                                                                  |

| 33  | GND                  | GND                                                         | Ground.                                                                                         |

| 34  | PCM_OUT              | CMOS output, tristatable with weak internal pull-down       | PCM data output.                                                                                |

| 35  | PCM_CLK              | Bi-directional with weak internal pull-down                 | PCM data clock.                                                                                 |

| 36  | UART_CTS             | CMOS input with weak internal pull-down                     | UART clear to send, active low.                                                                 |

| 37  | SPI_MOSI             | Bi-directional with programmable weak internal pull-up/down | Serial Peripheral Interface data input.                                                         |

| 38  | PIO_5/<br>USB_DETACH | CMOS input with weak internal pull-up                       | Programmable I/O line or chip detaches from USB when this input is high.                        |

| 39  | SPI_CSB              | CMOS input with weak internal pull-down                     | Chip select for Serial Peripheral Interface, active low.                                        |

| 40  | VDD1.8               | VDD                                                         | Supply voltage 1.8V. This pin need a decoupling capacitor that more than 2.2µF.                 |

#### **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Item               |        | Min.  | Max.    | Unit |

|--------------------|--------|-------|---------|------|

| Storage temperat   | ure    | -20   | -20 +85 |      |

| Company of the sec | VDD1.8 | -0.40 | 1.90    | V    |

| Supply voltage     | VDD3.0 | -0.40 | 3.60    | V    |

# **Recommended Operating Conditions**

| Item             | Min.        | Max. | Unit |    |

|------------------|-------------|------|------|----|

| Operating temper | ature range | -20  | +85  | °C |

| Supply voltage   | VDD1.8      | 1.70 | 1.90 | V  |

| Supply voltage   | VDD3.0      | 2.30 | 3.60 | V  |

## **Input/Output Terminal Characteristics**

(Temperature: -20 to +85°C)

This I/O pin characteristics is the Bluetooth® IC specifications used internally of the CXN1010.

| Digital Terminals             | Min.          | Тур.                      | Max. | Unit         |    |

|-------------------------------|---------------|---------------------------|------|--------------|----|

| Input Voltage                 |               |                           |      |              |    |

| Vı∟ input logic level low     | VDD3.0 = 3.0V | -0.4                      |      | 0.8          | V  |

| VIL IIIput logic level low    | VDD1.8 = 1.8V | -0.4                      |      | 0.4          | V  |

| Vін input logic level high    |               | $0.7 \times V$ DD $3.0$   |      | VDD3.0 + 0.4 | ٧  |

| Output Voltage                |               |                           |      |              |    |

| Vo∟ output logic level low    | VDD3.0 = 3.0V | _                         | _    | 0.2          | V  |

| (lo = 4.0mA)                  | VDD1.8 = 1.8V | _                         | _    | 0.4          | V  |

| Voн output logic level high   | VDD3.0 = 3.0V | V <sub>DD</sub> 3.0 - 0.2 | _    | _            | ٧  |

| (lo = 4.0mA)                  | VDD1.8 = 1.8V | VDD1.8 - 0.4              | _    | _            | ٧  |

| Input and Tristate Current wi | th:           |                           |      |              |    |

| Weak pull-up                  |               | -5                        | -1   | 0            | μΑ |

| Weak pull-down                | 0             | 1                         | 5    | μΑ           |    |

| I/O pad leakage current       |               | -1                        | 0    | 1            | μΑ |

| Cı input capacitance          |               | 2.5                       | _    | 10           | рF |

# Input/Output Terminal Characteristics (continued)

| USB Terminals                                   | Min.                    | Min. Typ. Max. |                         |    |  |  |  |

|-------------------------------------------------|-------------------------|----------------|-------------------------|----|--|--|--|

| Input Threshold                                 |                         |                |                         |    |  |  |  |

| Vı∟ input logic level low                       | _                       | _              | $0.3 \times V$ DD $3.0$ | V  |  |  |  |

| Vін input logic level high                      | $0.7 \times V$ DD $3.0$ | _              | _                       | ٧  |  |  |  |

| Input Leakage Current                           |                         |                |                         |    |  |  |  |

| GND < VIN < VDD3.0                              | -1                      | _              | 1                       | μΑ |  |  |  |

| Cı input capacitance                            | 2.5                     | _              | 10                      | рF |  |  |  |

| Output Levels to Correctly Terminated USB Cable |                         |                |                         |    |  |  |  |

| Vo∟ input logic level low                       | 0                       | _              | 0.2                     | V  |  |  |  |

| Voн input logic level high                      | 2.8                     | _              | VDD3.0                  | ٧  |  |  |  |

| Auxiliary DAC, 8-bit Resolution     | Min.         | Тур.             | Max.         | Unit |

|-------------------------------------|--------------|------------------|--------------|------|

| Resolution                          | _            | _                | 8            | Bits |

| Average output step size            | 12.5         | 14.5             | 17           | mV   |

| Output Voltage                      | Mono         | otonic: 0.2 to V | DD3.0 - 0.2V |      |

| Voltage range (Io = 0)              | GND          | _                | VDD3.0       | ٧    |

| Current range                       | -10          | _                | 0.1          | mA   |

| Minimum output voltage (Io = 100μA) | 0            | _                | 0.2          | ٧    |

| Maximum output voltage (Io = 10mA)  | VDD3.0 - 0.3 | _                | VDD3.0       | V    |

| High impedance leakage current      | -1           | _                | 1            | μA   |

| Offset                              | -220         | _                | 120          | mV   |

| Integral non-linearity              | -2           | _                | 2            | LSB  |

| Starting time (50pF load)           | _            | _                | 10           | μs   |

| Setting time (50pF load)            | _            | _                | 5            | μs   |

| PD-RST Terminal                  | Min. | Тур. | Max. | Unit |

|----------------------------------|------|------|------|------|

| VDD falling threshold            | 1.40 | 1.50 | 1.60 | ٧    |

| V <sub>DD</sub> rising threshold | 1.50 | 1.60 | 1.70 | ٧    |

| Hysteresis                       | 0.05 | 0.10 | 0.15 | V    |

# **Input/Output Terminal Characteristics (continued)**

| CE Terminal                            | Min.  | Тур. | Max.   | Unit |

|----------------------------------------|-------|------|--------|------|

| Input Voltage                          |       |      |        |      |

| Vı∟ input logic level low              | _     | _    | 0.2    | V    |

| V <sub>IH</sub> input logic level high | 1.7   | _    | VDD3.0 | V    |

| Input Current                          |       |      |        |      |

| Iı∟ input logic level low              | -0.15 | _    | 0.15   | μA   |

| Ін input logic level high              | -0.15 | _    | 0.15   | μA   |

## **Radio Characteristics**

(Temperature: -20 to +85°C)

| Transmitter                         |              | Condition | Min. | Тур. | Max. | Unit         | Remark           |

|-------------------------------------|--------------|-----------|------|------|------|--------------|------------------|

| Output power (Average)              |              | N & ETC   | -6   | 0    | 4    | dBm          | Internal PA = 46 |

| Modulation characteristics          | delta-f1 avg | N & ETC   | 140  | 165  | 175  | kHz          | 11110000 mod.    |

| Modulation characteristics          | delta-f2 max | N & ETC   | 115  | 140  |      | kHz          | 1010 mod.        |

| Initial carrier frequency tolerance |              | N & ETC   |      | 10   | 75   | kHz          |                  |

|                                     | DH1          | N & ETC   |      | 12   | 25   | kHz          |                  |

| Carrier frequency drift             | DH3          | N & ETC   |      | 12   | 40   | kHz          |                  |

|                                     | DH5          | N & ETC   |      | 15   | 40   | kHz          |                  |

|                                     | DH1          | N & ETC   |      | 8    | 20   | kHz/<br>50µs |                  |

| Drift rate                          | DH3          | N & ETC   |      | 10   | 20   | kHz/<br>50µs |                  |

|                                     | DH5          | N & ETC   |      | 12   | 20   | kHz/<br>50µs |                  |

| 20dB bandwidth                      |              | N & ETC   |      | 900  | 1000 | kHz          |                  |

| Adjacent channel power              | M-N  = 2     | N & ETC   |      | -40  | -20  | dBm          |                  |

| Aujacent channel power              | M-N  ≥3      | N & ETC   |      | -50  | -40  | dBm          |                  |

|                                     | 30M-1G       | N & ETC   |      | -65  | -36  | dBm          |                  |

| Out-of-band spurious                | 1G-12.75G    | N & ETC   |      | -55  | -30  | dBm          |                  |

| emissions                           | 1.8G-1.9G    | N & ETC   |      | -75  | -47  | dBm          |                  |

|                                     | 5.15G-5.3G   | N & ETC   |      | -75  | -47  | dBm          |                  |

NTC: Normal Test Conditions +15 to +35°C, N & ETC: Normal & Extreme Test Conditions -20 to +85°C

# **Radio Characteristics (Continued)**

| Receiver                          |                              | Condition | Min. | Тур. | Max.        | Unit | Remark     |

|-----------------------------------|------------------------------|-----------|------|------|-------------|------|------------|

| Sensitivity (single slot packets) |                              | N & ETC   |      | -85  | -78         | dBm  | BER < 0.1% |

|                                   | co-ch.                       | NTC       |      | 9    | 11          | dB   |            |

|                                   | 1MHz                         | NTC       |      | -2   | 0           | dB   |            |

| C/I porformance                   | 2MHz                         | NTC       |      | -34  | -30         | dB   |            |

| C/I performance                   | ≥3MHz                        | NTC       |      | -43  | -40         | dB   |            |

|                                   | Image                        | NTC       |      | -18  | -9          | dB   |            |

|                                   | Image ± 1MHz                 | NTC       |      | -23  | -20         | dB   |            |

|                                   | 30-2000M                     | NTC       | -10  |      |             | dBm  |            |

|                                   | 800M-1000M                   | NTC       |      | 10   |             | dBm  |            |

| Blocking performance              | 1800M-1900M                  | NTC       |      | 10   |             | dBm  |            |

| Blocking performance              | 2000-2399M                   | NTC       | -27  |      |             | dBm  |            |

|                                   | 2498-3000M                   | NTC       | -27  |      |             | dBm  |            |

|                                   | 3G-12.75G                    | NTC       | -10  |      |             | dBm  |            |

| Inter modulation perforr          | Inter modulation performance |           | -39  | -30  |             | dBm  |            |

| Spurious emissions                | 30M-1G                       | N & ETC   |      | -78  | <b>-</b> 57 | dBm  |            |

| Spurious emissions                | 1G-12.75G                    | N & ETC   |      | -55  | -47         | dBm  |            |

| Maximum input level               |                              | NTC       | -20  | 2    | 5           | dBm  |            |

NTC: Normal Test Conditions, N & ETC: Normal & Extreme Test Conditions

## **Current Consumption**

(Temperature: -20 to +85°C)

| Mode                                        |           | Average | Peak | Unit | Remark          |

|---------------------------------------------|-----------|---------|------|------|-----------------|

| SCO connection HV3 (1s interval sniff mode) |           | 26      |      | mA   | Master or Slave |

| SCO connection HV1 (Master or Slave)        |           | 53      |      | mA   |                 |

| ACL data transfer 115.2Kbps UART (Master)   |           | 15.5    |      | mA   |                 |

| ACL data transfer 720Kbps USB               |           | 53      |      | mA   | Master or Slave |

| ACL connection, Sniff Mode 40ms interval    |           | 4       |      | mA   | 38.4Kbps BCSP   |

| ACL connection, Sniff Mode 1.28s interval   |           | 0.5     |      | mA   | 38.4Kbps BCSP   |

| Parked Slave, 1.28s beacon interval         |           | 0.6     |      | mA   | 38.4Kbps BCSP   |

| Deep sleep mode                             |           | 0.06    | 20   | mA   | 38.4Kbps BCSP   |

| Sleep mode                                  |           | 2.2     | 22   | mA   | 115.2Kbps H4    |

| Peak RF current during RF burst             | (0dBm Tx) | 57      | 68   | mA   |                 |

|                                             | (Rx)      | 47      | 70   | mA   |                 |

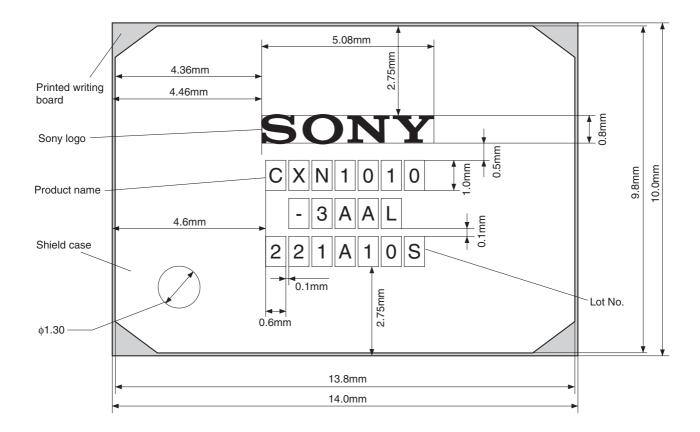

#### **Marking Contents**

- Sony logo: Fixed

- Product name: The string of alphanumerics "-3AAL" on the second line differs according to the module contents.

- Lot No.: It is displayed according to "The change-control marking rule of IC Lot No." (QR-3007-001).

(ex. "221A10S" on the third line means "20th, May, 2002. Lot No.10 producted in Senmaya".

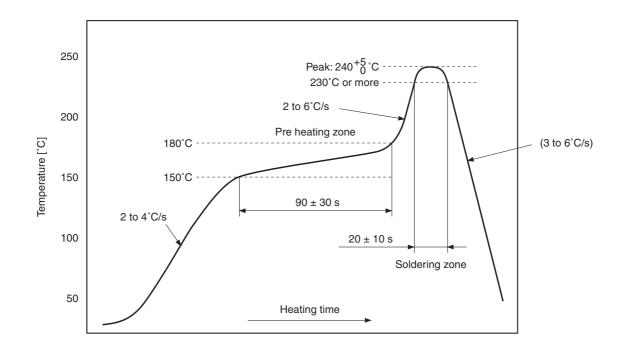

# **Recommended Temperature Profile for Unleaded Reflow Soldering**

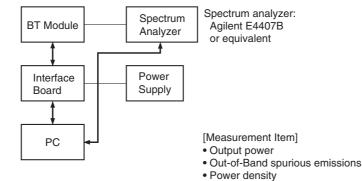

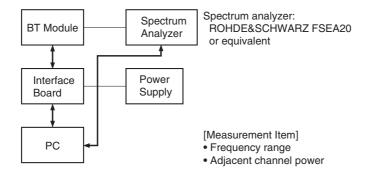

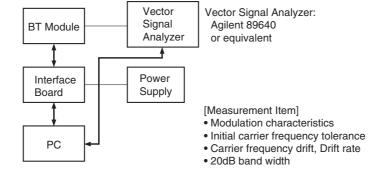

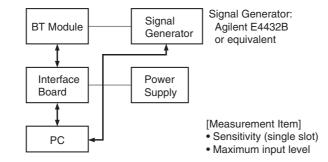

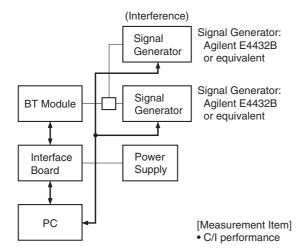

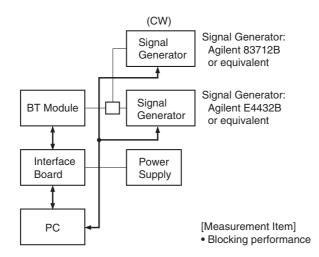

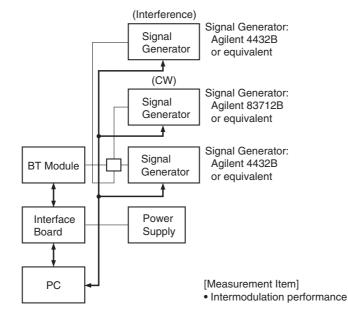

#### Radio Characteristics Measurement System Block Diagram (Application System Block Diagram)

## System A

#### System B

#### System C

## System D

## System E

## System F

## System G

\* For details of the contents below, see the specifications of the BlueCore 2-External (equivalent to the CXD3251GL) made by CSR.

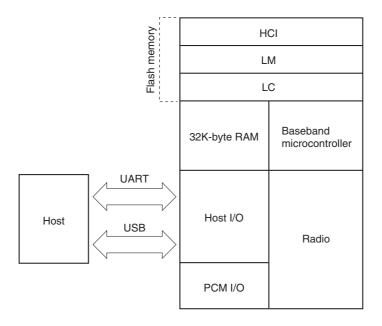

#### **Software Stack**

The CXN1010 features a 16-bit RISC microcontroller which runs a software stack complying with Bluetooth specifications ver. 1.1.

The following are the three software stack options to integrate into the CXN1010.

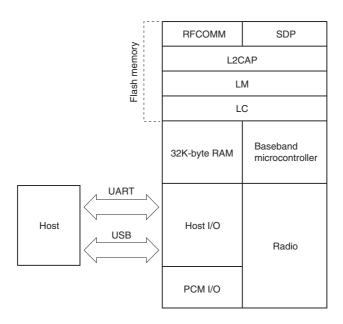

#### 1) HCI Stack

**HCI Stack Configuration**

The HCI stack enables the layers up to the host controller interface (HCI) to be executed by the on-module RISC microcontroller. It is considered to be the most common stack configuration with general-purpose capabilities. All layers above HCI are handled by the host processor.

#### 2) RFCOMM Stack

**RFCOMM Stack Configuration**

The RFCOMM stack enables the layers up to RFCOMM to be executed by the on-module RISC microcontroller. Then, the amount of processing is reduced on the host processor.

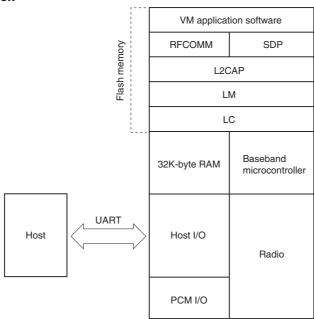

## 3) Virtual Machine Stack

**Virtual Machine Stack Configuration**

The Virtual Machine stack eliminates the need for a host processor. The applications and Bluetooth stack can be run on the integrated RISC microprocessor using a application execution environment called Virtual Machine (VM).

In order to develop applications, the BlueLab® software development environment (SDK) and Casira development kit supplied by CSR are required. Inquire for further details.

#### External Interfaces

#### **UART Interface**

The UART interface makes it easy to communicate with other serial devices using the RS-232 standard\*1.

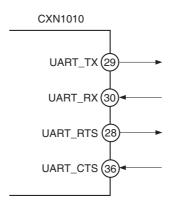

**UART Pins**

As shown in the figure above, four signals are used to execute the UART function. When the CXN1010 is connected to another digital device, data is transmitted between the two devices using the UART\_RX and UART\_TX signals. The remaining two low active signals, UART\_CTS and UART\_RTS, can be used for RS-232 hardware flow control. All the UART pins are configured as CMOS I/O pins. Their signal levels are 0V and VDD3.0. The baud rate, packet format and other UART configuration parameters are set using PS Tool or other BlueCore software.

**Note:** In order to communicate with UART at the maximum data rate using a standard PC, a serial port adapter card with acceleration must be installed in the PC.

\*1 The RS-232 protocol is used, but the voltage level is from 0V to VDD3.0. (An RS-232 transceiver IC must be externally attached.)

| Parameter           |         | Possible values       |  |  |

|---------------------|---------|-----------------------|--|--|

| Baud rate           | Minimo  | 1200 baud (≤2% error) |  |  |

|                     | Minimum | 9600 baud (≤1% error) |  |  |

|                     | Maximum | 1.5M baud (≤1% error) |  |  |

| Flow control        |         | RTS/CTS or none       |  |  |

| Parity              |         | None, odd or even     |  |  |

| Number of stop bits |         | 1 or 2                |  |  |

| Bits per channel    |         | 8                     |  |  |

**UART Settings**

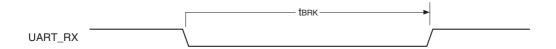

With the UART interface, the CXN1010 can be reset as soon as a break signal is received. As shown in the figure below, the break is identified by the continuous low logic level in the UART\_RX pin. Resetting occurs if tbrk is longer than the value defined by PSKEY\_HOST\_IO\_UART\_RESET\_TIMEOUT (0x1A4) persistent store key. The system can be initialized to a known status from the host using this function.

The CXN1010 can also send break characters that can be used for starting the host.

**Break Signal**

The frequently used baud rates and the values of the PSKEY\_UART\_BAUD\_RATE (0x204) persistent store key linked to those rates are shown in the table below. These standard values are not necessarily required conditions, and all baud rates within the range supported can be set by the persistent store key with the following equation.

| Baud rate | Persistent | Error |        |

|-----------|------------|-------|--------|

|           | Hex        | Dec   | EHOI   |

| 1200      | 0x0005     | 5     | 1.73%  |

| 2400      | 0x000A     | 10    | 1.73%  |

| 4800      | 0x0014     | 20    | 1.73%  |

| 9600      | 0x0027     | 39    | -0.82% |

| 19200     | 0x004F     | 79    | 0.45%  |

| 38400     | 0x009D     | 157   | -0.18% |

| 57600     | 0x00EC     | 236   | 0.03%  |

| 76800     | 0x013B     | 315   | 0.14%  |

| 115200    | 0x01D8     | 472   | 0.03%  |

| 230400    | 0x03B0     | 944   | 0.03%  |

| 460800    | 0x075F     | 1887  | -0.02% |

| 921600    | 0x0EBF     | 3775  | 0.00%  |

| 1382400   | 0x161E     | 5662  | -0.01% |

**Standard Baud Rates**

#### **USB** Interface

The USB pins of the CXN1010 support a full speed (12Mbps) USB interface. They enable direct drive of the USB cable, thereby obviating the need for an external USB transceiver. With this interface, the CXN1010 can operate as a USB unit and respond to requests from a PC or other master host controller. The interface supports both OHCI and UHCI standards. It also complies with Bluetooth specifications Ver.1.1 and part H2. Although USB is a system that is capable of both master and slave operations, the CXN1010 supports USB slave operations only.

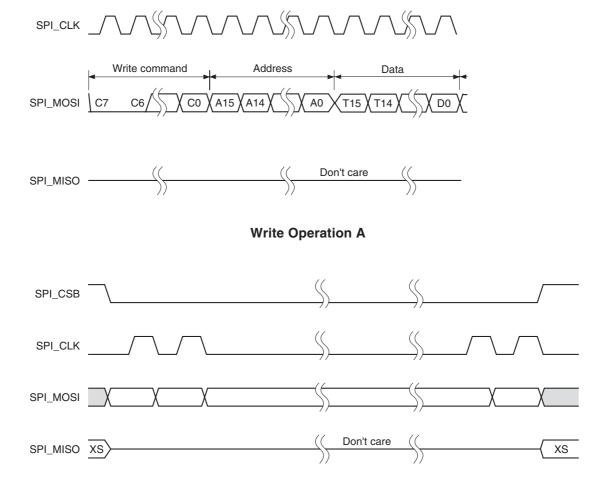

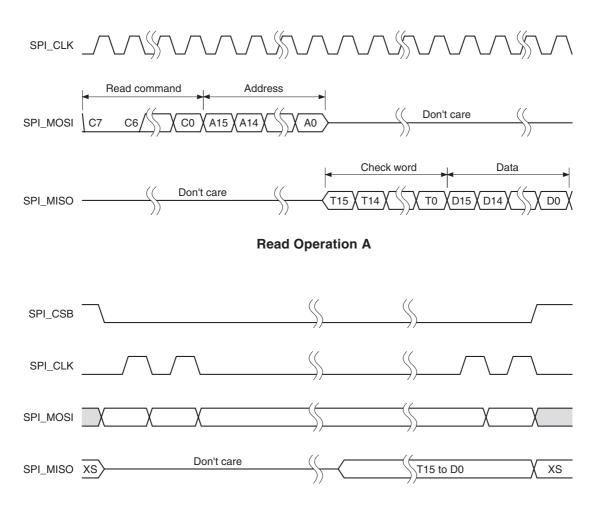

## **Serial Peripheral Interface (SPI)**

When data is sent or received through the SPI pins, the CXN1010 uses 16-bit data and 16-bit addresses. Through these pins, data is transmitted and received while the internal processor is operating and not operating. Data is written or read one word at a time unless the auto increment function is used to access blocks.

**Write Operation B**

**Read Operation B**

#### **PCM Interface**

The PCM interface of the CXN1010 supports the continuous transmission and reception of PCM data using hardware. This reduces the overhead of processors for wireless headset applications. The CXN1010 provides a bidirectional digital audio interface that is connected directly to the baseband layer of the on-chip firmware. The bidirectional digital audio interface does not pass the HCl protocol layer.

Data can be transmitted and received with one or more SCO connections using the hardware of the CXN1010. The PCM interface supports up to three SCO connections at a time.

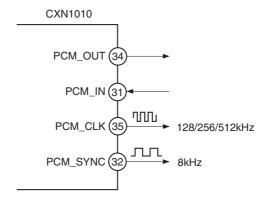

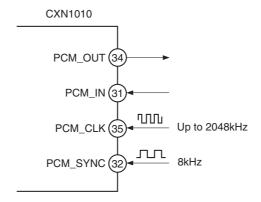

The CXN1010 can operate as the PCM interface master for generating an output clock of 128, 256 or 512kHz. Alternatively, when it is set to serve as the PCM interface slave, it can operate using an input clock up to 2048kHz. The CXN1010 can support many different clock types including long frame sync, short frame sync and GCI timings.

In terms of 8k per second sampling, the CXN1010 supports 13- or 16-bit linear, 8-bit  $\mu$ -Law and 8-bit A-Law companding sample formats. The PCM settings can be performed using the PSKEY\_PCM\_CONFIG (0x1B3) persistent store key.

#### **PCM Interface Master/Slave**

When the CXN1010 is set as the PCM interface master, PCM\_CLK and PCM\_SYNC are generated.

**PCM Interface Master**

When the CXN1010 is configured as the PCM interface slave, PCM\_CLK rates up to 2048kHz are accepted.

**PCM Interface Slave**

SONY

#### **PIO Port**

The parallel input/output (PIO) port serves as the general-purpose I/O interface of the CXN1010. It consists of nine programmable bidirectional I/O lines.

These programmable I/O lines can be accessed via either the installed application run by the CXN1010 or the private channel or manufacturer-designated HCI commands.

#### PIO[0]/RXEN

This multi-functional terminal is a programmable I/O line. Either the programmable I/O or control output for external LNA (if fitted).

#### PIO[1]/TXEN

This multi-functional terminal is a programmable I/O line. Either the programmable I/O or control output for external PA Class1 applications only.

## PIO[2]/USB\_PULL\_UP\*1

This multi-functional terminal is a programmable I/O line. Either the programmable I/O or PIO or USB pull-up (via  $1.5k\Omega$  resistor to USB\_D+).

#### PIO[3]/USB\_WAKE\_UP\*1

This multi-functional terminal is a programmable I/O line. Either the programmable I/O or USB\_WAKE\_UP function can be selected with the PSKEY\_USB\_PIO\_WAKEUP (0x2CF) persistent store key setting.

#### PIO[4]/USB\_ON\*1

This multi-functional terminal is a programmable I/O line. It can also be used as the USB\_ON function.

#### PIO[5]/USB\_DETACH\*1

This multi-functional terminal is a programmable I/O line. It can also be used as the USB\_DETACH function.

#### PIO[6]/CLK\_REQ

This is a multi-functional terminal whose function is determined by the persistent store keys. Using PSKEY\_CLOCK\_REQUEST\_ENABLE (0x246), it can be set to low when the CXN1010 is in deep sleep and to high when a clock is requested. If a shift in the timing in certain operation modes is to be avoided, the clock must be supplied within 4ms from the PIO[6] rising edge.

#### **PIO[7]**

Programmable I/O terminal

#### **PIO[8]**

Programmable I/O terminal

SONY CXN1010

## **PIO**[9]

Programmable I/O terminal

# PIO[10]

Programmable I/O terminal

## PIO[11]

Programmable I/O terminal

\*1 The USB function can be mapped in the software to any of the PIO terminals.

# AIO[0]

Programmable I/O line

## AIO[1]

Programmable I/O line

## **AIO**[2]

Programmable I/O line