# DM2502, DM2503, DM2504 Successive Approximation Registers

## **General Description**

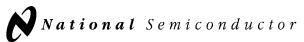

The DM2502, DM2503 and DM2504 are 8-bit and 12-bit TTL registers designed for use in successive approximation A/D converters. These devices contain all the logic and control circuits necessary in combination with a D/A converter to perform successive approximation analog-to-digital conversions.

The DM2502 has 8 bits with serial capability and is not expandable. The DM2503 has 8 bits and is expandable without serial capability. The DM2504 has 12 bits with serial capability and expandability.

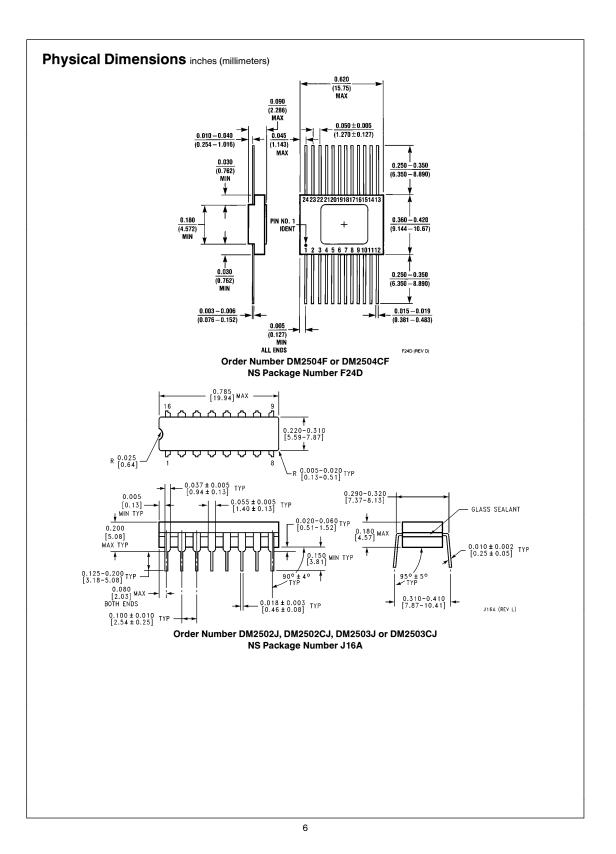

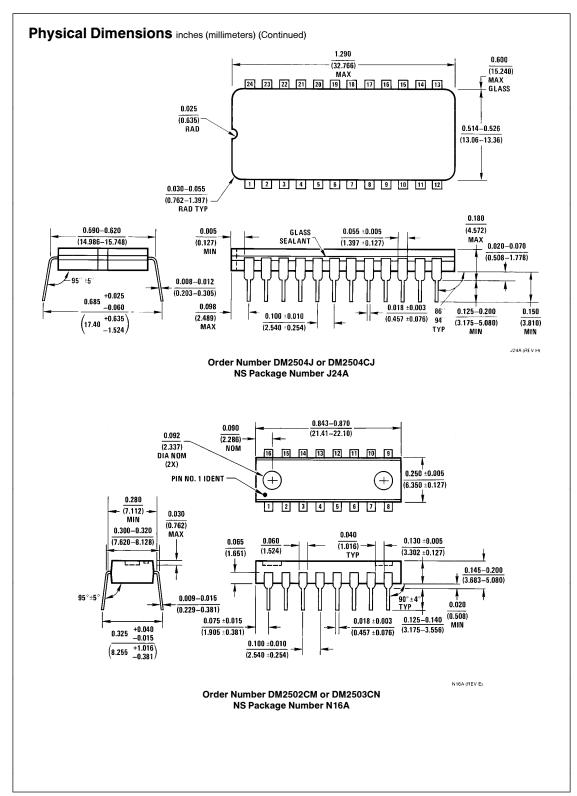

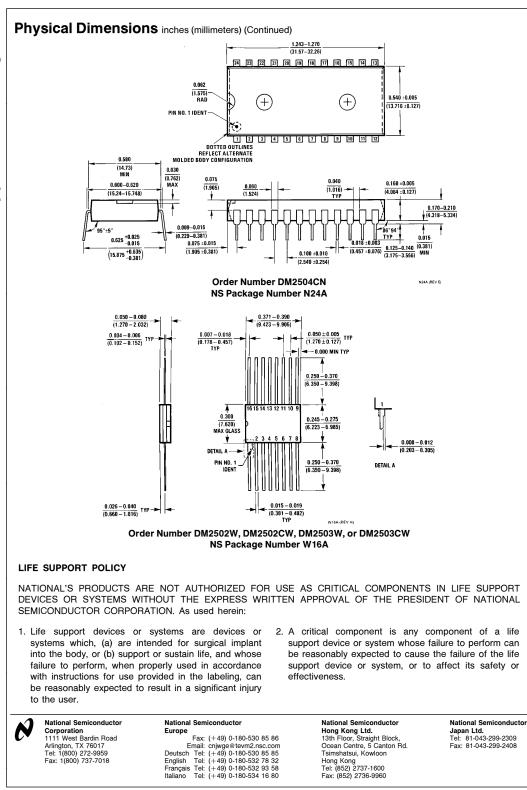

All three devices are available in ceramic DIP, ceramic flatpak, and molded Epoxy-B DIPs. The DM2502, DM2503 and

DM2504 operate over  $-55^\circ\text{C}$  to  $+125^\circ\text{C};$  the DM2502C, DM2503C and DM2504C operate over 0°C to  $+70^\circ\text{C}.$

#### Features

- Complete logic for successive approximation A/D converters

- 8-bit and 12-bit registers

- Capable of short cycle or expanded operation

- Continuous or start-stop operation

- Compatible with D/A converters using any logic code

- Active low or active high logic outputs

- Use as general purpose serial-to-parallel converter or ring counter

© 1995 National Semiconductor Corporation TL/F/5702

RRD-B30M115/Printed in U. S. A.

November 1995

# Absolute Maximum Ratings (Note 1)

| Supply Voltage                         | 7V                                |

|----------------------------------------|-----------------------------------|

| Input Voltage                          | 5.5V                              |

| Output Voltage                         | 5.5V                              |

| Storage Temperature Range              | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Lead Temperature (Soldering, 10 second | ls) 300°C                         |

| Operating Conditions                                            |      |      |       |  |  |  |  |  |  |  |

|-----------------------------------------------------------------|------|------|-------|--|--|--|--|--|--|--|

|                                                                 | Min  | Max  | Units |  |  |  |  |  |  |  |

| Supply Voltage, V <sub>CC</sub><br>DM2502C, DM2503C,<br>DM2504C | 4.75 | 5.25 | v     |  |  |  |  |  |  |  |

| DM2502, DM2503,<br>DM2504                                       | 4.5  | 5.5  | V     |  |  |  |  |  |  |  |

| Temperature, T <sub>A</sub>                                     |      |      |       |  |  |  |  |  |  |  |

0

-55

+70

+125

°C

°C

DM2502C, DM2503C,

DM2502, DM2503

DM2504C

DM2504

| Electrical Characteristics (Notes 2 and 3) V <sub>CC</sub> =5.0V, T <sub>A</sub> =25°C, C <sub>L</sub> =15 pF, unless otherwise sp. |

|-------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                                    | Conditions                                                                          | Min | Тур                        | Max                                | Units                      |  |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|----------------------------|------------------------------------|----------------------------|--|

| Logical ''1'' Input Voltage (V <sub>IH</sub> )                                                               | V <sub>CC</sub> = Min                                                               | 2.0 |                            |                                    | V                          |  |

| Logical ''1'' Input Current (I <sub>IH</sub> )<br>CP Input<br>D, Ē, Š Inputs<br>All Inputs                   | $V_{CC} = Max$ $V_{IH} = 2.4V$ $V_{IH} = 2.4V$ $V_{IH} = 5.5V$                      |     | 6<br>6                     | 40<br>80<br>1.0                    | μA<br>μA<br>mA             |  |

| Logical ''0'' Input Voltage (VIL)                                                                            | V <sub>CC</sub> = Min                                                               |     |                            | 0.8                                | V                          |  |

| Logical ''0'' Input Current (I <sub>IL</sub> )<br>CP, S Inputs<br>D, E Inputs                                | $V_{CC} = Max$ $V_{IL} = 0.4V$ $V_{IL} = 0.4V$                                      |     | -1.0<br>-1.0               | -1.6<br>-3.2                       | mA<br>mA                   |  |

| Logical "1" Output Voltage (V <sub>OH</sub> )                                                                | V <sub>CC</sub> =Min, I <sub>OH</sub> =0.48 mA                                      | 2.4 | 3.6                        |                                    | V                          |  |

| Output Short Circuit Current<br>(Note 4) (I <sub>OS</sub> )                                                  | V <sub>CC</sub> =Max; V <sub>OUT</sub> =0.0V;<br>Output High; CP, D, S, High; E Low | -10 | -20                        | -45                                | mA                         |  |

| Logical "0" Output Voltage (V <sub>OL</sub> )                                                                | V <sub>CC</sub> =Min, I <sub>OL</sub> =9.6 mA                                       |     | 0.2                        | 0.4                                | V                          |  |

| Supply Current (I <sub>CC</sub> )<br>DM2502C<br>DM2502<br>DM2503C<br>DM2503C<br>DM2503C<br>DM2504C<br>DM2504 | V <sub>CC</sub> = Max, All Outputs Low                                              |     | 65<br>65<br>60<br>90<br>90 | 95<br>85<br>90<br>80<br>124<br>110 | mA<br>mA<br>mA<br>mA<br>mA |  |

| Propagation Delay to a Logical "0"<br>From CP to Any Output (t <sub>pd0</sub> )                              |                                                                                     | 10  | 18                         | 28                                 | ns                         |  |

| Propagation Delay to a Logical ''0''<br>From Ē to Q7 (Q11) Output (t <sub>pd0</sub> )                        | CP High, S Low<br>DM2503, DM2503C, DM2504,<br>DM2504C Only                          |     | 16                         | 24                                 | ns                         |  |

| Propagation Delay to a Logical "1"<br>From CP to Any Output (t <sub>pd1</sub> )                              |                                                                                     | 10  | 26                         | 38                                 | ns                         |  |

| Propagation Delay to a Logical ''1''<br>From E to Q7 (Q11) Output (t <sub>pd1</sub> )                        | CP High, S Low<br>DM2503, DM2503C, DM2504,<br>DM2504C Only                          |     | 13                         | 19                                 | ns                         |  |

| Set-Up Time Data Input (t <sub>s(D)</sub> )                                                                  |                                                                                     | -10 | 4                          | 8                                  | ns                         |  |

| Set-Up Time Start Input (t <sub>s(S)</sub> )                                                                 |                                                                                     | 0   | 9                          | 16                                 | ns                         |  |

| Minimum Low CP Width (tPWL)                                                                                  |                                                                                     |     | 30                         | 42                                 | ns                         |  |

| Minimum High CP Width (t <sub>PWH</sub> )                                                                    |                                                                                     |     | 17                         | 24                                 | ns                         |  |

| Maximum Clock Frequency (f <sub>MAX</sub> )                                                                  |                                                                                     | 15  | 21                         |                                    | MHz                        |  |

they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range for the DM2502, DM2503 and DM2504, and across the 0°C to  $+70^{\circ}$ C range for the DM2502C, DM2503C and DM2504C. All typicals are given for V<sub>CC</sub>=5.0V and T<sub>A</sub>=25^{\circ}C.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

# **Application Information**

## OPERATION

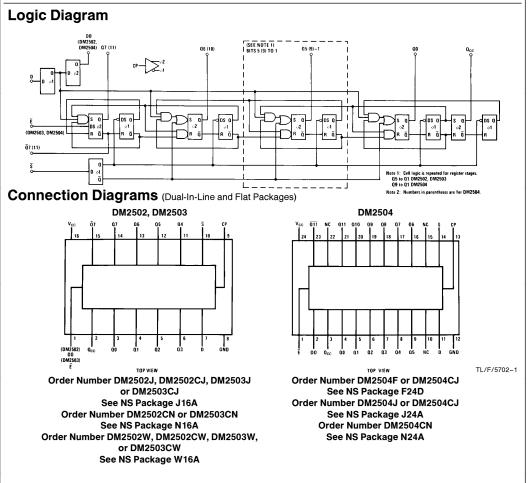

The registers consist of a set of master latches that act as the control elements in the device and change state on the input clock high-to-low transition and a set of slave latches that hold the register data and change on the input clock low-to-high transition. Externally the device acts as a special purpose serial-to-parallel converter that accepts data at the D input of the register and sends the data to the appropriate slave latch to appear at the register output and the DO output on the DM2502 and DM2504 when the clock goes from low-to-high. There are no restrictions on the data input; it can change state at any time except during a short interval centered about the clock low-to-high transition. At the same time that data enters the register bit the next less significant bit register is set to a low ready for the next iteration.

The register is reset by holding the  $\overline{S}$  (Start) signal low during the clock low-to-high transition. The register synchronously resets to the state Q7 (11) low, and all the remaining register outputs high. The Q<sub>CC</sub> (Conversion Complete) signal is also set high at this time. The  $\overline{S}$  signal should not be brought back high until after the clock low-to-high transition in order to guarantee correct resetting. After the clock has gone high resetting the register, the  $\overline{S}$  signal must be removed. On the next clock low-to-high transition the data on the D input is set into the Q7 (11) register bit and the Q6 (10) register bit is set to a low ready for the next clock cycle. On the next clock low-to-high transition data enters the Q6 (10) register bit and Q5 (9) is set to a low. This operation is repeated for each register bit in turn until the register has been filled. When the data goes into Q0, the  $Q_{CC}$  signal goes low, and the register is inhibited from further change until reset by a Start signal.

The DM2502, DM2503 and DM2504 have a specially tailored two-phase clock generator to provide nonoverlapping two-phase clock pulses (i.e., the clock waveforms intersect below the thresholds of the gates they drive). Thus, even at very slow dV/dt rates at the clock input (such as from relatively weak comparator outputs), improper logic operation will not result.

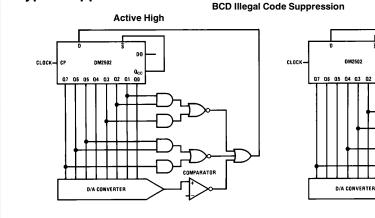

#### LOGIC CODES

All three registers can be operated with various logic codes. Two's complement code is used by offsetting the comparator  $\frac{1}{2}$  full range +  $\frac{1}{2}$  LSB and using the complement of the MSB ( $\overline{Q7}$  or  $\overline{Q11}$ ) with a binary D/A converter. Offset binary is used in the same manner but with the MSB ( $\overline{Q7}$  or  $\overline{Q11}$ ). BCD D/A converters can be used with the addition of illegal code suppression logic.

#### ACTIVE HIGH OR ACTIVE LOW LOGIC

The register can be used with either D/A converters that require a low voltage level to turn on, or D/A converters that require a high voltage level to turn the switch on. If D/A converters are used which turn on with a low logic level, the resulting digital output from the register is active low. That is, a logic "1" is represented as a low voltage level. If D/A converters are used that turn on with a high logic level then the digital output is active high; a logic "1" is represented as a high voltage level.

#### EXPANDED OPERATION

An active low enable input,  $\overline{E}$ , on the DM2503 and DM2504 allows registers to be connected together to form a longer register by connecting the clock, D, and  $\overline{S}$  inputs in parallel and connecting the  $Q_{CC}$  output of one register to the  $\overline{E}$  input of the next less significant register. When the start resets the register, the  $\overline{E}$  signal goes high, forcing the Q7 (11) bit high and inhibiting the register from accepting data until the previous register is full and its  $Q_{CC}$  goes low. If only one register is used the  $\overline{E}$  input should be held at a low logic level.

# Application Information (Continued)

## SHORT CYCLE

If all bits are not required, the register may be truncated and conversion time saved by using a register output going low rather then the Q<sub>CC</sub> signal to indicate the end of conversion. If the register is truncated and operated in the continuous conversion mode, a lock-up condition may occur on power turn-on. This condition can be avoided by making the start input the OR function of  $Q_{CC}$  and the appropriate register output.

#### COMPARATOR BIAS

To minimize the digital error below  $\pm \frac{1}{2}$  LSB, the comparator must be biased. If a D/A converter is used which requires a low voltage level to turn on, the comparator should be biased  $\,+\,1\!\!/_2$  LSB. If the D/A converter requires a high logic level to turn on, the comparator must be biased  $-\frac{1}{2}$ LSB.

# **Definition of Terms**

CP: The clock input of the register.

D: The serial data input of the register.

DO: The serial data out. (The D input delayed one bit).

$\overline{\mathbf{E}}:$  The register enable. This input is used to expand the length of the register and when high forces the Q7 (11) register output high and inhibits conversion. When not used for expansion the enable is held at a low logic level (ground).

$\mathbf{Q}_{i}\;i\!=\!7$  (11) to 0: The outputs of the register.

= Low Voltage Level

DI

Active Low

TL/F/5702-3

X = Don't Care NC = No Change

L.

Q<sub>CC</sub>: The conversion complete output. This output remains high during a conversion and goes low when a conversion is complete.

Q7 (11): The true output of the MSB of the register.

**Q7** (11): The complement output of the MSB of the register.  $\overline{\mathbf{S}}$ : The start input. If the start input is held low for at least a clock period the register will be reset to Q7 (11) low and all the remaining outputs high. A start pulse that is low for a shorter period of time can be used if it meets the set-up time requirements of the  $\overline{S}$  input.

# **Truth Table**

DM2502, DM2503

| Time                                                                                     |    | Inputs |    | Outputs <sup>1</sup> |    |    |    |    |    |    |    |    |                 |

|------------------------------------------------------------------------------------------|----|--------|----|----------------------|----|----|----|----|----|----|----|----|-----------------|

| t <sub>n</sub>                                                                           | D  | s      | Ē2 | D0 <sup>3</sup>      | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | Q <sub>CC</sub> |

| 0                                                                                        | х  | L      | L  | x                    | х  | х  | х  | х  | х  | х  | х  | х  | Х               |

| 1                                                                                        | D7 | н      | L  | x                    | L  | н  | н  | н  | н  | н  | н  | н  | н               |

| 2                                                                                        | D6 | н      | L  | D7                   | D7 | L  | н  | н  | н  | н  | н  | н  | н               |

| 3                                                                                        | D5 | н      | L  | D6                   | D7 | D6 | L  | н  | н  | н  | н  | н  | н               |

| 4                                                                                        | D4 | н      | L  | D5                   | D7 | D6 | D5 | L  | н  | н  | н  | н  | н               |

| 5                                                                                        | D3 | н      | L  | D4                   | D7 | D6 | D5 | D4 | L  | н  | н  | н  | н               |

| 6                                                                                        | D2 | н      | L  | D3                   | D7 | D6 | D5 | D4 | D3 | L  | н  | н  | н               |

| 7                                                                                        | D1 | н      | L  | D2                   | D7 | D6 | D5 | D4 | D3 | D2 | L  | н  | н               |

| 8                                                                                        | D0 | н      | L  | D1                   | D7 | D6 | D5 | D4 | D3 | D2 | D1 | L  | н               |

| 9                                                                                        | Х  | н      | L  | D0                   | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | L               |

| 10                                                                                       | х  | х      | L  | Х                    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | L               |

|                                                                                          | Х  | Х      | Н  | x                    | н  | NC              |

| Note 1: Truth table for DM2504 is extended to include 12 outputs. H = High Voltage Level |    |        |    |                      |    |    |    |    |    |    |    |    |                 |

Note 2: Truth table for DM2502 does not include E column or last line in truth table shown. Note 3: Truth table for DM2503 does not include D0 column.

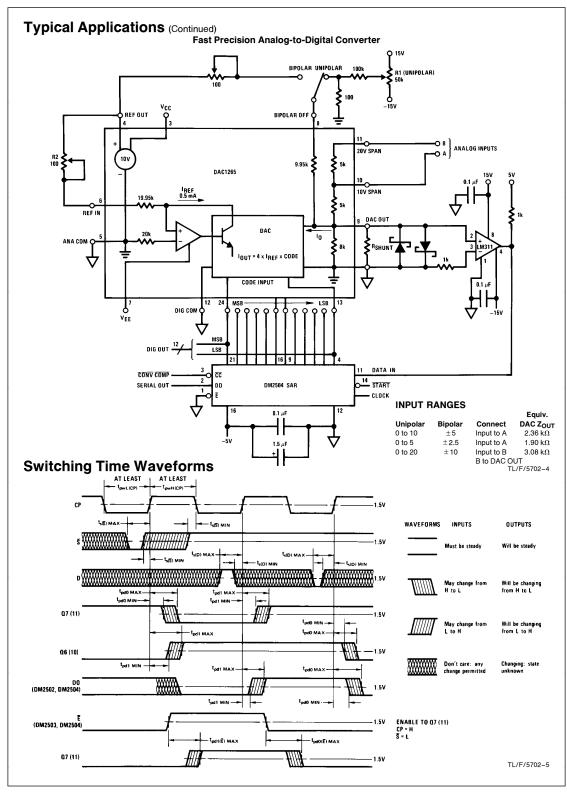

# **Typical Applications**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.