intersil

# EL7560

#### August 21, 1998

## FN7294

# Programmable CPU Power Supply Unit

The EL7560 is the simplest, most cost effective method for powering modern high power CPUs which require a user

OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

Contact our Technical Support Center at contact our lechnical support center at 1-888-INTERSIL or www.intersil.com/tsc

adjustable output voltage. Although it is particularly designed to function with next generation CPUs, its simple design can provide low cost solutions for any 5V to 3V application.

The circuit uses on chip resistorless current sensing for high efficiency, stable current mode control. An on chip temperature sensor resets the OT pin. The OT pin can be tied directly to the OUTEN pin for automatic overtemperature shutdown. The user can adjust the oscillator frequency as well as the slope compensation.

The output voltage is adjustable using a 4-bit parallel interface. A power OK signal "PWRGD' pulls high when the FB pin is within -7% of the programmed value.

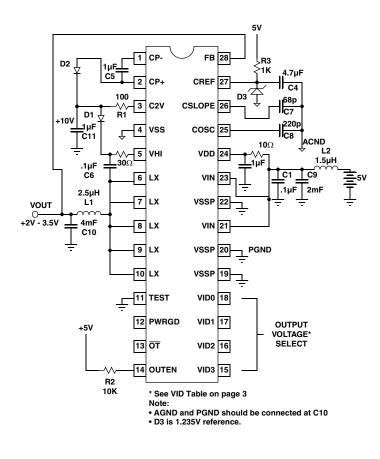

## Pinout

EL7560 (28-PIN SOIC) TOP VIEW

### Features

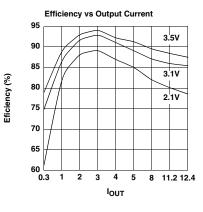

- 3.3V @ 12.4amps continuous

- Internal FETs

- >90% efficiency ٠

- · Synchronous switching

- 4-bit digitally adjustable output voltage

- User adjustable slope compensation

- Internal soft start •

- Over temperature indicator

- · Low current sleep mode

- Low parts count

- Pulse by pulse current limiting

- · High efficiency at light load

- Operates up to 1MHz

- 1% output accuracy

- Sync function

- Power good signal

### Applications

- PC motherboards

- Local high power CPU supplies

## Ordering Information

| PART<br>NUMBER | TEMP. RANGE    | PACKAGE     | PKG. NO. |

|----------------|----------------|-------------|----------|

| EL7560CM       | -40°C to +85°C | 28-Pin SOIC | MDP0027  |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply (V <sub>IN</sub> , V <sub>DD</sub> ) | V |

|---------------------------------------------|---|

| Output Pins0.3V below GND, +0.3V above VD   | D |

| Instantaneous Peak Output Current           | А |

| Storage Temperature Range65°C to +150°C     | С |

Ambient Operating Temperature

-40°C to +85°C

Operating Junction Temperature

135°C

Power Dissipation

3W

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| DC Electrical Specifications | $V_{DD} = V_{IN} = 5V, C_{OSO}$ | $C = 1$ nF, $C_{SLOPE} = 68$ pF, $T_A$ | = 25°C, unless | otherwise specified (Note 1) |

|------------------------------|---------------------------------|----------------------------------------|----------------|------------------------------|

|------------------------------|---------------------------------|----------------------------------------|----------------|------------------------------|

| PARAMETER             | DESCRIPTION                                                   | CONDITION                                                                        | MIN   | ТҮР  | МАХ   | UNITS  |

|-----------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------|-------|--------|

| V <sub>2X</sub>       | Voltage Doubler Output                                        | V <sub>DD</sub> =5V, I <sub>LOAD</sub> =20mA                                     | 8.0   | 9    | 9.5   | V      |

| DAC <sub>LSB</sub>    | DAC Resolution                                                |                                                                                  | 0.095 |      | 0.105 | V      |

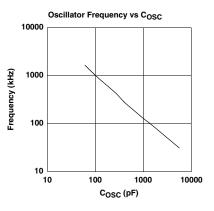

| F <sub>OSC</sub>      | Oscillator Initial Accuracy                                   |                                                                                  | 105   | 120  | 135   | kHz    |

| Fosctc                | Oscillator Tempco                                             | 0°C <t<sub>A&lt;125°C</t<sub>                                                    |       | ±0.1 |       | %/°C   |

| V <sub>RAMP</sub>     | Oscillator Ramp Amplitude                                     |                                                                                  |       | 1.2  |       | V      |

| M <sub>SS</sub>       | Soft Start Slope                                              | F <sub>OSC</sub> =500kHz                                                         |       | 0.3  |       | V/msec |

| I <sub>VID</sub>      | VID Pull Up Current                                           | VID = 0V                                                                         | 9     | 13   | 18    | μΑ     |

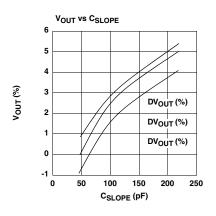

| ICSLOPE               | C <sub>SLOPE</sub> Charging Current                           |                                                                                  | 32    | 40   | 48    | μΑ     |

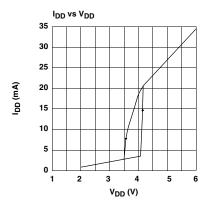

| I <sub>DD</sub>       | Supply Current                                                | OUTEN=4V F <sub>OSC</sub> =120kHz                                                |       | 25   | 35    | mA     |

| IDDOFF                | Stdby Current                                                 | OUTEN=0V                                                                         |       | 3    | 5     | mA     |

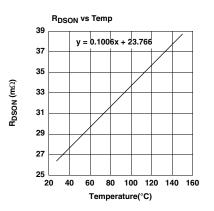

| R <sub>DSON</sub>     | Composite FET Resistance                                      |                                                                                  | 18    |      | 25    | mΩ     |

| R <sub>DSONTC</sub>   | R <sub>DSON</sub> Tempco                                      |                                                                                  |       | 0.1  |       | mΩ/°C  |

| V <sub>OUT</sub>      | Output Initial Acurracy                                       | VID=0111                                                                         | 2.765 | 2.8  | 2.835 | V      |

| V <sub>RANGE</sub>    | Output Voltage Range                                          | VID=1110 to 0000                                                                 | 2.065 |      | 3.535 | V      |

| I <sub>LMAX</sub>     | Maximum current                                               | V <sub>OUT</sub> =0                                                              |       | 14.0 |       | amps   |

| V <sub>OUT-TC</sub>   | Output Tempco                                                 | 0°C <t<sub>A&lt;70°C</t<sub>                                                     |       | ±1   |       | %      |

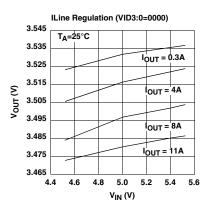

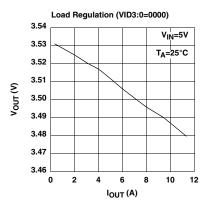

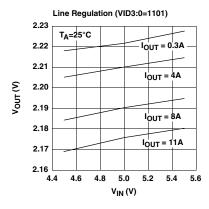

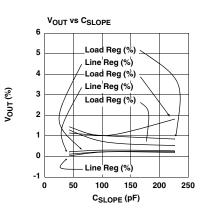

| V <sub>OUT-LINE</sub> | Output Line Regulation                                        | V <sub>OUT</sub> =2.8, 4.5V <sub>DD</sub> <5.5, V <sub>DD</sub> =V <sub>IN</sub> | -1    |      | 1     | %      |

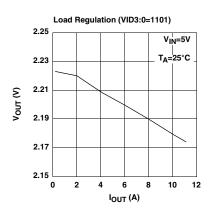

| V <sub>OUT-LOAD</sub> | Output Load Regulation                                        | 0.3A <i<sub>LOAD&lt;12.4A</i<sub>                                                | -1    |      | 1     | %      |

| V <sub>OUT-TOT</sub>  | Output Total Variation                                        |                                                                                  | -2    |      | 2     | %      |

| OT <sub>OFF</sub>     | Over Temperature Threshold                                    |                                                                                  |       | 135  |       | °C     |

| OT <sub>HYS</sub>     | Over Temperature Hysteresis                                   |                                                                                  |       | 50   |       | °C     |

| V <sub>PWRGD</sub>    | Power Good Threshold with Respect to<br>Desired OutputVoltage | VID=0111                                                                         | -9    | -7   | -5    | %      |

| V <sub>DD-ON</sub>    | Minimum V <sub>DD</sub> form Startup                          |                                                                                  |       |      | 4     | V      |

| V <sub>DD-OFF</sub>   | Maximum V <sub>DD</sub> for Shutdown                          |                                                                                  | 3.75  |      |       | V      |

NOTE:

1. The oscillator and voltage doubler operate normally when V<sub>DD</sub> exceeds V<sub>DD-ON</sub> threshold, independent of the OUTEN logic level.

2

# Voltage Identification Codes

| P6 PINS          |                  |                  |                  |                 |

|------------------|------------------|------------------|------------------|-----------------|

| V <sub>ID3</sub> | V <sub>ID2</sub> | V <sub>ID1</sub> | V <sub>ID0</sub> | V <sub>DC</sub> |

| 1                | 1                | 1                | 1                | 0, No CPU       |

| 1                | 1                | 1                | 0                | 2.1             |

| 1                | 1                | 0                | 1                | 2.2             |

| 1                | 1                | 0                | 0                | 2.3             |

| 1                | 0                | 1                | 1                | 2.4             |

| 1                | 0                | 1                | 0                | 2.5             |

| 1                | 0                | 0                | 1                | 2.6             |

| 1                | 0                | 0                | 0                | 2.7             |

| 0                | 1                | 1                | 1                | 2.8             |

| 0                | 1                | 1                | 0                | 2.9             |

| 0                | 1                | 0                | 1                | 3.0             |

| 0                | 1                | 0                | 0                | 3.1             |

| 0                | 0                | 1                | 1                | 3.2             |

| 0                | 0                | 1                | 0                | 3.3             |

| 0                | 0                | 0                | 1                | 3.4             |

| 0                | 0                | 0                | 0                | 3.5             |

# EL7560 Pin Descriptions

| PIN<br>NUMBER | NAME               | DESCRIPTION                                                                                                                                                         |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1             | C <sub>P</sub> -   | Negative input for the charge pump bootstrap capacitor. (Note 1)                                                                                                    |  |  |

| 2             | C <sub>P</sub> +   | Positive input for the charge pump bootstrap capacitor. (Note 1)                                                                                                    |  |  |

| 3             | C2V                | Voltage doubler output. Pin requires at least a 1µF capacitor to GND. (Note 1)                                                                                      |  |  |

| 4             | V <sub>SS</sub>    | Ground return for the control circuitry.                                                                                                                            |  |  |

| 5             | V <sub>HI</sub>    | Positive supply for the high side driver. This pin is bootstrapped from the LX pin with a 0.1µF capacitor.                                                          |  |  |

| 6             | LX                 | Common connection between the two large internal FETs. External inductor connection.                                                                                |  |  |

| 7             | LX                 | Same as pin 6.                                                                                                                                                      |  |  |

| 8             | LX                 | Same as pin 6.                                                                                                                                                      |  |  |

| 9             | LX                 | Same as pin 6.                                                                                                                                                      |  |  |

| 10            | LX                 | Same as pin 6.                                                                                                                                                      |  |  |

| 11            | TEST               | This is test pin and must remain grounded at all times                                                                                                              |  |  |

| 12            | PWRGD              | Pin pulls high when the FB pin is within - 7%(typ) of its programmed value.                                                                                         |  |  |

| 13            | OT                 | Overtemperature indicator. Pulls low when the die temperature exceeds 135°C. Pin has 10mA pull-up.                                                                  |  |  |

| 14            | OT                 | A logic high on OUTEN enables the regulator (Note 1)                                                                                                                |  |  |

| 15            | VID3               | Bit 3(MSB) of the output voltage select DAC.                                                                                                                        |  |  |

| 16            | VID2               | Bit 2 of the output voltage select DAC.                                                                                                                             |  |  |

| 17            | VID1               | Bit 1 of the output voltage select DAC.                                                                                                                             |  |  |

| 18            | VID0               | Bit 0(LSB) of the output voltage select DAC.                                                                                                                        |  |  |

| 19            | V <sub>SSP</sub>   | Ground return to the buck regulator.                                                                                                                                |  |  |

| 20            | V <sub>SSP</sub>   | Same as pin 19.                                                                                                                                                     |  |  |

| 21            | VIN                | Positive power supply input to the buck regulator.                                                                                                                  |  |  |

| 22            | V <sub>SSP</sub>   | Same as pin 19.                                                                                                                                                     |  |  |

| 23            | VIN                | Same as pin 21.                                                                                                                                                     |  |  |

| 24            | V <sub>DD</sub>    | Pin supplies power to the internal control circuitry.                                                                                                               |  |  |

| 25            | C <sub>OSC</sub>   | Oscillator timing capacitor. Oscillator Frequency is approximately: F <sub>OSC</sub> (Hz)=0.0001/C <sub>OSC</sub> (F). The duty cycle is approximately 5%. (Note 1) |  |  |

| 26            | C <sub>SLOPE</sub> | Slope compensation capacitor.                                                                                                                                       |  |  |

| 27            | C <sub>REF</sub>   | External reference input pin.                                                                                                                                       |  |  |

| 28            | FB                 | Voltage feedback pin for the buck regulator.                                                                                                                        |  |  |

#### NOTE:

1. The oscillator and voltage doubler operate normally when V<sub>DD</sub> exceeds V<sub>DD-ON</sub> threshold, independent of the OUTEN logic level.

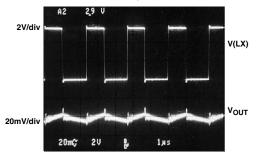

# **Typical Performance Curves**

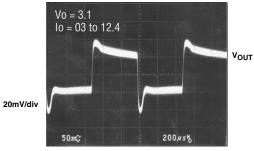

## Typical Performance Curves (Continued)

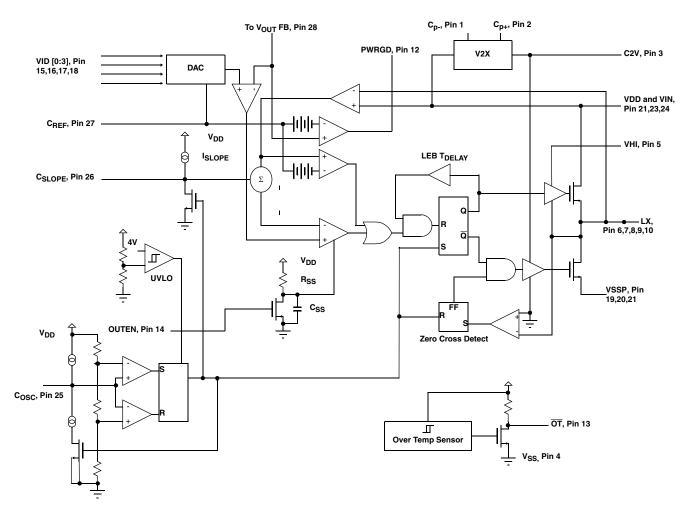

### EL7560 Functional Block Diagram

#### Thermal considerations and power dissipation:

To achieve the maximum 12.4A continuous output current, the EL7560 is packaged in a 28 pin HSOP (Heat-Slug SO Package). Within the package, the EL7560 die is attached to one side of a copper slug. The other side of the slug is coincident with the package top surface, and is therefore exposed to the ambient environment. The copper slug provides an exceptionally low thermal resistance ( $\theta$ JC) of typically 7°C/W. To obtain low junction to ambient thermal resistance ( $\theta$ JA), a heatsink is required to provide heat transfer path from the die to the ambient. The EL7560 power dissipation is a direct function of the "on" resistance of the internal power FETs (Rds-on) and the output current. For the maximum 12.4A output current and the worse case Rds-on at 125°C ( $35m\Omega$ ), the power dissipation is lout<sup>2</sup>\*R = 5.38W. To maintain 12.4A continuous output current operation at the maximum 70°C ambient temperature, the die temperature must be kept below the 135°C thermal shut down temperature. This requires a  $\theta$ JA of 12°C/W. To help achieve such a low  $\theta$ JA with practical size heatsink, airflow is also required. Application note #13 shows the 11°C/W thermal resistance can be achieved with the Wakefield heatsink #8052-60 and minimum 200LFM airflow.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com