# Ultra Low Power Microcontroller with 4x20 LCD Driver

#### **Features**

- Low Power 2.6 μA active mode, LCD On

- 0.5 µA standby mode, LCD Off

- 0.1 μA sleep mode @ 1.5 V, 32 KHz, 20 °C

- Low Voltage 1.2 to 3.6 V

- 2 clocks per instruction cycle

- 72 basic instructions

- ROM 4k x 16 bits

- RAM 128 x 4 bits

- Max. 12 inputs; port A, port B, port SP

- Max. 8 outputs; port B, port SP

- Voltage Level Detector, 8 levels software selectable from 1.2 V up to 4.0 V

- Melody, 7 tones + silence inclusive 4-bit timer

- Universal 10-bit counter, PWM, event counter

- Prescaler down to 1 second (crystal = 32 KHz)

- 1/1000 sec 12 bit binary coded decimal counter with hard or software start/stop function

- · LCD 20 Segments, 3 or 4 times multiplexed

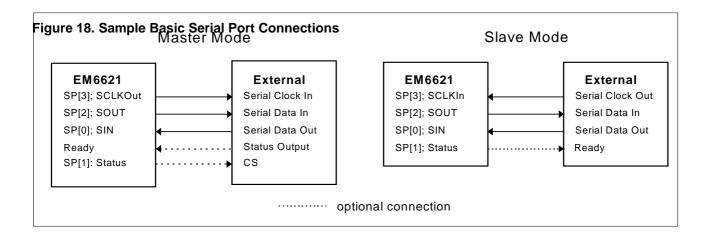

- 3 wire serial port, 8 bit, master and slave mode

- 5 external interrupts (port A, serial interface)

- 8 internal interrupts (3x prescaler, BCD counter 2x10-bit counter, melody timer, serial interface)

- · timer watchdog and oscillation supervisor

### **Description**

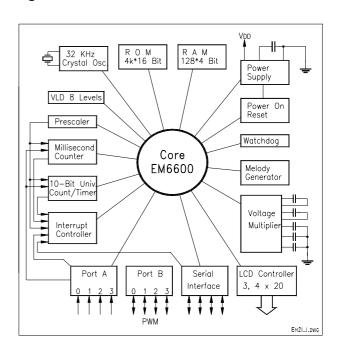

The EM6621 is an advanced single chip low cost CMOS 4-bit microcontroller. It contains ROM, RAM, LCD driver, power on reset, watchdog timer, oscillation detection circuit, 10-bit up/down and event counter, 1ms BCD counter, prescaler, voltage level detector (VId), serial interface and several clock functions. The low voltage feature and low power consumption make it the most suitable controller for battery, stand alone and mobile equipment. The EM6621 is manufactured using EM Microelectronic's advanced low power (ALP) CMOS process.

#### **Typical Applications**

- Timing device

- Automotive controls with display

- Intelligent display driver

- Measurement equipment

- Domestic appliance

- Interactive system with display

- Timer / sports timing devices

- Bicycle computers

- Safety and security devices

Figure 1. Architecture

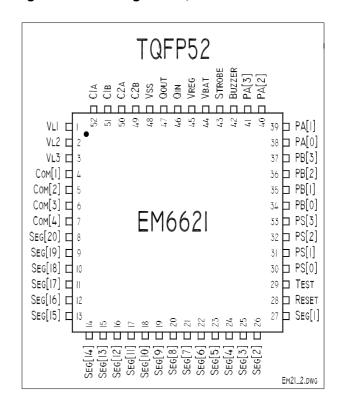

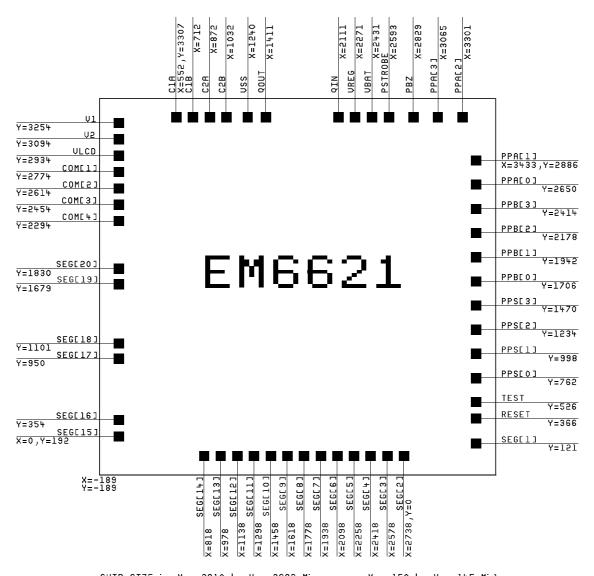

Figure 2. Pin Configuration, TQFP52 10 \* 10 \* 1 mm

# EM6621 at a glance

### Power Supply

- Low voltage low power architecture including internal voltage regulator

- 1.2 ... 3.6 V battery voltage

- 2.6 µA in active mode (Xtal, LCD on, 25 °C)

- 0.5 µA in standby mode (Xtal, LCD off, 25 °C)

- 0.1 µA in sleep mode (25 °C)

- 32 KHz Oscillator

#### RAM

- 64 x 4 bit, direct addressable

- 64 x 4 bit, indexed addressable

#### ROM

- 4k x 16 bit, metal mask programmable

#### • CPU

- 4-bit RISC architecture

- 2 clock cycles per instruction

- 72 basic instructions

### Main Operating Modes and Resets

- Active mode (CPU is running)

- Standby mode (CPU in halt)

- Sleep mode (no clock, reset state)

- Initial reset on power on (POR)

- Watchdog reset (logic and oscillation watchdogs)

- Reset terminal

- Reset with input combination on port A (register selectable)

#### Prescaler

- 15 stage system clock divider down to 1Hz

- 3 Interrupt requests; 1Hz, 32Hz or 8Hz, Blink

- Prescaler reset (4kHz to 1Hz)

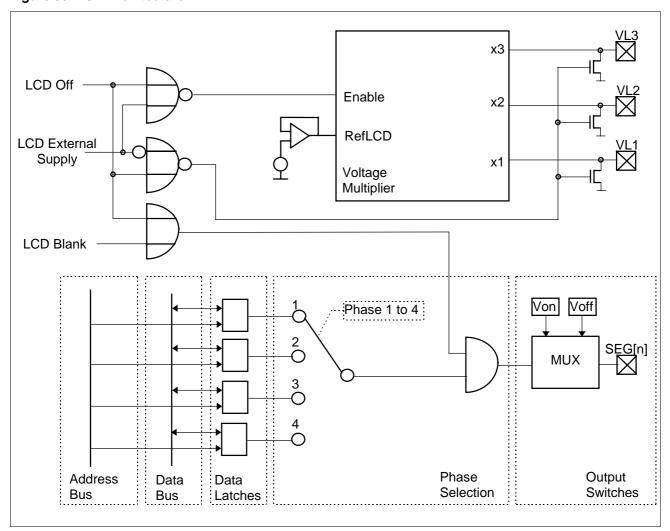

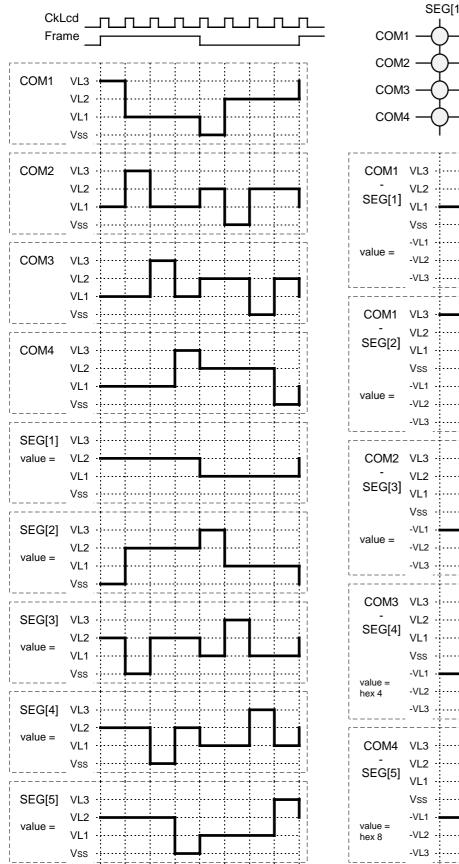

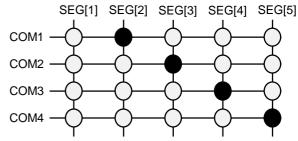

#### Liquid Crystal Display Driver (LCD)

- 20 Segments 3 or 4 times multiplexed

- Internal or external voltage multiplier

- Free Segment allocation architecture (metal 2 mask)

- LCD switch off for power save

#### 8-Bit Serial Interface

- 3 wire (Clock, DataIn , DataOut) master/slave mode

- READY output during data transfer

- Maximum shift clock is equal to the main system clock

- Interrupt request to the CPU after 8 bits data transfer

- Supports different serial formats

- Can be configured as a parallel 4 bit input/output port

- Direct input read on the port terminals

- All outputs can be put tristate (default)

- Selectable pull-downs in input mode

- CMOS or Nch. open drain outputs

- Weak pull-up selectable in Nch. open drain mode

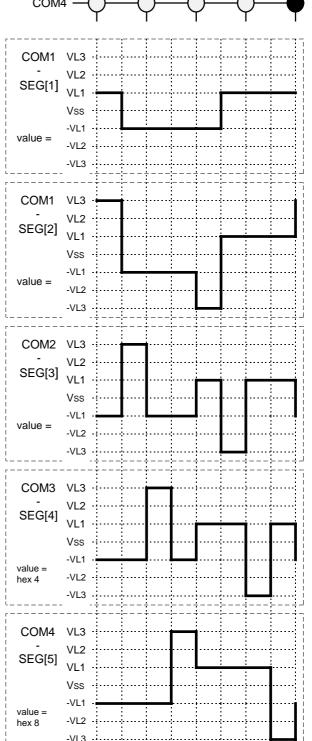

# • 4-Bit Input Port A

- Direct input read on the port terminals

- Debouncer function available on all inputs

- Interrupt request on positive or negative edge

- Pull-up or pull-down or none selectable by register

- Test variables (software) for conditional jumps

- PA[0] and PA[3] are inputs for the event counter

- PA[3] is Start/Stop input for the millisecond counter

- Reset with input combination (register selectable)

#### 4-Bit Bi-directional Port B

- All different functions bit-wise selectable

- Direct input read on the port terminals

- Data output latches

- CMOS or Nch. open drain outputs

- Pull-down or pull-up selectable

- Weak pull-up in Nch. open drain mode

- Selectable PWM, 32kHz, 1kHz and 1Hz output

### Melody Generator

- Dedicated Buzzer terminal

- 7 tones plus silence output

- The output can be put tristate (default)

- Internal 4-bit timer, usable also in standalone mode

- 4 different timer input clocks

- Timer with automatic reload or single run

- Timer interrupt request when reaching 0

### Voltage Level Detector (SVLD)

- 8 different levels from 1.2 V to 4.0 V.

- Busy flag during measure

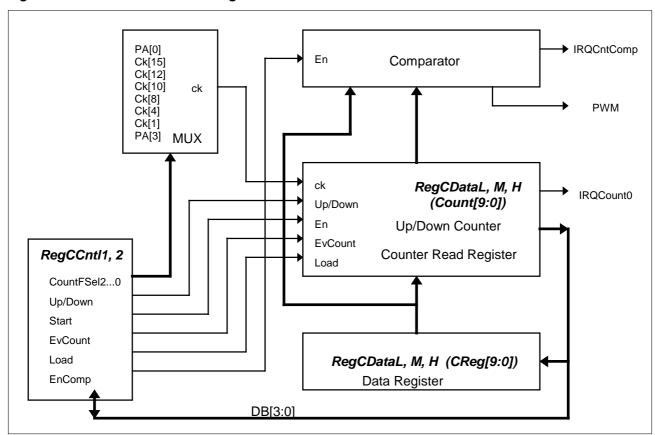

# • 10-Bit Universal Counter

- 10, 8, 6 or 4 bit up/down counting

- Parallel load

- Event counting (PA[0] or PA[3])

- 8 different input clocks-

- Full 10 bit or limited (8, 6, 4 bit) compare function

- 2 interrupt requests (on compare and on 0)

- Hi-frequency input on PA[3] and PA[0]

- Pulse width modulation (PWM) output

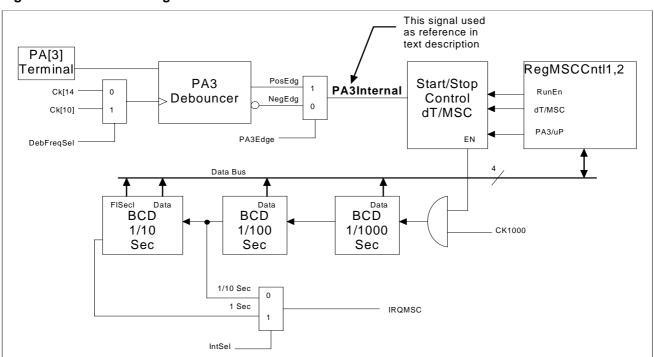

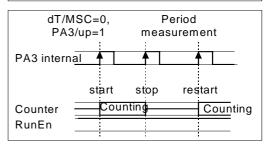

#### Millisecond Counter

- 3 digits binary coded decimal counter (12 bits)

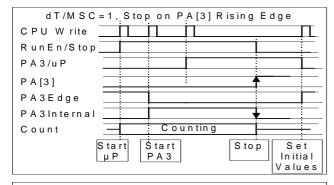

- PA[3] input signal pulse width and period measurement

- Internal 1000 Hz clock generation

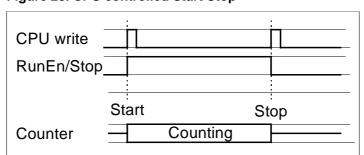

- Hardware or software controlled start stop mode

- Interrupt request on either 1/10 Sec or 1Sec

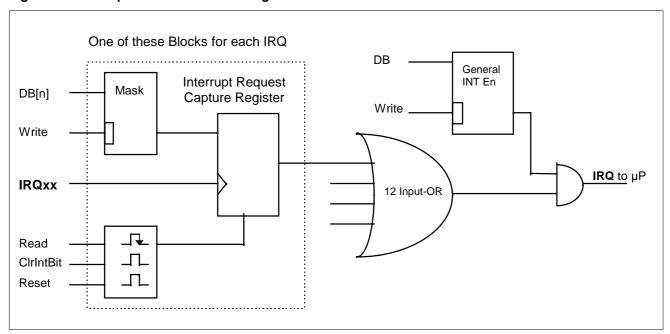

### Interrupt Controller

- 5 external and 8 internal interrupt request sources

- Each interrupt request can individually be masked

- Each interrupt flag can individually be reset

- Automatic reset of each interrupt request after read

General interrupt request to CPU can be disabled

- Automatic enabling of general interrupt request flag when going into HALT mode.

# **Table of Contents**

|     | TURI |                                                   | _ 1  |

|-----|------|---------------------------------------------------|------|

| _   | _    | PTION                                             | _ 1  |

|     |      | APPLICATIONS                                      | _ 1  |

| _   |      | AT A GLANCE                                       | _ 2  |

| 1.  |      | DESCRIPTION FOR EM6621                            |      |

| 2.  | OPE  | RATING MODES                                      | _ 6  |

| 2.1 |      | ACTIVE MODE                                       | _ 6  |

| 2.2 |      | STANDBY MODE                                      |      |

| 2.3 |      | SLEEP MODE                                        |      |

| 3.  | POV  | VER SUPPLY                                        | 7    |

| 4.  | RES  |                                                   |      |

| 4.1 |      | OSCILLATION DETECTION CIRCUIT                     | 9    |

| 4.2 |      | RESET TERMINAL                                    | _ 9  |

| 4.3 |      | INPUT PORT A RESET FUNCTION                       | _ 9  |

| 4.4 |      | DIGITAL WATCHDOG TIMER RESET                      | 10   |

| 4.5 |      | CPU STATE AFTER RESET                             | 10   |

| 5.  | osc  | CILLATOR AND PRESCALER                            |      |

| 5.1 |      | OSCILLATOR                                        |      |

| 5.2 |      | Prescaler                                         |      |

| 6.  | INPI |                                                   |      |

| 6.1 |      | Ports Overview                                    | 13   |

| 6.2 |      | PORT A                                            |      |

|     | 2.1  | IRQ on Port A                                     |      |

|     | 2.2  | Pull-up or Pull-down                              | 15   |

|     | 2.3  | Pull-up or Pull-downSoftware Test Variables       | 15   |

|     | 2.4  | Port A for 10-Bit Counter and MSC                 | 15   |

| 6.3 | ∠.⊤  | PORT A REGISTERS                                  | 15   |

| 6.4 |      |                                                   |      |

| -   | 4.1  | PORT BInput / Output Mode<br>Pull-up or Pull-down | 17   |

|     | 4.2  | Pull-up or Pull-down                              | 12   |

| -   | 4.3  | CMOS / NCH. Open Drain Output                     |      |

| _   | 4.4  | PWM and Frequency Output                          | 19   |

| 6.5 | 4.4  | PORT B REGISTERS                                  | 19   |

| 6.6 |      |                                                   |      |

|     | 6.1  |                                                   | 20   |

|     | 6.2  | 4-bit Parallel I/O<br>Pull-up or Pull-down        | 20   |

|     | 6.3  | Nch. Open Drain Outputs                           | 22   |

|     | 6.4  | General Functional Description                    |      |

|     | 6.5  | Detailed Functional Description                   |      |

|     | 6.6  | Output Modes                                      |      |

| _   |      | Reset and Sleep on Port SP                        | 20   |

| 6.7 | 6.7  | Reset and Sleep on Port SP                        | . 24 |

| -   | MEI  | SERIAL INTERFACE REGISTERS                        |      |

|     |      | ODY, BUZZER                                       | 21   |

|     |      | 4-BIT TIMER                                       | 27   |

|     | 1.1  | Single Run Mode                                   | . 28 |

|     | 1.2  | Continuos Run Mode                                |      |

| 7.2 |      |                                                   | 29   |

| 7.3 |      |                                                   | 29   |

| 8.  | 10-E | BIT COUNTER                                       | 31   |

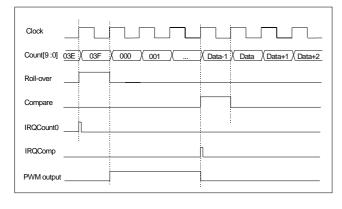

| 8.1 |      | FULL AND LIMITED BIT COUNTING                     | 31   |

| 8.2 |      | FREQUENCY SELECT AND UP/DOWN COUNTING             |      |

| 8.3 |      |                                                   | . 33 |

| 8.4 |      | COMPARE FUNCTION                                  | 33   |

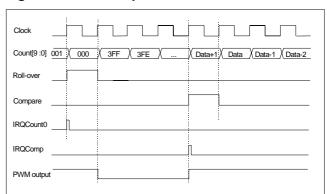

| 8.5 |      | Pulse Width Modulation (PWM)                      |      |

|     | 5.1  | How the PWM Generator works                       |      |

| 8.  | 5.2  | PWM Characteristics                               | 34   |

| 8.6            | COUNTER SETUP                             | 35       |

|----------------|-------------------------------------------|----------|

| 8.7            | 10-BIT COUNTER REGISTERS                  | 35       |

| 9. M           | ILLISECOND COUNTER                        | 37       |

| 9.1            | PA[3] INPUT FOR MSC                       | 37       |

| 9.2            | IRQ FROM MSC                              | 37       |

| 9.3            | IRQ FROM MSCMSC-MODES                     | 38       |

| 9.4            | Mode selection                            | 38       |

| 9.5            | MILLISECOND COUNTER REGISTERS             | 40       |

| 10.            | INTERRUPT CONTROLLER                      | 41       |

| 10.1           |                                           | 42       |

| <b>11.</b>     | SUPPLY VOLTAGE LEVEL DETECTOR             | 43       |

| 11.1           |                                           | 43<br>43 |

|                | SVLD REGISTER                             | -        |

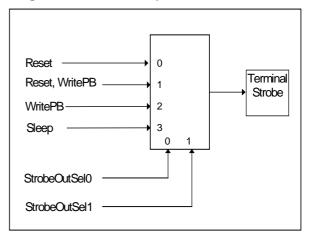

| 12.            | STROBE OUTPUT                             | 44       |

| 12.1           | STROBE REGISTER                           | 44       |

| 13.            | RAM                                       | 45       |

| 14.            |                                           | 46       |

| 14.1           | LCD CONTROL                               | 47       |

| 14.2           | LCD Addressing                            | 47       |

| 14.3           | FREE SEGMENT ALLOCATION                   | 48       |

| 14.4           | LCD REGISTERS                             | 48       |

| 15.            | PERIPHERAL MEMORY MAP                     | 50       |

| 16.            | OPTION REGISTER MEMORY MAP                | 54       |

| 17.            | ACTIVE SUPPLY CURRENT TEST                | 55       |

| 18.            | MASK OPTIONS                              | 56       |

| 18.1           | INPUT / OUTPUT PORTS                      | 56       |

| 18.1           | .1 Port A Metal Options                   | 56       |

| 18.1           | .2 Port A Metal Options                   | 56       |

| 18.1           | .3 Port B Metal Options                   | 57       |

| 18.1           | .4 Port SP Metal Options                  | 58       |

| 18.1           | .5 Voltage Regulator Option               | 59       |

| 18.1           | .6 Debouncer Frequency Option             | 59       |

| 18.1           | .7 User defined LCD Segment Allocation    |          |

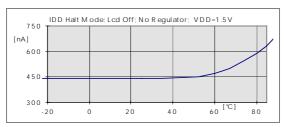

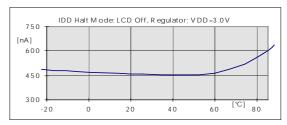

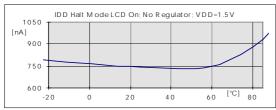

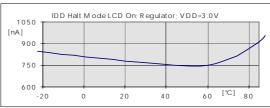

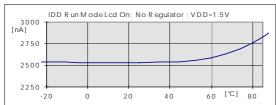

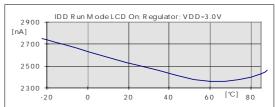

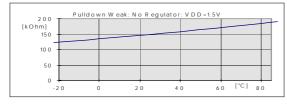

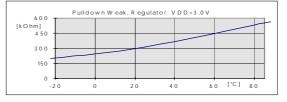

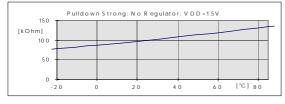

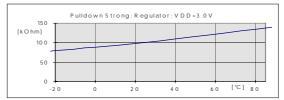

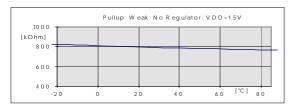

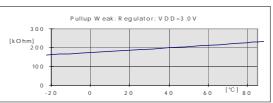

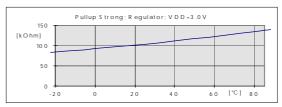

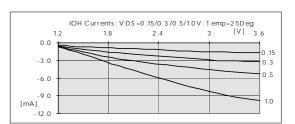

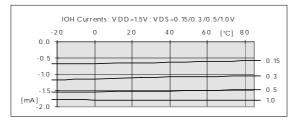

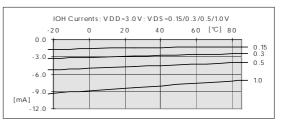

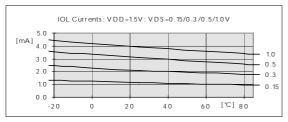

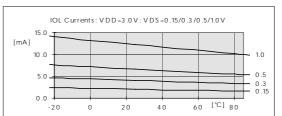

| 19.            | TEMP. AND VOLTAGE BEHAVIORS               | 60       |

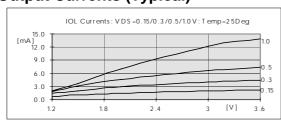

| 19.1           | IDD CURRENT (TYPICAL)                     | 60       |

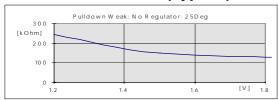

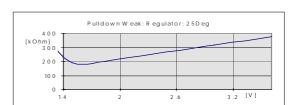

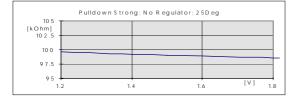

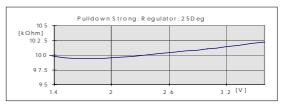

| 19.2           | Pull-down Resistance (Typical)            | 60       |

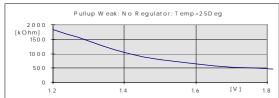

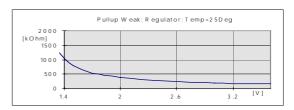

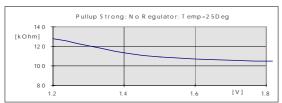

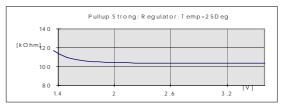

| 19.3           |                                           | 61       |

| 19.4           | OUTPUT CURRENTS (TYPICAL)                 | 61       |

| 20.            | ELECTRICAL SPECIFICATION                  | 62       |

| 20.1           | ABSOLUTE MAXIMUM RATINGS                  | 62       |

| 20.2           | HANDLING PROCEDURES                       | 62       |

| 20.2           | STANDARD OPERATING CONDITIONS             |          |

| 20.4           | DC CHARACTERISTICS - POWER SUPPLY         | 62       |

| 20.5           | SUPPLY VOLTAGE LEVEL DETECTOR             | 63       |

|                | _                                         | 63       |

| 20.6<br>20.7   | OSCILLATOR DC CHARACTERISTICS - I/O PINS  | 64       |

| 20.7           | LCD SEC[20:4] OUTPUTS                     | 65       |

|                | LCD SEG[20:1] OUTPUTSLCD COM[4:1] OUTPUTS | 65       |

| 20.9           | DC OUTPUT COMPONENT                       | -        |

| 20.10<br>20.11 | DC OUTPUT COMPONENT                       | 65       |

|                | LCD VOLTAGE MULTIPLIER                    | 65       |

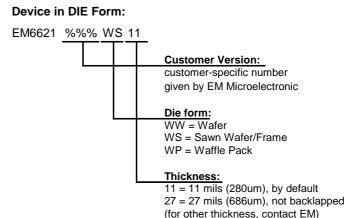

| 21.            | DIE, PAD LOCATION AND SIZE                | 66       |

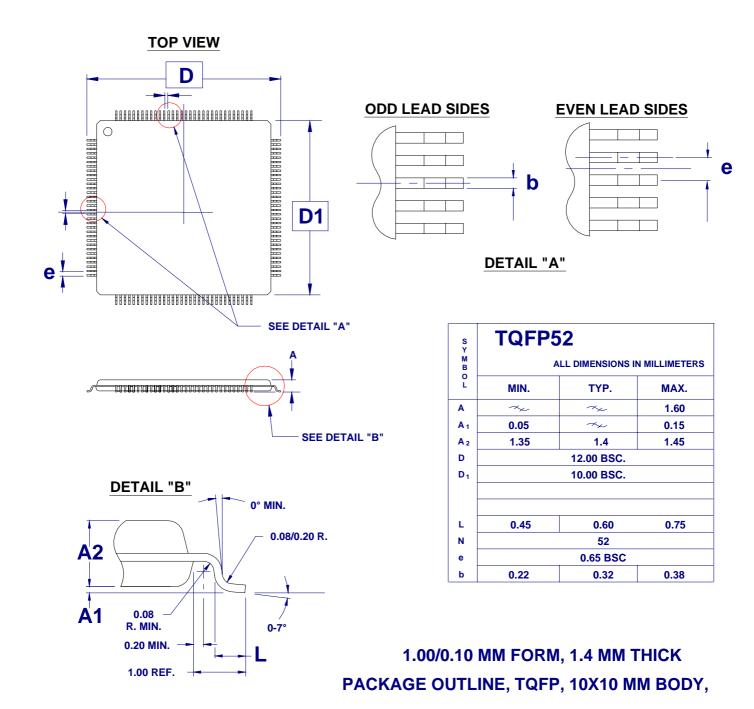

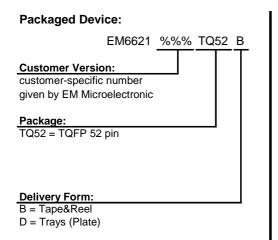

| 22.            | PACKAGE & ORDERING INFORMATION            | 67       |

| 22.1           | ORDERING INFORMATION                      | _68      |

| 22.2           | PACKAGE MARKING                           | 68       |

| 22.3           | CUSTOMER MARKING                          | 68       |

| 23.            | SPEC UPDATE                               | 69       |

# 1. Pin Description for EM6621

| Chip | TQFP<br>52 | DIL<br>64 | Signal Name | Function                                                                   | Remarks                                                             |

|------|------------|-----------|-------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|

| 1    | 1          | 10        | VL1         | Voltage multiplier level 1 LCD level 1 input, if externa supply selected   |                                                                     |

| 2    | 2          | 11        | VL2         | Voltage multiplier level 2 LCD level 2 input, if externa supply selected   |                                                                     |

| 3    | 3          | 12        | VL3         | Voltage multiplier level 3                                                 | LCD level 3 input, if external supply selected                      |

| 4    | 4          | 13        | COM[1]      | LCD back plane 1                                                           |                                                                     |

| 5    | 5          | 14        | COM[2]      | LCD back plane 2                                                           |                                                                     |

| 6    | 6          | 15        | COM[3]      | LCD back plane 3                                                           |                                                                     |

| 7    | 7          | 16        | COM[4]      | LCD back plane 4                                                           | Not used if 3 times multiplexed                                     |

| 8    | 8          | 18        | SEG[20]     | LCD Segment 20                                                             |                                                                     |

| 9    | 9          | 19        | SEG[19]     | LCD Segment 19                                                             |                                                                     |

| 10   | 10         | 20        | SEG[18]     | LCD Segment 18                                                             |                                                                     |

| 11   | 11         | 21        | SEG[17]     | LCD Segment 17                                                             |                                                                     |

| 12   | 12         | 22        | SEG[16]     | LCD Segment 16                                                             |                                                                     |

| 13   | 13         | 23        | SEG[15]     | LCD Segment 15                                                             |                                                                     |

| 14   | 14         | 26        | SEG[14]     | LCD Segment 14                                                             |                                                                     |

| 15   | 15         | 27        | SEG[13]     | LCD Segment 13                                                             |                                                                     |

| 16   | 16         | 28        | SEG[12]     | LCD Segment 12                                                             |                                                                     |

| 17   | 17         | 29        | SEG[11]     | LCD Segment 11                                                             |                                                                     |

| 18   | 18         | 30        | SEG[10]     | LCD Segment 10                                                             |                                                                     |

| 19   | 19         | 31        | SEG[9]      | LCD Segment 9                                                              |                                                                     |

| 20   | 20         | 33        | SEG[8]      | LCD Segment 8                                                              |                                                                     |

| 21   | 21         | 34        | SEG[7]      | LCD Segment 7                                                              |                                                                     |

| 22   | 22         | 35        | SEG[6]      | LCD Segment 6                                                              |                                                                     |

| 23   | 23         | 36        | SEG[5]      | LCD Segment 5                                                              |                                                                     |

| 24   | 24         | 37        | SEG[4]      | LCD Segment 4                                                              |                                                                     |

| 25   | 25         | 38        | SEG[3]      | LCD Segment 3                                                              |                                                                     |

| 26   | 26         | 39        | SEG[2]      | LCD Segment 2                                                              |                                                                     |

| 27   | 27         | 42        | SEG[1]      | LCD Segment 1                                                              |                                                                     |

| 28   | 28         | 43        | Reset       | Input reset terminal,                                                      | Main reset                                                          |

|      |            |           |             | internal pull-down 15 KOhm                                                 |                                                                     |

| 29   | 29         | 44        | Test        | Input test terminal,<br>internal pull-down 15 KOhm                         | For EM tests only, ground 0! Except when needed for MFP programming |

| 30   | 30         | 45        | PSP[0]      | Input/output , open drain<br>serial port : SIN<br>parallel out terminal 0  | Serial interface data in or parallel data[0] in/out                 |

| 31   | 31         | 46        | PSP[1]      | Output , open drain<br>serial port : Ready/CS<br>parallel out terminal 1   | Serial interface Ready CS<br>or<br>parallel data[1] in/out          |

| 32   | 32         | 47        | PSP[2]      | Output , open drain<br>serial port : SOUT<br>parallel out terminal 2       | Serial interface data out<br>or<br>parallel data[2] in/out          |

| 33   | 33         | 49        | PSP[3]      | Input/output , open drain<br>serial port : SCLK<br>parallel out terminal 3 | Serial interface clock I/O or parallel data[3] in/out               |

| 34   | 34         | 50        | PB[0]       | Input/output, open drain port B terminal 0                                 | Port B data[0] I/O or<br>Ck[1] output                               |

| Chip | TQFP<br>52 | DIL<br>64 | Signal Name | Function                                   | Remarks                                              |

|------|------------|-----------|-------------|--------------------------------------------|------------------------------------------------------|

| 35   | 35         | 51        | PB[1]       | Input/output, open drain port B terminal 1 | Port B data[1] I/O or<br>Ck[11] output               |

| 36   | 36         | 52        | PB[2]       | Input/output, open drain port B terminal 2 | Port B data[2] I/O or<br>Ck[16] output               |

| 37   | 37         | 53        | PB[3]       | Input/output, open drain port B terminal 3 | Port B data[3] I/O or<br>PWM output                  |

| 38   | 38         | 54        | PA[0]       | Input port A terminal 0                    | TestVar 1 Event counter                              |

| 39   | 39         | 55        | PA[1]       | Input port A terminal 1                    | TestVar 2                                            |

| 40   | 40         | 58        | PA[2]       | Input port A terminal 2                    | TestVar 3                                            |

| 41   | 41         | 59        | PA[3]       | Input port A terminal 3                    | Event counter,<br>MSC start/stop control             |

| 42   | 42         | 60        | Buzzer      | Output Buzzer terminal                     |                                                      |

| 43   | 43         | 61        | Strobe      | Output Strobe terminal                     | μP reset state or/and port B write or sleep flag out |

| 44   | 44         | 62        | Vbat = VDD  | Positive power supply                      | MFP Connection                                       |

| 45   | 45         | 63        | Vreg        | Internal voltage regulator                 | Connect to minimum 100nF, MFP connection             |

| 46   | 46         | 64        | Qin/Osc1    | Crystal terminal 1                         | 32 KHz crystal, MFP connection                       |

| 47   | 47         | 2         | Qout /Osc2  | Crystal terminal 2                         | 32 KHz crystal, MFP connection                       |

| 48   | 48         | 3         | Vss         | Negative power supply                      | ref. terminal, MFP connection                        |

| 49   | 49         | 4         | C2B         | Voltage multiplier                         | Not needed if ext. supply                            |

| 50   | 50         | 5         | C2A         | Voltage multiplier                         | Not needed if ext. supply                            |

| 51   | 51         | 6         | C1B         | Voltage multiplier                         | Not needed if ext. supply                            |

| 52   | 52         | 7         | C1A         | Voltage multiplier                         | Not needed if ext. supply                            |

Gray shaded areas: Terminals needed for MFP programming connections (VDD, Vreg, Qin, Qout, Test).

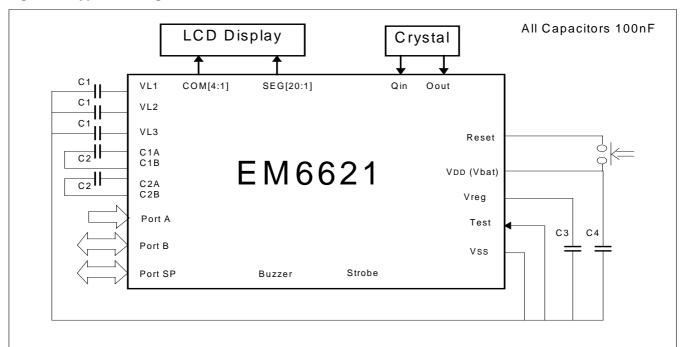

Figure 3. Typical Configuration

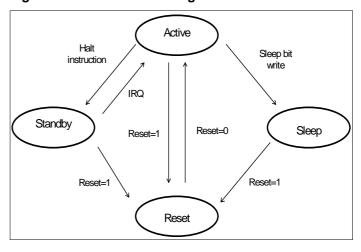

## 2. Operating Modes

The EM6621 has two low power dissipation modes, standby and sleep. Figure 4 is a transition diagram for these modes.

#### 2.1 Active Mode

The active mode is the actual CPU running mode. Instructions are read from the internal ROM and executed by the CPU. Leaving active mode via the halt instruction to go into standby mode, the **Sleep** bit write to go into Sleep mode or a reset from port A to go into reset mode.

### 2.2 Standby Mode

Executing a halt instruction puts the EM6621 into standby mode. The voltage regulator, oscillator, watchdog timer, LCD, interrupts, timers and counters are operating. However, the CPU stops since the clock related to instruction execution stops. Registers, RAM and I/O pins retain their states prior to standby mode. A reset or an interrupt request if enabled cancels standby.

### 2.3 Sleep Mode

Writing to the **Sleep** bit in the **RegSysCntl1** register puts the EM6621 in sleep mode. The oscillator stops and most functions of the EM6621 are inactive. To be able to write to the **Sleep** bit, the **SleepEn** bit in **RegSysCntl2** must first be set to "1". In

Figure 4 Mode transition diagram

sleep mode only the voltage regulator and the reset input are active. The RAM data integrity is maintained. Sleep mode may be canceled only by a high level of min 10µs at the EM6621 Reset terminal or by the selected port A input reset combination, if option **InpResSleep** is turned on.

Due to the cold-start characteristics of the oscillator, waking up from sleep mode may take some time to guarantee stable oscillation. During sleep mode and the following start up the EM6621 is in reset state. Waking up from sleep clears the **Sleep** flag but not the **SleepEn** bit. Inspecting the **SleepEn** allows to determine if the EM6621 was powered up (**SleepEn** = "0") or woken up from sleep (**SleepEn** = "1").

Table 2.3.1. Internal State in Standby and Sleep Mode

| Function                   | Standby                             | Sleep                                |

|----------------------------|-------------------------------------|--------------------------------------|

| Oscillator                 | Active                              | Stopped                              |

| Oscillator Watchdog        | Active                              | Stopped                              |

| Instruction Execution      | Stopped                             | Stopped                              |

| Interrupt Functions        | Active                              | Stopped                              |

| Registers and Flags        | Retained                            | Reset                                |

| RAM Data                   | Retained                            | Retained                             |

| Option Registers           | Retained                            | Retained                             |

| Timer & Counter            | Active                              | Reset                                |

| Logic Watchdog             | Active                              | Reset                                |

| I/O Port B and Serial Port | Active                              | High Impedance,                      |

|                            |                                     | Pull's as defined in option register |

| Input Port A               | Active                              | No pull-downs and inputs deactivated |

|                            |                                     | except if InpResSleep = "1"          |

| LCD                        | Active                              | Stopped (display off)                |

| Strobe Output              | Active                              | Active                               |

| Buzzer Output              | Active                              | High Impedance                       |

| Voltage Level Detector     | Finishes ongoing measure, then stop | Stopped                              |

| Reset Pin                  | Active                              | Active                               |

# 3. Power Supply

The EM6621 is supplied by a single external power supply between VDD (Vbat) and VSS (Ground). A built-in voltage regulator generates Vreg providing regulated voltage for the oscillator and the internal logic. The output drivers are supplied directly from the external supply VDD. The internal power configuration is shown below in Figure 5.

To supply the internal core logic it is possible to use either the internal voltage regulator (Vreg < VDD) or Vbat directly (Vreg = VDD). The selection is done by metal 1 mask option. By default the voltage regulator is used. Refer to chapter 18.1.5 for the metal mask selection.

The internal voltage regulator is chosen for high voltage systems. It saves power by reducing the internal core logic's power supply to an optimum value. However, due to the inherent voltage drop over the regulator the minimal VDD is restricted to 1.4 V.

A direct Vbat connection can be selected for systems running on a 1.5 V battery. The internal 1 KOhm resistor together with the external capacitor on Vreg is filtering the VDD supply to the internal core. In this case the minimum VDD can be as low as 1.2 V.

Figure 5. Internal Power Supply

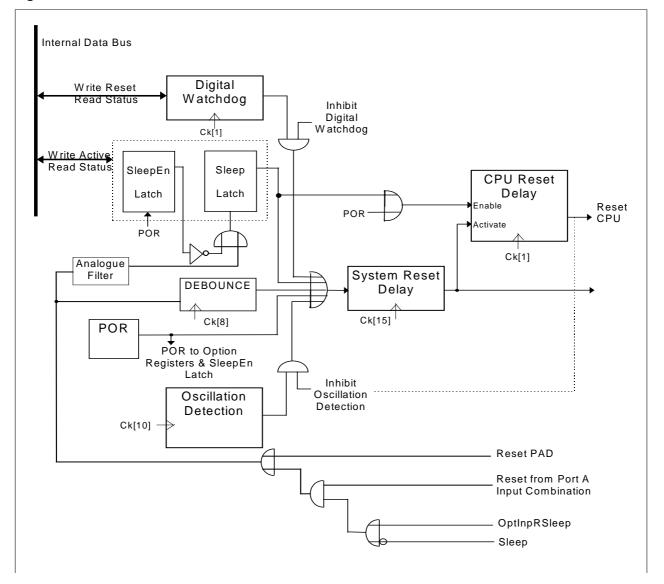

#### 4. Reset

Figure 6. illustrates the reset structure of the EM6621. One can see that there are six possible reset sources:

- (1) Internal initial reset from the Power On Reset (POR) circuitry. --> POR

- (2) External reset from the Reset terminal. --> System Reset, Reset CPU

- (3) External reset by simultaneous high/low inputs to port A. --> System Reset, Reset CPU (Combinations are defined in the registers **OptInpRSel1** and **OptInpRSel2**)

- (4) Internal reset from the Digital Watchdog.

- --> System Reset, Reset CPU

- (5) Internal reset from the Oscillation Detection Circuit.

- --> System Reset, Reset CPU

(6) Internal reset when sleep mode is activated.

--> System Reset, Reset CPU

All reset sources activate the System Reset and the Reset *CPU*. The 'System Reset Delay' ensures that the system reset remains active long enough for all system functions to be reset (active for n system clock cycles). The 'CPU Reset Delay' ensures that the reset CPU remains active until the oscillator is in stable oscillation.

As well as activating the system reset and the reset CPU, the POR also resets all option registers and the sleep enable (SleepEn) latch. System reset and reset CPU do not reset the option registers nor the SleepEn latch. Reset state can be shown on Strobe terminal by selecting StrobeOutSel1,0 = 0 in RegLcdCntl1.

Figure 6. Reset Structure

#### 4.1 Oscillation Detection Circuit

At power on, the voltage regulator starts to follow the supply voltage and triggers the power on reset circuitry, and thus the system reset. The CPU of the EM6621 remains in the reset state for the 'CPU Reset Delay', to allow the oscillator to stabilize after power up.

The oscillator is disabled during sleep mode. So when waking up from sleep mode, the CPU of the EM6621 remains in the reset state for the CPU Reset Delay, to allow the oscillator to stabilize. During this time, the Oscillation Detection Circuit is inhibited.

In active or standby modes, the oscillator detection circuit monitors the oscillator. If it stops for any reason, a system reset is generated. After clock restart the CPU waits for the CPU Reset Delay before executing the first instructions.

The oscillation detection circuitry can be inhibited with bit **NoOscWD** = 1 in register **RegVIdCntI.** At power up, and after any system reset, the function is activated.

The 'CPU Reset Delay' is 32768 system clocks (Ck[16]) long.

#### 4.2 Reset Terminal

During active or standby modes the Reset terminal has a debouncer to reject noise. Reset must therefore be active for at least 16 ms (system clock = 32 KHz).

When canceling sleep mode, the debouncer is not active (no clock), however, reset passes through an analogue filter with a time constant of typical.  $5\mu s$ . In this case Reset pin must be high for at least 10  $\mu s$  to generate a system reset.

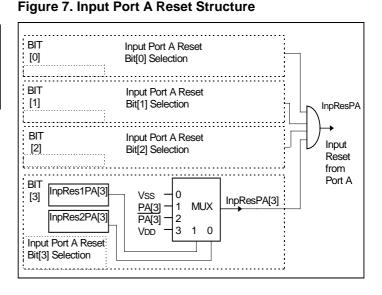

### 4.3 Input Port A Reset Function

By writing the **OptInpRSel1** and **OptInpRSel2** registers it is possible to choose any combination of port A input values to execute a system reset. The reset condition must be valid for at least 16ms (system clock = 32kHz) in active and standby mode.

**OPTInpRSleep** selects the input port A reset function in sleep mode. If set to "1" the occurrence of the selected combination for input port A reset will immediately trigger a system reset (no debouncer) .

Reset combination selection (*InpReset*) is done with registers **OptInpRSel1** and **OptInpRSel2**. Following formula is applicable :

InpResPA = InpResPA[0] • InpResPA[1] • InpResPA[2] • InpResPA[3]

| InpRes1PA[n] | InpRes2PA[n] | InpResPA[n] |

|--------------|--------------|-------------|

| 0            | 0            | Vss         |

| 0            | 1            | PA[n]       |

| 1            | 0            | not PA[n]   |

| 1            | 1            | VDD         |

n = 0 to 3

i.e.; - no reset if InpResPA[n] = Vss.

- Don't care function on a single bit with its InpResPA[n] = VDD.

- Always Reset if InpResPA[3:0] = 'b1111

03/02 REV. D/444

# 4.4 Digital Watchdog Timer Reset

The digital watchdog is a simple, non-programmable, 2-bit timer, that counts on each rising edge of Ck[1]. It will generate a system reset if it is not periodically cleared. The watchdog timer function can be inhibited by activating an inhibit digital watchdog bit (**NoLogicWD**) located in **RegVIdCntI**. At power up, and after any system reset, the watchdog timer is activated.

If for any reason the CPU stops, then the watchdog timer can detect this situation and activate the system reset signal. This function can be used to detect program overrun, endless loops, etc. For normal operation, the watchdog timer must be reset periodically by software at least every 2.5 seconds (system clock = 32 KHz), or a system reset signal is generated.

The watchdog timer is reset by writing a '1' to the **WDReset** bit in the timer. This resets the timer to zero and timer operation restarts immediately. When a '0' is written to **WDReset** there is no effect. The watchdog timer operates also in the standby mode and thus, to avoid a system reset, one should not remain in standby mode for more than 2.5 seconds.

From a system reset state, the watchdog timer will become active after 3.5 seconds. However, if the watchdog timer is influenced from other sources (i.e. prescaler reset), then it could become active after just 2.5 seconds. It is therefore recommended to use the Prescaler **IRQHz1** interrupt to periodically reset the watchdog every second.

It is possible to read the current status of the watchdog timer in **RegSysCntl2**. After watchdog reset, the counting sequence is (on each rising edge of CK[1]): '00', '01', '10', '11' {**WDVal1 WDVal0**}. When going into the '11' state, the watchdog reset will be active within ½ second. The watchdog reset activates the system reset which in turn resets the watchdog. If the watchdog is inhibited it's timer is reset and therefore always reads '0'.

Table 4.4.1 Watchdog Timer Register RegSysCntl2

| Bit | Name    | Reset | R/W | Description                            |

|-----|---------|-------|-----|----------------------------------------|

| 3   | WDReset | 0     | R/W | Reset the Watchdog                     |

|     |         |       |     | 1 -> Resets the Logic Watchdog         |

|     |         |       |     | 0 -> No action                         |

|     |         |       |     | The Read value is always '0'           |

| 2   | SleepEn | 0     | R/W | See Operating modes (sleep)            |

| 1   | WDVal1  | 0     | R   | Watchdog timer data Ck[1] divided by 4 |

| 0   | WDVal0  | 0     | R   | Watchdog timer data Ck[1] divided by 2 |

### 4.5 CPU State after Reset

Reset initializes the CPU as shown in Table 4.5.1 below.

Table 4.5.1 Initial CPU Value after Reset.

| Name                 | Bits | Symbol | Initial Value                   |

|----------------------|------|--------|---------------------------------|

| Program counter 0    | 12   | PC0    | hex 000 (as a result of Jump 0) |

| Program counter 1    | 12   | PC1    | Undefined                       |

| Program counter 2    | 12   | PC2    | Undefined                       |

| Stack pointer        | 2    | SP     | PSP[0] selected                 |

| Index register       | 7    | IX     | Undefined                       |

| Carry flag           | 1    | CY     | Undefined                       |

| Zero flag            | 1    | Z      | Undefined                       |

| Halt                 | 1    | HALT   | 0                               |

| Instruction register | 16   | IR     | Jump 0                          |

|                      |      |        |                                 |

| Periphery registers  | 4    | Reg.   | See peripheral memory map       |

#### 5. Oscillator and Prescaler

#### 5.1 Oscillator

A built-in crystal oscillator generates the system operating clock for the CPU and peripheral blocks, from an externally connected crystal (typically 32.768kHz). The oscillator circuit is supplied by the regulated voltage, Vreg. In sleep mode the oscillator is stopped.

EM's special design techniques guarantee the low current consumption of this oscillator. The external impedance between the oscillator pads must be greater than 10MOhm. Connection of any other components to the two oscillator pads must be confirmed by EM Microelectronic-Marin SA.

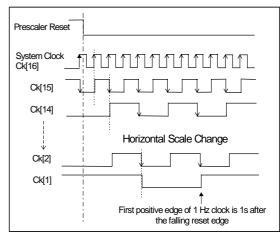

#### 5.2 Prescaler

The prescaler consists of fifteen elements divider chain which delivers clock signals for the peripheral circuits such as timer/counter, buzzer, LCD voltage multiplier, debouncer and edge detectors, as well as generating prescaler interrupts. The input to the prescaler is the system clock signal. Power on initializes the prescaler to Hex(0001).

**Table 5.2.1 Prescaler Clock Name Definition**

| Function           | Name   | 32 KHz Xtal |

|--------------------|--------|-------------|

| System clock       | Ck[16] | 32768 Hz    |

| System clock / 2   | Ck[15] | 16384 Hz    |

| System clock / 4   | Ck[14] | 8192 Hz     |

| System clock / 8   | Ck[13] | 4096 Hz     |

| System clock/ 16   | Ck[12] | 2048 Hz     |

| System clock / 32  | Ck[11] | 1024 Hz     |

| System clock / 64  | Ck[10] | 512 Hz      |

| System clock / 128 | ck [9] | 256 Hz      |

| Function             | Name  | 32 KHz Xtal |

|----------------------|-------|-------------|

| System clock / 256   | Ck[8] | 128 Hz      |

| System clock / 512   | Ck[7] | 64 Hz       |

| System clock / 1024  | Ck[6] | 32 Hz       |

| System clock / 2048  | Ck[5] | 16 Hz       |

| System clock / 4096  | Ck[4] | 8 Hz        |

| System clock / 8192  | Ck[3] | 4 Hz        |

| System clock / 16384 | Ck[2] | 2 Hz        |

| System clock / 32768 | Ck[1] | 1 Hz        |

Table 5.2.2 Control of Prescaler Register RegPresc

| Bit | Name     | Reset | R/W | Description                                                                                                  |

|-----|----------|-------|-----|--------------------------------------------------------------------------------------------------------------|

| 3   | PWMOn    | 0     | R/W | see 10 bit counter                                                                                           |

| 2   | ResPresc | 0     | R/W | Write Reset prescaler  1 -> Resets the divider chain from Ck[14] down to Ck[2], sets Ck[1].  0 -> No action. |

|     |          |       |     | The Read value is always '0'                                                                                 |

| 1   | PrIntSel | 0     | R/W | Interrupt select. 0 -> Interrupt from Ck[4] 1 -> Interrupt from Ck[6]                                        |

| 0   | DebSel   | 0     | R/W | Debouncer clock select. 0 -> Debouncer with Ck[8] 1 -> Debouncer with Ck[11] or Ck[14]                       |

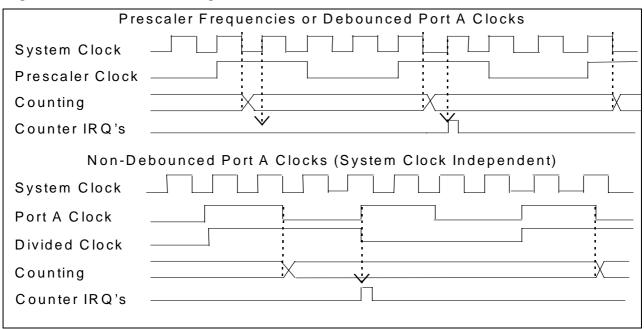

Figure 8. Prescaler Frequency Timing

With DebSel = 1 one may choose either the Ck[11] or Ck[14] debouncer frequency by selecting the corresponding metal mask option. Relative to 32kHz the corresponding max. debouncer times are then 2 ms or 0.25 ms. For the metal mask selection refer to chapter 18.1.6.

Switching the **PrIntSel** may generate an interrupt request. Avoid it with **MaskIRQ32/8** = 0 selection during the switching operation.

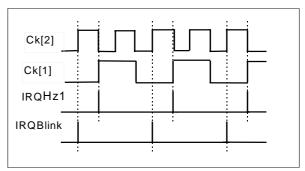

The prescaler contains 3 interrupt sources:

- IRQ32/8 ; this is Ck[6] or Ck[4] positive edge interrupt, the selection is depending on bit **PrIntSel**.

- IRQHz1; this is Ck[1] positive edge interrupt

- IRQBlink; this is 3/4 of Ck[1] period interrupt

There is no interrupt generation on reset.

The first IRQHz1 Interrupt occurs 1 sec (32kHz) after reset.

A possible application for the IRQBlink is LCD-Display blinking control together with IRQHz1.

Figure 9. Prescaler Interrupts

# 6. Input and Output Ports

The EM6621 has:

- One 4-bit input port ( port A )

- One 4-bit input/output port. ( port B )

- One serial interface (port SP) also configurable as 4-bit I/O port

Pull-up and pull-down resistors can be added to all this ports with metal and/or register options.

### **6.1 Ports Overview**

Table 6.1.1 Input and Output Ports Overview

| Port        | Mode                                               | Mask(M:) or Register(R:) Option                                                                                                                                                   | Function                                                                                                                                                                           | Bit-wise M                                          | ultifunctior                   | on Ports                    |                                   |

|-------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------|-----------------------------|-----------------------------------|

| PA<br>[3:0] | Input                                              | M: Pull-up M: Pull-down (default) R: Pull(up/down) select R: Debouncer or direct input for IRQ requests and Counter R: + or - for IRQ-edge and counter R: Input reset combination | -Input -Bit-wise interrupt request -Software test variable conditional jump -PA[3],PA[0] input for the event counter -PA[3] input for the millisecond counter -Port A reset inputs | PA[3]  10 bit event counter clock start/stop of MSC | PA[2]<br>-<br>-                | PA[1]<br>-<br>-             | PA[0]  10 bit event counter clock |

| PB<br>[3:0] | Individual<br>input or<br>output                   | R: CMOS or<br>Nch. open drain output<br>R: Pull-down on input<br>R: Pull-up on input                                                                                              | -Input or output -PB[3] for the PWM output -PB[2:0] for the Ck[16,11,1] output -Tristate output                                                                                    | PB[3]<br>PWM<br>output                              | PB[2]<br>Ck[16]<br>output      | PB[1]<br>Ck[11]<br>output   | PB[0]<br>Ck[1]<br>output          |

| PS<br>[3:0] | Serial I/O<br>or<br>port-wise<br>input /<br>output | R: CMOS or<br>Nch open drain output<br>R: Pull-down on input<br>R: Pull-up on input                                                                                               | -PSP[3], serial clock out<br>-PSP[2], serial data out<br>-PSP[1], serial status out<br>-PSP[0], serial data in<br>-PSP[3:0] 4-bit input/output<br>-Tristate output                 | PSP[3]  Serial clock output  SCLK                   | PSP[2] Serial data output SOUT | PSP[1] Ready or CS Ready/CS | PSP[0] Serial data input SIN      |

#### 6.2 Port A

The EM6621 has one four bit general purpose CMOS input port. The port A input can be read at any time, internal pull-up or pull-down resistors can be chosen. All selections concerning port A are bit-wise executable. I.e. Pull-up on PA[2], pull-down on PA[0], positive IRQ edge on PA[0] but negative on PA[1], etc.

In sleep mode the port A pull-up or pull-down resistors are turned off, and the inputs are deactivated except if the **InpResSleep** bit in the option register **OPTFSeI** is set to 1. In this case the port A inputs are continuously monitored to match the input reset condition which will immediately wake the EM6621 from sleep mode (all pull resistors remain).

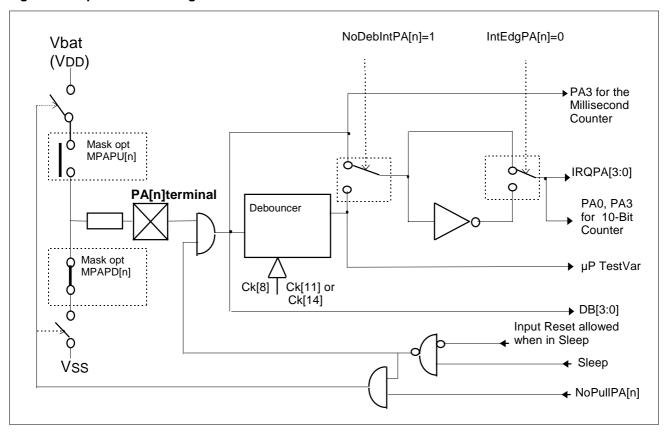

Figure 10. Input Port A Configuration

#### 6.2.1 IRQ on Port A

For interrupt request generation (IRQ) one can choose direct or debouncer input and positive or negative edge IRQ triggering. With the debouncer selected ( **OPTDebIntPA** ) the input must be stable for two rising edges of the selected debouncer clock (**RegPresc**). This means a worst case of 16 ms (default) or 2 ms (0.25 ms by metal mask) with a system clock of 32 KHz.

Either a positive or a negative edge on the port A inputs - after debouncer or not - can generate an interrupt request. This selection is done in the option register **OPTIntEdgPA**.

All four bits of port A can provide an IRQ, each pin with its own interrupt mask bit in the **RegIRQMask1** register. When an IRQ occurs, inspection of the **RegIRQ1**, **RegIRQ2** and **RegIRQ3** registers allows the interrupt to be identified and treated.

At power on or after any reset the **RegIRQMask1** is set to 0, thus disabling any input interrupt. A new interrupt is only stored with the next active edge after the corresponding interrupt mask is cleared. See also the interrupt chapter 10.

It is recommended to mask the port A IRQ's while one changes the selected IRQ edge. Else one may generate a IRQ (Software IRQ). I.e. PA[0] on '0' then changing from positive to negative edge selection on PA[0] will immediately trigger an IRQPA[0] if the IRQ was not masked.

with n=0...3

### 6.2.2 Pull-up or Pull-down

Each of the input port terminals PA[3:0] has a resistor integrated which can be used either as pull-up or pull-down resistor, depending on the selected metal mask options. See the port A metal mask chapter for details. The pull resistor can be inhibited using the **NoPullPA[n]** bits in the register **OptNoPullPA**.

Table 6.2.1. Pull-up or Pull-down Resistor on Port A Inputs

| Option mask | Option mask | NoPullPA[n] |                           |

|-------------|-------------|-------------|---------------------------|

| pull-up     | pull-down   | value       | Action                    |

| MPAPU[n]    | MPAPD[n]    |             |                           |

| no          | no          | х           | no pull-up, no pull-down  |

| no          | yes         | 0           | no pull-up, pull-down     |

| no          | yes         | 1           | no pull-up, no pull-down  |

| yes         | no          | 0           | pull-up, no pull-down     |

| yes         | no          | 1           | no pull-up , no pull-down |

| yes         | yes         | х           | not allowed*              |

<sup>\*</sup> only pull-up or pull-down may be chosen on any port A terminal (one choice is excluding the other)

#### 6.2.3 Software Test Variables

The port A terminals PA[2:0] are also used as input conditions for conditional software branches. Independent of the **OPTDebIntPA** and the **OPTIntEdgPA**. These CPU inputs always have a debouncer.

- Debounced PA[0] is connected to CPU TestVar1.

- Debounced PA[1] is connected to CPU TestVar2.

- Debounced PA[2] is connected to CPU TestVar3.

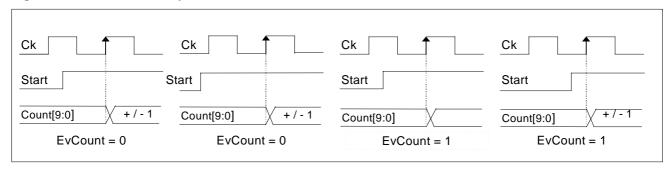

#### 6.2.4 Port A for 10-Bit Counter and MSC

The PA[0] and PA[3] inputs can be used as the clock input terminal for the 10 bit counter in "event count" mode. As for the IRQ generation one can choose debouncer or direct input with the register **OPTDebIntPA** and non-inverted or inverted input with the register **OPTIntEdgPA**. Debouncer input is always recommended.

Pad input PA[3] is also used as start/stop control for the millisecond counter. This control signal is derived from PA[3], it is independent of the port A debouncer and edge selection. Refer also to Figure 10.

#### 6.3 Port A Registers

Table 6.3.1 Register RegPA

| Bit | Name      | Reset | R/W | Description        |

|-----|-----------|-------|-----|--------------------|

| 3   | PAData[3] | -     | R*  | PA[3] input status |

| 2   | PAData[2] | -     | R*  | PA[2] input status |

| 1   | PAData[1] | -     | R*  | PA[1] input status |

| 0   | PAData[0] | -     | R*  | PA[0] input status |

<sup>\*</sup> Direct read on port A terminals

### Table 6.3.2 Register RegIRQMask1

| Bit | Name         | Reset | R/W | Description                    |

|-----|--------------|-------|-----|--------------------------------|

| 3   | MaskIRQPA[3] | 0     | R/W | Interrupt mask for PA[3] input |

| 2   | MaskIRQPA[2] | 0     | R/W | Interrupt mask for PA[2] input |

| 1   | MaskIRQPA[1] | 0     | R/W | Interrupt mask for PA[1] input |

| 0   | MaskIRQPA[0] | 0     | R/W | Interrupt mask for PA[0] input |

Default "0" is: interrupt request masked, no new request stored

# Table 6.3.3 Register RegIRQ1

| Bit | Name     | Reset | R/W  | Description                |

|-----|----------|-------|------|----------------------------|

| 3   | IRQPA[3] | 0     | R/W* | Interrupt request on PA[3] |

| 2   | IRQPA[2] | 0     | R/W* | Interrupt request on PA[2] |

| 1   | IRQPA[1] | 0     | R/W* | Interrupt request on PA[1] |

| 0   | IRQPA[0] | 0     | R/W* | Interrupt request on PA[0] |

<sup>\*;</sup> Write "1" clears the bit, write "0" has no action, default "0" is: no interrupt request

# Table 6.3.4 Register OPTIntEdgPA

| Bit | Name        | power on | R/W | Description                     |

|-----|-------------|----------|-----|---------------------------------|

|     |             | value    |     |                                 |

| 3   | IntEdgPA[3] | 0        | R/W | Interrupt edge select for PA[3] |

| 2   | IntEdgPA[2] | 0        | R/W | Interrupt edge select for PA[2] |

| 1   | IntEdgPA[1] | 0        | R/W | Interrupt edge select for PA[1] |

| 0   | IntEdgPA[0] | 0        | R/W | Interrupt edge select for PA[0] |

Default "0" is: Positive edge selection

## Table 6.3.5 Register OPTDebIntPA

| Bit | Name          | power on value | R/W | Description                   |

|-----|---------------|----------------|-----|-------------------------------|

| 3   | NoDebIntPA[3] | 0              | R/W | Interrupt debounced for PA[3] |

| 2   | NoDebIntPA[2] | 0              | R/W | Interrupt debounced for PA[2] |

| 1   | NoDebIntPA[1] | 0              | R/W | Interrupt debounced for PA[1] |

| 0   | NoDebIntPA[0] | 0              | R/W | Interrupt debounced for PA[0] |

Default "0" is: Debounced inputs for interrupt generation

# Table 6.3.6 Register OPTNoPullPA

| Bit | Name        | power on | R/W | Description                     |

|-----|-------------|----------|-----|---------------------------------|

|     |             | value    |     |                                 |

| 3   | NoPullPA[3] | 0        | R/W | Pull-up/down selection on PA[3] |

| 2   | NoPullPA[2] | 0        | R/W | Pull-up/down selection on PA[2] |

| 1   | NoPullPA[1] | 0        | R/W | Pull-up/down selection on PA[1] |

| 0   | NoPullPA[0] | 0        | R/W | Pull-up/down selection on PA[0] |

Default "0" depending on mask selection

#### 6.4 Port B

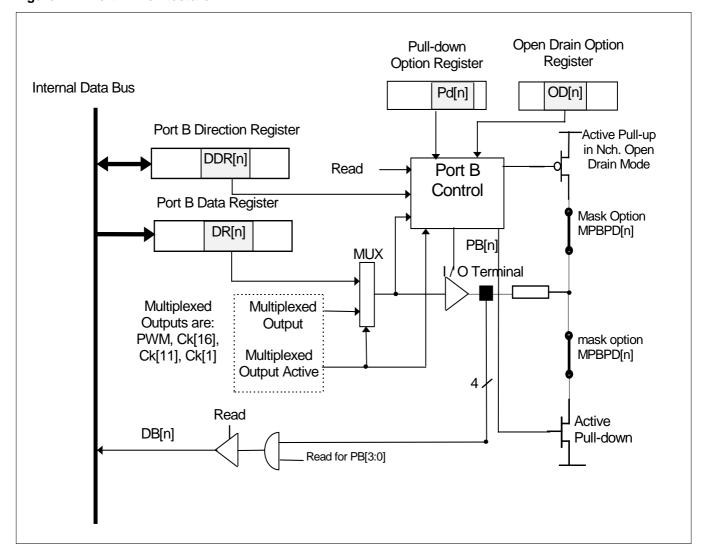

The EM6621 has one four bit general purpose I/O port. Each bit can be configured individually by software for input/output, pull-up, pull-down and CMOS or Nch. open drain output type. The port outputs either data, frequency or PWM signals.

### 6.4.1 Input / Output Mode

Each port B terminal is bit-wise bi-directional. The input or output mode on each port B terminal is set by writing the corresponding bit in the **RegPBCntl** control register. To set for input (default), 0 is written to the corresponding bit of the **RegPBCntl** register which results in a high impedance state for the output driver. The output mode is set by writing 1 in the control register, and consequently the output terminal follows the status of the bits in the **RegPBData** register.

The port B terminal status can be read on address **RegPBData** even in output mode. Be aware that the data read on port B is not necessary of the same value as the data stored on **RegPBData** register. See also Figure 11 for details.

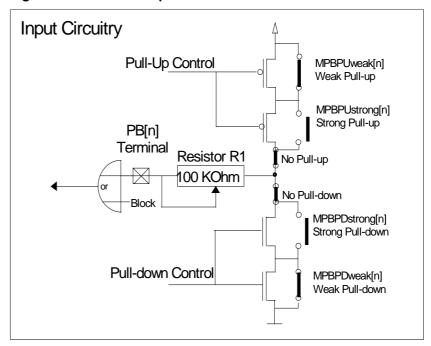

Figure 11. Port B Architecture

### 6.4.2 Pull-up or Pull-down

On each terminal of PB[3:0] an internal input pull-up (metal mask MPBPU[n]) or pull-down (metal mask MPBPD[n]) resistor can be connected per metal mask option. Per default the two resistors are in place. In this case one can chose per software to have either a pull-up, a pull-down or no resistor. See below.

For Metal mask selection and available resistor values refer to chapter 18.1.3.

**Pull-down ON**: MPBPD[n] must be in place,

AND bit NoPdPB[n] must be '0'.

Pull-down OFF: MPBPD[n] is not in place,

**OR** if MPBPD[n] is in place **NoPdPB**[n] = '1' cuts off the pull-down.

**OR** selecting **NchOpDPB**[n] = '1' cuts off the pull-down.

**Pull-up ON** \* : MPBPU[n] must be in place.

AND bit NchOpDPB[n] must be '1',

AND (bit PBIOCntl[n] = '0' (input mode) OR if PBIOCntl[n] = '1' while PBData[n] = 1.)

**Pull-up OFF\*** : MPBPU[n] is not in place,

**OR** if MPBPU[n] is in place **NchOpDPB**[n] = '0' cuts off the pull-up,

**OR** if MPBPU[n] is in place and if **NchOpDPB**[n] = '1' then **PBData**[n] = 0 cuts off the pull-up.

Never pull-up and pull-down can be active at the same time.

For **POWER SAVING** one can switch off the port B pull resistors between two read phases. No cross current flows in the input amplifier while the port B is not read. The recommended order is:

- Switch on the pull resistor.

- Allow sufficient time RC constant for the pull resistor to drive the line to either Vss or VDD.

- · Read the port B

- Switch off the pull resistor

Minimum time with current on the pull resistor is 4 system clock periods, if the RC time constant is lower than 1 system clock period. Adding a NOP instruction before reading moves the number of periods with current in the pull resistor to 6 and the maximum RC delay to 3 clock periods.

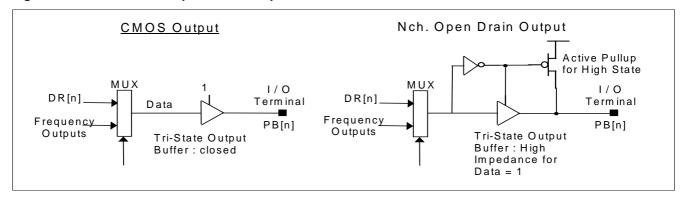

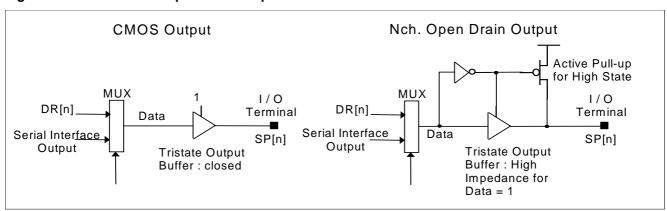

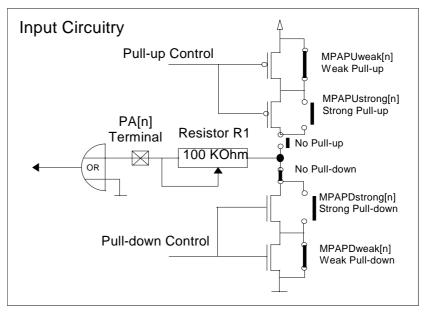

### 6.4.3 CMOS / NCH. Open Drain Output

The port B outputs can be configured as either CMOS or Nch. open drain outputs. In CMOS both logic '1' and '0' are driven out on the terminal. In Nch. Open Drain only the logic '0' is driven on the terminal, the logic '1' value is defined by the internal pull-up resistor (if implemented), or high impedance.

Figure 12. CMOS or Nch. Open Drain Outputs

www.emmicroelectronic.com

## 6.4.4 PWM and Frequency Output

PB[3] can also be used to output the PWM (Pulse Width Modulation) signal from the 10-Bit Counter, the Ck[16], Ck[11] as well as the Ck[1] prescaler frequencies.

- -Selecting PWM output on PB[3] with bit **PWMOn** in register **RegPresc** and running the counter.

- -Selecting Ck[16] output on PB[2] with bit PB32kHzOut in register OPTFSelPB

- -Selecting Ck[11] output on PB[1] with bit PB1kHzOut in register OPTFSelPB

- -Selecting Ck[1] output on PB[0] with bit PB1HzOut in register OPTFSelPB

### 6.5 Port B Registers

#### Table 6.5.1 Register RegPBData

| Bit | Name      | Reset | R/W  | Description            |

|-----|-----------|-------|------|------------------------|

| 3   | PBData[3] | -     | R*/W | PB[3] input and output |

| 2   | PBData[2] | -     | R*/W | PB[2] input and output |

| 1   | PBData[1] | -     | R*/W | PB[1] input and output |

| 0   | PBData[0] | -     | R*/W | PB[0] input and output |

<sup>\*:</sup> Direct read on the port B terminal (not the internal register)

#### Table 6.5.2 Register RegPBCntl

| Bit | Name        | Reset | R/W | Description           |

|-----|-------------|-------|-----|-----------------------|

| 3   | PBIOCntl[3] | 0     | R/W | I/O control for PB[3] |

| 2   | PBIOCntl[2] | 0     | R/W | I/O control for PB[2] |

| 1   | PBIOCntl[1] | 0     | R/W | I/O control for PB[1] |

| 0   | PBIOCntl[0] | 0     | R/W | I/O control for PB[0] |

Default "0" is: port B in input mode

### **Table 6.5.3 Option Register OPTFSelPB**

| Bit | Name        | power on | R/W | Description                  |

|-----|-------------|----------|-----|------------------------------|

|     |             | value    |     |                              |

| 3   | InpResSleep | 0        | R/W | Reset from sleep with port A |

| 2   | PB32kHzOut  | 0        | R/W | Ck[16] output on PB[2]       |

| 1   | PB1kHzOut   | 0        | R/W | Ck[11] output on PB[1]       |

| 0   | PB1HzOut    | 0        | R/W | Ck[1] output on PB[0]        |

Default "0" is: No frequency output, port A Input Reset can not reset the SLEEP mode.

### **Table 6.5.4 Option Register OPTNoPdPB**

| Bit | Name      | power on value | R/W | Description           |

|-----|-----------|----------------|-----|-----------------------|

| 3   | NoPdPB[3] | 0              | R/W | No pull-down on PB[3] |

| 2   | NoPdPB[2] | 0              | R/W | No pull-down on PB[2] |

| 1   | NoPdPB[1] | 0              | R/W | No pull-down on PB[1] |

| 0   | NoPdPB[0] | 0              | R/W | No pull-down on PB[0] |

Default "0" is: Pull-down on

### Table 6.5.5 Option Register OPTNchOpDPB

| Bit | Name        | power on | R/W | Description              |

|-----|-------------|----------|-----|--------------------------|

|     |             | value    |     | ·                        |

| 3   | NchOpDPB[3] | 0        | R/W | Nch. Open Drain on PB[3] |

| 2   | NchOpDPB[2] | 0        | R/W | Nch. Open Drain on PB[2] |

| 1   | NchOpDPB[1] | 0        | R/W | Nch. Open Drain on PB[1] |

| 0   | NchOpDPB[0] | 0        | R/W | Nch. Open Drain on PB[0] |

Default "0" is: CMOS output

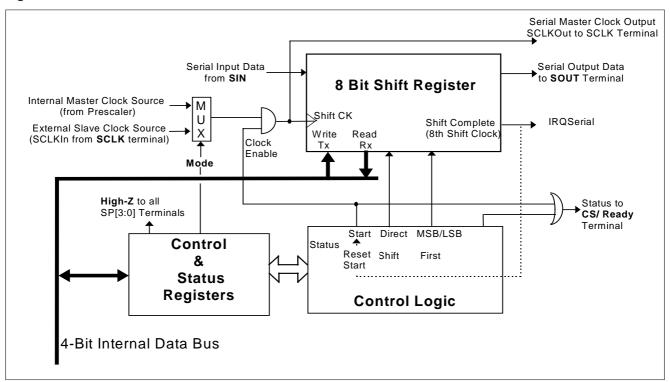

#### 6.6 Port Serial

The EM6621 contains a simple, half duplex three wire synchronous type serial interface., which can be used to program or read an external EEPROM, ADC, ... etc.

For data reception, a shift-register converts the serial input data on the SIN(PSP[0]) terminal to a parallel format, which is subsequently read by the CPU in registers **RegSDataL** and **RegSDataH** for low and high nibble. To transmit data, the CPU loads data into the shift register, which then serializes it on the SOUT(PSP[2]) terminal. It is possible for the shift register to simultaneously shift data out on the SOUT terminal and shift data on the SIN terminal. In Master mode, the shifting clock is supplied internally by the Prescaler: one of three prescaler frequencies are available, Ck[16], Ck[15] or Ck[14]. In Slave mode, the shifting clock is supplied externally on the SCLKIn(PSP[3]) terminal. In either mode, it is possible to program: the shifting edge, shift MSB first or LSB first and direct shift output. All these selection are done in register **RegSCnt11** and **RegSCnt12**.

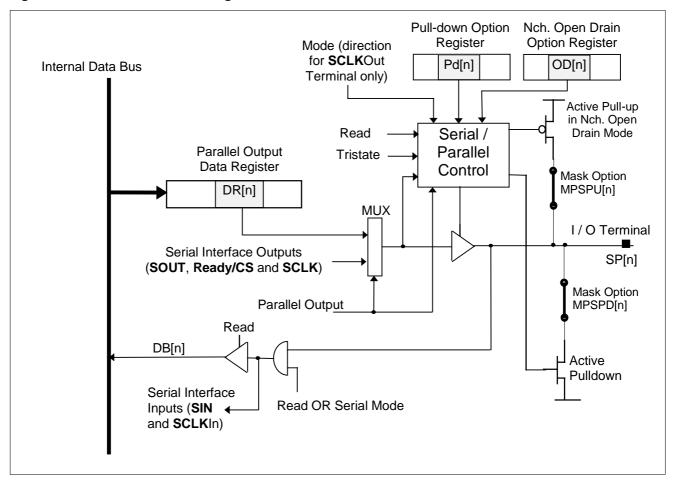

Figure 13. Serial Interface Architecture

The PSP[3..0] terminal configuration is shown in Figure 14. When the Serial Interface is active then :

- \* PSP[1] {Ready / CS) is outputting the ready (slave mode) or the CS signal (master mode).

- PSP[2] {SOUT} is always an output.

- \* PSP[0] {SIN} is always an input.

- PSP[3] {SCLK} is an output for Master mode {SCLKOut} and an input for Slave mode {SCLKIn}

### 6.6.1 4-bit Parallel I/O

Selecting OM[1],OM[0] = '1' in register RegSCntl2 the PSP[3:0] terminals are configured as a 4-bit Output. Output data is stored in the register RegSPData.

The **RegSPData** is defined as a read/write register, but what is read is not the register output, but the port PSP[3:0] terminal values

Selecting **OM[1],OM[0]** = '0' in register **RegSCntl2** the PSP[3:0] outputs are cut off (tristate). The terminals can be used as inputs with individual (bit-wise) pull-up or pull-down settings.

Independent of the selected configuration, the PSP[3:0] terminal levels are always readable.

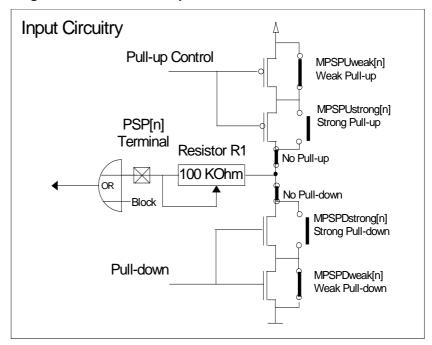

Figure 14. Port SP Terminal Configuration

### 6.6.2 Pull-up or Pull-down

For each terminal of PSP[3:0] an input pull-up (metal mask MPSPU[n]) or pull-down (metal mask MPSPD[n]) resistor can be implemented per metal mask option. Per default the two metal masks are in place, so one can chose per software to have either a pull-up, a pull-down or no resistor. For Metal mask selection and available resistor values refer to chapter 18.1.4

Pull-down ON: MPSPD[n] must be in place,

AND the bit NoPdPS[n] must be '0'.

Pull-down OFF: MPSPD[n] is not in place,

**OR** if MPSPD[n] is in place NoPdPS[n] = '1' cuts off the pull-down.

**OR** selecting **NchOpDPS**[n] = '1' cuts off the pull-down.

Pull-up ON \* : MPSPU[n] must be in place,

AND the bit NchOpDPS[n] must be '1',

AND (the bits OM[1,0] in RegSysCntl2 = '00' (input mode) OR any of the port SP terminals

is in output mode with a logic '1' to be driven).

Pull-up OFF\* : MPSPU[n] is not in place,

**OR** if MPSPU[n] is in place **NchOpDPS**[n] = '0' cuts off the pull-up,

**OR** if MPSPU[n] is in place and NchOpDPS[n] = '1' then SerPData[n] = 0 cuts off the pull-up.

For **POWER SAVING** one can switch off the port SP pull resistors between two read phases. No cross current flows in the input amplifier while the port SP is not read.

This power saving feature must only be used in tristate mode (OM[0,1]=0). The recommended order is :

- switch on the pull resistor.

- allow sufficient time RC constant for the pull resistor to drive the line to either Vss or VDD.

- Read the port SP

- · Switch off the pull resistor

Minimum time with current on the pull resistor is 4 periods of the system clock, if the RC constant is lower than 1 system clock period. Adding a NOP before reading moves the number of periods with current in the pull resistor to 6 and the maximum RC delay to 3 clock periods.

### 6.6.3 Nch. Open Drain Outputs

The port SP outputs can be configured as either CMOS or Nch. open drain outputs.

In CMOS both logic '1' and '0' are driven out on the terminal.

In Nch. open drain only the logic '0' is driven out on the terminal, the logic '1' value is high impedance or defined by the internal pull-up resistor (if existing).

Figure 15. CMOS or Nch. Open Drain outputs

### 6.6.4 General Functional Description

After power on or after any reset the serial interface is in serial slave mode with **Start** and **Status** set to 0, LSB first, negative shift edge and all outputs are in high impedance state.

When the **Start** bit is set, the shift operation is enabled and the serial interface is ready to transmit or receive data, eight shift operations are performed: 8 serial data values are read from the data input terminal into the shift register and the previous loaded 8-bits are send out via the data output terminal. After the eight shift operation, an interrupt is generated, and the **Start** bit is reset.

Parallel to serial conversion procedure (master mode example).

Write to RegSCntl1 serial control (clock freq. in master mode, edge and MSB/LSB select).

Write to RegSDataL and RegSDataH (shift out data values).

Write to **RegSCntl2** (Start=1, mode select, status). ---> Starts the shift out

After the eighth clock an interrupt is generated, Start becomes low. Then, interrupt handling

Serial to parallel conversion procedure (slave mode example).

Write to RegSCntl1 (slave mode, edge and MSB/LSB select).

Write to RegSCntl2 (Start=1, mode select, status).

After eight serial clocks an interrupt is generated, Start becomes low.

Interrupt handling.

Shift register RegSDataL and RegSDataH read.

A new shift operation can be authorized.

# 6.6.5 Detailed Functional Description

Master or Slave mode is selected in the control register RegSCntl1.

In Slave mode, the serial clock comes from an external device and is input via the PSP[3] terminal as a synchronous clock (SCLKIn) to the serial interface. The serial clock is ignored as long as the **Start** bit is not set. After setting **Start**, only the eight following active edges of the serial clock input PSP[3] are used to shift the serial data in and out. After eight serial clock edges the **Start** bit is reset. The PSP[1] terminal is a copy of the (**Start OR Status**) bit values, it can be used to indicate to the external master, that the interface is ready to operate or it can be used as a chip select signal in case of an external slave.

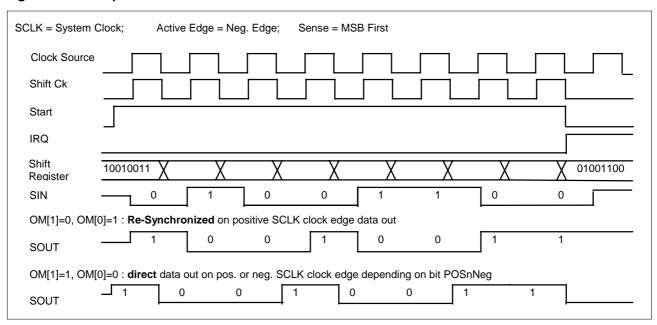

In Master mode, the synchronous serial clock is generated internally from the system clock. The frequency is selected from one out of three sources ( MS0 and MS1 bits in RegSCntl1). The serial shifting clock is only generated during Start = high and is output to the SCLK terminal as the Master Clock (SCLKOut). When Start is low, the serial clock output on PSP[3] is 0.

An interrupt request **IRQSerial** is generated after the eight shift operations are done. This signal is set by the last negative edge of the serial interface clock on PSP[3] (master or slave mode) and is reset to 0 by the next write of **Start** or by any reset. This interrupt can be masked with register **RegIRQMask3**. For more details about the interrupt handling see chapter 10.

Serial data input on PSP[0] is sampled by the positive or negative serial shifting clock edge, as selected by the Control Register **POSnNeg** bit. Serial data input is shifted in LSB first or MSB first, as selected by the Control Register **MSBnLSB** bit.

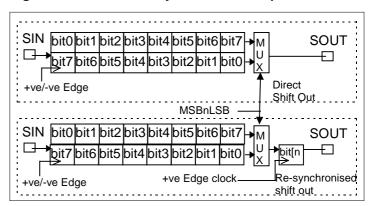

#### 6.6.6 Output Modes

Serial data output is given out in two different ways (Refer also to Figure 16 and Figure 17).

#### - OM[1] = 1, OM[0] = 0:

The serial output data is generated with the selected shift register clock (**POSnNeg**). The first data bit is available <u>directly</u> after the **Start** bit is set.

#### -OM[1] = 0, OM[0] = 1:

The serial output data is <u>re-synchronized</u> by the positive serial interface clock edge, independent of the selected clock shifting edge. The first data bit is available on the first positive serial interface clock edge after Start='1'.

Figure 16. Direct or Re-Synchronized Output

Table 6.6.6 Output Mode Selection in RegSCntl2

| OM[1] | OM[0] | Output mode             | Description                                  |

|-------|-------|-------------------------|----------------------------------------------|

| 0     | 0     | Tristate                | Output disable (tristate on PSP[3:0])        |

| 0     | 1     | Serial-<br>Synchronized | Re-synchronized positive edge data shift out |

| 1     | 0     | Serial-Direct           | Direct shift pos. or neg. edge data out      |

| 1     | 1     | Parallel                | Parallel port SP output                      |

Tristate output is selected by default.

# 6.6.7 Reset and Sleep on Port SP

During circuit initialization, all option registers are reset by Power On Reset and therefore all pull-ups are off and all pull-downs are on. During Sleep mode, Port SP inputs are cut-off , the circuit is in Reset State. However the Reset State does not reset the option registers and pull-downs, if previously turned on, remain on even during Sleep mode. After any reset the serial interface parameters are reset to : Slave mode, Start and Status = 0, LSB first, negative edge shift , PSP[3:0] tristate.

**Note:** A write operation in the control registers or in the data registers while **Start** is high will change internal values and may cause an error condition. The user must take care of the serial interface status before writing internal registers. In order to read the correct values on the data registers, the shift operation must be halted during the read accesses.

# 6.7 Serial Interface Registers

Table 6.7.1 Register RegSCntl1

| Bit | Name    | Reset | R/W | Description                                   |  |

|-----|---------|-------|-----|-----------------------------------------------|--|

| 3   | MS1     | 0     | R/W | R/W Frequency selection                       |  |

| 2   | MS0     | 0     | R/W | Frequency selection                           |  |

| 1   | POSnNeg | 0     | R/W | Positive or negative clock edge selection for |  |

|     | _       |       |     | shift operation                               |  |

| 0   | MSBnLSB | 0     | R/W | Shift MSB or LSB value first                  |  |

Default "0" is: Slave mode external clock, negative edge, LSB first

**Table 6.7.2 Frequency and Master Slave Mode Selection**

| MS1 | MS0 | Description                     |  |  |  |

|-----|-----|---------------------------------|--|--|--|

| 0   | 0   | Slave mode: Clock from external |  |  |  |

| 0   | 1   | Master mode: System clock / 4   |  |  |  |

| 1   | 0   | Master mode: System clock / 2   |  |  |  |

| 1   | 1   | Master mode: System clock       |  |  |  |

Table 6.7.3 Register RegSCntl2

| Bit | Name   | Reset | R/W | Description                           |

|-----|--------|-------|-----|---------------------------------------|

| 3   | Start  | 0     | R/W | Enabling the interface,               |

| 2   | Status | 0     | R/W | Ready or Chip Select output on PSP[1] |

| 1   | OM[1]  | 0     | R/W | Output mode select 1                  |

| 0   | OM[0]  | 0     | R/W | Output mode select 0                  |

Default "0" is: Interface disabled, status 0, serial mode, output tristate.

Table 6.7.4 Register RegSDataL

| Bit | Name        | Reset | R/W | Description            |

|-----|-------------|-------|-----|------------------------|

| 3   | SerDataL[3] | 0     | R/W | Serial data low nibble |

| 2   | SerDataL[2] | 0     | R/W | Serial data low nibble |

| 1   | SerDataL[1] | 0     | R/W | Serial data low nibble |

| 0   | SerDataL[0] | 0     | R/W | Serial data low nibble |

Default "0" is: Data equal 0.

Table 6.7.5 Register RegSDataH

| Bit | Name        | Reset | R/W | Description             |

|-----|-------------|-------|-----|-------------------------|

| 3   | SerDataH[3] | 0     | R/W | Serial data high nibble |

| 2   | SerDataH[2] | 0     | R/W | Serial data high nibble |

| 1   | SerDataH[1] | 0     | R/W | Serial data high nibble |

| 0   | SerDataH[0] | 0     | R/W | Serial data high nibble |

Default "0" is: Data equal 0.

# Table 6.7.6 Register RegSPData

| Bit | Name        | Reset | R/W  | Description          |

|-----|-------------|-------|------|----------------------|

| 3   | SerPData[3] | 0     | R*/W | Parallel output data |

| 2   | SerPData[2] | 0     | R*/W | Parallel output data |

| 1   | SerPData[1] | 0     | R*/W | Parallel output data |

| 0   | SerPData[0] | 0     | R*/W | Parallel output data |

R\*: The input terminal value is read, not the register

**Table 6.7.7 Option Register OPTNoPdPS**

| Bit | Name      |   | R/W | Description            |

|-----|-----------|---|-----|------------------------|

| 3   | NoPdPS[3] | 0 | R/W | No pull-down on PSP[3] |

| 2   | NoPdPS[2] | 0 | R/W | No pull-down on PSP[2] |

| 1   | NoPdPS[1] | 0 | R/W | No pull-down on PSP[1] |

| 0   | NoPdPS[0] | 0 | R/W | No pull-down on PSP[0] |

Default "0" is: Pull-down on

# **Table 6.7.8 Option Register OPTNchOpDPS**

| Bit | Name        |   | R/W | Description               |

|-----|-------------|---|-----|---------------------------|

| 3   | NchOpDPS[3] | 0 | R/W | Nch. Open Drain on PSP[3] |

| 2   | NchOpDPS[2] | 0 | R/W | Nch. Open Drain on PSP[2] |

| 1   | NchOpDPS[1] | 0 | R/W | Nch. Open Drain on PSP[1] |

| 0   | NchOpDPS[0] | 0 | R/W | Nch. Open Drain on PSP[0] |

Default "0" is: CMOS output

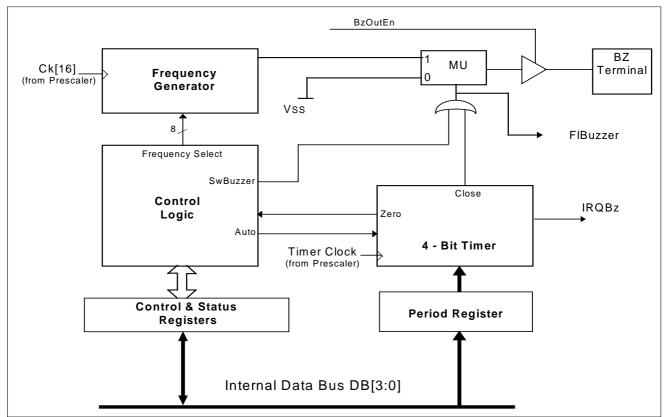

### 7. Melody, Buzzer

A normal application is to drive a buzzer connected onto the terminal Buzzer.

This peripheral cell is a combination of a 7 frequency tone generator and a 4-bit timer, used to provide a 50% duty cycle signal on the Buzzer terminal of a pre-selected length and frequency. The Buzzer terminal is active as long as the timer is not 0 or the **SwBuzzer** is set to '1'. The 4-bit timer can be used for another application independent of the Buzzer terminal by selecting "silence" instead of another frequency on the Buzzer output. "Silence" can also be used as part of a melody, or to switch off the buzzer.

To use the buzzer independent of the 4-bit timer one has to set the switch **SwBuzzer**. This bit is in register **RegMelTim** and selects the signal duration on the buzzer output. If **SwBuzzer**=1 then the signal is output until the bit is set back to 0 . With **SwBuzzer**=0 the output signal duration is controlled by the 4bit timer. If neither the **SwBuzzer** or the timer are active, the Buzzer terminal is on 0.

The high impedance state setting with **BzOutEn** is independent of the **SwBuzzer** and Timer settings. As soon as the bit is set to 1 the Buzzer terminal is set tristate. See also Figure 19.

Figure 19. Melody Generator Block Diagram

#### 7.1 4-Bit Timer

The timer has 2 modes:

- Single run mode (Auto=0)

- Continuos run mode (Auto=1)

Mode selection and timer count down frequency is done in register **RegMelTim.** All timer frequencies are coming from the prescaler. The 4-bit timer can be used independent of the melody buzzer application.

Whenever the timer reaches 0 it generates an interrupt request IRQBz in the register RegIRQ2. This interrupt can be masked with the bit MaskIRQBz in register RegIRQMask2. By writing 0 into the timer period register the timer stops immediately and does not generate an interrupt.

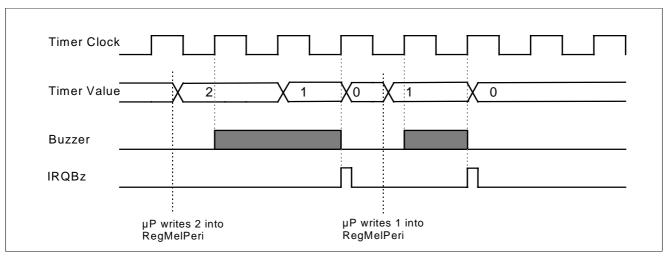

### 7.1.1 Single Run Mode

The RegMelPeri value and the selected timer frequency in RegMelTim control the timer duration. The timer is counting down from its previously charged value until it reaches 0. On 0 the timer stops and generates an interrupt request. The buzzer frequency output is enabled after the <u>next positive timer clock edge</u> and remains enabled until the timer reaches 0.

Figure 20. Single Run Mode

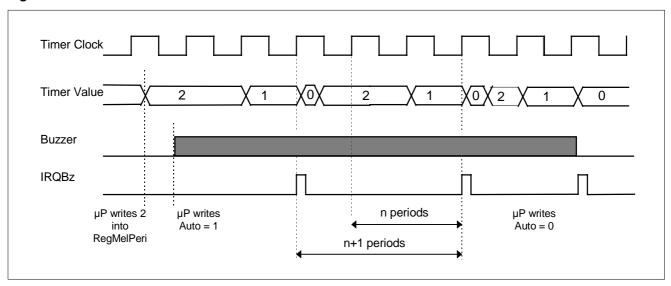

#### 7.1.2 Continuos Run Mode

This is almost the same as the single run mode only that in this case the timer after reaching 0 reloads itself automatically with the register **RegMelPeri** value. Every time the timer reaches 0 an interrupt request is send. There are 2 ways to stop the continuos mode.

- First, changing the mode to single run mode. As the timer reaches 0 it stops. The last period after **Auto**=0 is of length **RegMelPeri** + 1.

- Second, loading 0 into the timer period register **RegMelPeri** stops the timer immediately, no interrupt is generated and the **Auto** flag is reset. The buzzer frequency output is <u>enabled directly</u> by writing **Auto**=1.

Figure 21. Continuos Run Mode

# 7.2 Programming Order

Single run mode usage

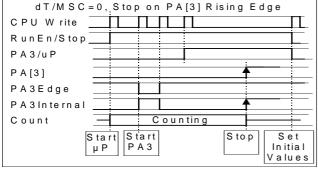

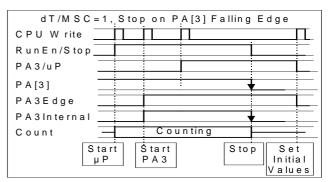

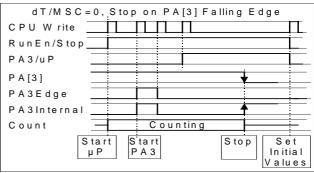

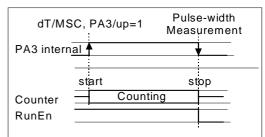

1st, selecting the buzzer frequency into RegMelFSel.