# Dual 150/300mA LDO with POR

### DESCRIPTION

The EUP7212 is a dual low dropout linear regulator. The first regulator is capable of sourcing 150mA, while the second regulator can source up to 300mA and includes a power-on reset function.

The EUP7212 is stable with small ceramic output capacitors. The performance of EUP7212 is optimized for battery power systems to deliver low noise, low dropout voltage, low quiescent current and excellent line and load transient response.

The EUP7212 is available in fixed output voltages in the 8-pin 3mm×3mm DFN leadless package.

### **FEATURES**

- Input Voltage Range: 2.5V to 5.5V

- Stable with Ceramic Output Capacitor

- 2 LDO Outputs:

- Output 1-150mA Output Current

- Output 2-300mA Output Current

- Power-on Reset Function with Adjustable Delay Time

- Low Dropout Voltage of 100mV@150mA

- Low Quiescent Current of 150μA

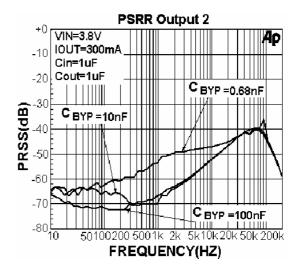

- High PSRR 70dB at 1kHz:

- Thermal Shutdown Protection

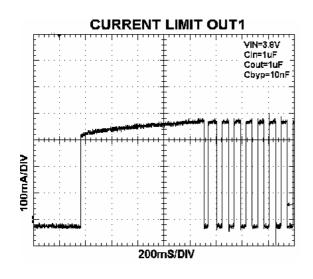

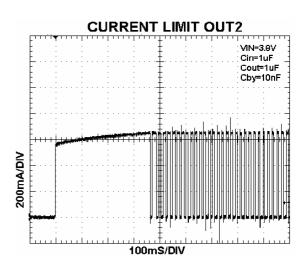

- Current Limit Protection

- 3mmx3mm DFN-8 Package

- RoHS Compliant and 100% Lead (Pb)-Free

### **APPLICATIONS**

- Cellular Phones

- Wireless Modems

- PDAs

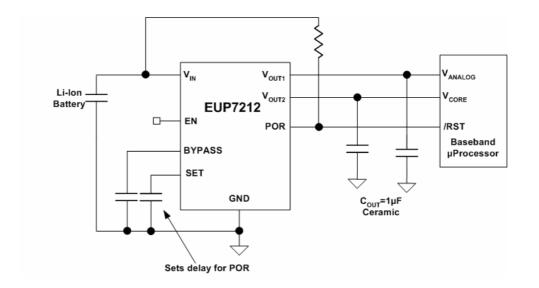

## **Typical Application**

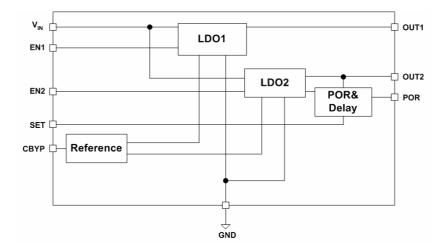

## **Block Diagram**

## **Pin Configurations**

| Part Number | Pin Configurations |         |  |

|-------------|--------------------|---------|--|

|             | VIN 1              | 8 VOUT1 |  |

| EUP7212     | EN 2               | 7 VOUT2 |  |

| DFN-8       | ВҮР 3              | 6 POR   |  |

|             | SET 4              | 5 GND   |  |

## **Pin Description**

| PIN          | Pin | DESCRIPTION                                                                                                                                                     |  |

|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{\rm IN}$ | 1   | Input voltage of the LDO                                                                                                                                        |  |

| EN           | 2   | Enable input: Enables to regulator 1 outputs. Active high input. High=on, low=off. Do not leave floating.                                                       |  |

| BYPASS       | 3   | Optional bypass capacitor for noise reduction                                                                                                                   |  |

| SET          | 4   | Delay Set Input: Connect external capacitor to GND to set the internal delay for the POR output. When left open, there is no delay. This pin cannot be grounded |  |

| GND          | 5   | Ground                                                                                                                                                          |  |

| POR          | 6   | Power-On Reset Output: Open-Drain Output. Active low indicates an output undervoltage condition on regulator 2                                                  |  |

| VOUT2        | 7   | Output of regulator 2: 300mA output current                                                                                                                     |  |

| VOUT1        | 8   | Output of regulator 1: 150mA output current                                                                                                                     |  |

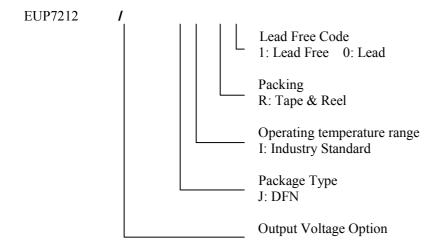

## **Ordering Information**

| Order Number        | Package Type | Marking       | Operating Temperature range |

|---------------------|--------------|---------------|-----------------------------|

| EUP7212-1.8/2.8JIR1 | DFN-8        | DEXX<br>P7212 | -40 °C to 125°C             |

| EUP7212-1.8/2.8JIR0 | DFN-8        | DEXX<br>P7212 | -40 °C to 125°C             |

| EUP7212-3.3/1.8JIR1 | DFN-8        | ндхх<br>Р7212 | -40 °C to 125°C             |

| EUP7212-3.3/1.8JIR0 | DFN-8        | ндхх<br>Р7212 | -40 °C to 125°C             |

## **Absolute Maximum Ratings**

## **Operating Ratings**

### **Electrical Characteristics**

$V_{IN} = V_{OUT} + 1.0V, \ I_{OUT} = 1 \\ mA, \ C_{OUT} = 1 \\ \mu F. \ Typical \ values \ and \ limits \ appearing \ in \ standard \ type face \ are \ for \ T_J = 25 \\ ^{\circ}C$

| Symbol            | Parameter                      | Conditions                                     | Min  | Тур     | Max     | Units   |  |

|-------------------|--------------------------------|------------------------------------------------|------|---------|---------|---------|--|

| $V_{OUT}$         | Output Voltage Accuracy        | Variation from nominal Vout                    | -1.5 |         | 1.5     | %       |  |

| Reg Line          | Line Regulation                | Input range Vin=Vout+1V to 5.5V                | -0.2 | 0.02    | 0.2     | %/V     |  |

| Reg Load          | Load Regulation                | Iout=100μA to 150mA(Vout 1 & Vout 2)           |      | 0.7     | 0.7 2 % |         |  |

|                   |                                | Iout=100μA to 300mA(Vout)                      |      | 1       | 2.5     |         |  |

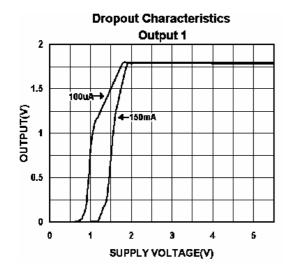

| V <sub>Drop</sub> | Dropout Voltage                | Iout=150mA(Vout 1)                             |      | 120     | 180     | mV      |  |

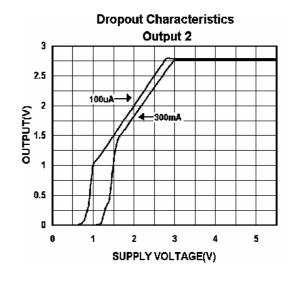

|                   |                                | Iout= 300mA(Vout 2)                            |      | 240 350 |         | 111 V   |  |

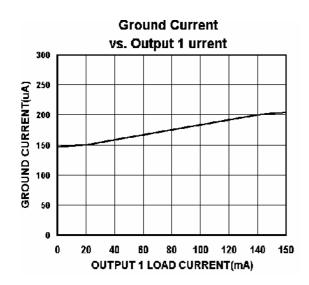

| I <sub>O</sub>    | Ground Pin Current             | Iout 1=Iout2=0                                 |      | 150     | 170     | μА      |  |

| 1Q                |                                | Iout 1=150mA & Iout=300mA                      |      | 250     | 300     |         |  |

| IQ_SD             | Ground Pin Current in Shutdown | $V_{EN}$ 0.4V                                  |      | 3       | 5       | μΑ      |  |

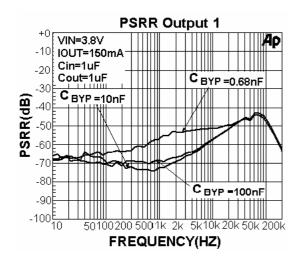

| PSRR              | Ripple Rejection               | Freq.=1Khz; Cout=1.0µF; C <sub>BYP</sub> =10nF |      | 70      |         | dB      |  |

| Iout(Max)         | Current Limit                  | Output 1 Short to Ground                       | 150  | 340     |         | A       |  |

| ioui(iviax)       | Current Limit                  | Output 2 Short to Ground                       | 300  | 580     |         | mA      |  |

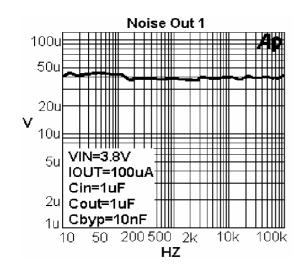

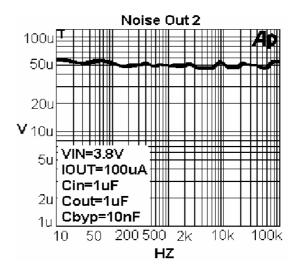

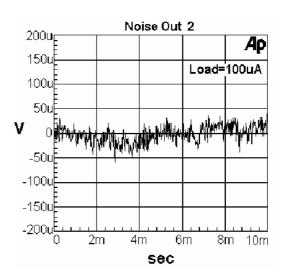

| Noise             | Output Voltage Noise           | Cout= $1.0\mu$ F; $C_{BYP}=10n$ F;             |      | 40      |         | μVrms   |  |

|                   | 1 0                            | BW=10~100KHz                                   | 40   |         |         | μντιτισ |  |

| Enable Inp        | ut                             |                                                |      | r       |         |         |  |

| $V_{\rm EN}$      | Enable Input voltage           | Logic Low (Regulator Shutdown)                 |      |         | 0.6     | V       |  |

| V EN              |                                | Logic High(Regulator Enable)                   | 1.8  |         |         |         |  |

| $I_{EN}$          | Enable Input Current           | V <sub>IL</sub> <0.6V (Regulator Shutdown)     | -0.5 | 0.01    | 0.5     | II /\ I |  |

|                   |                                | V <sub>IH</sub> >1.8V (Regulator Enable)       | -0.5 | 0.01    | 0.5     |         |  |

| POR Outp          | ut                             | 1                                              | 1    | ı       | 1       |         |  |

| ${ m V}_{ m TH}$  | Low Threshold                  | Low Threshold, % of nominal Vout 2 (Flag ON)   | 90   |         |         | %       |  |

|                   | High Threshold                 | High Threshold, % of nominal Vout 2 (Flag OFF) |      |         | 96      | %       |  |

| V <sub>OL</sub>   | POR output logic low voltage;  | $I_L$ =250 $\mu$ A                             |      | 0.17    | 0.2     | V       |  |

| $I_{POR}$         | Flag leakage Current           | Flag 0FF                                       | -1   | 0.01    | 1       | μA      |  |

| SET Input         |                                |                                                |      |         |         |         |  |

| I <sub>SET</sub>  | SET Pin Current Source         | Set pin Voltage to 0                           | 0.75 | 1.25    | 1.75    | μΑ      |  |

| V <sub>SET</sub>  | SET Pin Threshold<br>Voltage   | POR = High                                     |      | 1.25    |         | V       |  |

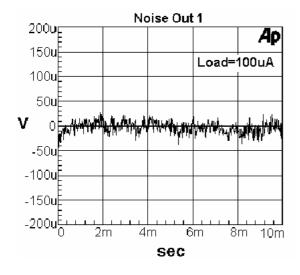

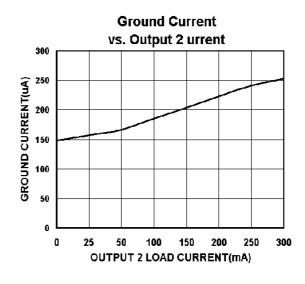

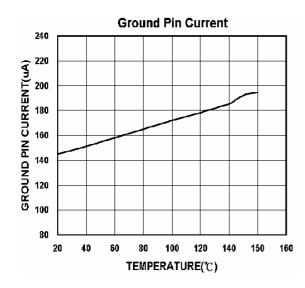

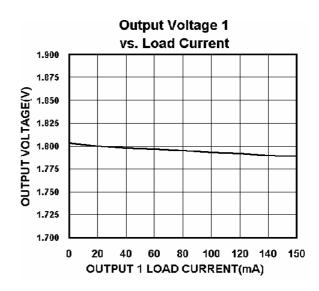

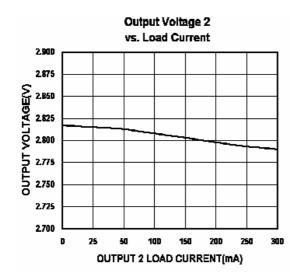

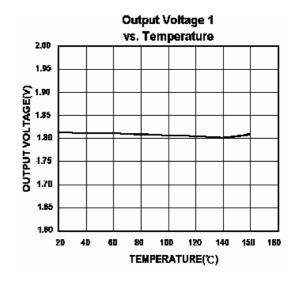

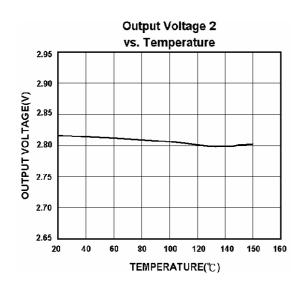

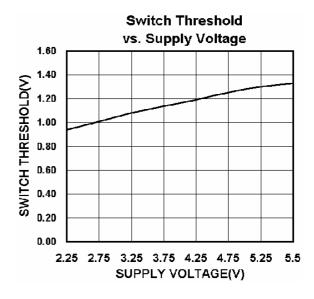

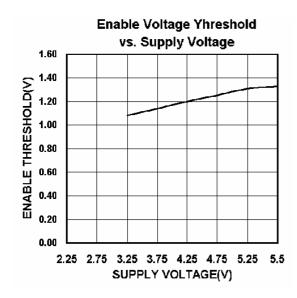

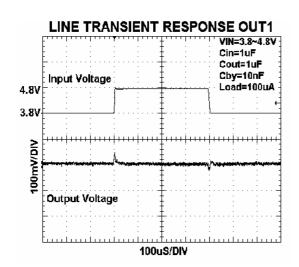

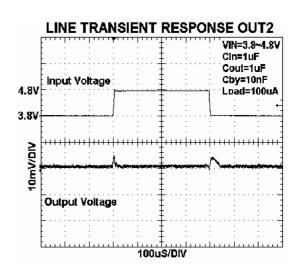

## **Typical Operating Characteristics**

Unless otherwise specified,  $C_{IN}$ = $C_{COUT}$ = $1\mu F$  Ceramic,  $C_{BYPASS}$ =100nF,  $V_{IN}$ = $V_{OUT}$ +1V,  $I_{OUT}$ = $100\mu A$   $T_A$ =25°C, Enable pin is tied to  $V_{IN}$ .

## **Application Note**

### **Function Description**

The EUP7212 is a high performance, low quiescent current power management IC consisting of two  $\mu$ Cap low dropout regulators, a power-on reset (POR) circuit and an open-drain driver. The first regulator is capable of sourcing 150mA at output voltages from 1.25V to 5V. The second regulator is capable of sourcing 300mA of current at output voltages from 1.25V to 5V. The second regulator has a POR circuit that monitors its output voltage and indicates when the output voltage is within 5% of nominal. The POR offers a delay time that is externally programmable with a single capacitor to ground. An open-drain driver completes the power management chipset, offering the capability of driving LEDs for keypad backlighting in applications such as cellphones.

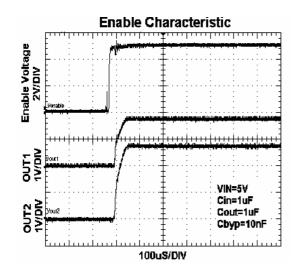

#### **Enable**

The enable input allows for logic control of both output voltages with one enable input. The EUP7212 is turned off by pulling the  $V_{\rm EN}$  pin low, and turned on by pulling it high. If this feature is not used, the  $V_{\rm EN}$  pin should be tied to  $V_{\rm IN}$  to keep the regulator output on at all time. To assure proper operation, the signal source used to drive the  $V_{\rm EN}$  input must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under  $V_{\rm IL}$  and  $V_{\rm IH}$ .

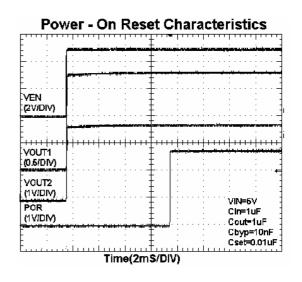

#### Power-On Reset (POR)

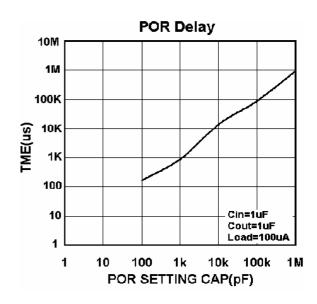

The power-on reset output is an open-drain N-Channel device, requiring a pull-up resistor to either the input voltage output voltage for proper voltage for proper voltage levels. The POR output has a delay time that is programmable with a capacitor from the SET pin to ground. The delay time can be programmed to be as long as 1 second.

The SET pin is a current source output that charges a capacitor that sets the delay time for the power-on reset output. The current source is a  $1\mu A$  current source that charges a capacitor up from 0V. When the capacitor reaches 1.25V, the output of the POR is allowed to go high.

#### **External Capacitors**

Like any low-dropout regulator, the EUP7212 requires external capacitors for regulator stability. The EUP7212 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

### **Input Capacitor**

An input capacitance of  $\ge 1\mu F$  or greater is required between the EUP7212 input pin and ground (the amount of the capacitance may be increased without limit).

This capacitor must be located a distance of not more than 1cm from the input pin and returned to a clean analog ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

#### **Output Capacitor**

The EUP7212 is designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (temperature characteristics X7R, X5R, Z5U, or Y5V) in 1 to  $22\mu F$  range with  $5m\Omega$  to  $500m\Omega$  ESR range is suitable in the EUP7212 application circuit.

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR (Equivalent Series Resistance) value which is within a stable range  $(5m\Omega \text{ to } 500m\Omega)$

## **No-Load Stability**

The EUP7212 will remain stable and in regulation with no external load. This is specially important in CMOS RAM keep-alive applications.

### **Capacitor Characteristics**

The EUP7212 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer: for capacitance values in the range of  $1\mu F$  to  $4.7\mu F$  range, ceramic capacitors are the smallest, least expensive and have the lowest ESR values (which makes them best for eliminating high frequency noise). The ESR of a typical  $1\mu F$  ceramic capacitor is in the range of  $20m\Omega$  to  $40m\Omega$ , which easily meets the ESR requirement for stability by the EUP7212.

The ceramic capacitor's capacitance can vary with temperature. The capacitor type X7R, which operates over a temperature range of -55°C to +125°C, will only vary the capacitance to within  $\pm 15\%$ . Most large value ceramic capacitors ( $\approx 2.2 \mu F$ ) are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more than 50% as the temperature goes from 25°C to 85°C. Therefore, X7R is recommended over Z5U and Y5V in applications where the ambient temperature will change significantly above or below 25°C.

#### **Noise Bypass Capacitor**

Connecting a  $0.01\mu F$  capacitor between the  $C_{BYPASS}$  pin and ground significantly reduces noise on the regulator output. This cap is connected directly to a high impedance node in the bandgap reference circuit. Any significant loading on this node will cause a change on the regulated output voltage. For this reason, DC leakage current through this pin must be kept as low as possible for best output voltage accuracy. The types of capacitors best suited for the noise bypass capacitor are ceramic and film.

Unlike many other LDO's, addition of a noise reduction capacitor does not effect the load transient response of the device.

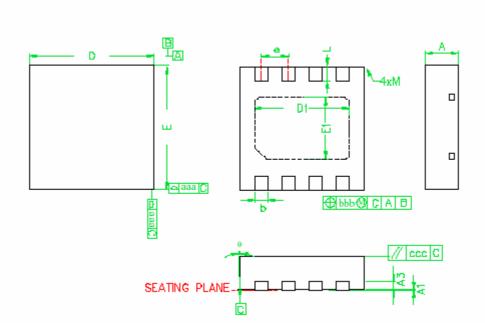

## **Packaging Information**

DFN-8

## NOTE

- 1. All dimensions are in millimeters,  $\theta$  is in degrees

- 2. M: The maximum allowable corner on the molded plastic body corner

- 3. Dimension D does not include mold protrusions or gate burrs. Mold protrusions and gate burrs shall not exceed 0.15mm per side

- 4. Dimension E does not include interterminal mold protrusions or terminal protrusions. Interminal mold protrusions and/or terminal protrusions shall not exceed 0.20mm per side

- 5. Dimension b applies to plated terminals. Dimension A1 is primarily Y terminal plating, but may or may not include a small protrusion of terminal below the bottom surface of the package

- 6. Burr shall not exceed 0.060mm

- 7. JEDEC MO-229

| SYMBOLS | DIMENSIONS IN MILLIMETERS |          |      |

|---------|---------------------------|----------|------|

|         | MIN.                      | NOM.     | MAX. |

| A       | 0.81                      | 0.9      | 1.00 |

| A1      | 0                         | 0.015    | 0.03 |

| A3      |                           | 0.20 REF |      |

| В       | 0.25                      | 0.30     | 0.37 |

| D       | 2.85                      | 3.00 BSC | 3.15 |

| D1      |                           | 2.3 BSC  |      |

| Е       | 2.85                      | 3.00 BSC | 3.15 |

| E1      |                           | 1.5 BSC  |      |

| e       |                           | 0.65 BSC |      |

| L       | 0.25                      | 0.35     | 0.45 |

| aaa     |                           | 0.25     |      |

| bbb     |                           | 0.10     |      |

| ccc     |                           | 0.10     |      |

| M       |                           |          | 0.05 |

| θ       | -12                       |          | 0    |