Data Sheet

#### November 30, 2005

## 100MHz, JFET Input, High Slew Rate, Uncompensated, Operational Amplifier

intercil

The HA-5160 is a wideband, uncompensated, operational amplifier with FET/Bipolar technologies and Dielectric Isolation. This monolithic amplifier features superior high frequency capabilities further enhanced by precision laser trimming of the input stage to provide excellent input characteristics. This device has excellent phase margin at a closed loop gain of 10 without external compensation.

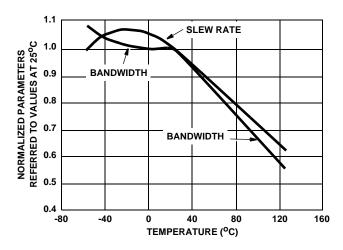

The HA-5160 offers a number of important advantages over similar FET input op amps from other manufacturers. In addition to superior bandwidth and settling characteristics, the Intersil devices have nearly constant slew rate, bandwidth, and settling characteristics over the operating temperature range. This provides the user predictable performance in applications where settling time, full power bandwidth, closed loop bandwidth, or phase shift is critical. Note also that Intersil specified all parameters at ambient (rather than junction) temperature to provide the designer meaningful data to predict actual operating performance.

Complementing the HA-5160's predictable and excellent dynamic characteristics are very low input offset voltage, very low input bias current, and a very high input impedance. This ideal combination of features make these amplifiers most suitable for precision, high speed, data acquisition system designs and for a wide variety of signal conditioning applications. The HA-5160 provides excellent performance for applications which require both precision and high speed performance.

Military version (/883) data sheets are available upon request.

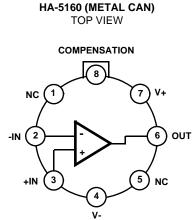

## Pinout

NOTE: Case connected to V-.

#### Features

| - Wide Gain Bandwidth (A $_V \geq$ 10) 10  | 00MHz  |

|--------------------------------------------|--------|

| • High Slew Rate 12                        | 20V/µs |

| Settling Time                              | 280ns  |

| • Power Bandwidth                          | .9MHz  |

| Offset Voltage                             | 1.0mV  |

| • Bias Current                             | 20pA   |

| Compensation Pin for Unity Gain Capability |        |

## Compensation Pin for Unity Gain Capability

### Applications

- · Video and RF Amplifiers

- Data Acquisition

- Pulse Amplifiers

- Precision Signal Generation

## **Ordering Information**

| PART<br>NUMBER | PART<br>MARKING |         |                 | PKG.<br>DWG. # |

|----------------|-----------------|---------|-----------------|----------------|

| HA2-5160-5     | HA2-5160-5      | 0 to 75 | 8 Pin Metal Can | T8.C           |

1

#### **Absolute Maximum Ratings**

| Voltage Between V+ and V                       | 40V  |

|------------------------------------------------|------|

| Differential Input Voltage                     | 40V  |

| Peak Output Current Full Short Circuit Protect | tion |

#### **Operating conditions**

| Temperature Ranges                                 |    |

|----------------------------------------------------|----|

| HA-5160-5                                          | °C |

| Supply Voltage Range (Typical) $\pm 7V$ to $\pm 1$ | 8V |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)  | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------------------------------------|------------------------|------------------------|

| Metal Can Package                     | 155                    | 67                     |

| Maximum Junction Temperature          |                        | 175°C                  |

| Maximum Storage Temperature Range .   | 6                      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 1 | 0s)                    | 300°C                  |

#### **Die Characteristics**

| Number of Transistors                  | 82   |

|----------------------------------------|------|

| Substrate Potential (Powered Up) Float | ting |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## $\label{eq:superior} \textbf{Electrical Specifications} \quad V_{SUPPLY} = \pm 15V, \, \text{Unless Otherwise Specified}$

| PARAMETER                     | TEST CONDITIONS                          | TEMP.<br>(°C) | MIN | ТҮР              | МАХ | UNITS |

|-------------------------------|------------------------------------------|---------------|-----|------------------|-----|-------|

| INPUT CHARACTERISTICS         |                                          |               | 1   | I                | L   |       |

| Offset Voltage                |                                          | 25            | -   | 1                | 3   | mV    |

|                               |                                          | Full          | -   | 3                | 5   | mV    |

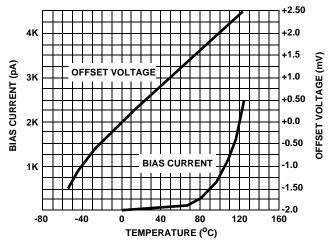

| Offset Voltage Average Drift  |                                          | Full          | -   | 20               | -   | μV/°C |

| Bias Current                  |                                          | 25            | -   | 20               | 50  | pА    |

|                               |                                          | Full          | -   | 5                | 10  | nA    |

| Offset Current                |                                          | 25            | -   | 2                | 10  | рА    |

|                               |                                          | Full          | -   | 2                | 5   | nA    |

| Input Capacitance             |                                          | 25            | -   | 5                | -   | pF    |

| Input Resistance              |                                          | 25            | -   | 10 <sup>12</sup> | -   | Ω     |

| Common Mode Range             |                                          | Full          | ±10 | ±11              | -   | V     |

| TRANSFER CHARACTERISTICS      | 1                                        |               |     | I                | I   |       |

| Large Signal Voltage Gain     | V <sub>OUT</sub> = ±10V,                 | 25            | 75  | 150              | -   | kV/V  |

|                               | $R_L = 2k\Omega$                         | Full          | 60  | 100              | -   | kV/V  |

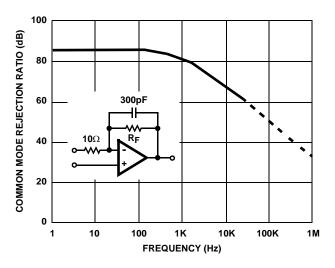

| Common Mode Rejection Ratio   | $V_{CM} = \pm 10V$                       | Full          | 74  | 80               | -   | dB    |

| Minimum Stable Gain           |                                          | 25            | 10  | -                | -   | V/V   |

| Gain Bandwidth Product        | $A_V \ge 10$                             | Full          | -   | 100              | -   | MHz   |

| OUTPUT CHARACTERISTICS        | I                                        |               |     | I                | 1   |       |

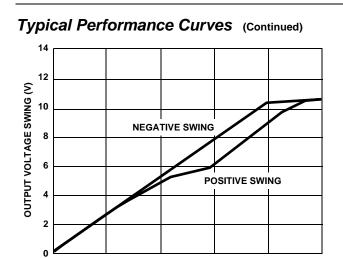

| Output Voltage Swing          | $R_L = 2k\Omega$                         | 25            | ±10 | ±11              | -   | V     |

|                               |                                          | Full          | ±10 | ±11              | -   | V     |

| Output Current                | V <sub>OUT</sub> = ±10V                  | 25            | ±10 | ±20              | -   | mA    |

| Output Short Circuit Current  |                                          | 25            | -   | ±35              | -   | mA    |

| Full Power Bandwidth (Note 2) | $V_{OUT} = \pm 10V,$<br>$R_L = 2k\Omega$ | 25            | 1.6 | 1.9              | -   | MHz   |

| Output Resistance             | Open Loop                                | 25            | -   | 50               | -   | Ω     |

| TRANSIENT RESPONSE (Note 3)   |                                          | I             | 1   | 1                | 1   | l     |

| Rise Time                     | A <sub>V</sub> = +10                     | 25            | -   | 20               | -   | ns    |

| Slew Rate                     | A <sub>V</sub> = +10                     | 25            | 100 | 120              | -   | V/µs  |

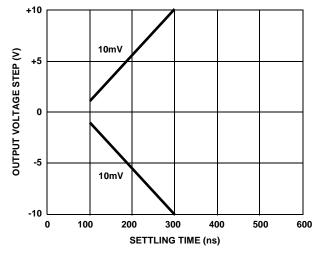

| Settling Time (Note 4)        | A <sub>V</sub> = -10                     | 25            | -   | 280              | -   | ns    |

**Electrical Specifications**  $V_{SUPPLY} = \pm 15V$ , Unless Otherwise Specified (Continued)

| PARAMETER                    | TEST CONDITIONS              | TEMP.<br>(°C) | MIN | ТҮР | МАХ | UNITS |  |  |

|------------------------------|------------------------------|---------------|-----|-----|-----|-------|--|--|

| POWER SUPPLY CHARACTERISTICS |                              |               |     |     |     |       |  |  |

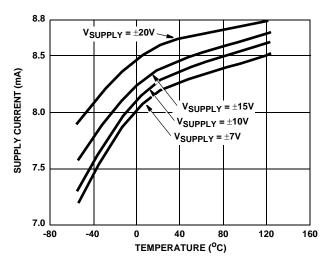

| Supply Current               |                              | Full          | -   | 8   | 10  | mA    |  |  |

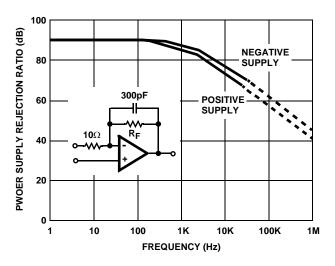

| Power Supply Rejection Ratio | $V_S = \pm 10V$ to $\pm 20V$ | 25            | 74  | 86  | -   | dB    |  |  |

NOTES:

2. Full Power Bandwidth guaranteed, based on slew rate measurement using: FPBW =  $\frac{\text{Slew Ra}}{2-V}$

3. Refer to Test circuits section of the data sheet.

4. Settling Time is measured to 0.2% of final value for a 10V output step.

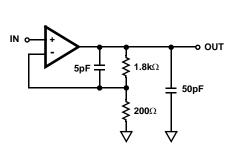

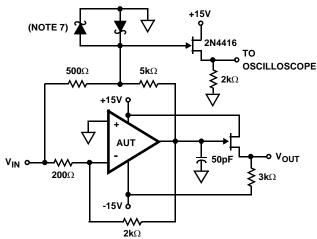

## **Test Circuits and Waveforms**

NOTES:

5. A<sub>V</sub> = -10.

6. Feedback and summing resistors should be 0.1% matched.

7. Clipping diodes are optional. HP5082-2810 recommended.

#### FIGURE 2. SETTLING TIME TEST CIRCUIT

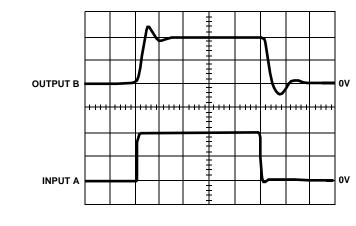

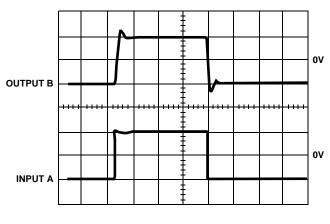

Vertical Scale: A = 10mV/Div., B = 100mV/Div. Horizontal Scale: 100ns/Div.

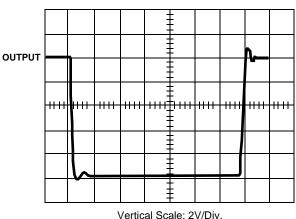

#### SMALL SIGNAL RESPONSE

FIGURE 1. LARGE AND SMALL SIGNAL RESPONSE TEST CIRCUIT

Vertical Scale: A = 0.5V/Div., B = 5V/Div. Horizontal Scale: 500ns/Div.

#### LARGE SIGNAL RESPONSE

3

$\frac{\text{Slew Rate}}{2\pi V}$ PEAK

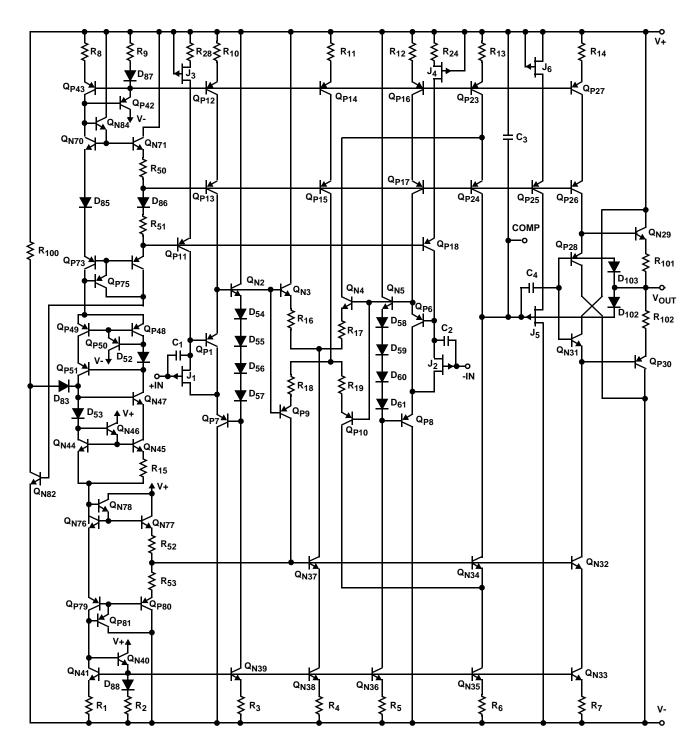

# Schematic Diagram

## Application Information

#### Power Supply Decoupling

Although not absolutely necessary, it is recommended that all power supply lines be decoupled with  $0.01\mu$ F ceramic capacitors to ground. Decoupling capacitors should be located as near to the amplifier terminals as possible.

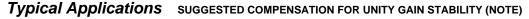

#### Stability

The phase margin of the HA-5160 will be improved by connecting a small capacitor (>10pF) between the output

and the inverting input of the device This small capacitor compensates for the input capacitance of the FET.

#### **Capacitive Loads**

When driving large capacitive loads (>100pF), it is suggested that a small resistor ( $\approx$ 100 $\Omega$ ) be connected in series with the output of the device and inside the feedback loop.

#### **Power Supply Minimum**

The absolute supply minimum is  $\pm 6V$  and the safe level is  $\pm 7V.$

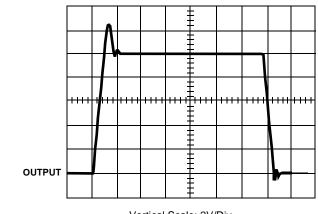

Horizontal Scale: 500ns/Div.

FIGURE 3A. INVERTING UNITY GAIN CIRCUIT

15pF

FIGURE 3. GAIN OF -1

Vertical Scale: 2V/Div. Horizontal Scale: 500ns/Div.

NOTE: Values were determined experimentally for optimum speed and settling time.

FIGURE 4A. NONINVERTING UNITY GAIN CIRCUIT

OUT

COMPENSATION

FIGURE 4B. NONINVERTING UNITY GAIN PULSE RESPONSE

FIGURE 4. GAIN OF +1

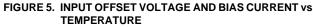

FIGURE 7. OUTPUT VOLTAGE SWING vs FREQUENCY

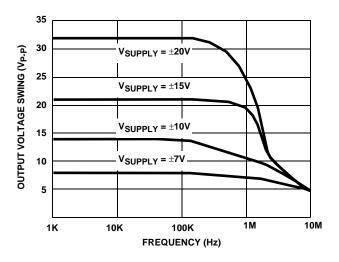

FIGURE 9. INPUT NOISE VOLTAGE AND NOISE CURRENT vs FREQUENCY

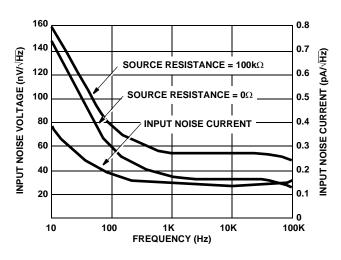

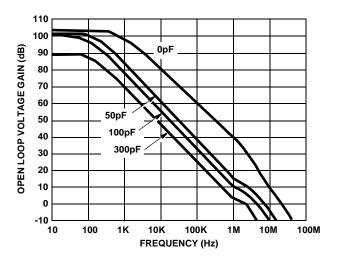

FIGURE 8. OPEN LOOP FREQUENCY RESPONSE FOR VARIOUS COMPENSATION CAPACITANCES

FIGURE 10. NORMALIZED AC PARAMETERS vs TEMPERATURE

LOAD RESISTANCE (Ω)

600

800

1K

400

200

FIGURE 13. COMMON MODE REJECTION RATIO vs FRE-QUENCY

FIGURE 12. SETTLING TIME FOR VARIOUS OUTPUT STEP VOLTAGES

FIGURE 14. POWER SUPPLY REJECTION RATIO vs FRE-QUENCY

FIGURE 15. POWER SUPPLY CURRENT vs TEMPERATURE

7 intersil

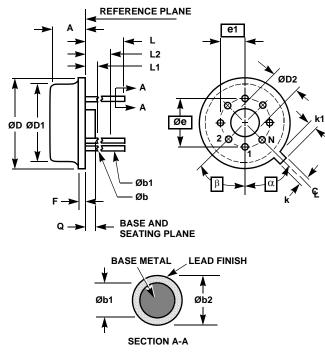

## Metal Can Packages (Can)

#### NOTES:

- 1. (All leads) Øb applies between L1 and L2. Øb1 applies between L2 and 0.500 from the reference plane. Diameter is uncontrolled in L1 and beyond 0.500 from the reference plane.

- 2. Measured from maximum diameter of the product.

- 3.  $\alpha$  is the basic spacing from the centerline of the tab to terminal 1 and  $\beta$  is the basic spacing of each lead or lead position (N -1 places) from  $\alpha$ , looking at the bottom of the package.

- 4. N is the maximum number of terminal positions.

- 5. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 6. Controlling dimension: INCH.

# **T8.C** MIL-STD-1835 MACY1-X8 (A1) 8 LEAD METAL CAN PACKAGE

|        | INCHES          |       | MILLI               |       |       |

|--------|-----------------|-------|---------------------|-------|-------|

| SYMBOL | MIN             | MAX   | MIN MAX             |       | NOTES |

| А      | 0.165           | 0.185 | 4.19                | 4.70  | -     |

| Øb     | 0.016           | 0.019 | 0.41                | 0.48  | 1     |

| Øb1    | 0.016           | 0.021 | 0.41                | 0.53  | 1     |

| Øb2    | 0.016           | 0.024 | 0.41                | 0.61  | -     |

| ØD     | 0.335           | 0.375 | 8.51                | 9.40  | -     |

| ØD1    | 0.305           | 0.335 | 7.75                | 8.51  | -     |

| ØD2    | 0.110           | 0.160 | 2.79                | 4.06  | -     |

| е      | 0.200 BSC       |       | 5.08                | -     |       |

| e1     | 0.100           | BSC   | 2.54 BSC            |       | -     |

| F      | -               | 0.040 | -                   | 1.02  | -     |

| k      | 0.027           | 0.034 | 0.69                | 0.86  | -     |

| k1     | 0.027           | 0.045 | 0.69                | 1.14  | 2     |

| L      | 0.500           | 0.750 | 12.70               | 19.05 | 1     |

| L1     | -               | 0.050 | -                   | 1.27  | 1     |

| L2     | 0.250           | -     | 6.35                | -     | 1     |

| Q      | 0.010           | 0.045 | 0.25                | 1.14  | -     |

| α      | 45 <sup>0</sup> | BSC   | 45 <sup>0</sup> BSC |       | 3     |

| β      | 45 <sup>0</sup> | BSC   | 45 <sup>0</sup> BSC |       | 3     |

| Ν      | 8               | 3     |                     | 8     | 4     |

Rev. 0 5/18/94

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com