# **ADVANCE INFORMATION**

August 1996

# Features

- Fully Supports VPW Specifications of SAE J1850 Standard for Class B Data Communications Network Interface

- On-Chip Memory

- 176 Bytes of RAM

- 2110 Bytes of User ROM

- 13 Bidirectional I/O Lines

- 16-Bit Timer with Capture and Compare Registers

- Serial Peripheral Interface (SPI) System

- Watchdog Timer and Slow Clock Detect

- 10MHz Operating Frequency (5.0MHz Internal Bus Frequency) at 5V

- Built-In-Test Bootstrap Mode with 242 Bytes of ROM

- Two Channel Analog Comparator

- On-Chip Oscillator Amplifier

- 8-Bit CPU Architecture

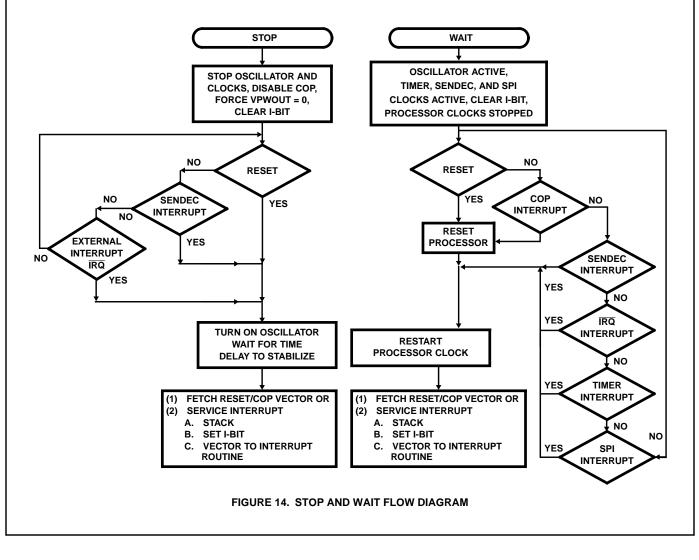

- Power-Saving STOP, WAIT and Data Retention Modes

- Full -40°C to 125°C Operating Range

- Single 3.0V to 6.0V Supply

- 28 Lead Dual-In-Line and Small Outline Plastic Packages

# Software Features

- Standard 68HC05 Instruction Set

- True Bit Manipulation

- Addressing Modes Include Indexed Addressing

Memory Mapped I/O

# Ordering Information

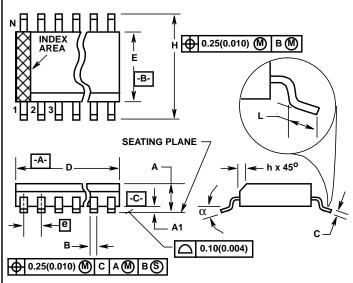

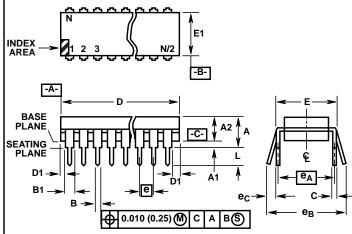

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE                     | PKG.<br>NO. |

|-------------|----------------------------------|-----------------------------|-------------|

| HIP7030A2P  | -40 to 125                       | 28 Lead Plastic<br>DIP      | M28.3       |

| HIP7030A2M  | -40 to 125                       | 28 Lead Plastic<br>SOIC (W) | E28.6       |

# J1850 8-Bit 68HC05 Microcontroller

# Description

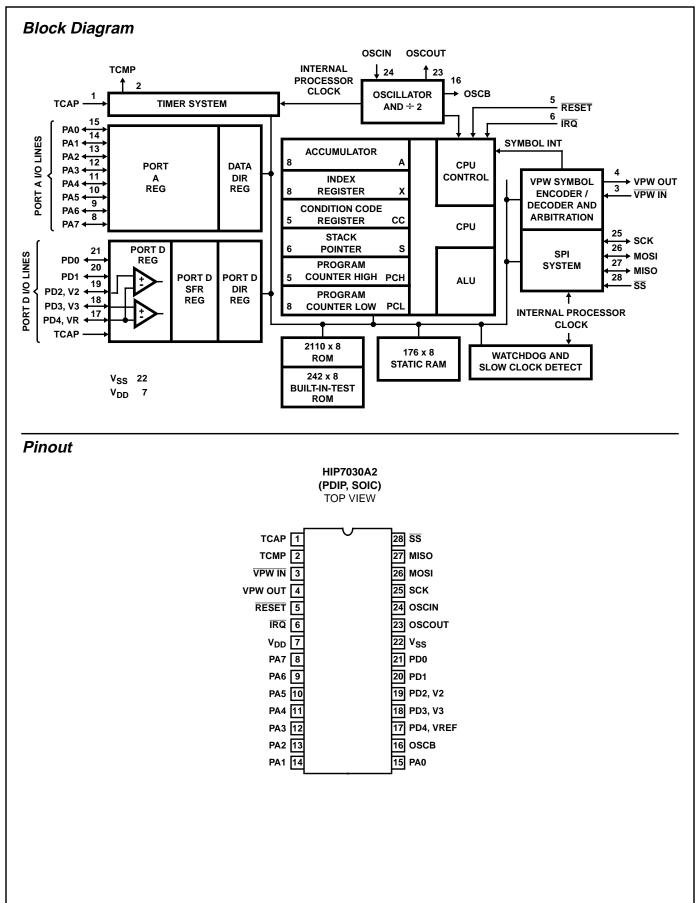

The HIP7030A2 HCMOS Microcomputer is a member of the CDP68HC05 family of low-cost single-chip microcomputers. The integrated hardware functions provide the system designer with a complete set of building blocks for implementing a "Class B" multiplexed communications network interface, which fully conforms to the VPW Multiplexed Wiring protocol specified in SAE Recommended Practice J1850. This 8-bit microcomputer unit (MCU) contains an on-chip oscillator, CPU, 176 bytes of RAM, 2110 bytes of user ROM, 13 I/O lines, a J1850 Variable Pulse Width Symbol Encoder/Decoder (VPW SENDEC) system, a Serial Peripheral Interface (SPI) system, a two channel analog Comparator, a Watchdog Timer, a Slow Clock Detect, and a 16-bit Timer. The static HCMOS design allows operation at input frequencies up to 10MHz (5MHz internal clock).

# Table of Contents

| Pinout2MCU Block Diagram.2Electrical & Timing Specifications.3Functional Pin Description9Integrated Hardware I/O11Memory.13Memory Map.15CPU Registers14Built-In Test15Resets16Interrupts16                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vector Addresses                                                                                                                                                                                                                      |

| Low Power Modes                                                                                                                                                                                                                       |

| Programmable Timer                                                                                                                                                                                                                    |

| Counter         25           Output Compare         25           Input Capture         25           Serial Peripheral Interface (SPI)         27           J1850 VPW Messaging         33           Symbol Encoder Decoder         33 |

| Control Register                                                                                                                                                                                                                      |

| Status Register         37           Data Register         39           COP System         40                                                                                                                                         |

| Effects of STOP and WAIT Modes                                                                                                                                                                                                        |

| Instruction Set       42         Package Outline Dimensions       55 - 56         Opcode Map       46         I/O, Control, Status and Data Register Definitions       52         Ordering       52                                   |

| Ordering<br>Information Sheet                                                                                                                                                                                                         |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

# **Absolute Maximum Ratings**

## **Thermal Information**

| Supply Voltage (V <sub>DD</sub> )0.3V to +7.0V                                 |

|--------------------------------------------------------------------------------|

| Input or Output Voltage                                                        |

| Pins with V <sub>DD</sub> Diode                                                |

| Pins without V <sub>DD</sub> Diode                                             |

| Current Drain Per Pin, I (Excluding V <sub>DD</sub> and V <sub>SS</sub> ) 25mA |

| Lead Temperature (Soldering 10s)+265°C                                         |

| ESD Classification Class 2                                                     |

| Gate Count                                                                     |

|                                                                                |

| Thermal Resistance (Typical) $\theta_{JA}$ Plastic DIP Package $60^{\circ}$ C/WPlastic SOIC Package $75^{\circ}$ C/WMaximum Package Power Dissipation at +125°C |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| DIP Package                                                                                                                                                     | 1 |

| SOIC Package                                                                                                                                                    | 1 |

| Operating Temperature Range (T <sub>A</sub> )40°C to +125°C                                                                                                     | ; |

| Storage Temperature Range (T <sub>STG</sub> )65 <sup>o</sup> C to +150 <sup>o</sup> C                                                                           | ; |

| Junction Temperature+150°C                                                                                                                                      | ; |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **Operating Conditions**

| Operating Voltage Range     |                                          |

|-----------------------------|------------------------------------------|

| Operating Temperature Range | -40 <sup>0</sup> C to 125 <sup>0</sup> C |

| Input Low Voltage           | 0V to +0.8V                              |

# **DC Electrical Specifications** $V_{DD} = 5V_{DC} \pm 10\%$ , $V_{SS} = 0V_{DC}$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ Unless Otherwise Specified

| PARAMETER                                                     | SYMBOL           | CONDITIONS                                      | MIN                  | ТҮР                  | МАХ                 | UNITS |

|---------------------------------------------------------------|------------------|-------------------------------------------------|----------------------|----------------------|---------------------|-------|

| No Load Output Voltage                                        | V <sub>OL</sub>  | $I_{LOAD} < \pm 10 \mu A$                       | -                    | -                    | 0.1                 | V     |

|                                                               | V <sub>OH</sub>  |                                                 | V <sub>DD</sub> -0.1 | -                    | -                   | V     |

| Output High Voltage: PA0-7, PD0-4, VPWOUT, TCMP               | V <sub>OH</sub>  | I <sub>LOAD</sub> = -0.8mA                      | V <sub>DD</sub> -0.8 | V <sub>DD</sub> -0.4 | -                   | V     |

| Output High Voltage: OSCOUT                                   | V <sub>ОН</sub>  | I <sub>LOAD</sub> = -0.08mA                     | V <sub>DD</sub> -0.8 | V <sub>DD</sub> -0.4 | -                   | V     |

| Output High Voltage: MISO, MOSI, SCK, OSCB                    | V <sub>ОН</sub>  | I <sub>LOAD</sub> = -1.6mA                      | V <sub>DD</sub> -0.8 | V <sub>DD</sub> -0.4 | -                   | V     |

| Output Low Voltage: OSCOUT                                    | V <sub>OL</sub>  | I <sub>LOAD</sub> = 0.17mA                      | -                    | 0.2                  | 0.4                 | V     |

| Output Low Voltage: MISO, MOSI, SCK, OSCB                     | V <sub>OL</sub>  | I <sub>LOAD</sub> = 1.6mA                       | -                    | 0.2                  | 0.4                 | V     |

| Input High Voltage: PA0-7, PD0-4, MISO, MOSI, SS, SCK         | V <sub>IH</sub>  |                                                 | 0.7•V <sub>DD</sub>  | -                    | V <sub>DD</sub>     | V     |

| Input High Voltage: RESET, IRQ, TCAP,<br>VPWIN, OSCIN         | V <sub>IH</sub>  |                                                 | 0.8•V <sub>DD</sub>  | -                    | V <sub>DD</sub>     | V     |

| Input Low Voltage: PA0-7, PD0-4, MISO, MOSI,<br>SS, SCK       | V <sub>IL</sub>  |                                                 | V <sub>SS</sub>      | -                    | 0.3•V <sub>DD</sub> | V     |

| Input Low Voltage: RESET, IRQ, TCAP, VPWIN, OSCIN             | VIL              |                                                 | V <sub>SS</sub>      | -                    | 0.2•V <sub>DD</sub> | V     |

| Input Hysteresis Voltage: RESET, IRQ, TCAP,<br>VPWIN, OSCIN   | V <sub>HYS</sub> |                                                 | 0.1•V <sub>DD</sub>  | 1.0                  | 0.5•V <sub>DD</sub> | V     |

| Supply Current                                                |                  |                                                 |                      |                      |                     |       |

| RUN                                                           | I <sub>RUN</sub> | f <sub>OSC</sub> = 10MHz Exter-                 | -                    | 8                    | 18                  | mA    |

| WAIT (Note 2)                                                 | IWAIT            | nal Square Wave                                 | -                    | 3.2                  | 10                  | mA    |

| STOP (Notes 2, 3)                                             | ISTOP            | T <sub>A</sub> = 25 <sup>o</sup> C              | -                    | 2                    | 50                  | μΑ    |

|                                                               |                  | $T_{A} = -40^{\circ}C \text{ to } 125^{\circ}C$ | -                    | 10                   | 250                 | μΑ    |

| I/O Ports Hi-Z Leakage Current: PA0-7, PD0-4, MISO, MOSI, SCK | Ι <sub>ΙL</sub>  |                                                 | -10                  | ±0.01                | +10                 | μΑ    |

| Input Current: RESET, IRQ, TCAP,<br>OSCIN, VPWIN, SS          | I <sub>IN</sub>  |                                                 | -1                   | .001                 | +1                  | μΑ    |

| <b>DC Electrical Specifications</b> | $V_{DD} = 5V_{DC} \pm 10\%$ , $V_{SS} = 0V_{DC}$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ Unless Otherwise Specified (Continued) |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                                        | SYMBOL            | CONDITIONS          | MIN                  | TYP | MAX                      |    |

|----------------------------------------------------------------------------------|-------------------|---------------------|----------------------|-----|--------------------------|----|

| Capacitance: (Note 4)                                                            | C <sub>OUT</sub>  |                     | -                    | -   | 12                       | pF |

|                                                                                  | C <sub>IN</sub>   |                     | -                    | -   | 8                        | pF |

| Powerdown Input Voltage: RESET, IRQ,<br>VPWIN, OSCIN                             | V <sub>INPD</sub> | V <sub>DD</sub> = 0 | -0.3                 | -   | 7                        | V  |

| Comparator:<br>Input Voltage: V <sub>2</sub> , V <sub>3</sub> , V <sub>REF</sub> | V <sub>IN</sub>   |                     | V <sub>SS</sub> -0.2 | -   | V <sub>DD</sub><br>+0.02 | v  |

| Input Current: V <sub>2</sub> , V <sub>3</sub> , V <sub>REF</sub>                | I <sub>IN</sub>   |                     | -1                   | -   | +1                       | μΑ |

| Offset Voltage                                                                   | VOFF              |                     | -                    | 20  | -                        | mV |

| Response                                                                         | t <sub>R</sub>    |                     | -                    | 2   | -                        | μs |

NOTES:

This device contains circuitry to protect the inputs against damage due to high static voltages of electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>IN</sub> and V<sub>OUT</sub> be constrained to the range V<sub>SS</sub><(V<sub>IN</sub> or V<sub>OUT</sub>)<V<sub>DD</sub>. Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>).

2. WAIT, STOP I\_DD: All ports configured as inputs, V\_IL = 0.2V and V\_IH = V\_DD - 0.2V.

3. STOP  $I_{DD}$  measured with OSCIN =  $V_{SS}$ , no feedback resistor connected.

4. Includes Ports used as Input/Output Pins, Ports used as Input only Pins; Ports used as Output only Pins.

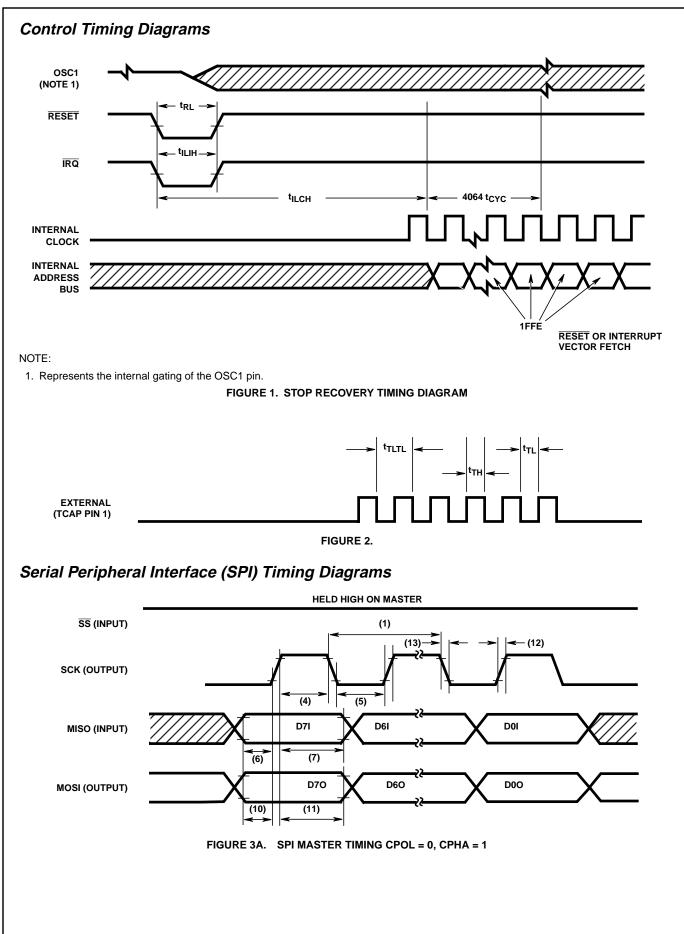

# **Control Timing** $V_{DD} = 5V_{DC} \pm 10\%$ , $V_{SS} = 0V_{DC}$ , $T_A = -40^{\circ}C$ to $125^{\circ}C$ Unless Otherwise Specified

| PARAMETER                                               | SYMBOL                            | CONDITIONS | MIN      | TYP | MAX | UNITS |

|---------------------------------------------------------|-----------------------------------|------------|----------|-----|-----|-------|

| Frequency Of Operation                                  |                                   |            |          |     |     |       |

| Crystal Option                                          | fosc                              |            | 1        | -   | 10  | MHz   |

| External Clock Option                                   | fosc                              |            | 1        | -   | 10  | MHz   |

| Internal Operating Frequency                            |                                   |            |          |     |     |       |

| Crystal (f <sub>OSC</sub> +2)                           | fop                               |            | 0.5      | -   | 5   | MHz   |

| External Clock (f <sub>OSC</sub> +2)                    | f <sub>OP</sub>                   |            | 0.5      | -   | 5   | MHz   |

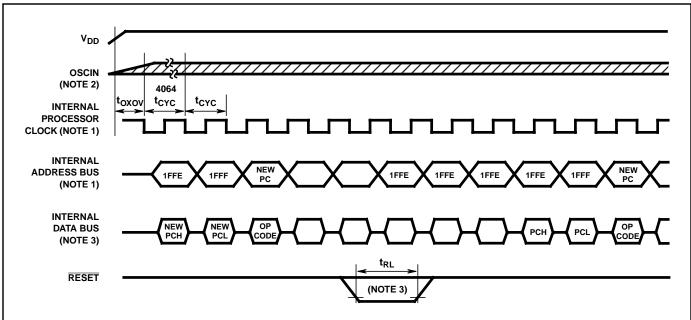

| Cycle Time                                              | tCYC                              |            | 200      | -   | -   | ns    |

| Crystal Oscillator Start-up Time for AT-cut Crystal     | toxov                             |            | -        | -   | 100 | ms    |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) | <sup>t</sup> ILCH                 |            | -        | -   | 100 | ms    |

| RESET Pulse Width                                       | t <sub>RL</sub>                   |            | 1.5      | -   | -   | tCYC  |

| Timer                                                   |                                   |            |          |     |     |       |

| Resolution (Note 1)                                     | t <sub>RES</sub>                  |            | 4        | -   | -   | tCYC  |

| Input Capture Pulse Width                               | t <sub>TH</sub> , t <sub>TL</sub> |            | 50       | -   | -   | ns    |

| Input Capture Pulse Period                              | t <sub>TL</sub> , t <sub>TL</sub> |            | (Note 2) | -   | -   | tCYC  |

| Interrupt Pulse Width Low (Edge-Triggered)              | t <sub>ILIH</sub>                 |            | 50       | -   | -   | ns    |

| OSC1 Pulse Width                                        | t <sub>OH</sub> , t <sub>OL</sub> |            | 35       | -   | -   | ns    |

| Slow Clock Detect Frequency Range                       | fslow                             |            | 20       | 50  | 200 | KHz   |

NOTES:

1. Since a 2-bit prescaler in the timer must count four internal cycles (t<sub>CYC</sub>), this is the limiting minimum factor in determining the timer resolution.

2. The minimum period  $t_{TLTL}$  should not be less than the number of cycle times it takes to execute the capture interrupt service routine plus 24  $t_{CYC}$ .

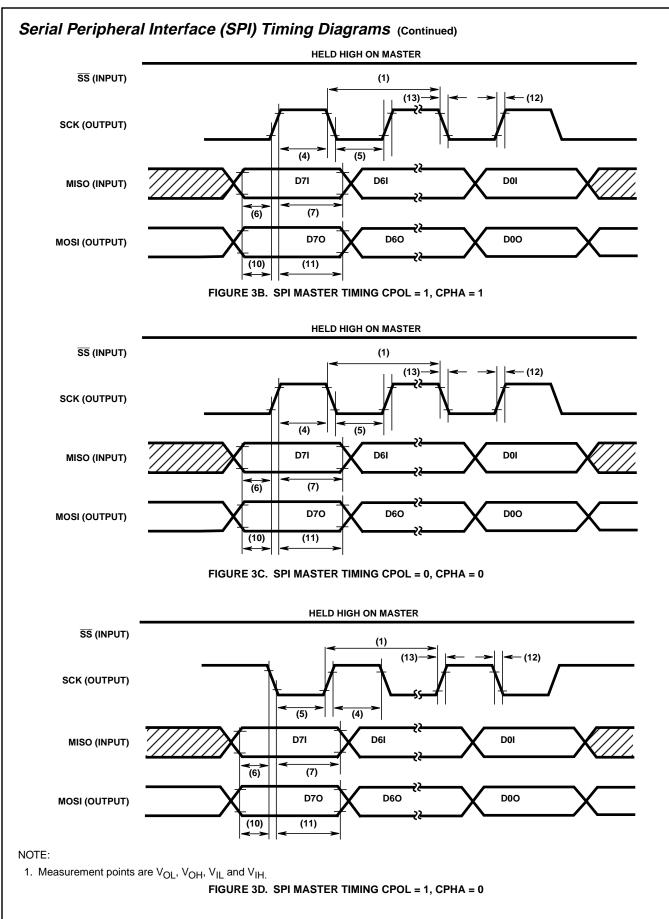

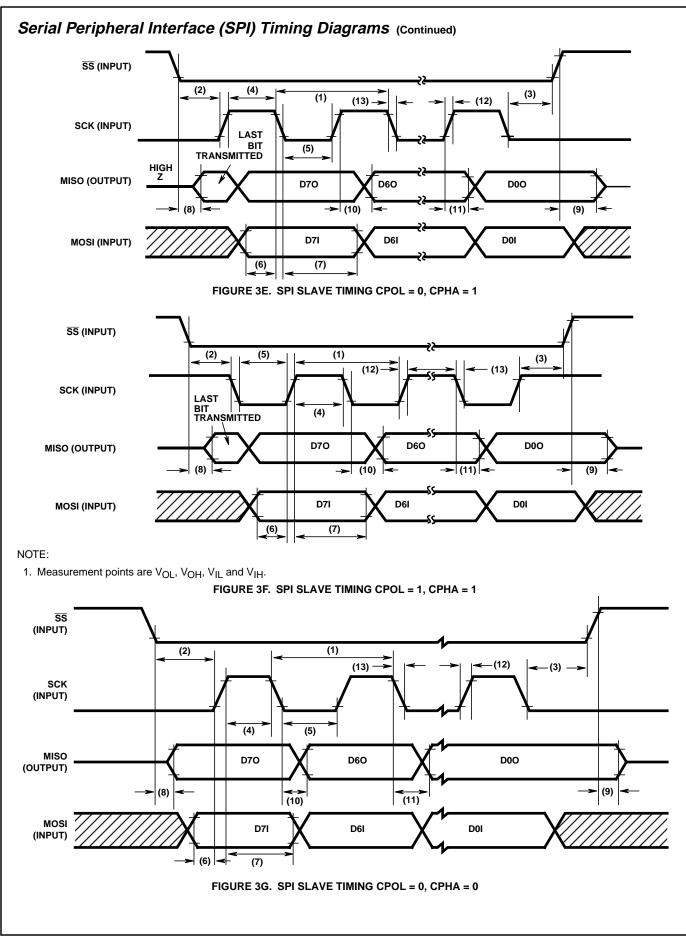

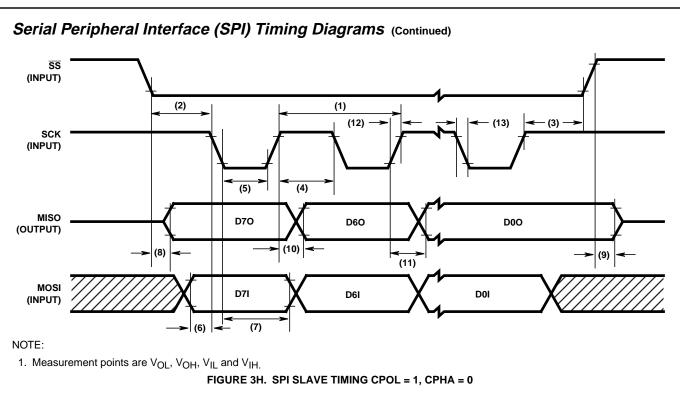

| NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                  | PARAMETER                                                                                                                                                                                                                                                                                                                                                             | SYMBOL               | MIN            | MAX                                                                       | UNITS                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------------------------------------------------------------------------|-----------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operating Frequency<br>Master                                                                                                                                                                                                                                                                                                                                         | fop(M)               | 0.03           | 0.5                                                                       | f <sub>OP</sub><br>(Note 3) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave                                                                                                                                                                                                                                                                                                                                                                 | fOP(S)               | DC             | 5                                                                         | MHz                         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                       | Cycle Time<br>Master                                                                                                                                                                                                                                                                                                                                                  | t <sub>CYC(M)</sub>  | 2              | -                                                                         | tCYC                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave                                                                                                                                                                                                                                                                                                                                                                 | tCYC(S)              | 200            | 0.5<br>5<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ns                          |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                       | Enable Lead Time<br>Master                                                                                                                                                                                                                                                                                                                                            | t <sub>LEAD(M)</sub> | (Note 1)       | -                                                                         | -                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave                                                                                                                                                                                                                                                                                                                                                                 | t <sub>LEAD(S)</sub> | 50             | -                                                                         | ns                          |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                       | Enable Lag Time<br>Master<br>Slave                                                                                                                                                                                                                                                                                                                                    | tLAG(M)              | (Note 1)<br>50 |                                                                           | -<br>ns                     |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clock (SCK) High Time<br>Master                                                                                                                                                                                                                                                                                                                                       | tw(sckh)M            | 200            | _                                                                         | ns                          |

| 3     Enable Lag Time     ILLA       Master     tLAG       Slave     tLAG       4     Clock (SCK) High Time       Master     tW(SC       Slave     tW(SC       Slave     tW(SC       5     Clock (SCK) Low Time       Master     tW(SC       5     Clock (SCK) Low Time       Master     tW(SC       Slave     tW(SC       6     Data Setup Time (Inputs)       Master     tSU       7     Data Hold Time (Inputs)       Master     tSU | tw(SCKH)S                                                                                                                                                                                                                                                                                                                                                             | 50                   | -              | ns                                                                        |                             |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                       | Master                                                                                                                                                                                                                                                                                                                                                                | tw(SCKL)M            | 200<br>50      |                                                                           | ns                          |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                       | W(SCRL)S             |                |                                                                           |                             |

| Ũ                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                       | t <sub>SU(M)</sub>   | 50             | -                                                                         | ns                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave                                                                                                                                                                                                                                                                                                                                                                 | t <sub>SU(S)</sub>   | 50             | -                                                                         | ns                          |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                       | t <sub>H(M)</sub>    | 50             | -                                                                         | ns                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave                                                                                                                                                                                                                                                                                                                                                                 | t <sub>H(S)</sub>    | 50             | -                                                                         | ns                          |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clock (SCK) Low Time Master Slave Data Setup Time (Inputs) Master Slave Data Hold Time (Inputs) Master Slave Access Time (Time to Data Active from High Impedance State) Slave Disable Time (Hold Time to High Impedance State) Slave                                                                                                                                 |                      | 0              | 120                                                                       | ns                          |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                       | Master         Slave         Data Setup Time (Inputs)         Master         Slave         Data Hold Time (Inputs)         Master         Slave         Access Time (Time to Data Active from High Impedance State)         Slave         Disable Time (Hold Time to High Impedance State)         Slave         Data Valid Time         Master (Before Capture Edge) |                      | -              | 200                                                                       | ns                          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                      | Master (Before Capture Edge)                                                                                                                                                                                                                                                                                                                                          | t <sub>V(M)</sub>    | 0.25           | -                                                                         | <sup>t</sup> CYC(M          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave (After Enable Edge) (Note 2)                                                                                                                                                                                                                                                                                                                                    | t <sub>V(S)</sub>    | -              | 150                                                                       | ns                          |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data Hold Time (Outputs)<br>Master (After Capture Edge)                                                                                                                                                                                                                                                                                                               | t <sub>HO(M)</sub>   | 0.25           | -                                                                         | <sup>t</sup> CYC(M          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | Slave (After Enable Edge)                                                                                                                                                                                                                                                                                                                                             | <sup>t</sup> HO(S)   | 0              | -                                                                         | ns                          |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                      | Rise Time (V <sub>DD</sub> = 20% to 70%, C <sub>L</sub> = 100pF)<br>SPI Outputs (SCK, MOSI, MISO)                                                                                                                                                                                                                                                                     | t <sub>R(M)</sub>    | -              | 50                                                                        | ns                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPI Inputs (SCK, MOSI, MISO, <del>SS</del> )                                                                                                                                                                                                                                                                                                                          | t <sub>R(S)</sub>    | -              | 2                                                                         | μs                          |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                      | Fall Time (V <sub>DD</sub> = 20% to 70%, C <sub>L</sub> = 100pF)<br>SPI Outputs (SCK, MOSI, MISO)                                                                                                                                                                                                                                                                     | t <sub>F(M)</sub>    | -              | 50                                                                        | ns                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPI Inputs (SCK, MOSI,MISO, SS)                                                                                                                                                                                                                                                                                                                                       | t <sub>F(S)</sub>    |                | 2                                                                         | μs                          |

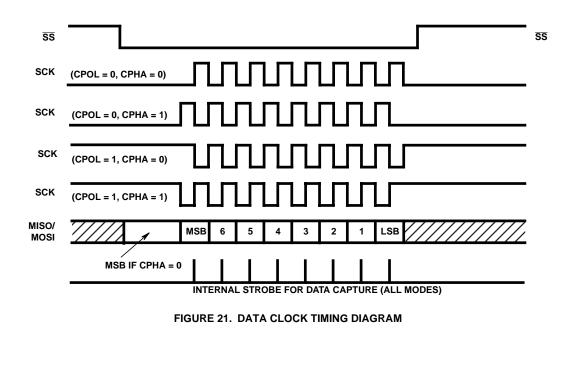

Serial Perinheral Interface (SPI) Timing (See Figure 3) Vic 5\/\_

#### NOTES:

1. Signal Production depends on software.

2. Assumes 200pF load on all SPI pins.

Note that the units this specification uses is f<sub>OP</sub> (internal operating frequency), not MHz! In the master mode the SPI bus is capable of running at one-half of the devices's internal operating frequency, therefore, 2.5MHz maximum.

# Functional Pin Description

This section provides a description of each of the 28 pins of the HIP7030A2 MCU.

# V<sub>DD</sub> and V<sub>SS</sub> (Power)

Power is supplied to the MCU using these two pins.  $V_{DD}$  is connected to the positive supply and  $V_{SS}$  is connected to the negative supply.

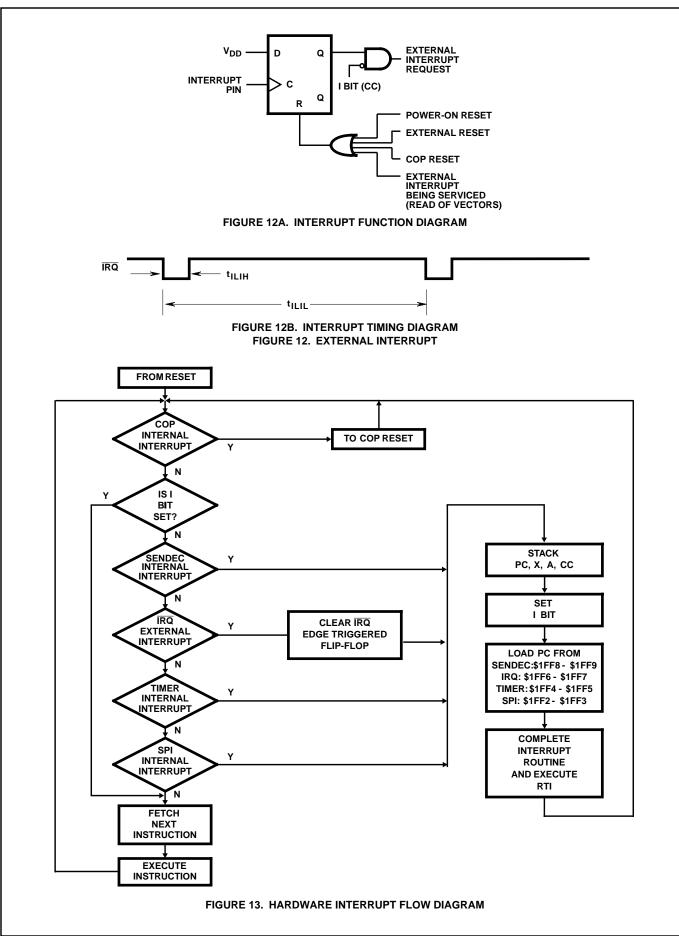

# **IRQ** (Maskable Interrupt Request - Input)

The  $\overline{IRQ}$  pin is negative edge-sensitive triggering. A high to low transition on the  $\overline{IRQ}$  pin will produce an interrupt.

In the event of an interrupt request, the MCU always completes the current instruction before it responds to the request. An internal mask can be used to inhibit the MCU from responding to IRQ interrupts.

An IRQ interrupt is generated if the  $\overline{IRQ}$  pin is pulled low for at least one t<sub>ILIH</sub>. The occurrence of the low going pulse is registered in a flip-flop and the IRQ interrupt will be recognized even if the  $\overline{IRQ}$  pin has returned to a high state before the interrupt can be serviced.

Once the edge-sensitive flip-flop is cleared, (it is automatically cleared at the start of the interrupt service routine) the interrupt request is removed until the  $\overline{IRQ}$  pin returns to a high level and once again goes low.

See *INTERRUPTS* for more details concerning IRQ interrupts.

# **RESET** (Master Reset - Input)

The HIP7030A2 contains an integrated Power-On Reset (POR) circuit and the RESET input is therefore not required for start-up. It can be used to reset the MCU internal state and provides for an orderly re-start of the software after initial power-up. Refer to *Resets* for a detailed description of POR and RESET.

# TCAP (Timer Capture - Input)

The TCAP input controls the input capture feature for the onchip programmable timer system. The TCAP input is also used as the strobe signal to the Port D strobed outputs. Refer to *Input Capture Register* and *PD0, PD1 Strobed Output Mode* for additional information.

# **TCMP (Timer Compare - Output)**

The TCMP pin provides an output for the output compare feature of the on-chip timer system. Refer to *Output Compare Register* for additional information.

## OSCIN (Oscillator Input - Input), OSCOUT (Oscillator Output - Output), OSCB (Oscillator Buffered Output - Output)

OSCIN is the input and OSCOUT is the output of an inverter/amplifier which can be used to build either a quartz crystal or ceramic resonator based clock oscillator. Alternatively, the OSCIN input can be driven from any external clock source which satisfies the CMOS Schmitt trigger input level requirements of the OSCIN pin. See *Electrical Specifications* for input level specification.

OSCB is a squared, buffered version of the OSCIN signal, available for driving one external CMOS load.

The fundamental internal clock is derived by a divide-by-two of the external oscillator frequency ( $f_{OSC}$ ). All other internal clocks are also derived from the external frequency. These clocks include the input to the 16-bit Timer, the Serial Clock (SCK), and the VPW Symbol Encoder/Decoder (SENDEC).

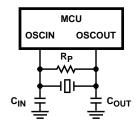

# **Quartz Crystal**

The circuit shown in Figure 4A is recommended when using a quartz crystal. The internal oscillator is designed to interface with an AT-cut parallel resonant quartz crystal in the frequency range specified for  $f_{OSC}$  in *Electrical Specifications*. Figure 4B lists the recommended capacitance and feedback resistance values. Use of an external CMOS oscillator is recommended when crystals outside the specified ranges are to be used. The crystal and components should be mounted as close as possible to the OSCIN and OSCOUT pins to minimize output distortion and start-up stabilization time.

# **Ceramic Resonator**

A ceramic resonator may be used in place of the crystal in cost sensitive applications. The circuit in Figure 4A is recommended when using a ceramic resonator. Figure 4C lists the recommended capacitance and feedback resistance values. The manufacturer of the particular ceramic resonator being considered should be consulted for specific information.

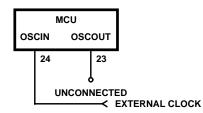

# External Clock

If an external clock is used, it should be applied to the OSCIN input with the OSCOUT output not connected, as shown in Figure 4E. The  $t_{OXOV}$  or  $t_{ILCH}$  specifications do not apply when using an external clock input. The equivalent specification of the external clock source should be used in lieu of  $t_{OXOV}$  or  $t_{ILCH}$ .

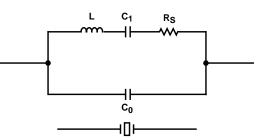

|                      | 2MHz  | 4MHz  | 8MHz  | 10MHz | UNITS |

|----------------------|-------|-------|-------|-------|-------|

| R <sub>S</sub> (Max) | 400   | 75    | 50    | 30    | Ω     |

| C <sub>0</sub>       | 5     | 7     | 5     | 5     | pF    |

| C <sub>1</sub>       | 0.008 | 0.012 | 0.015 | 0.018 | μF    |

| C <sub>IN</sub>      | 15-40 | 15-30 | 12-30 | 12-30 | pF    |

| C <sub>OUT</sub>     | 15-30 | 15-25 | 12-25 | 12-25 | pF    |

| R <sub>P</sub>       | 1-10  | 1-10  | 1-10  | 1-10  | MΩ    |

| Q                    | 30    | 30    | 30    | 30    | К     |

FIGURE 4B. QUARTZ CRYSTAL PARAMETERS

|                          | 10MHz | UNITS |

|--------------------------|-------|-------|

| R <sub>S</sub> (Typical) | 5.5   | Ω     |

| C <sub>0</sub>           | 35    | pF    |

| C <sub>1</sub>           | 5     | pF    |

| C <sub>IN</sub>          | 22    | pF    |

| C <sub>OUT</sub>         | 22    | pF    |

| R <sub>P</sub>           | 1-5   | MΩ    |

| Q                        | 500   | -     |

NOTES:

- When no power is applied to the HIP7030A2, the OSCIN, IRQ, RESET, and VPWIN pins can have up to 9V<sub>DC</sub> applied with no side effects.

- 2. When power is applied to the HIP7030A2, it is recommended that all unused inputs, except Port A and Port D I/O lines configured as outputs, be tied to an appropriate logic level (i.e., either  $V_{DD}$  or  $V_{SS}$ ).

#### FIGURE 4C. CERAMIC RESONATOR PARAMETERS

FIGURE 4E. EXTERNAL CLOCK SOURCE CONNECTIONS

# PA0-PA7 (Port A - Input/Output)

These eight I/O lines comprise Port A. The mode (i.e., input or output) of each pin is software programmable. All Port A I/Os are configured as inputs during a POR, COP, or external reset. Refer to *Port A* under *Port A* and *D* I/O Lines for a detailed description of programming the Port A I/O lines.

# PD0-PD4 (Port D - Input/Output)

These five I/O lines comprise Port D. As with PA0-PA7, the mode (i.e., input or output) of each pin is software programmable. In addition, a Special Function Register (SFRD) allows configuring PD0 and PD1 as "strobed" outputs, and/or PD2, PD3, and PD4 as inputs to an on-chip analog comparator.

All Port D I/Os are configured as inputs during a POR, COP, or external reset. Refer to *PD0-PD4 Special Function I/O Lines* under *Port A and D I/O Lines* for a detailed description of programming the Port D I/O lines.

#### VPWOUT (Variable Pulse Width Out - Output), VPWIN (Variable Pulse Width In - Input)

These two lines are used to interface to the J1850 bus transceiver.

VPWOUT is the pulse width modulated output of the SEN-DEC encoder block.

VPWIN is the inverted input to the SENDEC decoder block.

See *VPW Symbol Encoder/Decoder (SENDEC)* for a detailed description of the J1850 interface pins.

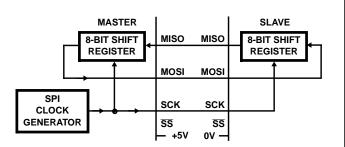

#### MISO (Master-in/Slave-out - Input/Output), MOSI (Master-out/Slave-in - Input/Output), SCK (Serial Clock - Input/Output), SS (Slave Select - Input)

These four lines constitute the Serial Peripheral Interface (SPI) communications port. The MCU can be configured as a SPI "master" or as a SPI "slave". In master mode MOSI and SCK function as outputs and MISO functions as an input. In slave mode MOSI and SCK are inputs and MISO is an output.  $\overline{\rm SS}$  is always an input.

Serial data words are transmitted and received over the MISO/MOSI lines synchronously with the SCK clock stream. The word size is fixed at 8-bits. Single buffering is used which results in an inherent inter-byte delay. The master device always provides the synchronizing clock.

A low on the  $\overline{SS}$  line causes the MCU to immediately assume the role of slave, regardless of it's current mode. This allows multi-master systems to be constructed with appropriate arbitration protocols.

See the detailed discussion of the SPI interface under *Serial Peripheral Interface (SPI)*.

# Integrated Hardware I/O Functions

# PORT A

Each of the Parallel Port pins of Port A may be individually programmed as an input or an output under software control. The direction of each pin is determined by the state of the corresponding bit in the Port A Data Direction Register (DDRA, location \$04).

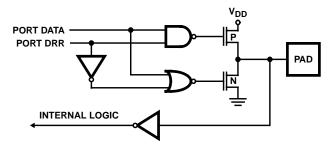

FIGURE 5A. PORT A I/O PAD CIRCUITRY

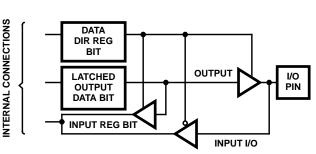

FIGURE 5B. PORT A FUNCTIONAL BLOCK DIAGRAM

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DA7 | DA6 | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |

PORT A DATA DIRECTION REGISTER (DDRA, LOCATION \$04)

Any Port A pin is configured as an output if its corresponding DDR bit is set to a logic one. A pin is configured as an input if its corresponding DDR bit is cleared to a logic zero. Any reset will clear all DDR bits, which configures all Port A and D pins as inputs. The data direction register is capable of being written to or read by the processor. Refer to Figure 5 and Table 1.

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

PORT A DATA REGISTER (PORTA, LOCATION \$00)

Port A is an 8-bit wide read-write data register. Regardless of the state of the DDRA bits, all Port A data latches are modified with each write to Port A. When Port A is read, the value read for bits programmed as outputs, is the contents of the data latch, not the pin. The value read for bits programmed as inputs is the value on the pin.

TABLE 1. PORT A TRUTH TABLE

| (NOTE 1)<br><b>R/W</b> | DDR | I/O PIN FUNCTION                                                                     |

|------------------------|-----|--------------------------------------------------------------------------------------|

| W                      | 0   | The I/O pin is in input mode.<br>Data is written into the output data latch          |

| W                      | 1   | Data is written into the output data latch and simultaneously output to the I/O pin. |

| R                      | 0   | The state of the I/O pin is read.                                                    |

| R                      | 1   | The I/O pin is in output mode.<br>The output data latch is read.                     |

NOTE:

1. R/W is an internal signal which equals R when reading the Port Data Register and equals W when writing the Port Data Register.

#### PD0-PD4 SPECIAL FUNCTION I/O LINES

These five lines comprise Port D. The five lines can be individually programmed to provide input or output capabilities similar to the eight Port A lines. Additionally, each of the lines can be programmed to provide special capabilities, beyond the standard digital input and output functions. The PD0-PD4 I/O lines are controlled via three read/write registers.

| [ | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|-----|

|   | 0 | 0 | 0 | DD4 | DD3 | DD2 | DD1 | DD0 |

#### PORT D DATA DIRECTION REGISTER (DDRD, LOCATION \$07)

DDRD contains five data direction bits, DD0-DD4, which control whether the associated I/O line behaves as an Input or as an Output. Setting a data direction bit causes the related I/O line to be configured as an output, while clearing the bit causes the line to be configured as an input. When configured as an output, the I/O line is actively driven by the HIP7030A2. When configured as an input, the I/O line appears as a high impedance input and should be driven by external circuitry.

DDRD bits D0-D4 are cleared by RESET.

| 7    | 6    | 5 | 4  | 3  | 2  | 1  | 0  |

|------|------|---|----|----|----|----|----|

| CMP3 | CMP2 | 0 | D4 | D3 | D2 | D1 | D0 |

#### PORT D DATA REGISTER (PORTD, LOCATION \$03)

PortD is an 8-bit wide register with 5 read/write data bits and 2 read-only bits. When writing to PortD, bits 5-7 are ignored. All other bits (D0-D4) are stored in latches until they are explicitly modified with a subsequent write (or read-modify-write) instruction. The utilization of bits D0-D4 is dependent on the value in the associated DDRD bit. If a line is programmed as an input, the value read in PortD (D0-D4) is the logic level present on the external I/O line. If a line is programmed as an output, the value read in PortD (D0-D4) is the value last written to the same bit in PortD and that value is forced onto the corresponding I/O line. The PortD CMP2 and CMP3 read-only input bits indicate the results of the last analog comparisons (see *PD2, PD3, PD4 Analog Comparator Inputs* for details on CMP2 and CMP3). PortD bit 5 is always read as a 0.

PortD is not affected by RESET.

| 7 | 6 | 5    | 4 | 3 | 2 | 1    | 0    |

|---|---|------|---|---|---|------|------|

| 0 | 0 | CMPE | 0 | 0 | 0 | STE1 | STE0 |

#### PORT D SPECIAL FUNCTION REGISTER (SFRD, LOCATION \$08)

SFRD is an 8-bit wide register with 3 read/write control bits. The Strobe Enable 0 and 1-bits (STE0 and STE1) and used to configure PD0 and PD1 as strobed outputs. STE0 and STE1 only affect PD0 and PD1 when they are programmed as outputs by setting the corresponding bits in DDRD. See *PD0, PD1 Strobed Outputs* for a detailed explanation. The Comparator Enable bit (CMPE) controls the HIP7030A2's auto-zeroing, analog comparator (see *PD2, PD3, PD4 Analog Comparator Inputs* for details on CMPE). SFRD bits 2, 3, 4, 6 and 7 are always read as a 0.

SFRD bit CMPE, is cleared by RESET. All other SFRD bits are unaffected by RESET.

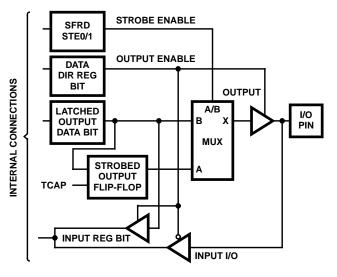

#### PD0, PD1 Strobed Output Mode

(DD0/DD1) is set, setting the STE0/1-bit configures the PD0/1 output in strobed mode. Clearing the STE0/1-bit causes the PD0/1 output to function identically to a PortA line in output mode. If the DDRD direction bit is clear, the associated line functions as an input and the state of the STE bit has no effect. When programmed as strobed outputs, data written to Port D Data Register bits 0 and 1 will appear on the external PD0 and PD1 pins synchronously with a low to high transition on the TCAP pin. This same transition on TCAP can be programmed to generate an interrupt to the processor. See Programmable Timer for details on using the interrupt capabilities of the TCAP pin. The strobed output mode of PD0 and PD1, coupled with the interrupt capability of TCAP, provides a mechanism for synchronously passing two bits of data between the HIP7030A2 and an external, asynchronous device.

#### FIGURE 6. STROBED OUTPUT BLOCK DIAGRAM (PD0, PD)

STE0 and STE1 are not affected by RESET.

TABLE 2. PORT D STROBED OUTPUTS TRUTH TABLE

| (NOTE 1)<br><b>R/W</b> | DDR | STE | I/O PIN FUNCTION                                                                                                         |

|------------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------|

| W                      | 0   | Х   | The I/O pin is in input mode.<br>Data is written into the output data latch.                                             |

| W                      | 1   | 0   | Data is written into the output data latch and simultaneously output to the I/O pin.                                     |

| W                      | 1   | 1   | Data is written into the output data latch<br>and transferred to the I/O pin on the<br>next TCAP low to high transition. |

| R                      | 0   | Х   | The state of the I/O pin is read.                                                                                        |

| R                      | 1   | 0   | The I/O pin is in standard output mode.<br>The output data latch is read.                                                |

| R                      | 1   | 1   | The I/O pin is in strobed output mode.<br>The output data latch is read.                                                 |

NOTE:

1. R/W is an internal signal which equals R when reading the Port Data Register and equals W when writing the Port Data Register.

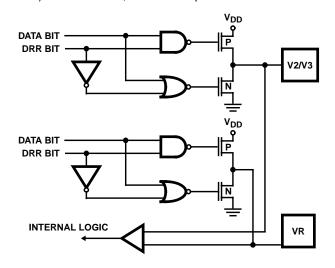

#### PD2, PD3, PD4 Analog Comparator Input Mode

When the CMPE bit is low in SFRD PD2, PD3, and PD4 behave as standard bidirectional I/O pins. Each of these three pins can be programmed as an input pin by setting the associated DDR bit low. Setting the DDR bit high configures the pin as an output. When CMPE is set high the three pins are connected to the appropriate comparator inputs and the contents of the DDRD doesn't affect comparator operation. While it is possible to perform comparisons of the pins when they are in the output mode (DDR bits are set high) the comparator result of comparing two equal digital values is not predictable. The comparator is intended for comparing analog input values, in which case the DDR bits must be set low to configure the pins as inputs. When CMPE is high, all of the associated PortD digital inputs (bits D4, D3, and D2 of PortD) are forced to 0, to conserve power.

FIGURE 7. ANALOG INPUT I/O PINS

The circuitry of the clocked comparator consists of a differential amplifier with requisite current sources, auto-zero storage elements, and multiplexing switches. It is convenient to view it as a conventional differential comparator to which PD4 is connected as a "reference" at the negative input and PD2 and PD3 are connected via a multiplexer at the positive input. The comparator is enabled be setting the CMPE bit (bit 5) of SFRD and disabled by clearing CMPE. To conserve power the comparator should be disabled when not in use. RESET clears the CMPE bit. The three analog inputs function properly with inputs from -0.3V to V<sub>DD</sub> +0.3V.

In order to use the comparator, PD4 and either (or both) PD2 or(and) PD3 should be selected as inputs via the DD2, DD3, and DD4 bits in DDRD. The results of the last comparison are available each time the PortD register is read. The CMP2 bit of PortD is set if PD2 was greater than PD4 during the last comparison and cleared otherwise. Similarly, the CMP3 bit of PortD is set if PD3 was greater than PD4 during the last comparison and cleared otherwise. CMP2 and CMP3 are not affected by RESET.

The HIP7030A2 includes a hardware sequencer to control the auto-zero function and input multiplexer of the comparator. Each complete compare cycle consists of a series of:

- 1. Auto Zero

- 2. Compare V2, write results to CMP2

- 3. Auto Zero

- 4. Compare V3, write results to CMP3

The hardware sequencer is enabled via the CMPE bit. Once enabled the compare cycling is performed continuously at a 1MHz step rate until CMPE is set low. A complete cycle takes  $4\mu$ s. It follows that, at any given time, the results read in CMP2 or CMP3 of the PortD Data Register can be, at most,  $4\mu$ s old.

The auto-zero operation involves charging a pair of bias capacitors. The charging time depends on the source impedance of the analog inputs, the relative voltages of V2 and V3, and the slew rate of all three input voltages. Incomplete charging of the capacitors will affect the accuracy of the comparator. The comparator is intended to perform favorably with input impedances up to  $10k\Omega$  and moderate slew rates.

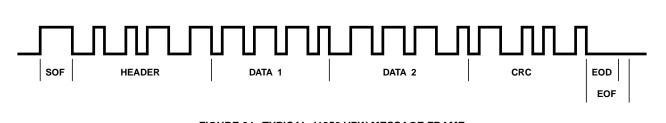

#### J1850 Bus Interface

The VPW Symbol Encoder/Decoder (SENDEC) block provides the design with all the features needed to send and receive properly timed messages on a J1850 Class B Multiplexed Bus. Refer to VPW Symbol Encoder/Decoder (SEN-DEC) for detailed documentation on the use of the SENDEC.

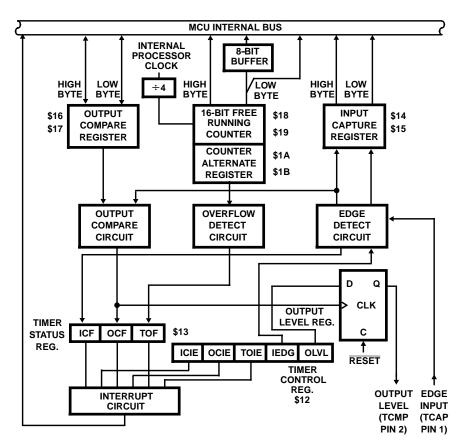

#### 16-Bit Timer

The integrated 16-bit Timer includes both capture and compare features. External events can be timed, pulses generated, and periodic interrupts programmed. A sophisticated set of control and status registers allows interrupt or polled operation. For a detailed guide to the operation of the Timer refer to *Programmable Timer*.

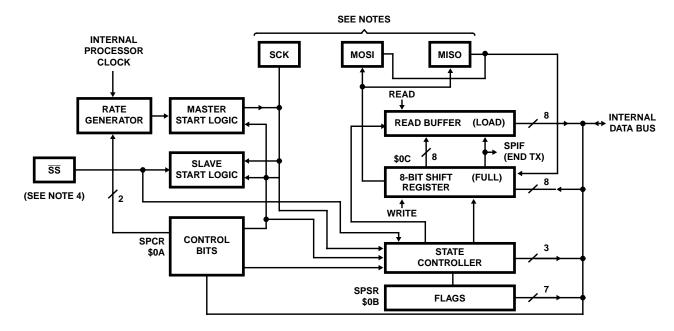

#### Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) is a synchronous serial interface with separate input, output, and clock lines. The SPI uses the MISO (serial data input/output), MOSI (serial data output/input), SCK (serial clock), and SS (slave select) pins. Refer to *Serial Peripheral Interface* for a detailed discussion of the SPI system.

# **Memory Organization**

The HIP7030A2 MCU is capable of addressing 8192 bytes of memory and I/O registers with its program counter. The MCU has implemented 2520 bytes of these locations as shown in Figure 8. The first 256 bytes of memory (page zero) include: 24 bytes of I/O features such as data ports, the port DDRs, Timer, serial peripheral interface (SPI), and J1850 VPW Registers; 48 bytes of user ROM, and 176 bytes of RAM. The next 2048 bytes complete the user ROM. The Built-In-Test ROM (228 bytes) and Built-In-Test vectors (14 bytes) are contained in memory locations \$1F00 through \$1FF1. The 14 highest address bytes contain the user defined reset and the interrupt vectors. Eight bytes of the lowest 32 memory locations are unused and the 176 bytes of user RAM include up to 64 bytes for the stack. Since most programs use only a small part of the allocated stack locations for interrupts and/or subroutine stacking purposes, the unused bytes are usable for program data storage.

# **CPU Registers**

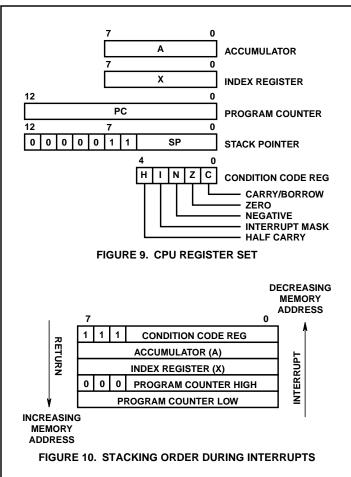

The CPU contains five registers, as shown in the programming model of Figure 9. The interrupt stacking order is shown in Figure 10.

# Accumulator (A)

The accumulator is an 8-bit general purpose register used to hold operands, results of the arithmetic calculations, and data manipulations.

## Index Register (X)

The X register is an 8-bit register which is used during the indexed modes of addressing. It provides an 8-bit value which is used to create an effective address. The index register is also used for data manipulations with the read-modify-write type of instructions and as a temporary storage register when not performing addressing operations.

# **Program Counter (PC)**

The program counter is a 13-bit register that contains the address of the next instruction to be executed by the processor.

# Stack Pointer (SP)

The stack pointer is a 13-bit register containing the address of the next free locations on the pushdown/popup stack. When accessing memory, the most significant bits are permanently configured to 0000011. These bits are appended to the six least significant register bits to produce an address within the range of \$00FF to \$00C0. The stack area of RAM is used to store the return address on subroutine calls and the machine state during interrupts. During external or power-on reset, and during a reset stack pointer (RSP) instruction, the stack pointer is set to its upper limit (\$00FF). Nested interrupt and/or subroutines may use up to 64 (decimal) locations. When the 64 locations are exceeded, the stack pointer wraps around and points to its upper limit (\$00FF), thus, losing the previously stored information. A subroutine call occupies two RAM bytes on the stack, while an interrupt uses five RAM bytes.

Since the Stack Pointer decrements during pushes, the PCL is stacked first, followed by PCH, etc. Pulling from the stack is in the reverse order.

# **Condition Code Register (CC)**

The condition code register is a 5-bit register which indicates the results of the instruction just executed as well as the state of the processor. These bits can be individually tested by a program and specified action taken as a result of their state. Each bit is explained in the following paragraphs.

# Half Carry Bit (H)

The H bit is set to a one when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. The H bit is useful in binary coded decimal subroutines.

#### Interrupt Mask Bit (I)

When the I-bit is set, all interrupts are disabled. Clearing this bit enables the interrupts. If an external interrupt occurs while the I-bit is set, the interrupt is latched and processed after the I-bit is next cleared; therefore, no interrupts are lost because of the I-bit being set. An internal interrupt can be lost if it is cleared while the I-bit is set (refer to Programmable Timer, Serial Communications Interface, and Serial Peripheral Interface Sections for more information).

#### Negative (N)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation is negative (bit 7 in the result is a logic one).

## Zero (Z)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation is zero.

# Carry/Borrow (C)

Indicates that a carry or borrow out of the arithmetic logic unit (ALU) occurred during the last arithmetic operation. This bit is also affected during bit test and branch instructions, shifts, and rotates.

# Built-In-Test (BIT)

The BIT test routines utilize the SPI interface of the HIP7030A2 to provide an efficient method to test devices, both at the component and board level. The BIT routines are invoked by resetting the HIP7030A2 while applying 9VDC (through a 4.7k $\Omega$  resistor) to the IRQ pin and 5V<sub>DC</sub> to the TCAP pin. After reset, the HIP7030A2 will begin executing the BIT code stored at locations \$1F00-\$1FF1. The COP system remains active during BIT. When the BIT program begins, the SPI is configured in the master mode. SPI transfers are therefore controlled by the HIP7030A2. The tester paces the transfers by driving the IRQ line low to initiate a SPI transfer. When the transfer is complete, the tester raises  $\overline{IRQ}$  (to 5-9V<sub>DC</sub>) to signal successful transfer and to prepare for the next transfer. A convenient means of driving the IRQ pin is to connect it to  $9V_{\mbox{DC}}$  through a  $4.7k\Omega$  resistor and to drive it with an open-collector/collector device such as the collector of an NPN device with its emitter grounded.

Following reset, the HIP7030A2 waits for a command to be received from the tester by monitoring the  $\overline{IRQ}$  line and the SPIF flag in the SSR.  $\overline{SS}$  should normally be held high throughout the BIT procedure. If  $\overline{SS}$  is low following reset, the BIT routine will immediately branch to location \$5D and begin executing the program stored there.

There are five BIT functions which are accessible via the SPI. Each is selected by sending the associated command number to the HIP7030A2. Following completion of each command (except Command \$00), the HIP7030A2 waits for another command. Commands outside of the range \$00-\$04 will be ignored.

# Download (Command \$00):

Download takes 175 bytes from the SPDR and writes them to RAM beginning at \$50 and ending and \$FE. After receiving the 175th byte, the program begins executing at location \$5D. The 13 locations \$50-\$5C are used as a link table to allow testing of the interrupt functions. The link locations are: SPI Interrupt \$50-51; Timer Interrupt \$52-53; IRQ Interrupt \$54-55; SED Interrupt \$56-57; COP Interrupt \$58-59; SWI Interrupt \$5A-5C. If any entries in the link table are not required for the downloaded program, they may be used for variables or subroutines. Interrupts are disabled when execution begins. If interrupts are enabled via a CLI instruction, handling of all interrupts which are generated (including the NEW interrupt) is required.

Location \$5D is always the start location.

| \$0000           | I/O                  | 0000             | PORTS                | 0000   | PORT A DATA REGISTER                | \$00   |                      |        |        |        |

|------------------|----------------------|------------------|----------------------|--------|-------------------------------------|--------|----------------------|--------|--------|--------|

|                  | 32 BYTES             |                  | 1 BYTE               | 4      | UNUSED                              | \$01   |                      |        |        |        |

| \$001f           |                      | 0031             | UNUSED<br>2 BYTES    |        | UNUSED                              | \$02   |                      |        |        |        |

| \$0020           |                      | 0032             | PORTS                | 4      | PORT D DATA REGISTER                | \$03   |                      |        |        |        |

|                  | USER<br>ROM          | 1                | 2 BYTES              |        | PORT A DATA DIRECTION REGISTER      | \$04   |                      |        |        |        |

|                  | 48 BYTES             | ۱.               | UNUSED               | 1      | UNUSED                              | \$05   |                      |        |        |        |

| \$004F<br>\$0050 |                      | 0079<br>0080     | 2 BYTES              |        | UNUSED                              | \$06   |                      |        |        |        |

| \$0050           |                      | 1                | PORTS<br>2 BYTES     |        | PORT D DATA DIRECTION REGISTER      | \$07   |                      |        |        |        |

|                  | RAM<br>176 BYTES     | 1                |                      | 4      | PORT D SPECIAL FUNCTION REGISTER    | \$08   |                      |        |        |        |

|                  | 170 BITES            | 1                | UNUSED<br>1 BYTE     |        | UNUSED                              | \$09   |                      |        |        |        |

| \$00BF<br>\$00C0 | · - <b> </b>         | 0191<br>0192     | SERIAL PERIPHERAL    | 1      | SERIAL PERIPHERAL CONTROL REGISTER  | \$0A   |                      |        |        |        |

|                  | STACK                | 1                | INTERFACE<br>3 BYTES |        | SERIAL PERIPHERAL STATUS REGISTER   | \$0B   |                      |        |        |        |

|                  | 64 BYTES             | 1                | UNUSED               | 1      | SERIAL PERIPHERAL DATA I/O REGISTER | \$0C   |                      |        |        |        |

| \$00FF           |                      | 0255             | 2 BYTES              |        | UNUSED                              | \$0D   |                      |        |        |        |

| \$0100           |                      | 0256             | SENDEC INTERFACE     |        | UNUSED                              | \$0E   |                      |        |        |        |

|                  | USER                 | 1                | 3 BYTES              |        | SENDEC CONTROL REGISTER             | \$0F   |                      |        |        |        |

|                  | ROM<br>2048 BYTES    | 1                | TIMER<br>10 BYTES    |        | SENDEC STATUS REGISTER              | \$10   |                      |        |        |        |

| \$08FF           |                      | 2303 \<br>2304 \ |                      |        |                                     | 4      | SENDEC DATA REGISTER | \$11   |        |        |

| \$0900           |                      |                  |                      |        | 2304 V                              | 2304 \ | 2304 V               | 2304 \ | 2304 \ | 1 BYTE |

|                  | UNUSED<br>5632 BYTES | 1                | WATCHDOG             | 1 [    | TIMER STATUS REGISTER               | \$13   |                      |        |        |        |

|                  | 3032 BTTES           | 1                | 2 BYTES              |        | INPUT CAPTURE HIGH REGISTER         | \$14   |                      |        |        |        |

| \$1EFF<br>\$1F00 |                      | 7935<br>7936     | UNUSED               | 1 F    | INPUT CAPTURE LOW REGISTER          | \$15   |                      |        |        |        |

|                  |                      |                  | 1 BYTE               | 0031   | OUTPUT COMPARE HIGH REGISTER        | \$16   |                      |        |        |        |

|                  | BUILT-IN-TEST        |                  |                      | ۱<br>۱ | OUTPUT COMPARE LOW REGISTER         | \$17   |                      |        |        |        |

| \$1FE1           |                      |                  |                      | Ň      | COUNTER HIGH REGISTER               | \$18   |                      |        |        |        |

| \$1FE2           |                      |                  |                      | N N    | COUNTER LOW REGISTER                | \$19   |                      |        |        |        |

|                  | BUILT-IN-TEST        | > 25             | 6 BYTES              | 1      | ALTERNATE COUNTER HIGH REGISTER     | \$1A   |                      |        |        |        |

|                  | VECTORS              |                  |                      | ۱<br>۱ | ALTERNATE COUNTER LOW REGISTER      | \$1B   |                      |        |        |        |

| \$1FF1           |                      | 8177             |                      | Ň      | UNUSED                              | \$1C   |                      |        |        |        |

| \$1FF2           |                      | 8178             |                      |        | WATCHDOG RESET REGISTER             | \$1D   |                      |        |        |        |

|                  | USER<br>VECTORS      |                  |                      | ۱<br>۱ | WATCHDOG STATUS REGISTER            | \$1E   |                      |        |        |        |

| \$1FFF           | 14 BYTES             | 8191             |                      | Ň      | UNUSED                              | \$1F   |                      |        |        |        |

FIGURE 8. MEMORY MAP OF THE HIP7030A2

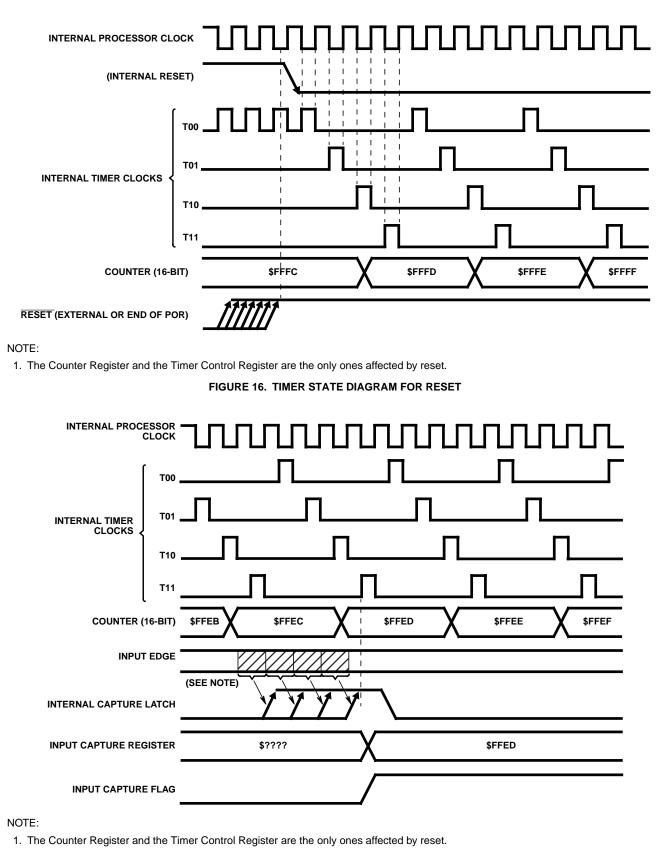

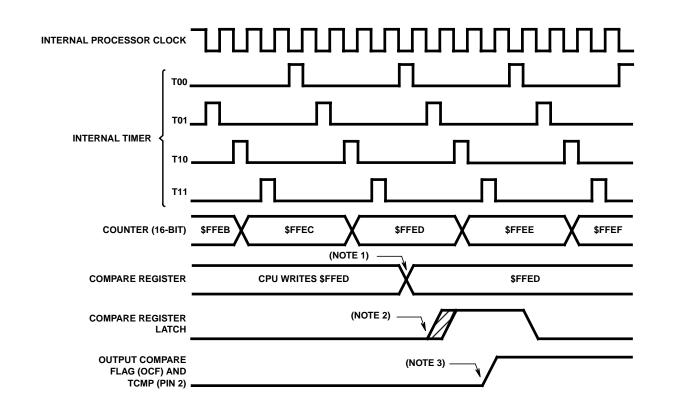

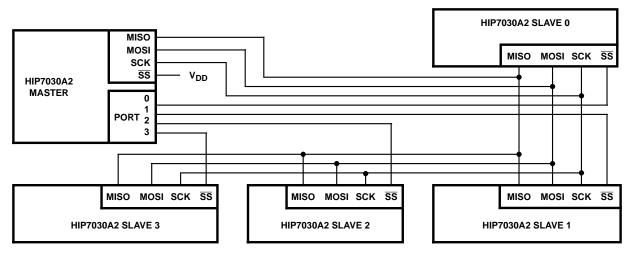

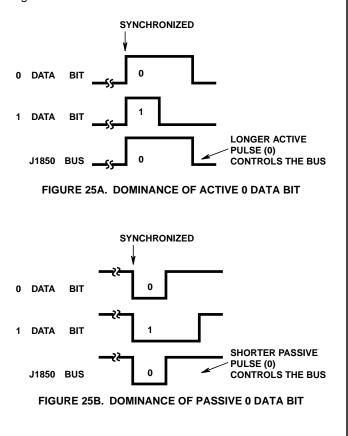

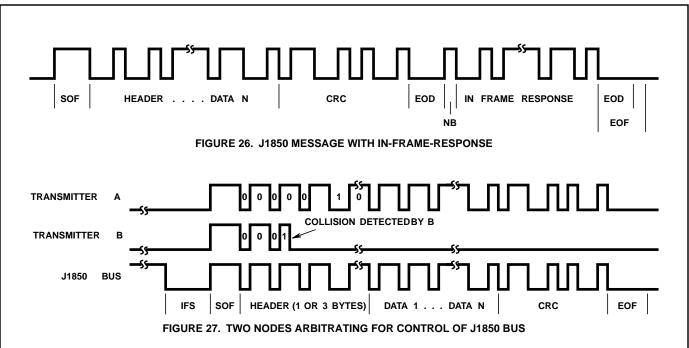

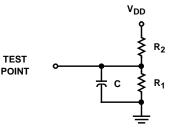

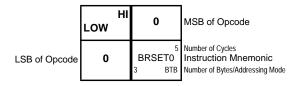

# ROM Dump (Command \$01):