HV9605C

Preliminary

## **High Voltage Current Mode PWM Controller**

### **Ordering Information**

|     | +V <sub>IN</sub> | Feedback | Мах        |                       | Package Options            |          |  |  |  |  |

|-----|------------------|----------|------------|-----------------------|----------------------------|----------|--|--|--|--|

| Mir |                  | Accuracy | Duty Cycle | 14 Pin<br>Plastic DIP | 14 Pin<br>Narrow Body SOIC | Die      |  |  |  |  |

| 15\ | / 250V           | <±1%     | 49%        | HV9605CP              | HV9605CNG                  | HV9605CX |  |  |  |  |

### **Features**

- BiCMOS/DMOS technology

- Current mode control

- □ 49% duty cycle operation

- Programmable START/STOP capability

- □ 15V to 250V input range internal start-up regulator

- □ 6.0µA standby supply current for +V<sub>IN</sub> <20V

- □ 0.9mA operating supply current

- □ 5.0V V<sub>DD</sub> supply operation

- 30KHz to 300KHz internal oscillator

- □ 15KHz to 150KHz converter output frequency

- 1.0MHz low offset error amplifier

- □ 1.25V 2% band gap reference

- Output driver optimized for under 10W applications

- $\Box$  Low driver output impedance with V<sub>DD</sub> = 0V

- □ Fast (90nsec) over current shutdown

- □ All pins are ESD protected

### **Applications**

- ISDN network terminations

- ISDN terminals

- ISDN terminal adapters

- Feature phones

- SLIC circuits

- PBX systems

- Modems

- Distributed power systems

- DC/DC converters

# **General Description**

The Supertex HV9605C is a BiCMOS/DMOS single-output, current mode, pulse width modulator IC designed to meet the requirements of ETR-080 for ISDN applications. In a 14 pin package, it provides all the necessary functions to implement a single-switch PWM with a minimum of external parts.

Utilizing Supertex's proprietary BiCMOS/DMOS technology, it requires less than one tenth of the operating power of conventional bipolar PWM ICs. Dynamic range for regulation is also increased to approximately 8 times that of similar bipolar parts. It operates directly from any DC input voltage between 15 and 250 VDC. The START and STOP input voltage thresholds can be programmed within the operating input voltage range by means of a resistor divider, provided +V<sub>IN(START)</sub> > +V<sub>IN(STOP)</sub>. The output stage is push-pull CMOS, eliminating the need for external clamping diodes. The clock frequency is set with a single external resistor.

### **Absolute Maximum Ratings\***

| +V <sub>IN</sub> , Input Voltage      | -0.5V to +250V  |

|---------------------------------------|-----------------|

| Supply Voltage, V <sub>DD</sub>       | -0.5V to +10V   |

| Operating Temperature Range           | -40°C to +85°C  |

| Storage Temperature Range             | -65°C to +150°C |

| Power Dissipation @ 25°C, SOIC        | 750mW           |

| Power Dissipation @ 25°C, Plastic DIP | 1000mW          |

\*All voltages referenced to GND

#### 11/12/01

Supertex Inc. does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement." Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of devices determined to be defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the Supertex website: http://www.supertex.com. For complete liability information on all Supertex products, refer to the most current databook or to the Legal/Disclaimer page on the Supertex website.

### **Electrical Characteristics**

| Symbol Parameters Min Typ Max Unit Conditions |

|-----------------------------------------------|

|-----------------------------------------------|

#### Pre-Regulator/Start-Up

| +V <sub>IN</sub>    | Regulator input voltage         | 15  |     | 250 | V  |                                                                   |

|---------------------|---------------------------------|-----|-----|-----|----|-------------------------------------------------------------------|

| +I <sub>IN</sub>    | Input leakage current           |     |     | 6.0 | μA | +V <sub>IN</sub> =20V, Start=0V, Stop=0V                          |

| +I <sub>IN</sub>    | Input leakage current           |     |     | 15  | μA | $+V_{IN} = 50V, V_{DD} = 4.7V$                                    |

| +I <sub>IN</sub>    | Input leakage current           |     |     | 70  | μA | $+V_{IN} = 250V, V_{DD} = 4.7V$                                   |

| +I <sub>START</sub> | Pre-regulator start-up current  | 5.0 |     |     | mA | +V <sub>IN</sub> = 15V,<br>Start & Stop 10MΩ to + V <sub>IN</sub> |

| V <sub>DD</sub>     | Regulator output voltage        | 4.4 | 4.5 | 4.6 | V  |                                                                   |

| UVLO                | Under voltage lockout threshold | 4.1 | 4.2 | 4.4 | V  | V <sub>DD</sub> rising                                            |

| HYST                | Under voltage hysteresis        | 0.1 | 0.3 | 0.4 | V  |                                                                   |

### Supply

| V <sub>DD</sub> | Operating range | 4.7 |     | 8.0 | V  |                                                              |

|-----------------|-----------------|-----|-----|-----|----|--------------------------------------------------------------|

| I <sub>DD</sub> | Supply current  |     | 0.9 | 1.3 | mA | OUT open,<br>$f_{OUT} = 20$ KHz to 150KHz,<br>$V_{DD} = 5$ V |

#### Start/Stop Control

| V <sub>START</sub> | Start threshold                 | 6.72 | 7.30 | 7.88 | V  |                        |

|--------------------|---------------------------------|------|------|------|----|------------------------|

| I <sub>START</sub> | Start input current             |      |      | 0.05 | μA | +V <sub>IN</sub> = 18V |

| I <sub>STOP</sub>  | Stop input current              |      |      | 0.05 | μA | +V <sub>IN</sub> = 18V |

| V <sub>CLAMP</sub> | Zener clamp voltage on STOP Pin | 15   |      |      | V  |                        |

#### **MOSFET Driver Output**

| V <sub>OUT(HIGH)</sub> | Output high voltage | 4.85 | 4.90 |      | V    | $I_{OUT} = 10 \text{mA}, V_{DD} = 5.00 \text{V}$ |

|------------------------|---------------------|------|------|------|------|--------------------------------------------------|

| V <sub>OUT(LOW)</sub>  | Output low voltage  |      | 0.05 | 0.15 | V    | $I_{OUT} = -10 mA$                               |

| t <sub>R</sub>         | Rise time           |      | 30   | 50   | nsec | C <sub>L</sub> = 250pF                           |

| t <sub>F</sub>         | Fall time           |      | 20   | 50   | nsec | C <sub>L</sub> = 250pF                           |

#### Oscillator

|                  |                            |      | 150 |      | KHz    | $R_T = 91 K\Omega$                                    |

|------------------|----------------------------|------|-----|------|--------|-------------------------------------------------------|

| f <sub>OUT</sub> | Output converter frequency | 45   | 50  | 55   | KHz    | $R_T = 357 K\Omega$                                   |

|                  |                            | 31.5 | 35  | 38.5 | KHz    | $R_T = 536 K\Omega$                                   |

|                  |                            | 18   | 20  | 22   | KHz    | $R_T = 1.0M\Omega$                                    |

| T <sub>C</sub>   | Temperature coefficient    |      | 100 | 300  | PPM/°C | f <sub>OUT</sub> = 50KHz                              |

| Δf/f             | Voltage stability          |      | 1   | 3    | %      | f <sub>OUT</sub> = 50KHz, 4.5V< V <sub>DD</sub> <5.5V |

### Electrical Characteristics (continued)

| Symbol Parameters Min Typ Max Unit Conditions |

|-----------------------------------------------|

|-----------------------------------------------|

#### PWM

| D <sub>MAX</sub> | Maximum duty cycle                        | 49.0 |    | 49.9 | %    | f <sub>OUT</sub> = 20KHz |

|------------------|-------------------------------------------|------|----|------|------|--------------------------|

| D <sub>MIN</sub> | Minimum duty cycle                        |      |    | 0    | %    |                          |

|                  | Minimum pulse width before pulse drop out |      | 80 | 125  | nsec |                          |

#### Reference

| V <sub>REF</sub>        | Reference output voltage | 1.225 | 1.250 | 1.275 | V  | $T_A = 25^{\circ}C$             |

|-------------------------|--------------------------|-------|-------|-------|----|---------------------------------|

| V <sub>REF</sub>        | Load regulation          |       | 1.0   | 5.0   | mV | 0 < I <sub>REF</sub> < 0.3mA    |

| V <sub>REF</sub>        | Line regulation          |       | 2.0   | 5.0   | mV | 4.5V < V <sub>DD</sub> < 5.5V   |

| V <sub>REF</sub>        | Reference output voltage | 1.207 | 1.250 | 1.293 | V  | -40°C < T <sub>A</sub> < 85°C   |

|                         | Long term stability      |       | 3.0   |       | mV | T <sub>A</sub> = 125°C, 1000hrs |

| I <sub>REF(SHORT)</sub> | Short circuit current    |       | 0.5   | 1.0   | mA | V <sub>REF</sub> = SGND         |

#### **Current Sensing**

| V <sub>CS</sub>         | Usable control current sense range |     |     | V <sub>CS</sub> (limit) | V    |                        |

|-------------------------|------------------------------------|-----|-----|-------------------------|------|------------------------|

| V <sub>CS (LIMIT)</sub> | Current limit threshold            | 0.6 | 0.7 | 0.8                     | V    |                        |

| t <sub>DELAY</sub>      | Current limit delay to output      |     | 90  | 120                     | nsec | V <sub>CS</sub> = 1.5V |

### **Error Amplifier**

| V <sub>FB</sub>                    | Feedback voltage        | 1.238 | 1.250 | 1.263              | V   | REF shorted to NI, FB shorted to Comp, $T_A = 25^{\circ}C$ |

|------------------------------------|-------------------------|-------|-------|--------------------|-----|------------------------------------------------------------|

| I <sub>FB</sub> or I <sub>NI</sub> | Input bias current      |       | 25    | 200                | nA  | V <sub>FB</sub> = 3.0V, V <sub>NI</sub> = 2.5V             |

| V <sub>OS</sub>                    | Input offset voltage    |       | 5.0   | 25                 | mV  |                                                            |

| V <sub>CM</sub>                    | Common mode input range | 0     |       | V <sub>DD</sub> -1 | V   |                                                            |

| A <sub>VOL</sub>                   | Open loop voltage gain  | 65    | 90    |                    | dB  |                                                            |

| BW                                 | Unity gain bandwidth    | 1.0   | 1.5   |                    | MHz |                                                            |

| ISOURCE                            | Output current sourcing |       | -2    | -1                 | mA  | V <sub>FB</sub> < V <sub>NI</sub>                          |

| I <sub>SINK</sub>                  | Output current sinking  | 2     | 4     |                    | mA  | V <sub>FB</sub> > V <sub>NI</sub>                          |

| PSRR                               | Power supply rejection  | 50    | 72    |                    | dB  | 4.5V < V <sub>DD</sub> < 5.5V, f=1KHz                      |

#### Status Output

| I <sub>SINK</sub>         | Output current sinking  | 5.0                  | 10   |          | mA   | V <sub>STATUS</sub> = 2.0V |

|---------------------------|-------------------------|----------------------|------|----------|------|----------------------------|

| I <sub>SOURCE</sub>       | Output current sourcing | 5.0                  | 10   | 15       | μΑ   |                            |

| V <sub>STATUS(HIGH)</sub> | High output voltage     | V <sub>DD</sub> -0.2 |      | $V_{DD}$ | V    | No load                    |

| V <sub>STATUS(LOW)</sub>  | Low output voltage      |                      | 1.0  | 2.0      | V    | Sinking 5mA                |

|                           |                         |                      | 0.02 | 0.04     | V    | Sinking 100µA              |

| t <sub>R</sub>            | Rise time               | 1.0                  | 5.0  |          | msec | 4.7nF From Status to GND   |

HV9605C

- SGND Common connection for all low level signal and digital circuits. While SGND and PGND must be electrically connected together, having separate common pins enhances the ability of the designer to prevent coupling of noise into critical circuits.

- PGND This pin provides common return for the high transient current of the output driver circuits. While PGND and SGND must be electrically connected, having a separate connection prevents common noise created by the high transient currents of the output driver from being injected into critical circuits.

- +V<sub>IN</sub> This is the start-up linear pre-regulator input which can accept DC input voltages in the range of 15V to 250V. With START and STOP set to more than 20V, the leakage current on this pin is less than  $6.0\mu A$  at +V<sub>IN</sub> = 20V.

- **START** The resistive divider from  $+V_{IN}$  sets the start voltage.

- **STOP** The resistive divider from  $+V_{IN}$  sets the stop voltage.

- V<sub>DD</sub> This is the supply pin for the PWM circuits. When the input voltage to the +V<sub>IN</sub> pin exceeds the start voltage the input regulator seeks to regulate the voltage on the capacitor connected to this pin to a nominal 4.5V.

- OUT This high current push-pull CMOS output is intended to drive the gate of a power MOSFET. In order to protect the power MOSFET in high electrical noise environment, this output appears as low impedance to PGND when V<sub>DD</sub> is at zero volts.

- CS This is the current sense input to the PWM comparators. Under normal operation the over current limit is triggered when the voltage on this pin is at 0.70V and the loop control operating peak current may be set to any level below this, typically in the range of 0.2 to 0.5V.

- **COMP** The low impedance output of the error amplifier.

- **FB** The high impedance inverting input of the error amplifier.

- NI The high impedance non-inverting input of the error amplifier.

- REF This pin provides a 2% accuracy 1.25V low output impedance buffered reference which is current limited to 0.5mAmps and should be bypassed, REF to SGND, with a 0.1μF ceramic capacitor.

- **RT** The resistor connected from this pin to SGND sets the frequency of the internal oscillator by setting the charging current for the internal timing capacitor. The oscillator frequency is twice the PWM output frequency.

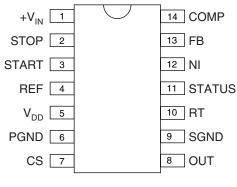

### **Pin Configuration**

14 Pin SOIC/DIP Package

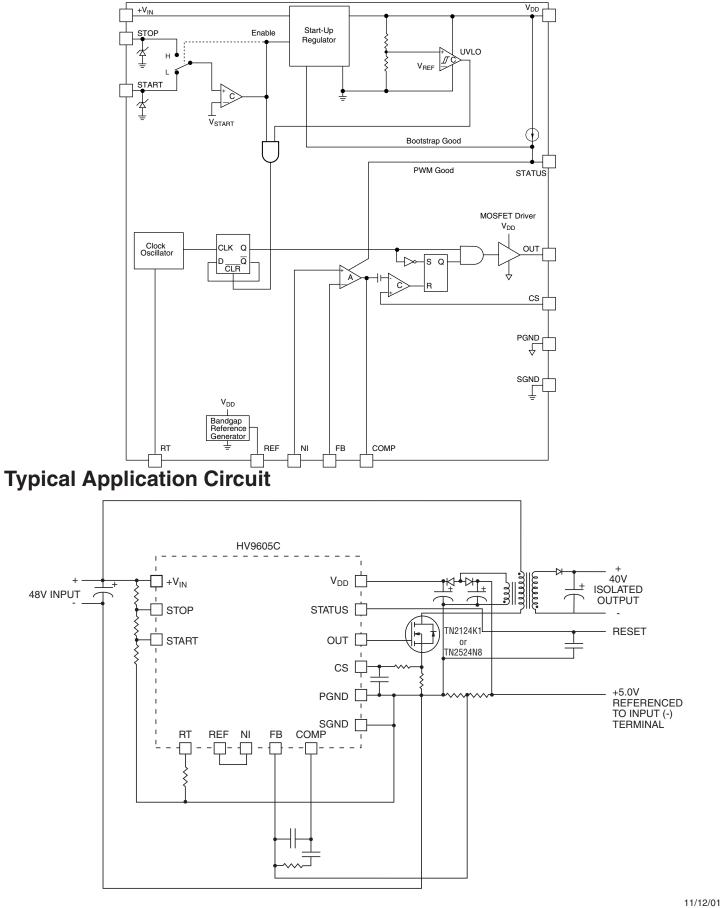

### **Functional Block Diagram**

Supertex inc.

1235 Bordeaux Drive, Sunnyvale, CA 94089 TEL: (408) 744-0100 • FAX: (408) 222-4895 www.supertex.com

©2001 Supertex Inc. All rights reserved. Unauthorized use or reproduction prohibited.