## **INTEL 430MX PCISET** 82371MX MOBILE PCI I/O IDE XCELERATOR (MPIIX)

- Provides a Bridge Between the PCI Bus and Extended I/O Bus

- PCI Bus; 25–33 MHz

- Extended I/O Bus: 7.5–8.33 MHz

- System Power Management (Intel SMM) Support)

- Programmable System Management Interrupt (SMI)—Hardware/Software Events. EXTSMI#

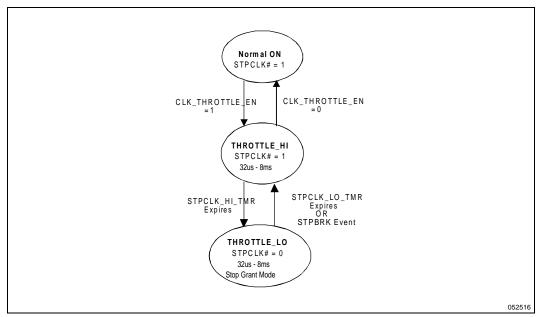

- Programmable CPU Clock Control (STPCLK#) with Auto Clock Throttle

- Peripheral Device Power Management (Local Standby)

- Suspend State Support (Suspend-to-DRAM and Suspend-to-Disk)

- Enhanced DMA Functions

- Two 8237 DMA Controllers

- Fast Type F DMA

- Compatible DMA Transfers

- PC/PCI DMA Expansion for Docking Support

- Fast IDE Interface

- PIO Mode 4 Transfers

- 2x16-Bit Posted Write Buffer and 1x32-Bit Read Prefetch Buffer

- Plug-n-Play Port for Motherboard Devices

- 3 Steerable DMA Channels

- 1 Steerable Interrupt Line (Plus 2) Steerable PCI Interrupts)

- 1 Programmable Chip Select

- Functionality of One 82C54 Timer System Timer

- Refresh Request

- Speaker Tone Output

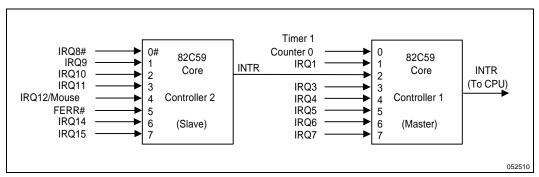

- Functionality of Two 82C59 Interrupt Controllers

- 14 Interrupts Supported

- Independently Programmable for **Edge/Level Sensitivity**

- X-Bus Peripheral Support - Chip Select Decode

- **Controls Lower X-Bus Data Byte** Transceiver

- Non-Maskable Interrupts (NMI) — PCI System Error Reporting

- NAND Tree for Board-Level ATE Testing

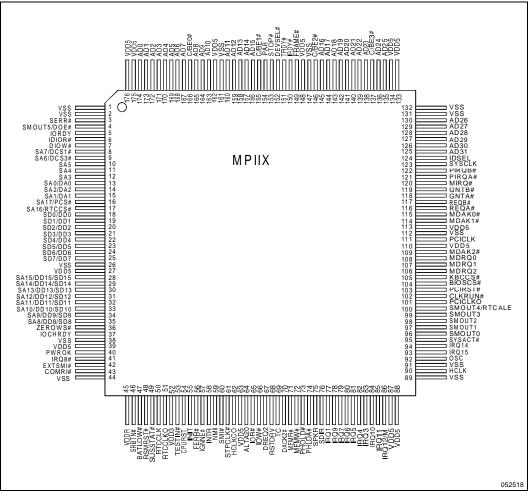

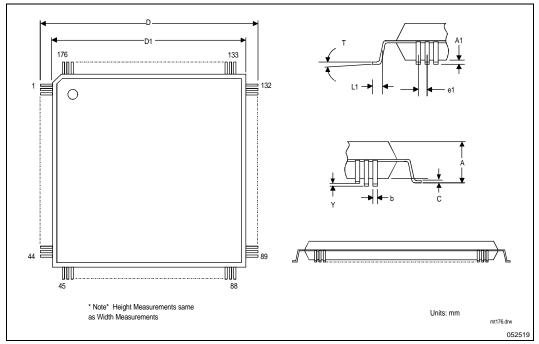

- 176-Pin TQFP

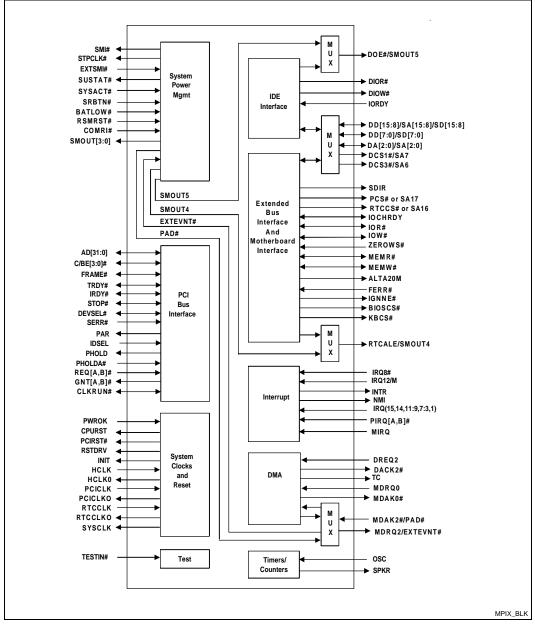

The 82371MX PCI I/O IDE Xcelerator (MPIIX) provides the bridge between the PCI bus and the ISA-like Extended I/O expansion bus. In addition, the 82371MX has an IDE interface that supports two IDE devices providing an interface for IDE hard disks and CD ROMs. The MPIIX integrates many common I/O functions found in ISA based PC systems—a seven-channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, Intel SMM power management support, and control logic for NMI generation. Chip select decoding is provided for BIOS, real time clock, and keyboard controller. Edge/Level interrupts and interrupt steering are supported for PCI plug and play compatibility.

The MPIIX also provides the Extended I/O Bus for a direct connection to Super I/O devices providing a complete PC-compatible I/O solution. MPIIX also provides support for the "Mobile PC/PCI" DMA Expansion protocol that enables the implementation of Docking Stations with full ISA and PCI capability without running the full ISA bus across the docking connector. For motherboard Plug-n-Play compatibility, the 82371MX also provides three steerable DMA channels, up to three steerable interrupt lines, and a programmable chip select. The interrupt lines can be routed to any of the available ISA interrupts.

The MPIIX's power management function supports SMI# interrupt sources, extensive clock control (including Auto Clock Throttling), peripheral power idle detection with access traps, system Suspend-to-DRAM and Suspend-to-Disk.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to those specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

COPYRIGHT © INTEL CORPORATION, 1996

April 1996

Order Number: 290525-001

82371MX MPIIX Block Diagram

## CONTENTS

| 1.0. ARCHITECTURE OVERVIEW                                         | 9  |

|--------------------------------------------------------------------|----|

| 2.0 SIGNAL DESCRIPTION                                             | 11 |

| 2.1. PCI Interface Signals                                         | 11 |

| 2.2. IDE Interface Signals                                         | 13 |

| 2.3. Extended I/O Bus Signals                                      | 14 |

| 2.4. Motherboard I/O Device Interface Signals                      | 15 |

| 2.5. DMA Signals                                                   | 17 |

| 2.6. Interrupt Controller Signals                                  | 17 |

| 2.7. System Power Management (SMM) Signals                         | 19 |

| 2.8. System Clock And Reset Signals                                | 20 |

| 2.9. Test Signals                                                  | 21 |

| 3.0. REGISTER DESCRIPTION                                          | 22 |

| 3.1. Register Access                                               | 22 |

| 3.2. PCI Configuration Registers                                   | 27 |

| 3.2.1. VID—VENDOR IDENTIFICATION REGISTER                          | 27 |

| 3.2.2. DID—DEVICE IDENTIFICATION REGISTER                          | 27 |

| 3.2.3. COM—COMMAND REGISTER                                        |    |

| 3.2.4. DS—DEVICE STATUS REGISTER                                   |    |

| 3.2.5. RID—REVISION IDENTIFICATION REGISTER                        | 29 |

| 3.2.6. CLASSC—CLASS CODE REGISTER                                  | 29 |

| 3.2.7. HEDT—HEADER TYPE REGISTER                                   | 30 |

| 3.2.8. SPPE—SERIAL & PARALLEL PORT ENABLE REGISTER                 | 30 |

| 3.2.9. ECRT— EXTENDED I/O CONTROLLER RECOVERY TIMER REGISTER       |    |

| 3.2.10. BIOSE — BIOS ENABLE REGISTER                               | 31 |

| 3.2.11. FDCE—FDC ENABLE REGISTER                                   |    |

| 3.2.12. PIRQRC [A,B]—PIRQX ROUTE CONTROL REGISTERS                 |    |

| 3.2.13. MSTAT—MISCELLANEOUS STATUS REGISTER                        |    |

| 3.2.14. IDETIM—IDE TIMING REGISTER                                 |    |

| 3.2.15. MIRQRC—MOTHERBOARD DEVICE IRQ ROUTE CONTROL REGISTER       |    |

| 3.2.16. MDMARC[2:0]-MOTHERBOARD DEVICE DMA ROUTE CONTROL REGISTERS |    |

| 3.2.17. AUDIOE—AUDIO ENABLE REGISTER                               |    |

| 3.2.18. DMADS—DMA CH[7:5] DATA SIZE REGISTER                       |    |

| 3.2.19. PCIDMAE—PCI DMA ENABLE REGISTER                            |    |

| 3.2.20. PCIDMA[A,B]—PCI DMA AND PCI DMA EXPANSION REGISTER         |    |

| 3.2.21. PMAC[1:0]—PROGRAMMABLE MEMORY ADDRESS CONTROL REGISTERS    |    |

| 3.2.22. PMAM[1:0]—PROGRAMMABLE MEMORY ADDRESS MASK REGISTERS       | 40 |

| 3.2.23. PARE—PROGRAMMABLE ADDRESS RANGE ENABLE REGISTER            | 40 |

| 3.2.24. PCSC—PROGRAMMABLE CHIP SELECT CONTROL REGISTER             | 41 |

## PRELIMINARY

3

| 3.2.25. | PAC[5:1]—PROGRAMMABLE ADDRESS CONTROL REGISTER      | .41 |

|---------|-----------------------------------------------------|-----|

| 3.2.26. | PAMA—PROGRAMMABLE ADDRESS MASK A REGISTER           | .41 |

| 3.2.27. | PAMB—PROGRAMMABLE ADDRESS MASK B REGISTER           | .42 |

| 3.2.28. | IOCA-I/O CONFIGURATION ADDRESS REGISTER             | .42 |

| 3.2.29. | PAMC—PROGRAMMABLE ADDRESS MASK C REGISTER           | .43 |

| 3.2.30. | PADE[2:0]—PERIPHERAL ACCESS DETECT ENABLE REGISTERS | .43 |

| 3.2.31. | LTADEV3—Local Trap Address for Device 3 Register    | .44 |

| 3.2.32. | LTMDEV3—Local Trap Mask for Device 3 Register       | .44 |

| 3.2.33. | LTSMIE—Local Trap SMI Enable Register               | .44 |

| 3.2.34. | LTSMIS—Local Trap SMI Status Register               | .45 |

| 3.2.35. | LSBSMIE—Local Standby SMI Enable Register           | .45 |

| 3.2.36. | LSBTRE—Local Standby Timer Reload Enable Register   | .46 |

| 3.2.37. | LSBSMIS—Local Standby SMI Status Register           | .47 |

| 3.2.38. | LSTBTIDE—Local Standby IDE Timer Register           | .47 |

| 3.2.39. | LSBTAUD—Local Standby Audio Timer Register          | .48 |

| 3.2.40. | LSBTCOM—Local Standby COM Timer Register            | .48 |

| 3.2.41. | LSBTDEV1—Local Standby Device 1 Timer Register      | .48 |

| 3.2.42. | LSBTDEV2—Local Standby Device 2 Timer Register      | .49 |

| 3.2.43. | LSBTDEV3—Local Standby Device 3 Timer Register      | .49 |

| 3.2.44. | SESMIT—Software/EXTSMI# SMI Delay Timer Register    | .49 |

| 3.2.45. | SUSSMIT—Suspend SMI Delay Timer Register            | .50 |

| 3.2.46. | GSBTMR—Global Standby Timer Register                | .50 |

| 3.2.47. | CLKTHSBYT — Clock Throttle Standby Timer Register   | .50 |

| 3.2.48. | SYSMGNTC—System Management Control Register         | .51 |

| 3.2.49. | SYSSMIE—System SMI Enable Register                  | .51 |

| 3.2.50. | MISCSMIE—Misc SMI Enable Register                   | .52 |

| 3.2.51. | GSMIE—Global SMI Enable Register                    | .52 |

| 3.2.52. | SYSSMIS—System SMI STATUS Register                  | .53 |

| 3.2.53. | MISCSMIS—Miscellaneous SMI STATUS Register          | .53 |

| 3.2.54. | GSMIS — Global SMI STATUS Register                  | .54 |

| 3.2.55. | SUSRSMC1—Suspend/Resume Control 1 Register          | .54 |

| 3.2.56. | SUSRSMC2—Suspend/Resume Control 2 Register          | .55 |

| 3.2.57. | SMOUTC—SMOUT Control Register                       | .55 |

| 3.2.58. | SYSEVNTE0—System EVENT Enable 0 Register            | .56 |

| 3.2.59. | SYSEVNTE1—System EVENT Enable 1 Register            | .56 |

| 3.2.60. | SYSEVNTE2—System EVENT Enable 2 Register            | .57 |

| 3.2.61. | BSTCLKT — Burst Count Timer Register                | .57 |

| 3.2.62. | CLKC—Clock Control Register                         | .58 |

| 3.2.63. | STPCLKLT—STPCLK# Low Timer Register                 | .58 |

| 3.2.64. | STPCLKHT—STPCLK# High Timer Count                   | .59 |

| 3.2.65. | STPBRKE0—Stop Break Event Enable 0 Register         | .59 |

| 3.2.66. | STPBRKE1—Stop Break Event Enable 1 Register         | .60 |

|         |                                                     |     |

4

##

| 3.2.67. STPBRKE2—Stop Break Event Enable 2 Register                          | 60 |

|------------------------------------------------------------------------------|----|

| 3.2.68. SHDW—Shadow Register Access Port                                     | 61 |

| 3.2.69. BSTCLKEE[6:0]—Burst Clock Event Enable Registers                     | 63 |

| 3.2.70. CLKTHLBRKEE[6:0]—Clock Throttle Break Event Enable Registers         | 64 |

| 3.3. ISA Compatible Registers                                                | 64 |

| 3.3.1. DMA REGISTERS                                                         | 64 |

| 3.3.1.1. DCOM—DMA Command Register                                           | 65 |

| 3.3.1.2. DCM—DMA Channel Mode Register                                       | 65 |

| 3.3.1.3. DR—DMA Request Register                                             | 66 |

| 3.3.1.4. Mask Register—Write Single Mask Bit                                 |    |

| 3.3.1.5. Mask Register—Write All Mask Bits                                   |    |

| 3.3.1.6. DS—DMA Status Register                                              |    |

| 3.3.1.7. DMA Base and Current Address Registers (8237 Compatible Segment)    | 68 |

| 3.3.1.8. DMA Base and Current Byte/Word Count Registers (Compatible Segment) |    |

| 3.3.1.9. DMA Memory Low Page Registers                                       | 69 |

| 3.3.1.10. DMA Clear Byte Pointer Register                                    |    |

| 3.3.1.11. DMC—DMA Master Clear Register                                      | 70 |

| 3.3.1.12. DCLM—DMA Clear Mask Register                                       |    |

| 3.3.2. TIMER/COUNTER REGISTERS                                               |    |

| 3.3.2.1. TCW—Timer Control Word Register                                     |    |

| 3.3.2.2. Interval Timer Status Byte Format Register                          |    |

| 3.3.2.3. Counter Access Ports Register                                       |    |

| 3.3.3. INTERRUPT CONTROLLER REGISTERS                                        |    |

| 3.3.3.1. ICW1—Initialization Command Word 1 Register                         |    |

| 3.3.3.2. ICW2—Initialization Command Word 2 Register                         |    |

| 3.3.3.3. ICW3—Initialization Command Word 3 Register                         |    |

| 3.3.3.4. ICW3—Initialization Command Word 3 Register                         |    |

| 3.3.3.5. ICW4—Initialization Command Word 4 Register                         |    |

| 3.3.3.6. OCW1—Operational Control Word 1 Register                            |    |

| 3.3.3.7. OCW2—Operational Control Word 2 Register                            |    |

| 3.3.3.8. OCW3—Operational Control Word 3 Register                            |    |

| 3.3.3.9. ELCR1—Edge/Level Triggered Register                                 |    |

| 3.3.3.10. ELCR2—Edge/Level Triggered Register                                |    |

| 3.3.4. RESET EXTENDED I/O-BUS IRQ12 AND IRQ1 REGISTER                        |    |

| 3.3.5. NMI REGISTERS                                                         |    |

| 3.3.5.1. NMISC—NMI Status and Control Register                               |    |

| 3.3.5.2. NMI Enable and Real-Time Clock Address Register                     |    |

| 3.3.5.3. Coprocessor Error Register                                          |    |

| 3.3.5.4. RC-Reset Control Register                                           |    |

| 3.3.5.5. Port 92 Register                                                    |    |

| 3.4. Advanced Power Management Registers                                     |    |

| 3.4.1. APMC—ADVANCED POWER MANAGEMENT CONTROL PORT                           | 83 |

| 3.4.2. APMS—ADVANCED POWER MANAGEMENT STATUS PORT                           | 83  |

|-----------------------------------------------------------------------------|-----|

| 4.0. FUNCTIONAL DESCRIPTION                                                 | 84  |

| 4.1. Memory And I/O Address Map                                             | 84  |

| 4.1.1. I/O ACCESSES                                                         | 84  |

| 4.1.2. BIOS MEMORY ACCESS                                                   | 84  |

| 4.1.3. PERIPHERAL CHIP SELECTS                                              | 85  |

| 4.2. PCI Interface                                                          | 86  |

| 4.2.1. TRANSACTION TERMINATION                                              | 86  |

| 4.2.2. PARITY SUPPORT                                                       | 86  |

| 4.2.3. PCI ARBITRATION                                                      | 87  |

| 4.2.4. PCI CLOCK CONTROL (CLKRUN#)                                          | 87  |

| 4.3. Extended I/O Bus                                                       |     |

| 4.3.1. EXTENDED I/O BUS CYCLES FOR MPIIX AS A MASTER (PCI MASTER INITIATED) | 88  |

| 4.3.2. EXTENDED I/O BUS DMA (8-BIT AND 16-BIT TRANSFERS)                    | 89  |

| 4.4. DMA Controller                                                         |     |

| 4.4.1. TYPE F TIMING                                                        |     |

| 4.4.2. DMA buffer for PCI DMA type F transfers                              | 91  |

| 4.4.3. EXTENDED I/O BUS DMA ARBITRATION                                     |     |

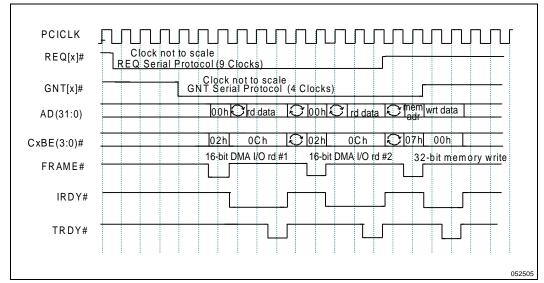

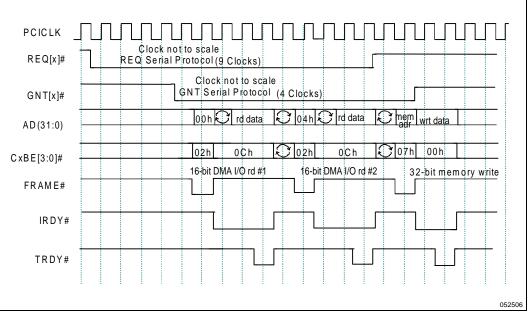

| 4.4.4. PCI DMA                                                              |     |

| 4.4.4.1. PCI DMA Expansion Protocol                                         |     |

| 4.4.4.2. PCI DMA Expansion Cycles                                           |     |

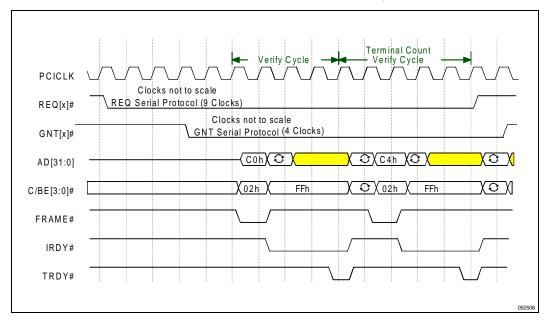

| 4.4.4.3. Normal DMA Cycle                                                   |     |

| 4.4.4.4. Normal DMA Cycle with Terminal Count                               |     |

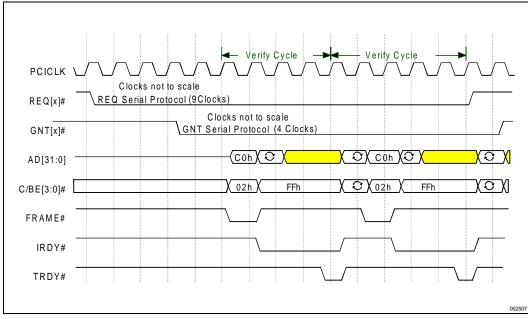

| 4.4.4.5. Verify DMA Cycle                                                   |     |

| 4.4.4.6. Verify DMA Cycle with Terminal Count                               |     |

| 4.5. IDE Interface                                                          |     |

| 4.5.1. ATA REGISTER BLOCK DECODE                                            |     |

| 4.5.2. ENHANCED TIMING MODES                                                |     |

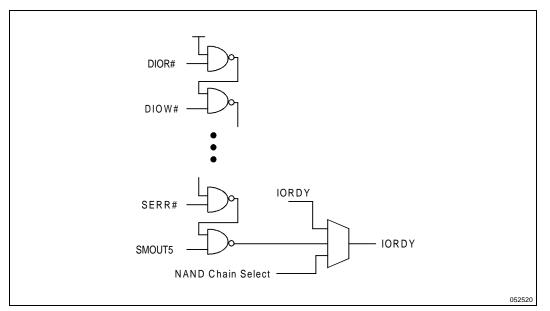

| 4.5.2.1. IORDY masking                                                      |     |

| 4.5.2.2. PIO 32 bit IDE data port mode                                      |     |

| 4.6. Interval Timer                                                         |     |

| 4.7. Interrupts                                                             |     |

| 4.7.1. PROGRAMMING THE INTERRUPT CONTROLLER                                 | -   |

| 4.7.1.1. Edge and Level Triggered Mode                                      |     |

| 4.7.2. INTERRUPT STEERING                                                   |     |

| 4.7.3. MOUSE FUNCTION                                                       |     |

| 4.7.4. COPROCESSOR ERROR FUNCTION                                           |     |

| 4.7.5. NMI SUPPOR I                                                         |     |

| 4.8. Power Management Support                                               |     |

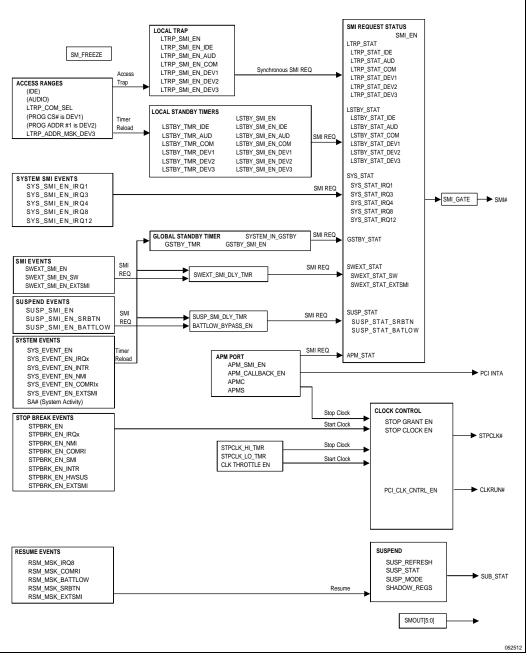

| 4.8.1. SMI GENERATION                                                       |     |

| 4.0.1.1. OWI LIADES                                                         | 100 |

##

### 82371MX (MPIIX)

# intel®

| 4.8.1.2. SMI Request Status                                 |     |

|-------------------------------------------------------------|-----|

| 4.8.1.3. SMI# Signal Generation                             | 108 |

| 4.8.1.4. SMI SOURCES                                        | 108 |

| 4.8.2. CPU POWER MANAGEMENT (CPU, DRAM, L2 CACHE, DATAPATH) | 110 |

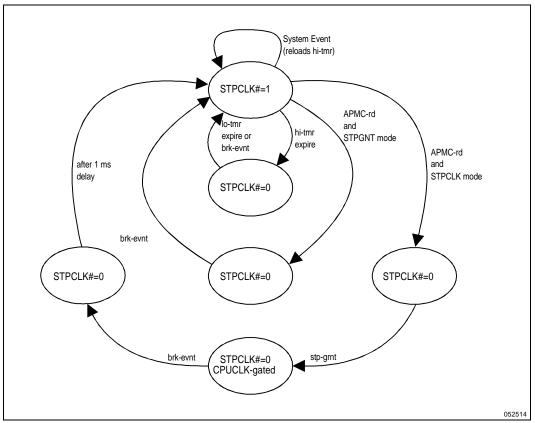

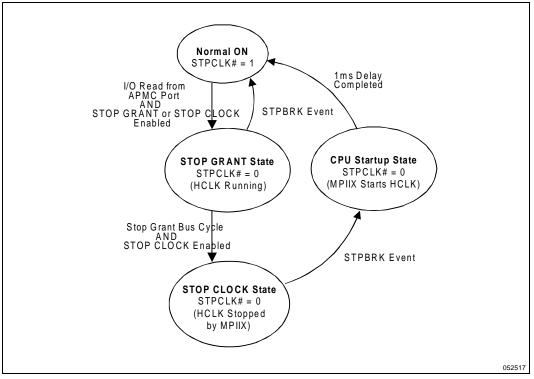

| 4.8.2.1. Stop Clock                                         | 110 |

| 4.8.2.2. Software Control of STPCLK#                        | 112 |

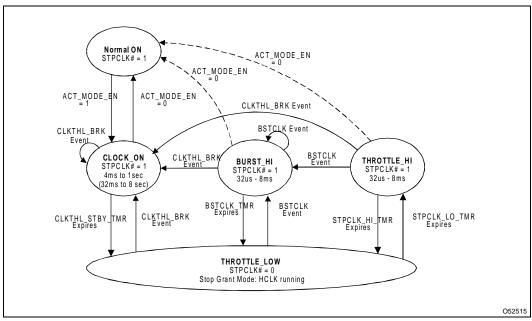

| 4.8.2.3. Emulating Clock Division (Clock Throttling)        | 112 |

| 4.8.2.4. STPCLK Control State Machine                       | 113 |

| 4.8.2.5. Auto Clock Throttle (ACT) Feature                  | 114 |

| 4.8.3. LOCAL STANDBY (PERIPHERAL MANAGEMENT)                | 117 |

| 4.8.3.1. Local Standby Sequence                             | 117 |

| 4.8.3.2. Access Ranges                                      | 118 |

| 4.8.3.3. Idle Timers                                        | 118 |

| 4.8.3.4. Access Traps                                       | 119 |

| 4.8.3.5. SMOUT Programmable Outputs                         | 119 |

| 4.8.4. SUSPEND                                              | 119 |

| 4.8.4.1. Suspend mode selects                               | 120 |

| 4.8.4.2. Suspend SMI# Requests (SRBTN# and BATLOW#)         |     |

| 4.8.4.3. Suspend Status (SUSTAT#) Signal and Register       |     |

| 4.8.4.4. POWER PLANE CONTROL                                |     |

| 4.8.4.5. SHADOW REGISTERS                                   |     |

| 4.8.5. SUMMARY OF TIMER RANGES                              |     |

| 4.9. Reset Support                                          | 124 |

| 5.0. PINOUT AND PACKAGE INFORMATION                         |     |

| 5.1. Pinout Information                                     | 125 |

| 5.2. Package Information                                    | 129 |

| 6.0. TESTABILITY                                            | 130 |

##

82371MX (MPIIX)

intel®

### **1.0. ARCHITECTURE OVERVIEW**

This section provides a brief overview of the MPIIX. More detailed descriptions are provided in the Signal Description, Register Description, and Functional Description sections.

**Power Management.** Flexible power management capabilites of the MPIIX permit the operating system and system software to efficiently manage the use of system resources. Various low power states are supported while providing the best performance to the user. MPIIX uses several mechanisms to help the power management software initiate and manage the transitions between the power managed states. These include, System Event Monitors such as Idle Timers to identify peripheral and system-wide idle and wake-up conditions, Intel's System Management Interrupt (SMI) support, Advanced Power Management (APM) interface, Pentium® Processor STPCLK# Clock Control, and Low Power Suspend/Resume hardware.

**Docking Support.** MPIIX provides the mechanisms necessary to implement a docking solution that supports both PCI and ISA in the docking station. DMA information is sent across the PCI bus according to the PC/PCI DMA expansion protocol. All ISA IRQx lines are provided. All cycles intended for the MPIIX are positively decoded so that the bus bridge in a docking station can be the subtractive decode agent.

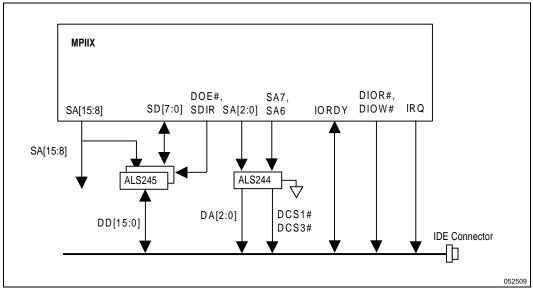

**Fast IDE Interface.** The MPIIX supports one IDE connector on the motherboard (up to 2 devices) and PIO IDE transfers up to 14 Mbytes/sec. The IDE interface has a 2-word write poster and read prefetcher for optimal transfers.

**Plug-n-Play Interface.** The MPIIX provides a Plug-n-Play interface for motherboard devices consisting of 3 steerable DMA channels, 1 steerable interrupt line, and 1 programmable chip select. Each steerable DMA channel supports TYPE F transfers and can use a 4-byte buffer.

**PCI Bus Interface.** The MPIIX provides both a master and slave interface to the PCI bus. As a PCI master, the MPIIX runs cycles on behalf of DMA. As a PCI slave, the MPIIX accepts cycles initiated by PCI masters targeted for the MPIIX's internal register set or the Extended I/O bus. The MPIIX directly supports the PCI Bus running at either 25 MHz or 30 MHz.

**Extended I/O Bus.** The MPIIX incorporates an 8-bit ISA-like interface for motherboard devices such as Multi-Function I/O, Keyboard Controller, Audio Chip, ROM or Flash memory, and a Real Time Clock. MPIIX also includes a 16-bit IDE interface. All cycles to this interface are positively decoded. One programmable Chip Select I/O range, PCS#, and 5 additional programmable I/O ranges are provided for other devices on the Extended I/O bus.

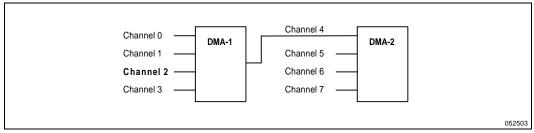

**DMA.** The DMA controller incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Channels [3:0] are hardwired to 8-bit, count by bytes transfers, and channels [7:5] can be programmed to either 16-bit, count by words transfers, or 8-bit transfers. All seven channels support fast DMA type F timings using the steerable DMA channels.

**Timer.** The timer block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These counters provide the system timer function and speaker tone. The 14.31818 MHz oscillator input provides the clock source for the counters.

**Interrupt Controller.** The MPIIX provides an ISA compatible interrupt controller that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and 1 internal interrupts are possible.

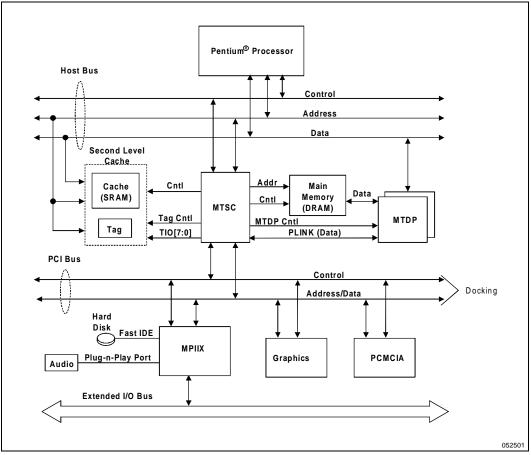

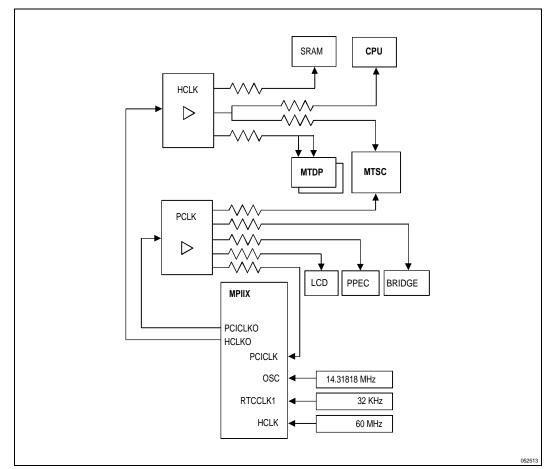

Figure 1. Intel 430MX PCIset PCIset System

### 2.0 SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The '#' symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When '#' is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of 'active-low' and 'active-high' signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

Certain signals are used to drive other signals with different functions through external buffers or transceivers. Both functions have been noted in the descriptions below, with the signal whose function is being described in **bold** font. The actual name given to the pin is the signal driven by MTSC.

The "PCIRST#" column indicates the state of the signals during reset.

The following notations are used to describe the signal type.

- I Input is a standard input-only signal.

- O Totem pole output is a standard active driver.

- o/d Open drain.

- t/s Tri-State is a bi-directional, tri-state input/output pin.

- s/t/s Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. An external pull-up is required to sustain the inactive state until another agent drives it and must be provided by the central resource.

- 3.3V Indicates a standard 3.3V low voltage TTL interface.

- 5/3V Indicates that this signal is normally 5V, but will be powered by the RTC voltage on the VDDR "resume well" power supply pin during the suspend state at normal 3.3 volts.

- pu Internal Pull-Up

- pd Internal Pull-Down

- **bk** Internal Bus Keeper

### 2.1. PCI Interface Signals

| Signal Name | Туре      | PCIRST#   | Description                                                                                                                                                               |

|-------------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | I/O<br>5V | Tri-state | <b>PCI ADDRESS/DATA:</b> The standard PCI address and data lines. The address is driven with FRAME# assertion and data is driven or received in following clocks.         |

| C/BE[3:0]#  | I/O<br>5V | Tri-state | <b>BUS COMMAND AND BYTE ENABLES:</b> The command is driven with FRAME# assertion. Byte enables corresponding to supplied or requested data is driven on following clocks. |

| Signal Name | Туре                 | PCIRST#   | Description                                                                                                                                                                                                                                                                    |

|-------------|----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME#      | I/O<br>(s/t/s)<br>5V | Tri-state | <b>FRAME:</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator. This signal requires a 2.7 K $\Omega$ pullup resistor.                                                                |

| TRDY#       | I/O<br>(s/t/s)<br>5V | Tri-state | <b>TARGET READY:</b> Asserted when the target is ready for a data transfer. This signal requires a 2.7 K $\Omega$ pullup resistor.                                                                                                                                             |

| IRDY#       | I/O<br>(s/t/s)<br>5V | Tri-state | <b>INITIATOR READY:</b> Asserted when the initiator is ready for a data transfer. This signal requires a 2.7 K $\Omega$ pullup resistor.                                                                                                                                       |

| STOP#       | I/O<br>(s/t/s)<br>5V | Tri-state | <b>STOP:</b> Asserted by the target to request the master to stop the current transaction. This signal requires a 2.7 K $\Omega$ pullup resistor.                                                                                                                              |

| IDSEL       | I<br>5V              |           | <b>INITIALIZATION DEVICE SELECT:</b> IDSEL is used as a chip select during configuration read and write transactions.                                                                                                                                                          |

| DEVSEL#     | I/O<br>(s/t/s)<br>5V | Tri-state | <b>DEVICE SELECT:</b> The MPIIX asserts DEVSEL# to claim a PCI transaction through positive decoding. This signal requires a 2.7 K $\Omega$ pullup resistor.                                                                                                                   |

| PAR         | O<br>5V              | Tri-state | <b>CALCULATED PARITY SIGNAL:</b> PAR is "even" parity and is calculated on 36 bits—AD[31:0] plus C/BE[3:0]#.                                                                                                                                                                   |

| SERR#       | I<br>5V              |           | <b>SYSTEM ERROR:</b> SERR# can be pulsed active by any PCI device that detects a system error condition. Upon sampling SERR# active, the MPIIX can be programmed to generate a non-maskable interrupt (NMI) to the CPU. This signal requires a 2.7 K $\Omega$ pullup resistor. |

| PHOLD#      | O<br>5V              | Tri-state | PCI HOLD: The MPIIX asserts this signal to request the PCI Bus.                                                                                                                                                                                                                |

| PHLDA#      | I<br>5∨              |           | <b>PCI HOLD ACKNOWLEDGE:</b> The MTSC asserts this signal to grant the PCI Bus to the MPIIX.                                                                                                                                                                                   |

| REQ[A,B]#   | I<br>5V              |           | <b>REQUEST A AND B:</b> PC/PCI requests for PCI DMA on a dedicated DMA channel or for PC/PCI DMA expansion. These signals should not be used for standard PCI Bus Masters.                                                                                                     |

| GNT[A,B]#   | O<br>5V              | Tri-state | <b>GRANT A AND B:</b> PC/ PCI grants for PCI DMA on a dedicated DMA channel or for PC/PCI DMA expansion. These signals should not be used for standard PCI Bus Masters.                                                                                                        |

| CLKRUN#     | I/O<br>5V            | Tri-state | <b>CLOCK RUN:</b> CLKRUN# is an asynchronous request to start the PCI clock. This signal also indicates PCI clock status.                                                                                                                                                      |

| PCIRST#     | O<br>5V              | Low       | PCI RESET: See System Clock and Reset Signal section.                                                                                                                                                                                                                          |

### 2.2. IDE Interface Signals

| Signal Name                                | Туре                                  | PCIRST#   | Description                                                                                                                                                                                                                                                    |

|--------------------------------------------|---------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DD[15:8]</b> /<br>SA[15:8]/<br>SD[15:8] | <b>I/O</b><br>O<br>5V<br>TTL<br>8mA   | Undefined | <b>DISK DATA</b> : These signals directly drive the corresponding signals on the IDE connector. In addition, these signals are externally buffered to produce the SA[15:8] signals (see separate descriptions).                                                |

| <b>DD[7:0]</b> /<br>SD[7:0]                | <b>I/O</b><br>I/O<br>5V<br>TTL<br>8mA | Tri-state | <b>DISK DATA</b> : These signals directly drive the corresponding signals on the IDE connector. In addition, these signals are externally buffered to produce the SD[7:0] signals (see separate descriptions).                                                 |

| DIOR#                                      | O<br>5V<br>TTL<br>8mA                 | High      | <b>DISK I/O READ</b> : This signal directly drives the corresponding signal on the IDE connector.                                                                                                                                                              |

| DIOW#                                      | O<br>5V<br>TTL<br>8mA                 | High      | <b>DISK I/O WRITE</b> : This signal directly drives the corresponding signal on the IDE connector.                                                                                                                                                             |

| IORDY                                      | l<br>5V<br>pu8KΩ                      |           | <b>IO CHANNEL READY</b> : This input signal is directly driven by the corresponding signal on the IDE connector.                                                                                                                                               |

| <b>DA[2:0]/</b><br>SA[2:0]                 | O<br>5V<br>TTL<br>8mA                 | Undefined | <b>DISK ADDRESS:</b> These address signals directly drive<br>the DA[2:0] signals on the IDE connector and are used to<br>indicate which byte in the ATA command block or control<br>block is being addressed. These pins are multiplexed with<br>SA[2:0].      |

| DCS1#,<br>DCS3# /<br>SA7,SA6               | O<br>5V<br>TTL<br>8mA                 | Undefined | <b>DISK CHIP SELECTS:</b> DCS1# controls the ATA command register block and corresponds to CS1FX# on the IDE connector. DCS3# controls the ATA control register block and corresponds to CS3FX# on the IDE connector. These pins are multiplexed with SA[7,6]. |

| DOE# /<br>SMOUT5                           | O<br>5V<br>TTL<br>4mA                 | High      | <b>DISK OUTPUT ENABLE:</b> This signal controls the OE# of the IDE isolation buffers. SMOUT5 is configured to enable this function via the SMOUT Control Register.                                                                                             |

### 2.3. Extended I/O Bus Signals

| Signal Name                                     | Туре                  | PCIRST#   | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCLK                                          | O<br>5V<br>TTL<br>8mA | Active    | <b>SYSTEM CLOCK:</b> SYSCLK is the reference clock for the Extended I/O Bus and drives the bus directly. SYSCLK is generated by dividing PCICLK by 3 or 4. The SYSCLK frequencies supported are 6.25 MHz, 7.5 MHz and 8.33 MHz. SYSCLK is a divided down version of PCICLK.                                                                                                                        |

|                                                 |                       |           | Hardware strapping option<br>SYSCLK is tri-stated when PWROK is negated. The value of<br>SYSCLK is sampled on the assertion of PWROK: If sampled<br>low, the ISA clock divisor is 3 (for 25 MHz PCI). Otherwise,<br>the divisor is 4 (for 30 MHz PCI). The default value (divide-<br>by-4) is determined by an internal pull-up resistor (50 K $\Omega$ ).<br>This pullup is disabled after reset. |

| IOCHRDY                                         | I<br>5V<br>pu8KΩ      |           | <b>I/O CHANNEL READY:</b> Resources on the Extended I/O Bus<br>negate IOCHRDY to indicate that additional time (wait-states)<br>is required to complete the cycle. This signal is normally high.<br>IOCHRDY is an input when the MPIIX owns the Extended I/O<br>Bus and the CPU or a PCI agent is accessing an Extended<br>I/O slave or during DMA transfers.                                      |

| IOR#                                            | O<br>5V<br>TTL<br>8mA | High      | <b>I/O READ:</b> IOR# is the command to an Extended I/O Bus slave device that the slave may drive data on the Extended I/O data bus (SD[15:0]).                                                                                                                                                                                                                                                    |

| IOW#                                            | O<br>5V<br>TTL<br>8mA | High      | <b>I/O WRITE:</b> IOW# is the command to an Extended I/O Bus slave device that the slave may latch data from the Extended I/O data bus (SD[15:0]).                                                                                                                                                                                                                                                 |

| <b>SA[7:0]</b> ,<br>DCS1#,<br>DCS3#,<br>DA[2:0] | O<br>5V<br>TTL<br>8mA | Undefined | SYSTEM ADDRESS BUS: These address output signals define the selection with the granularity of one byte. For I/O accesses, only SA[15:0] are used. SA[17:0] are outputs during memory cycles to the Extended I/O Bus BIOS range. SA[17:0] are at an unknown state during PCIRST#. SA[15:0]                                                                                                          |

| <b>SA[15:8]/</b><br>DD[15:8]/<br>SD[15:8]       | 0                     | Undefined | are driven to 0 durintg DMA cycles to the Extended I/O Bus.<br>SA[17:16] are driven to 1 following PCIRST# and during DMA<br>cycles to the Extended I/O Bus.                                                                                                                                                                                                                                       |

| <b>SA[17,16]</b> ,<br>PCS#,<br>RTCCS#           | 5V                    | Undefined |                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>SD[15:8]/</b><br>DD[15:8]/<br>SA[15:8]       | I/O<br>5V             | Undefined | <b>SYSTEM DATA BUS:</b> SD[15:8] provide the higher byte of the data path to DMA devices residing on the Extended I/O Bus. SD[15:8] are not available to memory or I/O devices on the Extended I/O Bus.                                                                                                                                                                                            |

| MEMR#                                           | O<br>5V<br>TTL<br>8mA | High      | <b>MEMORY READ:</b> MEMR# is the command to the BIOS memory that it may drive data onto the Extended I/O data bus.                                                                                                                                                                                                                                                                                 |

| Signal Name                 | Туре                             | PCIRST#   | Description                                                                                                                                                                                                                                |

|-----------------------------|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMW#                       | O<br>5V<br>TTL<br>8mA            | High      | <b>MEMORY WRITE:</b> MEMW# is the command to the BIOS memory that it may latch data from the Extended I/O data bus.                                                                                                                        |

| ZEROWS#                     | I<br>5V<br>st<br>pu8KΩ<br>TTL    |           | <b>ZERO WAIT STATES:</b> An Extended I/O Bus slave asserts ZEROWS# after its address and command signals have been decoded to indicate that the current cycle can be shortened. An 8-bit ISA memory cycle can be reduced to three SYSCLKs. |

| <b>SD[7:0]</b> /<br>DD[7:0] | I/O<br>5V<br>pu8KΩ<br>TTL<br>8mA | Tri-state | SYSTEM DATA: SD[7:0] provide the 8-bit data path for devices residing on the Extended I/O Bus. The MPIIX tri-<br>states these signals during PCIRST#.                                                                                      |

| SDIR                        | O<br>5V<br>TTL<br>4mA            | Low       | SYSTEM ADDRESS TRANSCEIVER DIRECTION: This signal controls the direction of the '245 transceivers that interface the DD[15:0] signals to the SA[15:8] and SD[7:0] signals. Default condition is high (transmit).                           |

### 2.4. Motherboard I/O Device Interface Signals

| Signal Name          | Туре                  | PCIRST#   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|-----------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA17/<br><b>PCS#</b> | O<br>5V<br>TTL<br>8mA | Undefined | <b>PROGRAMMABLE CHIP SELECT.</b> PCS# is asserted<br>for Extended I/O Bus I/O cycles that are generated by<br>PCI masters, if the access is in the address range<br>programmed into the PCSC Register. The Extended I/O<br>Bus buffer signals are enabled when the chip select is<br>asserted (i.e., it is assumed that the peripheral that is<br>selected via this pin resides on the Extended I/O Bus).<br>PCS# can be used to control the isolation buffer to the<br>Plug-n-Play port isolation buffer. |

| BIOSCS#              | O<br>5V<br>TTL<br>4mA | Undefined | <b>BIOS CHIP SELECT:</b> BIOSCS# is asserted during read<br>or write accesses to BIOS. BIOSCS# is driven<br>combinatorially from the Extended I/O Bus addresses<br>SA[17:0], except during DMA. During DMA cycles,<br>BIOSCS# is not generated.                                                                                                                                                                                                                                                            |

| KBCS#                | O<br>5V<br>TTL<br>4mA | Undefined | <b>KEYBOARD CONTROLLER CHIP SELECT:</b> KBCS# is<br>asserted during I/O read or write accesses to KBC<br>locations 60h, 62h, 64h, and 66h. For DMA cycles,<br>KBCS# is never asserted.                                                                                                                                                                                                                                                                                                                     |

| SA16/<br>RTCCS#      | O<br>5V<br>TTL<br>8mA | Undefined | <b>REAL TIME CLOCK CHIP SELECT:</b> RTCCS# is asserted during read or write accesses to RTC location 71h, 73h, 75h, and 77h. RTCCS# can be tied to a pair of external OR gates to generate the real time clock read and write command signals.                                                                                                                                                                                                                                                             |

| Signal Name       | Туре                  | PCIRST# | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTCALE/<br>SMOUT4 | O<br>5V<br>TTL<br>4mA | High    | <b>REAL TIME CLOCK ADDRESS LATCH:</b> RTCALE is<br>used to latch the appropriate memory address into the<br>RTC. A write to port 70h, 72h, 74h, or 76h with the<br>appropriate RTC memory address that will be written to<br>or read from, causes RTCALE to be asserted. RTCALE<br>is asserted based on IOW# falling and remains asserted<br>for two SYSCLKs.                                                                                                                                                                                                                                                               |

| SPKR              | O<br>5V<br>TTL<br>8mA | Low     | <b>SPEAKER DRIVE:</b> The SPKR signal is the output of counter 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OSC               | I<br>5V<br>TTL        |         | <b>OSCILLATOR:</b> OSC is the 14.31818 MHz ISA clock signal. It is used by the internal 8254 Timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FERR#             | I<br>3.3V<br>pu50KΩ   |         | NUMERIC COPROCESSOR ERROR: This signal is tied<br>to the coprocessor error signal on the CPU. IGNNE# is<br>only used if the MPIIX coprocessor error reporting<br>function is enabled in the FDC Enable Register. If<br>FERR# is asserted, the MPIIX generates an internal<br>IRQ13 to its interrupt controller unit. The MPIIX then<br>asserts the INTR output to the CPU. FERR# is also used<br>to gate the IGNNE# signal to ensure that IGNNE# is not<br>asserted to the CPU unless FERR# is active. FERR#<br>has a weak internal pull-up used to ensure a high level<br>when the coprocessor error function is disabled. |

| IGNNE#            | od<br>3.3V            | High    | IGNORE ERROR: This signal is connected to the ignore<br>error pin on the CPU. IGNNE# is only used if the MPIIX<br>coprocessor error reporting function is enabled in the<br>FDC Enable Register. If FERR# is asserted, indicating a<br>coprocessor error, a write to the Coprocessor Error<br>Register (F0h) causes the IGNNE# to be asserted.<br>IGNNE# remains asserted until FERR# is negated. If<br>FERR# is not asserted when the Coprocessor Error<br>Register is written, the IGNNE# signal is not asserted.                                                                                                         |

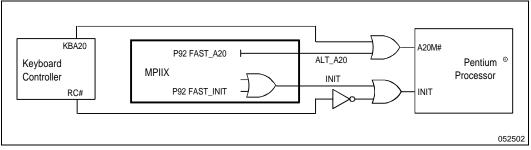

| ALTA20M           | O<br>5V<br>TTL<br>4mA | Low     | Alternative A20 MASK: This MPIIX output is externally OR'd with the A20gate from the KBC to generate A20M# to the CPU. A20M# is used to emulate the 1 Mbyte wrap-around.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

##

### 2.5. DMA Signals

| Signal Name            | Туре                         | PCIRST#   | Description                                                                                                                                                                                                                                                                                                |

|------------------------|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDRQ[2:0]/<br>EXTEVNT# | l<br>5V<br>pd50K<br>Ω        |           | <b>MOTHERBOARD DEVICE DMA REQUEST:</b> These signals can be connected internally to any of DREQ[3:0,7:5]. Each pair of request/acknowledge signals is controlled by a separate register.                                                                                                                   |

| MDAK[2:0]#/<br>PAD#    | O<br>5V<br>4mA               | High      | <b>MOTHERBOARD DEVICE DMA ACKNOWLEDGE:</b><br>These signals can be connected internally to any of<br>DACK[3:0,7:5]. Each pair of request/acknowledge<br>signals is controlled by a separate register. MDAK1 or<br>MDAK2 or both can be enabled to re-load the Local<br>Standby Timer for the audio device. |

| DREQ2                  | l<br>5V<br>pu50K<br>Ω<br>TTL |           | <b>DMA REQUEST 2:</b> DREQ2 is used by the floppy disk controller to request DMA service from the MPIIX's DMA controller. All inactive to active edges are assumed to be asynchronous. The request must remain active until the appropriate DACK2# signal is asserted.                                     |

| DACK2#                 | O<br>5V<br>TTL<br>4mA        | High      | <b>DMA ACKNOWLEDGE 2:</b> DACK2# indicates that a request for DMA service has been granted by the MPIIX. This line should be used to decode the DMA slave device with the IOR# or IOW# line to indicate selection.                                                                                         |

| TC                     | O<br>5V<br>TTL<br>4mA        | Tri-state | <b>TERMINAL COUNT:</b> The MPIIX asserts TC to DMA slaves as a terminal count indicator. MPIIX asserts TC after a new address has been output, if the byte count expires with that transfer. When all the DMA channels are not in use, TC is negated (low).                                                |

### 2.6. Interrupt Controller Signals

| Signal Name               | Туре                    | PCIRST# | Description                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|-------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ[15,14,<br>11:9,7:3,1] | I<br>5V<br>pu8KΩ<br>TTL |         | <b>INTERRUPT REQUEST:</b> The IRQ signals provide both system board components and docking station Extended I/O Bus I/O devices with a mechanism for asynchronously interrupting the CPU. The assertion mode of these inputs depends on the programming of the two ELCR Registers.                                                                          |

|                           |                         |         | IRQ1 (as well as IRQ[8#,2,0] and the internal IRQ13) are not<br>programmable through the ELCR Registers. These IRQs are<br>always active high edge triggered. An internal flip-flop latches<br>a low-to-high transition on IRQ1. The MPIIX continues to<br>generate an internal IRQ1 to the 8259 core until a PCIRST#<br>or an I/O read access to port 60h. |

|                           |                         |         | An active IRQ input must remain asserted until after the interrupt is acknowledged. If the IRQ is negated before this time, a DEFAULT IRQ7 occurs when the CPU acknowledges the interrupt.                                                                                                                                                                  |

| Signal Name | Туре                       | PCIRST# | Description                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ8#       | I<br>5/3V<br>pu8KΩ<br>CMOS |         | <b>INTERRUPT REQUEST EIGHT SIGNAL:</b> IRQ8# is always<br>an active low edge triggered interrupt input (i.e. this interrupt<br>can not be modified by software). This signal is monitored by<br>the low power 'Resume Well' circuitry during suspend.                                                                                                |

|             |                            |         | IRQ8# must remain asserted until after the interrupt is acknowledged. If the input goes inactive before this time, a DEFAULT IRQ7 will occur when the CPU acknowledges the interrupt.                                                                                                                                                                |

| IRQ12/M     | I<br>5V<br>pu8KΩ<br>TTL    |         | <b>INTERRUPT REQUEST / MOUSE INTERRUPT:</b> In addition to providing the standard interrupt function (see IRQ[15,14,11:9,7:3,1] signal description), this pin can be programmed (via the FDC Enable Register) to provide a mouse interrupt function.                                                                                                 |

|             |                            |         | When the mouse interrupt function is selected, a low-to-high transition on this signal is latched by the MPIIX and an INTR is generated to the CPU as IRQ12. An internal IRQ12 interrupt continues to be generated until a PCIRST# or an I/O read access to address 60h. After a PCIRST#, this signal provides the standard IRQ12 function.          |

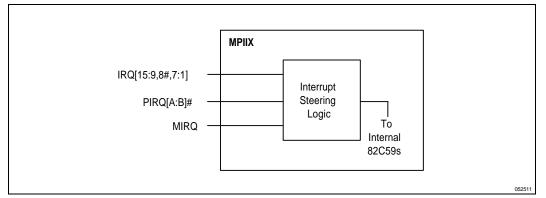

| MIRQ        | l<br>5V                    |         | <b>MOTHERBOARD DEVICE INTERRUPT REQUEST</b> : The MIRQ signal can be internally connected to interrupts IRQ[15,14,12:9,7:3]. If MIRQ line and PIRQx# are steered to the same interrupt, the device connected to the MIRQx should produce active high, level interrupts.                                                                              |

|             |                            |         | If the MIRQ line is steered to a given IRQ input to the internal 8259, the corresponding IRQ is masked, unless the Route Control register is programmed to allow the interrupts to be shared. This should only be done if the device connected to the MIRQ line and the device connected to the IRQ line both produce active high, level interrupts. |

| PIRQ[A,B]#  | l<br>5V<br>pu8KΩ<br>TTL    |         | <b>PROGRAMMABLE INTERRUPT REQUEST:</b> The PIRQx# signals can be shared with interrupts IRQ[15,14,12:9,7:3] as described in the Interrupt Steering section. Each PIRQx# line has a separate Route Control Register.                                                                                                                                  |

| INTR        | O<br>3.3V<br>TTL<br>4mA    | Low     | <b>CPU INTERRUPT:</b> INTR is driven by the MPIIX to signal the CPU that an interrupt request is pending and needs to be serviced. The interrupt controller must be programmed following PCIRST# to ensure that INTR is at a known state.                                                                                                            |

| NMI         | od<br>3.3V<br>TTL<br>4mA   |         | <b>NON-MASKABLE INTERRUPT:</b> NMI is used to force a non-<br>maskable interrupt to the CPU. The MPIIX generates an NMI<br>when SERR# is asserted, depending on how the NMI Status<br>and Control Register is programmed.                                                                                                                            |

### 2.7. System Power Management (SMM) Signals

| Signal Name                            | Туре                        | PCIRST#                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI#                                   | O<br>3.3V<br>TTL<br>4mA     | High                                                                                                                                                                                                                  | SYSTEM MANAGEMENT INTERRUPT: SMI# is an active low synchronous output that is asserted by the MPIIX in response to one of many enabled hardware or software events. During CPU Reset (INIT and CPURST), this signal is negated.                                                                                                                                                                                                      |

| STPCLK#                                | O<br>3.3V<br>TTL<br>4mA     | High STOP CLOCK: STPCLK# is an active low synchronous output that is asserted by the MPIIX in response to one of many hardware or software events. STPCLK# connects directly to the CPU and is synchronous to PCICLK. |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SUSTAT#                                | O<br>5/3V<br>CMOS<br>4mA    | High                                                                                                                                                                                                                  | <b>SUSPEND STATUS:</b> This output signal is used to switch off power to all non-critical devices during suspend. Activation of this signal is typically the last step in the SMM code.                                                                                                                                                                                                                                              |

| SYSACT#                                | I<br>5V<br>pu50KΩ<br>TTL    |                                                                                                                                                                                                                       | <b>SYSTEM ACTIVITY:</b> This input signal can be used by system devices such as bridge chips to indicate system activity that is not visible to the MPIIX power management logic. This signal, if enabled through setup software, can be used by MPIIX to prevent the system from entering an idle state.                                                                                                                            |

| SRBTN#                                 | I<br>5/3V<br>CMOS           |                                                                                                                                                                                                                       | SUSPEND RESUME BUTTON: This signal can be<br>enabled to generates an SMI# request. SRBTN# is<br>monitored by the low power "Resume Well" circuitry<br>during suspend. This signal must always be driven to a<br>valid logic level.                                                                                                                                                                                                   |

| BATLOW#                                | I<br>5/3V<br>CMOS           |                                                                                                                                                                                                                       | <b>BATTERY LOW:</b> BATLOW# Indicates that battery power is low. Assertion of this signal triggers an SMI, if enabled. This signal is monitored by the low power "Resume Well" circuitry during suspend. MPIIX can be programmed to prevent a resume operation when the BATLOW# signal is active. This signal must always be driven to a valid logic level. Once asserted, this signal must remain asserted until SMI# is generated. |

| RSMRST#                                | I<br>5/3V<br>CMOS           |                                                                                                                                                                                                                       | <b>RESUME RESET:</b> This signal acts as a reset to the low power "Resume Well" circuitry. This signal must always be driven to a valid logic level.                                                                                                                                                                                                                                                                                 |

| <b>SMOUT[5:0]</b> /<br>DOE#,<br>RTCALE | O<br>5V<br>TTL<br>4mA       | High                                                                                                                                                                                                                  | SYSTEM MANAGEMENT OUTPUT ENABLES: These<br>six programmable outputs can be connected to control<br>the power circuits for various devices in the system.<br>SMOUT5 can be configured to generate a DISK Output<br>Enable. SMOUT4 can be configured to generate<br>RTCALE.                                                                                                                                                            |

| COMRI#                                 | I<br>5/3V<br>pu50KΩ<br>CMOS |                                                                                                                                                                                                                       | <b>COM RING INDICATE:</b> A modem connected to the COM port will asserts this signal to wake up a suspended system. This signal is monitored by the low power "Resume Well" circuitry during suspend.                                                                                                                                                                                                                                |

| Signal Name        | Туре                             | PCIRST# | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|----------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTSMI#            | I<br>st<br>5/3V<br>pu8KΩ<br>CMOS |         | EXTERNAL SYSTEM MANAGEMENT INTERRUPT:<br>EXTSMI# is a falling edge triggered input to the MPIIX<br>indicating that an external device is requesting the<br>system to enter SMM mode. When enabled, a low level<br>on EXTSMI# will result in the assertion of the SMI#<br>signal. EXTSMI# is an asynchronous input and should<br>be asserted for a minimum of 32 µsec.                                                                                                                                                                            |

| EXTEVNT#/<br>MDRQ2 | l<br>5V<br>pd50KΩ<br>TTL         |         | <b>EXTERNAL EVENT (EXTEVNT#):</b> The EXTEVNT#<br>signal allows events detected by the external logic to be<br>used as BSTCLK Events or CLKTHL Break Events.<br>MDRQ[2] is multiplexed with the EXTEVNT# signal. A<br>confguration bit selects which signal is enabled on the<br>pin. The power on default is the MDRQ[2] signal.                                                                                                                                                                                                                |

| PAD# /<br>MDAK2#   | O<br>5V<br>TTL<br>4mA            | High    | <b>Peripheral Access Decode:</b> The PAD# signal is<br>asserted by the MPIIX when a PCI memory or I/O<br>address is decoded to be in the same address range as<br>defined by the Peripheral Access Detect Tables and<br>enabled in the Peripheral Access Decode Enable<br>register. MPIIX does not have to be the target of the PCI<br>cycle for the PAD# signal to be asserted. MDAK2# is<br>multiplexed with the PAD# signal. A configuration bit<br>selects which signal is enabled on the pin. The power on<br>default is the MDAK2# signal. |

### 2.8. System Clock And Reset Signals

| Signal Name | Туре                    | PCIRST# | Description                                                                                                                                                                                                                                                |

|-------------|-------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK        | I<br>5V<br>TTL          |         | <b>HOST CLOCK:</b> Main system clock used to create clocks for PCI, MTSC, MTDP, and external cache.                                                                                                                                                        |

| PCICLK      | I<br>5V<br>TTL          |         | <b>PCI CLOCK:</b> PCICLK provides timing for all transactions on the PCI Bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge. PCI frequencies of 25–33 MHz are supported. |

| HCLKO       | O<br>3.3V<br>TTL<br>4mA | Active  | <b>HOST CLOCK OUT:</b> Must be buffered to provide CPU, MTSC, TDP, and external L2 cache clocks.                                                                                                                                                           |

| PCICLKO     | O<br>5V<br>TTL<br>4mA   | Active  | <b>PCI CLOCK OUTPUT:</b> Synchronous divide-by-2 of HCLK. Must be buffered to provide fully loadable PCI clock.                                                                                                                                            |

| RTCCLK      | I<br>5/3V<br>CMOS       |         | REAL TIME CLOCK INPUT.                                                                                                                                                                                                                                     |

##

| Signal Name | Туре                     | PCIRST#                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|--------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTCCLKO     | O<br>5/3V<br>CMOS<br>4mA | Active <b>REAL TIME CLOCK OUTPUT:</b> Gated RTCCLK to MTSC for suspend refresh operation. |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYSCLK      | O<br>5V                  |                                                                                           | SYSTEM CLOCK: See Extended I/O Bus Interface Section.                                                                                                                                                                                                                                                                                                                                                                                             |

| PWROK       | I<br>5/3V<br>st<br>CMOS  |                                                                                           | <b>POWER OK:</b> When asserted, PWROK is an indication to the MPIIX that power and PCICLK have been stable for at least 1 ms. PWROK can be driven asynchronously. When PWROK is negated, the MPIIX asserts CPURST, PCIRST# and RSTDRV. When PWROK is asserted, the MPIIX negates CPURST, PCIRST#, and RSTDRV.                                                                                                                                     |

| CPURST      | O<br>3.3V<br>TTL<br>4mA  | High                                                                                      | <b>CPU RESET:</b> The MPIIX asserts CPURST to reset the CPU. The MPIIX asserts CPURST during power-up and when a hard reset sequence is initiated through the RC Register. CPURST is driven synchronously to the rising edge of PCICLK. If a hard reset is initiated through the RC register, the MPIIX resets it's internal registers to the default state.                                                                                      |

| PCIRST#     | 0<br>5V                  | Low                                                                                       | <b>PCI RESET:</b> The MPIIX asserts PCIRST# to reset<br>devices that reside on the PCI Bus. The MPIIX asserts<br>PCIRST# during power-up and when a hard reset<br>sequence is initiated through the RC Register. PCIRST#<br>is driven inactive a minimum of 1ms after PWROK is<br>driven active. PCIRST# is driven active for a minimum of<br>1ms when initiated through the RC Register. PCIRST#<br>is driven asynchronously relative to PCICLK. |

| INIT        | O<br>3.3V<br>TTL<br>4mA  | High                                                                                      | <b>INITIALIZATION:</b> The MPIIX asserts INIT if it detects a shut down special cycle on the PCI Bus or if a soft reset is initiated via the RC Register (0CF9h).                                                                                                                                                                                                                                                                                 |