### 18-Bit 3.3V Registered Buffer

#### **Recommended Applications:**

- PC133 Registered Memory Module

- PC motherboards

- Servers and workstations

- Provides complete PC133 DIMM solution with ICS2509, ICS2510 PLL.

#### **Product Features:**

- · Meets JESD 82-2 specification

- Internal series resistors to reduce switching noise

- ±12 mA device capability

- · Low voltage operation

- $-V_{DD} = 3.3 \pm 0.3V$

- · 0.50 mm pitch, 56-Pin TSSOP package

### Function Table<sup>1</sup>

|     | Inputs |     |    |                               |  |

|-----|--------|-----|----|-------------------------------|--|

| OE# | LE     | CLK | Ax | Yx                            |  |

| Н   | Х      | Х   | Х  | Z                             |  |

| L   | Н      | Х   | L  | L                             |  |

| L   | Н      | Х   | Н  | Н                             |  |

| L   | L      | 1   | L  | L                             |  |

| L   | L      | 1   | Н  | Н                             |  |

| L   | L      | Н   | Х  | Y <sub>0</sub> <sup>(2)</sup> |  |

| L   | L      | L   | Х  | Y <sub>0</sub> (3)            |  |

#### Notes:

- H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- Z = High-Impedance ↑ = LOW-to-HIGH Transition

- Output level before the indicated steady-state 2. input conditions were established, provided that CLK is HIGH before LE went LOW.

- Output level before the indicated steady-state 3. input conditions were established.

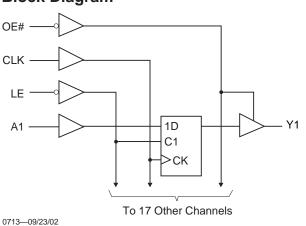

### **Block Diagram**

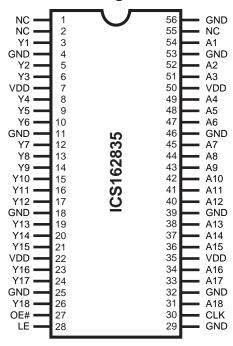

### **Pin Configurations**

56-Pin TSSOP 6.10 mm. Body, 0.50 mm. pitch

### **Pin Description**

| Pin Names       | Description                      |

|-----------------|----------------------------------|

| OE#             | Output Enable Input (Active Low) |

| CLK             | Clock Input                      |

| LE              | Latch Enable Input               |

| Ax              | Data Input                       |

| Yx              | Data Outputs                     |

| V <sub>DD</sub> | Supply Voltage                   |

| GND             | Ground                           |

### ICS162835

### **Advance Information**

### **General Description**

The ICS162835 low voltage 18-bit register combines D-type latches and D-type flip-flops to allow data flow in transparent, latched and clocked modes. Date flow is controlled by output-enable (OE#), latch enable (LE), and clock (CLK) inputs. The device operates in transparent mode when LE is held high. The device operates in clocked mode when LE is low and CLK is toggled. Data transfers from the inputs (A[18:1]) to outputs (Y[18:1]) on a positive edge transition of the clock. When OE# is low, the output state is enabled. When OE# is high, the output port is in a high impedance state.

The 18-bit registered buffer is designed to operate with a 3.0V to 4.6V supply voltage.

All inputs support operation with standard LVTTL interface levels. This includes data inputs, clock inputs and control inputs. Device outputs meet the requirements of the PC133 Registered DIMM specification. The device functions as defined supports latched, registered and flow through modes of operations. The PC133 Specification requires only registered mode.

Package is a 56 thin shrink small-outline package as defined by JEDEC Publication, JEP95, MO-153.

# ICS162835 Advance Information

### **Absolute Maximum Ratings**

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

**Recommended Operating Conditions**

| PARAMETER        | DESCRIPTION                    |                 | MIN  | TYP | MAX      |

|------------------|--------------------------------|-----------------|------|-----|----------|

| $V_{DD}$         | Supply Voltage                 |                 | 3.0  | 3.3 | 3.6      |

| $V_{IN}$         | Voltage Applied to input pins  |                 | -0.3 |     | 3.6      |

|                  | Voltage Applied to             | Outputs enabled | 0    |     | $V_{DD}$ |

| V <sub>OUT</sub> | output or I/O pins             | Outputs high-Z  | 0    |     | $V_{DD}$ |

| T <sub>A</sub>   | Operating free-air temperature |                 | 0    |     | 70       |

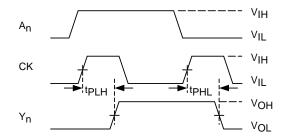

**Switching Characteristics**

| Cumb al                             | Dorometer                   | $V_{CC} = 3.3$ | LIMITO |       |

|-------------------------------------|-----------------------------|----------------|--------|-------|

| Symbol                              | Parameter                   | MIN            | MAX    | UNITS |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay CLK to Yx | 1.8            | 3.5    | ns    |

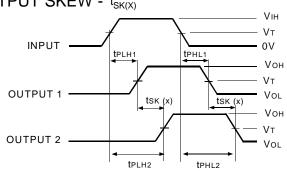

| t <sub>SK(0)</sub>                  | Output Skew*                | -              | 500    | ps    |

| f <sub>CLOCK</sub>                  |                             | 150            | -      | MHz   |

<sup>\*</sup> Skew between any two putputs of the same package and switching in the same direction

### ICS162835

### **Advance Information**

### **Electrical Characteristics - DC**

$T_A = 0 - 70^{\circ} \text{ C}$ ;  $V_{DD} = 3.3 \pm 0.3 \text{ V}$ ,  $V_{DDQ} = 3.3 \pm 0.3 \text{ V}$ ; (unless otherwise stated)

| SYMBOL          | PARAMETERS                | CONDITIONS                                       | V <sub>DD</sub> (V) | MIN | TYP | MAX | UNITS |

|-----------------|---------------------------|--------------------------------------------------|---------------------|-----|-----|-----|-------|

| $V_{IH}$        | HIGH-level input voltage  |                                                  | 3.0 - 3.6           | 2.0 |     |     | V     |

| $V_{IL}$        | LOW-level input voltage   |                                                  | 3.0 - 3.6           |     |     | 0.8 | V     |

| V <sub>OH</sub> | HIGH-level output voltage | $I_{OH} = -12 \text{ mA}, V_{IH} = 2.0 \text{V}$ | 3.0                 | 2.2 |     |     | V     |

| $V_{OL}$        | Low-level output voltage  | $I_{OL} = 12 \text{ mA}, V_{IL} = 0.8 \text{V}$  | 3.0                 |     |     | 0.8 |       |

| $I_1$           | Input leakage current     | $V_I = V_{DD}$ or GND                            | 3.0 - 3.6           |     |     | ±10 | μΑ    |

| I <sub>OZ</sub> | Off-state leakage current | $V_O = V_{DD}$ or GND#, OE = $V_{DD}$            |                     |     |     | ±20 | μA    |

| I <sub>DD</sub> | Quiescent Supply Current  | $V_I = V_{DD}$ or GND, $I_O = 0$                 |                     |     |     | ±40 | μА    |

<sup>\*</sup> Parameters are characterized over recommended operating conditions.

**Critical Register Specifications\***

| SYMBOL             | PARAMETERS                  | CONDITION                       | V <sub>DD</sub> (V) | MIN | TYP | MAX | UNITS |

|--------------------|-----------------------------|---------------------------------|---------------------|-----|-----|-----|-------|

| t <sub>PD</sub> ** | Propagation Delay (CK to Y) | $R_L = 500 \Omega, C_L = 50 pF$ | 3.0 - 3.6           | 1.4 |     | 3.5 | ns    |

| t <sub>PD</sub> ** | Propagation Delay (CK to Y) | $R_L = 500 \Omega, C_L = 30 pF$ | 3.0 - 3.6           | 0.7 |     | 2.5 | ns    |

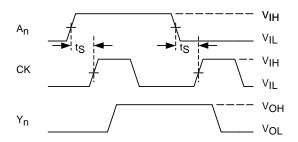

| ts                 | Setup time (A before CK)    |                                 | 3.0 - 3.6           | 1.0 |     |     | ns    |

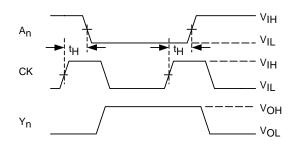

| t <sub>H</sub>     | Hold time (A after CK)      |                                 | 3.0 - 3.6           | 0.6 |     |     | ns    |

| Cı                 | Clock input capacitance     |                                 | 3.0 - 3.6           | 3.3 | 4.0 | 6.0 | pF    |

<sup>\*</sup> Parameters are characterized over recommended operating conditions.

<sup>\*\*</sup> The t<sub>PD</sub> value in this table would equate to the 'Time-to-Vm' delay described in the post register timing specifications of the PC133 registered DIMM Specification. The first value applies to DIMMs with nine SDRAM loads per register output, and the second to DIMMs with eighteen SDRAM loads per register output. These values should serve as only an initial starting point,

## ICS162835 Advance Information

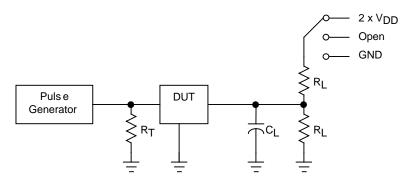

### Test Circuit and Switching Waveforms

**Test Circuit**

Test circuit component values:

$R_L$  = Load Resistor = 500  $\Omega$

C<sub>L</sub> = Load Capacitance and includes probe and jig capacitance

$R_T$  = Termination resistance should be equal to  $Z_{OUT}$  of Pulse Generator

$V_{IN} = 0$  to  $V_{DD}$

$t_r = t_f$  2.0 ns (10% to 90%) unless otherwise specified.

| Parameter Tested | Switch Position     |

|------------------|---------------------|

| t <sub>PLH</sub> | Open                |

| t <sub>PHL</sub> | Open                |

| t <sub>PZH</sub> | GND                 |

| t <sub>PZL</sub> | 2 x V <sub>DD</sub> |

| t <sub>PHZ</sub> | GND                 |

| t <sub>PLZ</sub> | 2 x V <sub>DD</sub> |

### ICS162835

### **Advance Information**

### PROPAGATION DELAY MEASUREMENT

### SETUP TIME MEASUREMENTS

### HOLD TIME MEASUREMENTS

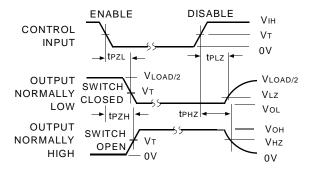

### ENABLE AND DISABLE TIMES

#### NOTE

Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

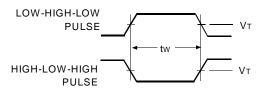

## OUTPUT SKEW - t<sub>SK(X)</sub> PULSE

tsk(x) = |tplh2 - tplh1| or |tphl2 - tphl1|

### PULSE WIDTH

#### NOTES:

- 1. For tsk(o) OUTPUT1 and OUTPUT2 are any two outputs.

- 2. For tsk(b) OUTPUT1 and OUTPUT2 are in the same bank.

Switching Waveforms

0713-09/23/02

# ICS162835 Advance Information

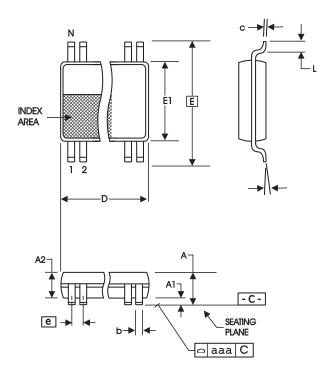

6.10 mm. Body, 0.50 mm. pitch TSSOP (240 mil) (0.020 mil)

|        | In Millimeters |            | In Inches      |           |  |

|--------|----------------|------------|----------------|-----------|--|

| SYMBOL | COMMON DI      | MENSIONS   | COMMON D       | IMENSIONS |  |

|        | MIN            | MAX        | MIN            | MAX       |  |

| Α      |                | 1.20       |                | .047      |  |

| A1     | 0.05           | 0.15       | .002           | .006      |  |

| A2     | 0.80           | 1.05       | .032           | .041      |  |

| b      | 0.17           | 0.27       | .007           | .011      |  |

| С      | 0.09           | 0.20       | .0035          | .008      |  |

| D      | SEE VARIATIONS |            | SEE VARIATIONS |           |  |

| Е      | 8.10 B         | 8.10 BASIC |                | BASIC     |  |

| E1     | 6.00           | 6.20       | .236           | .244      |  |

| е      | 0.50 B         | ASIC       | 0.020 E        | BASIC     |  |

| L      | 0.45           | 0.75       | .018           | .030      |  |

| N      | SEE VAR        | IATIONS    | SEE VAR        | RIATIONS  |  |

| α      | 0°             | 8°         | 0°             | 8°        |  |

| aaa    |                | 0.10       | 004            |           |  |

#### 'ARIATIONS

| N    | D m   | ım.   | D (inch) |      |

|------|-------|-------|----------|------|

| I IN | MIN   | MAX   | MIN      | MAX  |

| 56   | 13.90 | 14.10 | .547     | .555 |

Reference Doc.: JEDEC Publication 95, M O-153

10-0039

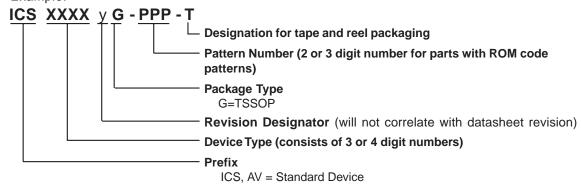

### **Ordering Information**

### ICS162835AG-T

0713-09/23/02