# LM5112 Tiny 7A MOSFET Gate Driver General Description

The LM5112 MOSFET gate driver provides high peak gate drive current in the tiny LLP-6 package (SOT23 equivalent footprint) with improved package power dissipation required for high frequency operation. The compound output driver stage includes MOS and bipolar transistors operating in parallel that together sink more than 7A peak from capacitive loads. Combining the unique characteristics of MOS and bipolar devices reduces drive current variation with voltage and temperature. Under-voltage lockout protection is provided to prevent damage to the MOSFET due to insufficient gate turn-on voltage. The LM5112 provides both inverting and non-inverting inputs to satisfy requirements for inverting and non-inverting gate drive with a single device type.

#### Features

- Compound CMOS and bipolar outputs reduce output current variation

- 7A sink/3A source current

- Fast propagation times (25 ns typical)

- Fast rise and fall times (14 ns/12 ns rise/fall with 2 nF load)

- Inverting and non-inverting inputs provide either configuration with a single device

- Supply rail under-voltage lockout protection

- Dedicated input ground (IN\_REF) for split supply or single supply operation

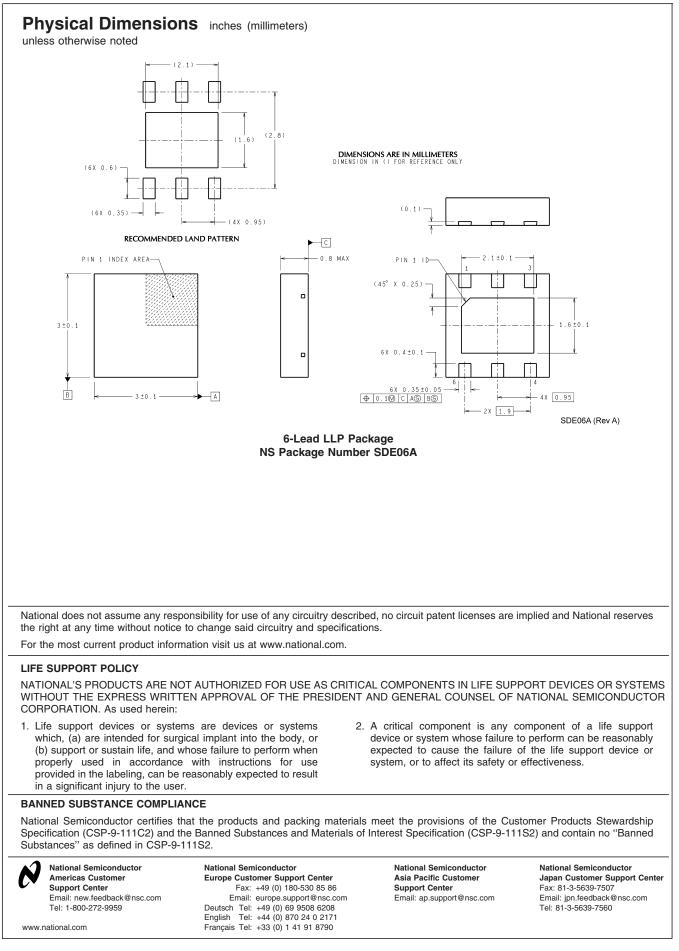

- Power Enhanced 6-pin LLP package (3.0mm x 3.0mm)

- Output swings from V<sub>CC</sub> to V<sub>EE</sub> which can be negative relative to input ground

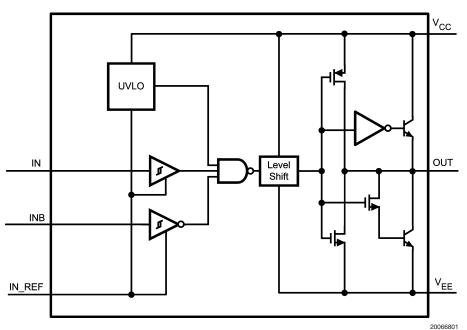

### **Block Diagram**

#### Block Diagram of LM5112

LM5112

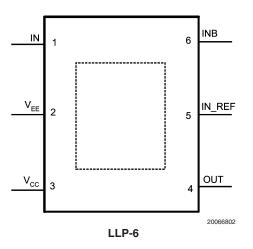

# Pin Configurations

## **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplied As                 |

|--------------|--------------|---------------------|-----------------------------|

| LM5112-SD    | LLP-6        | SDE06A              | 1000 shipped in Tape & Reel |

| LM5112-SDX   | LLP-6        | SDE06A              | 4500 shipped in Tape & Reel |

## **Pin Description**

| Pin  | Name                                            | Description                     | Application Information                                         |  |  |

|------|-------------------------------------------------|---------------------------------|-----------------------------------------------------------------|--|--|

| 1 IN |                                                 | Non-inverting input pin         | TTL compatible thresholds. Pull up to $V_{CC}$ when             |  |  |

|      |                                                 |                                 | not used                                                        |  |  |

| 2    | V <sub>EE</sub>                                 | Power ground for driver outputs | Connect to either power ground or a negative                    |  |  |

|      |                                                 |                                 | gate drive supply for positive or negative voltage              |  |  |

|      |                                                 |                                 | swing                                                           |  |  |

| 3    | 3 V <sub>CC</sub> Positive Supply voltage input |                                 | Locally decouple to V <sub>EE</sub> . The decoupling capaci     |  |  |

|      |                                                 |                                 | should be located close to the chip                             |  |  |

| 4    | OUT                                             | Gate drive output               | Capable of sourcing 3A and sinking 7A. Voltage                  |  |  |

|      |                                                 |                                 | swing of this output is from $V_{\text{EE}}$ to $V_{\text{CC}}$ |  |  |

| 5    | IN_REF                                          | Ground reference for control    | Connect to power ground (V <sub>EE</sub> ) for standard         |  |  |

|      |                                                 | inputs                          | positive only output voltage swing. Connect to                  |  |  |

|      |                                                 |                                 | system logic ground when V <sub>EE</sub> is connected to a      |  |  |

|      |                                                 |                                 | negative gate drive supply                                      |  |  |

| 6    | INB                                             | Inverting input pin             | TTL compatible thresholds. Connect to IN_REF                    |  |  |

|      |                                                 |                                 | when not used                                                   |  |  |

|      | Exposed                                         | Exposed Pad, underside of LLP   | Internally bonded to the die substrate. Connect to              |  |  |

|      | Pad                                             | package                         | V <sub>EE</sub> ground pin for low thermal impedance            |  |  |

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| $V_{CC}$ to $V_{EE}$      | –0.3V to 15V |

|---------------------------|--------------|

| V <sub>CC</sub> to IN_REF | –0.3V to 15V |

| IN/INB to IN_REF          | –0.3V to 15V |

IN\_REF to V<sub>FF</sub> -0.3V to 5V Storage Temperature Range -55°C to +150°C Maximum Junction Temperature +150°C **Operating Junction Temperature** -40°C+125°C ESD Rating

2kV

## Electrical Characteristics T<sub>J</sub> = -40°C to +125°C, V<sub>CC</sub> = 12V, INB = IN\_REF = V<sub>EE</sub> = 0V, No Load on out-

put, unless otherwise specified.

| SYMBOL            | PARAMETER                                                              | CONDITIONS                                      | MIN | ТҮР  | MAX | UNITS |

|-------------------|------------------------------------------------------------------------|-------------------------------------------------|-----|------|-----|-------|

| SUPPLY            |                                                                        |                                                 |     |      | 1   |       |

| V <sub>cc</sub>   | V <sub>CC</sub> operating range                                        | $V_{CC}$ – IN_REF and $V_{CC}$ - $V_{EE}$       | 3.5 |      | 14  | V     |

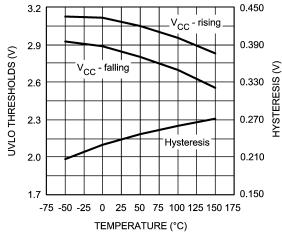

| UVLO              | V <sub>CC</sub> Under-voltage lockout (rising)                         | V <sub>CC</sub> – IN_REF                        | 2.4 | 3.0  | 3.5 | V     |

| V <sub>CCH</sub>  | V <sub>CC</sub> Under-voltage hysteresis                               |                                                 |     | 230  |     | mV    |

| I <sub>cc</sub>   | V <sub>CC</sub> supply current                                         |                                                 |     | 1.0  | 2.0 | mA    |

| CONTROL           | INPUTS                                                                 |                                                 |     |      |     |       |

| V <sub>IH</sub>   | Logic High                                                             |                                                 |     | 1.75 | 2.3 | V     |

| V <sub>IL</sub>   | Logic low                                                              |                                                 | 0.8 | 1.35 |     | V     |

| HYS               | Input Hysteresis                                                       |                                                 |     | 400  |     | mV    |

| I <sub>IL</sub>   | Input Current Low                                                      | IN = INB = 0V                                   | -1  | 0.1  | 1   | μA    |

| I <sub>IH</sub>   | Input Current High                                                     | $IN = INB = V_{CC}$                             | -1  | 0.1  | 1   | μA    |

| OUTPUT [          | DRIVER                                                                 |                                                 |     | •    |     |       |

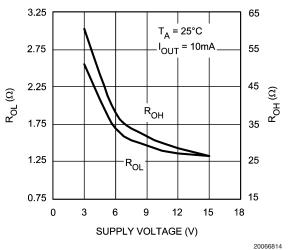

| R <sub>OH</sub>   | Output Resistance High                                                 | I <sub>OUT</sub> = -10mA                        |     | 30   | 50  | Ω     |

| R <sub>OL</sub>   | Output Resistance Low                                                  | I <sub>OUT</sub> = 10mA                         |     | 1.4  | 2.5 | Ω     |

| ISOURCE           | Peak Source Current                                                    | OUT = V <sub>CC</sub> /2, 200ns pulsed current  |     | 3    |     | A     |

| I <sub>sink</sub> | Peak Sink Current                                                      | OUT = V <sub>CC</sub> /2, 200ns pulsed current  |     | 7    |     | A     |

| SWITCHIN          | G CHARACTERISTICS                                                      | 1                                               |     | 1    |     | 1     |

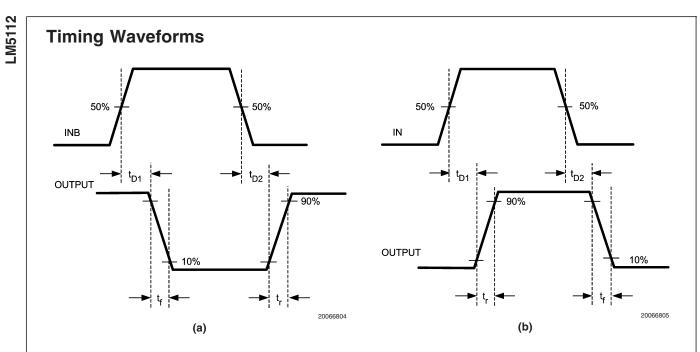

| td1               | Propagation Delay Time Low to<br>High,<br>IN/ INB rising ( IN to OUT)  | C <sub>LOAD</sub> = 2 nF, see <i>Figure 3</i>   |     | 25   | 40  | ns    |

| td2               | Propagation Delay Time High to<br>Low,<br>IN / INB falling (IN to OUT) | C <sub>LOAD</sub> = 2 nF, see <i>Figure 3</i>   |     | 25   | 40  | ns    |

| tr                | Rise time                                                              | C <sub>LOAD</sub> = 2 nF , see <i>Figure 3</i>  |     | 14   |     | ns    |

| tf                | Fall time                                                              | $C_{LOAD} = 2 \text{ nF}$ , see <i>Figure 3</i> |     | 12   |     | ns    |

| LATCHUP           | PROTECTION                                                             |                                                 |     |      |     |       |

|                   | AEC -Q100, METHOD 004                                                  | T <sub>.1</sub> = 150°C                         |     | 500  |     | mA    |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

LM5112

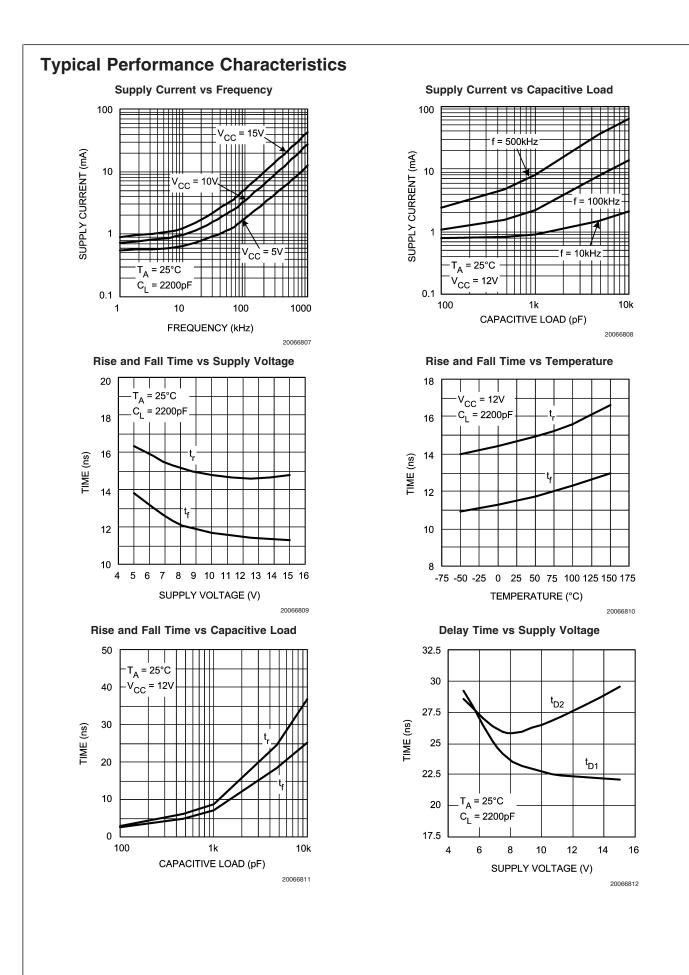

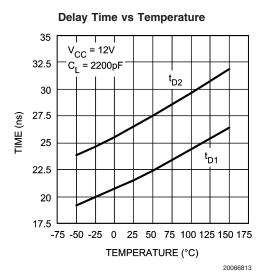

### Typical Performance Characteristics (Continued)

**RDSON vs Supply Voltage**

**UVLO Thresholds and Hysteresis vs Temperature**

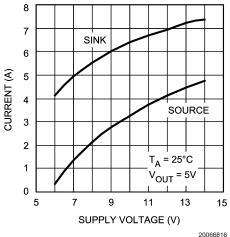

Peak Current vs Supply Voltage

20066815

### **Detailed Operating Description**

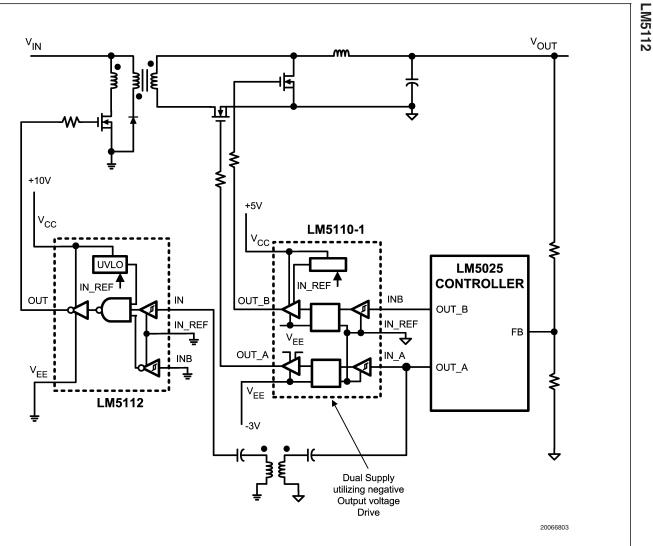

The LM5112 is a high speed, high peak current (7A) single channel MOSFET driver. The high peak output current of the LM5112 will switch power MOSFET's on and off with short rise and fall times, thereby reducing switching losses considerably. The LM5112 includes both inverting and noninverting inputs that give the user flexibility to drive the MOSFET with either active low or active high logic signals. The driver output stage consists of a compound structure with MOS and bipolar transistor operating in parallel to optimize current capability over a wide output voltage and operating temperature range. The bipolar device provides high peak current at the critical Miller plateau region of the MOS-FET V<sub>GS</sub> , while the MOS device provides rail-to-rail output swing. The totem pole output drives the MOSFET gate between the gate drive supply voltage  $V_{\rm CC}$  and the power ground potential at the V<sub>EE</sub> pin.

The control inputs of the driver are high impedance CMOS buffers with TTL compatible threshold voltages. The negative supply of the input buffer is connected to the input ground pin IN\_REF. An internal level shifting circuit connects the logic input buffers to the totem pole output drivers. The level shift circuit and separate input/output ground pins provide the option of single supply or split supply configurations.

When driving the MOSFET gates from a single positive supply, the IN\_REF and  $\rm V_{EE}$  pins are both connected to the power ground.

The isolated input and output stage grounds provide the capability to drive the MOSFET to a negative V<sub>GS</sub> voltage for a more robust and reliable off state. In split supply configuration, the IN\_REF pin is connected to the ground of the controller which drives the LM5112 inputs. The V<sub>EE</sub> pin is connected to a negative bias supply that can range from the IN\_REF potential to as low as 14 V below the Vcc gate drive supply. For reliable operation, the maximum voltage difference between V<sub>CC</sub> and IN\_REF or between V<sub>CC</sub> and V<sub>EE</sub> is 14V.

The minimum recommended operating voltage between Vcc and IN\_REF is 3.5V. An Under Voltage Lock Out (UVLO) circuit is included in the LM5112 which senses the voltage difference between V<sub>CC</sub> and the input ground pin, IN\_REF. When the V<sub>CC</sub> to IN\_REF voltage difference falls below 2.8V the driver is disabled and the output pin is held in the low state. The UVLO hysteresis prevents chattering during brown-out conditions; the driver will resume normal operation when the V<sub>CC</sub> to IN\_REF differential voltage exceeds 3.0V.

#### **Layout Considerations**

Attention must be given to board layout when using LM5112. Some important considerations include:

- 1. A Low ESR/ESL capacitor must be connected close to the IC and between the V<sub>CC</sub> and V<sub>EE</sub> pins to support high peak currents being drawn from V<sub>CC</sub> during turn-on of the MOSFET.

- 2. Proper grounding is crucial. The driver needs a very low impedance path for current return to ground avoiding inductive loops. Two paths for returning current to ground are a) between LM5112 IN\_REF pin and the ground of the circuit that controls the driver inputs and b) between LM5112  $V_{\rm EE}$  pin and the source of the power MOSFET being driven. Both paths should be as short as possible to reduce inductance and be as wide as possible to reduce resistance. These ground paths should be distinctly separate to avoid coupling between the high current output paths and the logic signals that drive the LM5112. With rise and fall times in the range of 10 to 30nsec, care is required to minimize the lengths of current carrying conductors to reduce their inductance and EMI from the high di/dt transients generated when driving large capacitive loads.

- 3. If either channel is not being used, the respective input pin (IN or INB) should be connected to either  $V_{EE}$  or  $V_{CC}$  to avoid spurious output signals.

### **Thermal Performance**

#### INTRODUCTION

The primary goal of the thermal management is to maintain the integrated circuit (IC) junction temperature (Tj) below a specified limit to ensure reliable long term operation. The maximum T<sub>J</sub> of IC components should be estimated in worst case operating conditions. The junction temperature can be calculated based on the power dissipated on the IC and the junction to ambient thermal resistance  $\theta_{JA}$  for the IC package in the application board and environment. The  $\theta_{JA}$  is not a given constant for the package and depends on the PCB design and the operating environment.

# DRIVE POWER REQUIREMENT CALCULATIONS IN LM5112

LM5112 is a single low side MOSFET driver capable of sourcing / sinking 3A / 7A peak currents for short intervals to drive a MOSFET without exceeding package power dissipation limits. High peak currents are required to switch the MOSFET gate very quickly for operation at high frequencies.

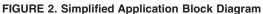

FIGURE 3.

The schematic above shows a conceptual diagram of the LM5112 output and MOSFET load. Q1 and Q2 are the switches within the gate driver. Rg is the gate resistance of the external MOSFET, and Cin is the equivalent gate capacitance of the MOSFET. The equivalent gate capacitance is a difficult parameter to measure as it is the combination of Cgs (gate to source capacitance) and Cgd (gate to drain capacitance). The Cgd is not a constant and varies with the drain voltage. The better way of quantifying gate capacitance is the gate charge Qg in coloumbs. Qg combines the charge required by Cgs and Cgd for a given gate drive voltage Vgate. The gate resistance Rg is usually very small and losses in it can be neglected. The total power dissipated in the MOSFET driver due to gate charge is approximated by:

$$P_{DRIVER} = V_{GATE} \times Q_G \times F_{SW}$$

Where

$F_{SW}$  = switching frequency of the MOSFET.

For example, consider the MOSFET MTD6N15 whose gate charge specified as 30 nC for  $V_{\rm GATE}$  = 12V.

Therefore, the power dissipation in the driver due to charging and discharging of MOSFET gate capacitances at switching frequency of 300 kHz and  $V_{GATE}$  of 12V is equal to

$P_{DRIVER} = 12V \times 30 \text{ nC} \times 300 \text{ kHz} = 0.108W.$

In addition to the above gate charge power dissipation, - transient power is dissipated in the driver during output transitions. When either output of the LM5112 changes state, current will flow from  $V_{\rm CC}$  to  $V_{\rm EE}$  for a very brief interval of time through the output totem-pole N and P channel MOSFETs. The final component of power dissipation in the driver is the power associated with the quiescent bias current consumed by the driver input stage and Under-voltage lockout sections.

Characterization of the LM5112 provides accurate estimates of the transient and quiescent power dissipation components. At 300 kHz switching frequency and 30 nC load used in the example, the transient power will be 8 mW. The 1 mA nominal quiescent current and 12V  $V_{GATE}$  supply produce a 12 mW typical quiescent power.

Therefore the total power dissipation

$P_{\rm D} = 0.118 + 0.008 + 0.012 = 0.138 {\rm W}.$

We know that the junction temperature is given by

$T_{J} = P_{D} \ x \ \theta_{JA} + T_{A}$ Or the rise in temperature is given by  $T_{BISE} = T_{J} - T_{A} = P_{D} \ x \ \theta_{JA}$

### Thermal Performance (Continued)

For LLP-6 package, the integrated circuit die is attached to leadframe die pad which is soldered directly to the printed circuit board. This substantially decreases the junction to ambient thermal resistance ( $\theta_{JA}$ ). By providing suitable means of heat dispersion from the IC to the ambient through

exposed copper pad, which can readily dissipate heat to the surroundings,  $\theta_{JA}$  as low as 40°C / Watt is achievable with the package. The resulting Trise for the driver example above is thereby reduced to just 5.5 degrees.

Therefore  $T_{\mbox{\scriptsize RISE}}$  is equal to