### LMX2531

# PLLatinum™ High Performance Frequency Synthesizer System with Integrated VCO

### **General Description**

The LMX2531 is a low power, high performance frequency synthesizer system which includes a fully integrated deltasigma PLL and VCO with fully integrated tank circuit. The third and fourth poles are also integrated and also adjustable. Also included are integrated ultra-low noise and high precision LDOs for the PLL and VCO which give higher supply noise immunity and also more consistent performance. When combined with a high quality reference oscillator, the LMX2531 generates very stable, low noise local oscillator signals for up and down conversion in wireless communication devices. The LMX2531 is a monolithic integrated circuit, fabricated in an advanced BiCMOS process. There are actually several different versions of this product, for which the primary difference is frequency range.

Device programming is facilitated using a three-wire MICROWIRE Interface that can operate down to 1.8 volts.

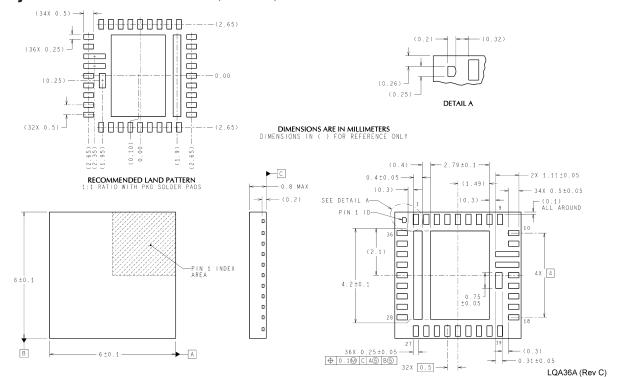

Supply voltage range is 2.8 to 3.2 Volts. The LMX2531 is available in a 36 pin 6x6x0.8 mm Lead-Free Leadless Lead-frame Package (LLP).

### **Target Applications**

- 3G Cellular Base Stations (WCDMA, TD-SCDMA,CDMA2000)

- 2G Cellular Base Stations (GSM/GPRS, EDGE, CDMA1xRTT)

- Wireless LAN

- Broadband Wireless Access

- Satellite Communications

- Wireless Radio

- Automotive

- CATV Equipment

- Instrumentation and Test Equipment

- RFID Readers

#### **Features**

#### **Multiple Frequency Options Available**

- See Selection Guide Below

- Frequencies from: 765 MHz 2790 MHz

#### **PLL Features**

- Fractional-N Delta Sigma Modulator Order programmable up to 4th order

- FastLock/Cycle Slip Reduction with Timeout Counter

- Partially integrated, adjustable Loop Filter

- Very low phase noise and spurs

#### **VCO Features**

- Integrated tank inductor

- Low phase noise

#### Other Features

- 2.8 V to 3.2 V Operation

- Low Power-Down Current

- 1.8V MICROWIRE Support

- Package: 36 Lead LLP

| Part           | Low Band        | High Band       |

|----------------|-----------------|-----------------|

| LMX2531LQ1570E | 765 - 818 MHz   | 1530 - 1636 MHz |

| LMX2531LQ1650E | 795 - 850 MHz   | 1590 - 1700 MHz |

| LMX2531LQ1700E | 831 - 885 MHz   | 1662 - 1770 MHz |

| LMX2531LQ1778E | 863 - 920 MHz   | 1726 - 1840 MHz |

| LMX2531LQ1910E | 917 - 1014 MHz  | 1834 - 2028 MHz |

| LMX2531LQ2080E | 952 - 1137 MHz  | 1904 - 2274 MHz |

| LMX2531LQ2265E | 1089 - 1200 MHz | 2178 - 2400 MHz |

| LMX2531LQ2570E | 1168 - 1395 MHz | 2336 - 2790 MHz |

PLLatinum™ is a trademark of National Semiconductor Corporation.

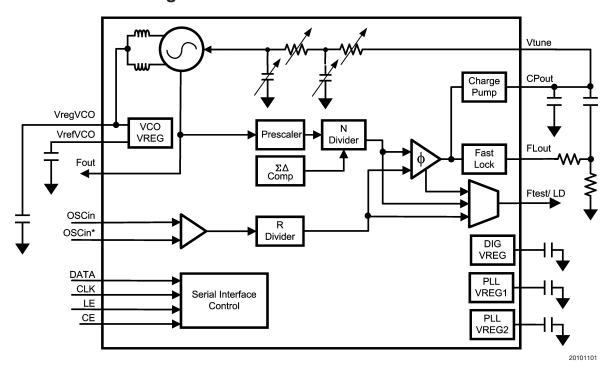

## **Functional Block Diagram**

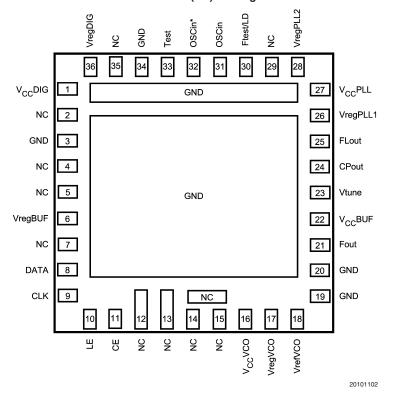

## **Connection Diagram**

#### 36-Pin LLP (LQ) Package

## **Pin Descriptions**

| Pin                              | _        |     |                                                                                                                                                                                                                                                            |

|----------------------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number                           | Pin Name | I/O | Description                                                                                                                                                                                                                                                |

| 1                                | VccDIG   | -   | Power Supply for digital LDO circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                  |

| 3                                | GND      | -   | Ground                                                                                                                                                                                                                                                     |

| 2,4,5,7,<br>12,<br>13,<br>29, 35 | NC       | -   | No Connect.                                                                                                                                                                                                                                                |

| 6                                | VregBUF  | -   | Internally regulated voltage for the VCO buffer circuitry. Connect to ground with a capacitor.                                                                                                                                                             |

| 8                                | DATA     | ı   | MICROWIRE serial data input. High impedance CMOS input. This pin must not exceed 2.75V. Data is clocked in MSB first. The last bits clocked in form the control or register select bits.                                                                   |

| 9                                | CLK      | I   | MICROWIRE clock input. High impedance CMOS input. This pin must not exceed 2.75V. Data is clocked into the shift register on the rising edge.                                                                                                              |

| 10                               | LE       | I   | MICROWIRE Latch Enable input. High impedance CMOS input. This pin must not exceed 2.75V.  Data stored in the shift register is loaded into the selected latch register when LE goes HIGH.                                                                  |

| 11                               | CE       | I   | Chip Enable Input. High impedance CMOS input. This pin must not exceed 2.75V. When CE is brought high the LMX2531 is powered up corresponding to the internal power control bits. It is necessary to reprogram the R0 register to get the part to re-lock. |

| 14, 15                           | NC       | -   | No Connect. Do NOT ground.                                                                                                                                                                                                                                 |

| 16                               | VccVCO   | -   | Power Supply for VCO regulator circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                |

| 17                               | VregVCO  | -   | Internally regulated voltage for VCO circuitry. Not intended to drive an external load. Connect to ground with a capacitor and some series resistance.                                                                                                     |

| 18                               | VrefVCO  | -   | Internal reference voltage for VCO LDO. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                        |

| 19                               | GND      | -   | Ground for the VCO circuitry.                                                                                                                                                                                                                              |

| 20                               | GND      | -   | Ground for the RF Output Buffer circuitry.                                                                                                                                                                                                                 |

| 21                               | Fout     | 0   | Buffered RF Output for the VCO.                                                                                                                                                                                                                            |

| 22                               | VccBUF   | -   | Power Supply for the VCO Buffer circuitry. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                               |

| 23                               | Vtune    | ı   | Tuning voltage input for the VCO. For connection to the CPout Pin through an external passive loop filter.                                                                                                                                                 |

| 24                               | CPout    | 0   | Charge pump output for PLL. For connection to Vtune through an external passive loop filter.                                                                                                                                                               |

| 25                               | FLout    | 0   | An open drain NMOS output which is used for FastLock or a general purpose output.                                                                                                                                                                          |

| 26                               | VregPLL1 | -   | Internally regulated voltage for PLL charge pump. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                              |

| 27                               | VccPLL   | -   | Power Supply for the PLL. Input may range from 2.8 - 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                |

| 28                               | VregPLL2 | -   | Internally regulated voltage for RF digital circuitry. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                         |

| 30                               | Ftest/LD | 0   | Multiplexed CMOS output. Typically used to monitor PLL lock condition.                                                                                                                                                                                     |

| 31                               | OSCin    | I   | Oscillator input. The oscillator can be placed in either single-ended or differential mode of operation.                                                                                                                                                   |

| 32                               | OSCin*   | I   | Oscillator complimentary input. When a single ended source is used, then a bypass capacitor should be placed as close as possible to this pin and be connected to ground.                                                                                  |

| 33                               | Test     | 0   | This pin if for test purposes and should be grounded for normal operation.                                                                                                                                                                                 |

| 34                               | GND      | -   | Ground                                                                                                                                                                                                                                                     |

| 36                               | VregDIG  | -   | Internally regulated voltage for LDO digital circuitry.                                                                                                                                                                                                    |

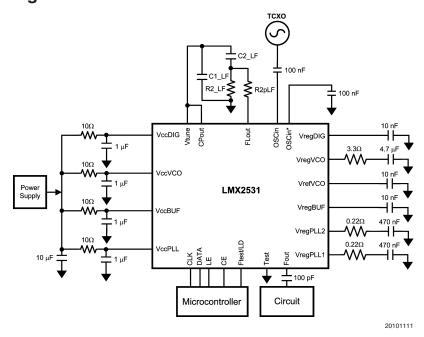

## **Connection Diagram**

| Pin(s)                                                                                                                                                                                                                                                                                                                                                                                                                                         | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VccDIG<br>VccVCO<br>VccBUF<br>VccPLL                                                                                                                                                                                                                                                                                                                                                                                                           | Because the LMX2531 contains internal regulators, the power supply noise rejection is very good and capacitors at this pin are not critical. If desired, capacitors can be placed at these pins to improve the noise rejection. Recommended values are from open to 1 µF.                                                                                                                                                                                        |  |  |  |  |  |

| VregDIG                                                                                                                                                                                                                                                                                                                                                                                                                                        | There is not really any reason to use any other values than the recommended values.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| VrefVCO                                                                                                                                                                                                                                                                                                                                                                                                                                        | If the VregVCO capacitor is changed, it is recommended to keep this capacitor between 1/100 and 1/1000 of the VregVCO capacitor.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| VregVCO                                                                                                                                                                                                                                                                                                                                                                                                                                        | Because this pin is the output of a regulator, there are be stability concerns if there is not sufficient series resistance. For ceramic capacitors the ESR (Equivalent Series Resistance) is too low, and it recommended that a series resistance of 1 - $3.3\Omega$ is necessary. If there is insufficient ESR, then there may be degradation in the phase noise, especially in the 100 - 300 kHz offset. Recommended values are from 1 $\mu$ F to 10 $\mu$ F. |  |  |  |  |  |

| VregPLL1 VregPLL2  The choice of the capacitor value at this pin involves a trade-off between integer spurs and phase 100 - 300 kHz offset range. If too much series resistance is at this pin, the spurs at far offset will degraded. If there is too little, the phase noise may be degraded. A 470 nF capacitor in series w provides optimal spurs with a minimal degradation in phase noise, although these optimal value design specific. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| CLK<br>DATA<br>LE                                                                                                                                                                                                                                                                                                                                                                                                                              | Since the maximum voltage on these pins is less than the minimum Vcc voltage, level shifting may be required, if the output voltage of the microcontroller is too high. This can be accomplished with a resistive divider.                                                                                                                                                                                                                                       |  |  |  |  |  |

| CE                                                                                                                                                                                                                                                                                                                                                                                                                                             | As with the CLK, DATA, and LE pins, level shifting may be required if the output voltage of the microcontroller is too high. A resistive divider is or a series diode are two ways to accomplish this. The diode has the advantage that no current flows through it when the chip is powered down.                                                                                                                                                               |  |  |  |  |  |

| Ftest/LD                                                                                                                                                                                                                                                                                                                                                                                                                                       | It is an option to use the lock detect information from this pin.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Fout                                                                                                                                                                                                                                                                                                                                                                                                                                           | This is the high frequency output. This needs to be AC coupled, and matching may also be required. The value of the DC blocking capacitor may be changed, depending on the output frequency.                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CPout<br>Vtune                                                                                                                                                                                                                                                                                                                                                                                                                                 | In most cases, it is sufficient to short these together. C1_LF, C2_LF, and R2_LF are used in conjunction with the internal loop filter to make a fourth order loop filter. However, the user always has the option of adding additional poles.                                                                                                                                                                                                                   |  |  |  |  |  |

| R2pLF                                                                                                                                                                                                                                                                                                                                                                                                                                          | This is the fastlock resistor, which can be useful in many cases, since the spurs are often better with low charge pump currents, and the internal loop filter can be adjusted during fastlock.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| OSCin                                                                                                                                                                                                                                                                                                                                                                                                                                          | This is the crystal oscillator input pin. It needs to be AC coupled.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OSCin*                                                                                                                                                                                                                                                                                                                                                                                                                                         | If the device is being driven single-ended, this pin needs to be shunted to ground with a capacitor.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Parameter                        | Symbol                                                 | Ratings     | Units |

|----------------------------------|--------------------------------------------------------|-------------|-------|

| Power Supply Voltage             | V <sub>CC</sub><br>(VccDIG, VccVCO,<br>VccBUF, VccPLL) | -0.3 to 3.5 | V     |

|                                  | All other pins (Except Ground)                         | -0.3 to 3.0 |       |

| Storage Temperature<br>Range     | T <sub>STG</sub>                                       | -65 to 150  | °C    |

| Lead Temperature (solder 4 sec.) | T <sub>L</sub>                                         | + 260       | °C    |

## **Recommended Operating Conditions**

| Parameter                                     | Symbol         | Min | Тур | Max  | Units |

|-----------------------------------------------|----------------|-----|-----|------|-------|

| Power Supply Voltage (VccDig, VccVCO, VccBUF) | Vcc            | 2.8 | 3.0 | 3.2  | V     |

| Serial Interface and Power Control<br>Voltage | V <sub>i</sub> | 0   |     | 2.75 | V     |

| Ambient Temperature (Note 3)                  | T <sub>A</sub> | -40 |     | +85  | °C    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only to the test conditions listed.

## **Electrical Characteristics** ( $V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le 85 ^{\circ}\text{C}$ ; except as specified.)

| Symbol                 | Parameter                                    | Conditions                                                                                           | Min  | Тур  | Max | Units  |

|------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|-----|--------|

|                        |                                              | Current Consumption                                                                                  |      |      |     |        |

|                        | Power Supply Current (All Parts Except       | Divider Disabled                                                                                     |      | 34   | 41  |        |

| I <sub>cc</sub>        | LMX2531LQ2265E,<br>LMX2531LQ2570E)           | Divider Enabled                                                                                      |      | 37   | 46  | mA     |

|                        | Power Supply Current (LMX2351LQ2265E,        | Divider Disabled                                                                                     |      | 38   | 44  |        |

|                        | LMX2531LQ2570E)                              | Divider Enabled                                                                                      |      | 41   | 49  |        |

| I <sub>CC</sub> PD     | Power Down Current                           | CE = 0 V, Part Initialized                                                                           |      | 7    |     | μΑ     |

|                        |                                              | Oscillator                                                                                           |      |      |     |        |

| I <sub>IH</sub> OSC    | Oscillator Input High Current                | V <sub>IH</sub> = 2.75 V                                                                             |      |      | 100 | μΑ     |

| I <sub>IL</sub> OSC    | Oscillator Input Low Current                 | V <sub>IL</sub> = 0                                                                                  | -100 |      |     | μΑ     |

| f <sub>OSCin</sub>     | Frequency Range                              |                                                                                                      | 5    |      | 80  | MHz    |

| V <sub>OSCin</sub>     | Oscillator Sensitivity                       |                                                                                                      | 0.5  |      | 2.0 | Vpp    |

|                        |                                              | PLL                                                                                                  |      |      |     |        |

| f <sub>COMP</sub>      | Phase Detector Frequency                     |                                                                                                      |      |      | 20  | MHz    |

|                        |                                              | ICP = 0                                                                                              |      | 90   |     | μΑ     |

| 1                      | Charge Pump                                  | ICP = 1                                                                                              |      | 180  |     | μΑ     |

| I <sub>CPout</sub>     | Output Current Magnitude                     | ICP = 3                                                                                              |      | 360  |     | μΑ     |

|                        |                                              | ICP = 15                                                                                             |      | 1510 |     | μΑ     |

| I <sub>CPout</sub> TRI | CP TRI-STATE Current                         | 0.4 V < V <sub>CPout</sub> < 2.0 V                                                                   |      | 2    | 10  | nA     |

| I <sub>CPout</sub> MM  | Charge Pump<br>Sink vs. Source Mismatch      | $V_{CPout} = 1.2 V$ $T_A = 25^{\circ}C$                                                              |      | 2    | 8   | %      |

| I <sub>CPout</sub> V   | Charge Pump Current vs. CP Voltage Variation | $0.4 \text{ V} < \text{V}_{\text{CPout}} < 2.0 \text{ V}$ $\text{T}_{\text{A}} = 25^{\circ}\text{C}$ |      | 4    |     | %      |

| I <sub>CPout</sub> T   | CP Current vs. Temperature  Variation        | V <sub>CPout</sub> = 1.2 V                                                                           |      | 8    |     | %      |

| I NI(f)                | Normalized Phase Noise  Contribution         | ICP = 1X Charge Pump Gain<br>4 kHz Offset                                                            |      | -202 |     | dBc/Hz |

| LN(f)                  | (Note 2)                                     | ICP = 16X Charge Pump Gain<br>4 kHz Offset                                                           |      | -212 |     | ubc/n2 |

## **Electrical Characteristics** ( $V_{CC}$ = 3.0 V, -40°C $\leq$ T<sub>A</sub> $\leq$ 85 °C; except as specified.) (Continued)

| Symbol               | Parameter                                               |                                                  | litions           | Min  | Тур   | Max      | Units    |

|----------------------|---------------------------------------------------------|--------------------------------------------------|-------------------|------|-------|----------|----------|

|                      |                                                         | VCO Frequenci                                    |                   |      |       |          |          |

|                      |                                                         |                                                  | 1LQ1570E          | 1530 |       | 1636     |          |

|                      | Oneveting Frequency Benge                               | LMX253                                           | 1LQ1650E          | 1590 |       | 1700     |          |

|                      | Operating Frequency Range (All options have a frequency | LMX253                                           | 1LQ1700E          | 1662 |       | 1770     |          |

| $f_{Fout}$           | divider, this applies before the                        | LMX253                                           | 1LQ1778E          | 1726 |       | 1840     | MHz      |

| 'Fout                | divider. The frequency after the                        | LMX253                                           | 1LQ1910E          | 1834 |       | 2028     | 1711 12  |

|                      | divider is half of what is shown)                       | LMX253                                           | 1LQ2080E          | 1904 |       | 2274     |          |

|                      |                                                         | LMX253                                           | 1LQ2265E          | 2178 |       | 2400     |          |

|                      |                                                         | LMX253                                           | 1LQ2570E          | 2336 |       | 2790     |          |

|                      |                                                         | Other VCO Specific                               | ations            |      |       |          |          |

|                      |                                                         | LMX2531LQ1570E                                   | , LMX2531LQ1650E  | 90   |       |          |          |

|                      | Continuous Lock Temperature                             | LMX2531LQ1700E                                   | , LMX2531LQ1778E, |      |       |          | *0       |

| $\Delta T_{CL}$      | Range                                                   | LMX2531LQ1910E                                   | LMX2531LQ2080E,   | 125  |       |          | °C       |

|                      | (Note 3)                                                | LMX2531LQ2265E                                   | ,LMX2531LQ2570E   |      |       |          |          |

|                      |                                                         | LMX2531LQ1570E                                   |                   | 2.0  | 4.5   | 8.0      |          |

|                      |                                                         | LMX2531LQ1650E                                   |                   | 2.0  | 4.5   | 8.0      |          |

|                      |                                                         | LMX2531LQ1700E                                   |                   | 1.0  | 3.5   | 7.0      |          |

|                      |                                                         | LMX2531LQ1778E                                   |                   | 1.0  | 3.5   | 7.0      |          |

|                      |                                                         | LMX2531LQ1910E                                   | Divider Disabled  | 1.0  | 3.5   | 7.0      | dBm      |

|                      |                                                         | LMX2531LQ2080E                                   |                   | 1.0  | 3.5   | 7.0      |          |

|                      |                                                         | LMX2531LQ2265E                                   |                   | 1.0  | 3.5   | 7.0      |          |

|                      | Output Power to a 50Ω/5pF Load                          | LMX2531LQ2570E                                   |                   | 0.0  | 3.0   | 6.0      |          |

| $p_{Fout}$           | (Applies across entire tuning                           | LMX2531LQ2570E                                   |                   | 1.0  | 2.5   | 6.0      |          |

|                      | range.)                                                 | LMX2531LQ1650E                                   |                   | 1.0  | 2.5   | 6.0      |          |

|                      |                                                         |                                                  |                   | H-1  |       |          |          |

|                      |                                                         | LMX2531LQ1700E                                   |                   | 1.0  | 3.0   | 6.0      |          |

|                      |                                                         | LMX2531LQ1778E                                   | Divider Enabled   | 1.0  | 3.0   | 6.0      | dBm      |

|                      |                                                         | LMX2531LQ1910E                                   |                   | 1.0  | 3.0   | 6.0      |          |

|                      |                                                         | LMX2531LQ2080E                                   |                   | 0.0  | 2.5   | 5.0      |          |

|                      |                                                         | LMX2531LQ2265E                                   |                   | 1.0  | 2.5   | 5.0      |          |

|                      |                                                         | LMX2531LQ2570E                                   |                   | -1.0 | 1.5   | 4.0      |          |

|                      | Fine Tuning Sensitivity                                 | LMX253                                           | 1LQ1570E          |      | 4-7   |          |          |

|                      | (When a range is displayed in the                       | LMX253                                           | 1LQ1650E          |      | 4-7   |          |          |

|                      | typical column, indicates the lower                     | LMX253                                           | 1LQ1700E          |      | 6-10  |          |          |

| K                    | sensitivity is typical at the lower                     | LMX253                                           | 1LQ1778E          |      | 6-10  |          | MHz/     |

| $K_{Vtune}$          | end of the tuning range, and the                        | LMX253                                           | 1LQ1910E          |      | 8-14  |          | IVII IZ/ |

|                      | higher tuning sensitivity is typical                    | LMX253                                           | 1LQ2080E          |      | 9-20  |          |          |

|                      | at the higher end of the tuning                         | LMX253                                           | 1LQ2265E          |      | 10-17 |          |          |

|                      | range.)                                                 | LMX253                                           | 1LQ2570E          |      | 10-23 |          |          |

|                      |                                                         | 2nd Harmonic, 50Ω /                              | Divider Disabled  |      | -30   | -25      |          |

|                      |                                                         | 5pF Load                                         | Divider Enabled   |      | -20   | -15      |          |

|                      |                                                         |                                                  | Divider Disabled  |      | -40   | -35      |          |

| 110                  | Harmonic Suppression                                    |                                                  | Divider Enabled   |      |       | $\vdash$ | -ID      |

| HS <sub>Fout</sub>   | (Applies Across Entire Tuning                           | 3rd Harmonic, 50Ω /                              | LMX2531LQ1570E    |      | -20   | -15      | dBc      |

|                      | Hange)                                                  | Range) 5pF Load LMX2531LQ10                      |                   |      |       |          |          |

|                      |                                                         |                                                  | Divider Enabled   |      |       |          |          |

|                      |                                                         | All Other Options                                |                   |      | -25   | -20      |          |

| PUSH <sub>Fout</sub> | Frequency Pushing                                       | Creg = 0.1uF, V <sub>DD</sub> ± 100mV, Open Loop |                   |      | 300   |          | kHz/\    |

| PULL <sub>Fout</sub> | Frequency Pulling                                       |                                                  | , Open Loop       |      |       | ±600     | kHz      |

|                      | , , , ,                                                 |                                                  | 1 1               |      |       |          |          |

7

## **Electrical Characteristics** ( $V_{CC}$ = 3.0 V, -40°C $\leq$ T<sub>A</sub> $\leq$ 85 °C; except as specified.) (Continued)

| Symbol               | Parameter                       | Cond                          | Min            | Тур | Max  | Units |         |  |

|----------------------|---------------------------------|-------------------------------|----------------|-----|------|-------|---------|--|

|                      |                                 | VCO Frequencie                |                |     |      |       |         |  |

|                      |                                 | VCO Phase Noise (N            |                |     | I    |       |         |  |

|                      |                                 |                               | 10 kHz Offset  |     | -93  |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 1583 MHz  | 100 kHz Offset |     | -118 |       |         |  |

|                      |                                 | DIV2 = 0                      | 1 MHz Offset   |     | -140 |       |         |  |

| L(f) <sub>Fout</sub> | Phase Noise                     |                               | 5 MHz Offset   |     | -154 |       | dBc/H   |  |

| -\'/Fout             | (LMX2531LQ1570E)                |                               | 10 kHz Offset  |     | -99  |       | G. 2 G/ |  |

|                      |                                 | f <sub>Fout</sub> = 791.5 MHz | 100 kHz Offset |     | -122 |       |         |  |

|                      |                                 | DIV2 = 1                      | 1 MHz Offset   |     | -144 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   |     | -155 |       |         |  |

|                      |                                 |                               | 10 kHz Offset  |     | -93  |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 1645 MHz  | 100 kHz Offset |     | -118 |       |         |  |

|                      |                                 | DIV2 = 0                      | 1 MHz Offset   |     | -140 |       |         |  |

| L(f) <sub>Fout</sub> | Phase Noise                     |                               | 5 MHz Offset   |     | -154 |       | dBc/F   |  |

| L(I)Fout             | (LMX2531LQ1650E)                |                               | 10 kHz Offset  |     | -99  |       | ubc/i   |  |

|                      |                                 | f <sub>Fout</sub> = 822.5 MHz | 100 kHz Offset |     | -122 |       |         |  |

|                      |                                 | DIV2 = 1                      | 1 MHz Offset   |     | -144 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   |     | -155 |       |         |  |

|                      |                                 |                               | 10 kHz Offset  |     | -92  |       |         |  |

|                      | Phase Noise<br>(LMX2531LQ1770E) | f <sub>Fout</sub> = 1716 MHz  | 100 kHz Offset |     | -117 |       |         |  |

|                      |                                 | DIV2 = 0                      | 1 MHz Offset   |     | -139 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   |     | -153 |       | dBc/Hz  |  |

| L(f) <sub>Fout</sub> |                                 |                               | 10 kHz Offset  |     | -98  |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 858 MHz   | 100 kHz Offset |     | -122 |       |         |  |

|                      |                                 | DIV2 = 1                      | 1 MHz Offset   |     | -144 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   |     | -154 |       |         |  |

|                      |                                 |                               | 10 kHz Offset  |     | -92  |       |         |  |

|                      |                                 |                               | 100 kHz Offset |     | -117 |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 1783 MHz  | 1 MHz Offset   |     | -139 |       | 7       |  |

|                      | Phase Noise                     |                               | 5 MHz Offset   |     | -152 |       |         |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1778E)                |                               | 10 kHz Offset  |     | -97  |       | dBc/F   |  |

|                      |                                 |                               | 100 kHz Offset |     | -122 |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 891.5 MHz | 1 MHz Offset   |     | -144 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   |     | -154 |       |         |  |

|                      |                                 |                               | 10 kHz Offset  |     | -89  |       |         |  |

|                      |                                 |                               | 100 kHz Offset |     | -115 |       |         |  |

|                      |                                 | f <sub>Fout</sub> = 1931      | 1 MHz Offset   |     | -138 |       |         |  |

|                      | Phase Noise                     |                               | 5 MHz Offset   |     | -151 |       | dBc/H   |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1910E)                |                               | 10 kHz Offset  |     | -95  | +     |         |  |

|                      | ,,                              |                               | 100 kHz Offset |     | -121 | +     |         |  |

|                      |                                 | f <sub>Fout</sub> = 965.5     | 1 MHz Offset   |     | -143 |       |         |  |

|                      |                                 |                               | 5 MHz Offset   | -   | -155 |       |         |  |

## **Electrical Characteristics** ( $V_{CC}$ = 3.0 V, -40°C $\leq$ T<sub>A</sub> $\leq$ 85 °C; except as specified.) (Continued)

| Symbol               | Parameter                       | Cond                           | litions        | Min | Тур  | Max | Units   |  |

|----------------------|---------------------------------|--------------------------------|----------------|-----|------|-----|---------|--|

|                      |                                 | VCO Frequenci                  | es             |     |      |     |         |  |

|                      |                                 |                                | 10 kHz Offset  |     | -87  |     |         |  |

|                      |                                 | f 2000 MU¬                     | 100 kHz Offset |     | -113 |     |         |  |

|                      |                                 | f <sub>Fout</sub> = 2089 MHz   | 1 MHz Offset   |     | -136 |     |         |  |

| 1 (f)                | Phase Noise<br>(LMX2531LQ2080E) |                                | 5 MHz Offset   |     | -150 |     | dBc/Hz  |  |

| L(f) <sub>Fout</sub> |                                 |                                | 10 kHz Offset  |     | -93  |     | UDC/FIZ |  |

|                      |                                 | f <sub>Fout</sub> = 1044.5 MHz | 100 kHz Offset |     | -119 |     |         |  |

|                      |                                 | Fout - 1044.5 WI12             | 1 MHz Offset   |     | -142 |     |         |  |

|                      |                                 |                                | 5 MHz Offset   |     | -154 |     |         |  |

|                      | Phase Noise<br>(LMX2531LQ2265E) |                                | 10 kHz Offset  |     | -90  |     |         |  |

|                      |                                 | f <sub>Fout</sub> = 2264 MHz   | 100 kHz Offset |     | -114 |     |         |  |

|                      |                                 | I <sub>Fout</sub> = 2204 IVID2 | 1 MHz Offset   |     | -137 |     |         |  |

| I (f)                |                                 |                                | 5 MHz Offset   |     | -151 |     | dBc/Hz  |  |

| L(f) <sub>Fout</sub> |                                 | f <sub>Fout</sub> = 1132 MHz   | 10 kHz Offset  |     | -95  |     | UDC/FIZ |  |

|                      |                                 |                                | 100 kHz Offset |     | -118 |     |         |  |

|                      |                                 |                                | 1 MHz Offset   |     | -142 |     |         |  |

|                      |                                 |                                | 5 MHz Offset   |     | -152 |     |         |  |

|                      |                                 |                                | 10 kHz Offset  |     | -86  |     |         |  |

|                      |                                 | f _ 0560 MH-                   | 100 kHz Offset |     | -112 |     |         |  |

|                      |                                 | f <sub>Fout</sub> = 2563 MHz   | 1 MHz Offset   |     | -135 |     |         |  |

| I (f)                | Phase Noise                     |                                | 5 MHz Offset   |     | -149 |     | dBc/Hz  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ2570E)                |                                | 10 kHz Offset  |     | -91  |     | UBC/HZ  |  |

|                      |                                 | f <sub>Fout</sub> = 1281.5 MHz | 100 kHz Offset |     | -117 |     |         |  |

|                      |                                 | Fout - 1201.3 WITZ             | 1 MHz Offset   |     | -139 |     |         |  |

|                      |                                 |                                | 5 MHz Offset   |     | -152 |     |         |  |

## $\textbf{Electrical Characteristics} \ (\text{V}_{\text{CC}} = 3.0 \ \text{V}, \ \text{-}40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85 \ ^{\circ}\text{C}; \ \text{except as specified.}) \ \ (\text{Continued})$

| Symbol           | Parameter                                              | Conditions                | Min  | Тур | Max  | Units |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------|---------------------------|------|-----|------|-------|--|--|--|--|--|--|--|

|                  | Digital Interface (DATA, CLK, LE, CE, Ftest/LD, FLout) |                           |      |     |      |       |  |  |  |  |  |  |  |

| V <sub>IH</sub>  | High-Level Input Voltage                               |                           | 1.6  |     | 2.75 | V     |  |  |  |  |  |  |  |

| V <sub>IL</sub>  | Low-Level Input Voltage                                |                           |      |     | 0.4  | V     |  |  |  |  |  |  |  |

| I <sub>IH</sub>  | High-Level Input Current                               | V <sub>IH</sub> = 1.75    | -3.0 |     | 3.0  | μA    |  |  |  |  |  |  |  |

| IIL              | Low-Level Input Current                                | V <sub>IL</sub> = 0 V     | -3.0 |     | 3.0  | μA    |  |  |  |  |  |  |  |

| V <sub>OH</sub>  | High-Level Output Voltage                              | I <sub>OH</sub> = 500 μA  | 2.0  |     |      | V     |  |  |  |  |  |  |  |

| V <sub>OL</sub>  | Low-Level Output Voltage                               | I <sub>OL</sub> = -500 μA |      |     | 0.4  | V     |  |  |  |  |  |  |  |

|                  |                                                        | MICROWIRE Timing          | •    |     |      |       |  |  |  |  |  |  |  |

| t <sub>CS</sub>  | Data to Clock Set Up Time                              | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>CH</sub>  | Data to Clock Hold Time                                | See Data Input Timing     | 20   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>cwh</sub> | Clock Pulse Width High                                 | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>CWL</sub> | Clock Pulse Width Low                                  | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>ES</sub>  | Clock to Enable Set Up Time                            | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>CES</sub> | Enable to Clock Set Up Time                            | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

| t <sub>EWH</sub> | Enable Pulse Width High                                | See Data Input Timing     | 25   |     |      | ns    |  |  |  |  |  |  |  |

Note 2: Normalized Phase Noise Contribution is defined as: LN(f) = L(f) - 20log(N) - 10log(Fcomp) where L(f) is defined as the single side band phase noise measured at an offset frequency, f, in a 1 Hz Bandwidth and Fcomp is the comparison frequency of the synthesizer. The offset frequency, f, must be chosen sufficiently smaller then the PLL's loop band-width, and large enough to avoid a substantial noise contribution from the reference.

Note 3: Continuous Lock Temperature Range is how far the temperature can drift in either direction from it's original value at the time of the part being programmed, before the PLL has to be reprogrammed. The action of programming the R0 register activates a calibration routine. However, if this register is not reprogrammed, the temperature drift spec applies. Note that regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of -40°C  $\leq$ Ta $\leq$  85°C without violating specifications.

Note 4: The VCO phase noise is measured assuming that the loop bandwidth is sufficiently narrow that the VCO noise dominates. The maximum limits apply only at center frequency and over temperature, assuming that the part is reloaded at each test frequency. Over frequency, the phase noise can vary 1-2 dB, with the worst case performance typically occurring at the highest frequency. Over temperature, the phase noise typically varies 1-2 dB, assuming the part is reloaded.

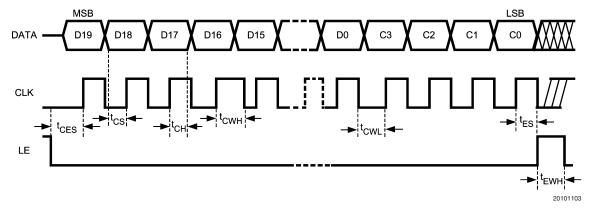

### **Serial Data Timing Diagram**

### 1.0 Functional Description

The LMX2531 is a low power, high performance frequency synthesizer system which includes the PLL, VCO, and partially integrated loop filter. Section 2.0 on programming describes the bits mentioned in this section in more detail.

#### 1.1 Reference Oscillator Input

Because the VCO frequency calibration algorithm is based on clocks from the OSCin pin, there are certain bits that need to be set depending on the OSCin frequency. XTLSEL (R6[22:20]) and XTLDIV (R7[9:8]) are both need to be set based on the OSCin frequency. For the LMX2531LQ2080E and the LMX2531LQ2570E, the XTLMAN[11:0] and XTLMAN2.

#### 1.2 R Divider

The R divider divides the OSCin frequency down to the phase detector frequency. The only valid R counter values are 2, 4, 8, 16, and 32. The R divider also has an impact on the fractional modulus that can be used, if it is greater than 8.

#### 1.3 N Divider

The N divider on the LMX2531 is fractional and can achieve any fractional denominator between 1 and 4,194,303 using a delta-sigma modulator of selectable order of 2, 3, or 4. Depending on the prescaler used, there are restrictions on how small the N counter can be.

#### 1.4 Phase Detector

The phase detector compares the outputs of the R and N counters and puts out a correction current corresponding to the phase error. The choice of the phase detector frequency does have an impact on performance.

#### 1.5 Partially Integrated Loop Filter

The LMX2531 integrates the third pole (formed by R3 and C3) and fourth pole (formed by R4 and C4) of the loop filter. This loop filter can be enabled or bypassed using the EN\_LPFLTR (R6[15]). The values for C3, C4, R3, and R4 can also be programmed independently through the MI-CROWIRE interface . Also, the values for R3 and R4 can be changed during FastLock, for minimum lock time. It is recommended that the integrated loop filter be set to the maximum possible attenuation (R3=R4=40kΩ, C3=C4=100pF), the internal loop filter is more effective at reducing certain spurs than the external loop filter. However, the attenuation of the internal loop filter is too high, it limits the maximum attainable loop bandwidth that can be achieved, which corresponds to the case where the shunt loop filter capacitor, C1, is zero. Increasing the charge pump current and/or the comparison frequency increases the maximum attainable loop bandwidth when designing with the integrated filter. Furthermore, this often allows the loop filter to be better optimized and have stronger attenuation. If the charge pump current and comparison frequency are already as high as they go, and the maximum attainable loop bandwidth is still too low, the resistor and capacitor values can be decreased or the internal loop filter can even be bypassed. For design tools and more information on partially integrated loop filters, go to wireless.national.com.

#### 1.6 Low Noise, Fully Integrated VCO

The LMX2531 includes a fully integrated VCO, including the inductors. In order for optimum phase noise performance, this VCO has frequency and phase noise calibration algo-

rithms. The VCO internally divides up the frequency range into several bands, in order to achieve a lower tuning gain, and therefore better phase noise performance. The frequency calibration routine is activated any time that the R0 register is programmed. If the temperature shifts considerably and the R0 register is not programmed, then it can not drift more than continuous lock temperature range,  $\Delta T_{\rm CL}$ , or else the VCO is not guaranteed to stay in lock. There is also a routine for optimum phase noise performance as well, for each version of the LMX2531, the VCO\_ACI\_SEL bit ( R6[19:16] ) needs to be set to the correct value to ensure the best possible phase noise.

The gain of the VCO can change considerably over frequency. It is lowest at the minimum frequency and highest at the maximum frequency. This range is specified in the datasheet. When designing the loop filter, the following method is recommended. First, take the gemetric mean of the minimum and maximum frequencies that are to be used. Then use a linear approximation to extrapolate the VCO gain. An example is in order. Suppose the application requires the LMX2531LQ2080E PLL to tune from 2100 to 2150 MHz. The geometric mean of these frequencies is sqrt(2100 x 2150) MHz = 2125 MHz. The VCO gain is specified as 9 MHz/V at 1904 MHz and 20 MHz/V at 2274 MHz. Over this range of 370 MHz, the VCO gain changes 11 MHz/volt. So at 2125 MHz, the VCO gain would be approximately 9 + (2125-1904)\* 11/370 = 15.6 MHz/V. Although the VCO gain can change from part to part, this variation is small to how much the VCO gain can change over frequency.

#### 1.7 Programmable Divide by 2

All options of the LMX2531 offer a divide by 2 option. This allows the user to get exactly half of the VCO frequency. In order to use this feature, the VCO is programmed to it's non-divided frequency. Note that R0 register should be reprogrammed the first time after the DIV2 bit is enabled or disabled for optimal phase noise performance.

## 1.8 Choosing the Charge Pump Current and Comparison Frequency

The LMX2531 has 16 levels of charge pump currents and a highly flexible fractional modulus. This gives the user many degrees of freedom. This section discusses some of the design considerations. From the perspective of the PLL noise, choosing the charge pump current and comparison frequency as high as possible are best for optimal phase noise performance. The far out PLL noise improves 3 dB for every doubling of the comparison frequency, but at lower offsets, this effect is much less due to the PLL 1/f noise. Increasing the charge pump current inproves the phase noise about 3 dB per doubling of the charge pump current, although there are small diminishing returns as the charge pump current goes higher.

So, from a loop filter design perspective and from a PLL phase noise perspective, one might think to always design with the highest possible comparison frequency and charge pump current. However, if one considers the worst case fractional spurs that occur at an output frequency equal to 1 channel spacing away from a multiple of the OSCin frequency, then this gives reason to reconsider. If the comparison frequency or charge pump currents are too high, then these spurs could be degraded, and the loop filter may not be able to filter these spurs as well as theoretically predicted. For optimal spur performance, a comparison frequency in the ballpark of 2.5 MHz and a charge pump current of 1X are recommended.

### 2.0 General Programming Information

The LMX2531 is programmed using 14 24-bit registers used to control the LMX2531 operation. A 24-bit shift register is used as a temporary register to indirectly program the on-chip registers. The shift register consists of a data field and an address field. The last 4 register bits, CTRL[3:0] form the address field, which is used to decode the internal register address. The remaining 20 bits form the data field DATA[19:0]. While LE is low, serial data is clocked into the shift register upon the rising edge of clock (data is programmed MSB first). When LE goes high, data is transferred from the data field into the selected register bank.

Although there are actually 14 registers in this part, only a portion of them should be programmed, since the state of the other hidden registers (R13, R11, and R10) are set during the initialization sequence. Although it is possible to program these hidden registers, as well as a lot of bits that are defined to either '1' or '0', the user should not experiment with these bits, since doing so may easily lead to degraded performance. The optimal settings for these bits have already been found, and not programming them would not be consistent with how the part is tested.

|     | DATA[19:0] |     |     |     |     |     |     |     |     |    | C  | ONTE | ROL[ | 3:0] |    |    |    |    |    |    |    |    |     |

|-----|------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|------|------|------|----|----|----|----|----|----|----|----|-----|

| MSB |            |     |     |     |     |     |     |     |     |    |    |      |      |      |    |    |    |    |    |    |    |    | LSB |

| D19 | D18        | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7   | D6   | D5   | D4 | D3 | D2 | D1 | D0 | СЗ | C2 | C1 | C0  |

#### 2.01 Register Location Truth Table

| C3 | C2 | C1 | C0 | Data Address |

|----|----|----|----|--------------|

| 1  | 1  | 0  | 0  | R12          |

| 1  | 0  | 0  | 1  | R9           |

| 1  | 0  | 0  | 0  | R8           |

| 0  | 1  | 1  | 1  | R7           |

| 0  | 1  | 1  | 0  | R6           |

| 0  | 1  | 0  | 1  | R5           |

| 0  | 1  | 0  | 0  | R4           |

| 0  | 0  | 1  | 1  | R3           |

| 0  | 0  | 1  | 0  | R2           |

| 0  | 0  | 0  | 1  | R1           |

| 0  | 0  | 0  | 0  | R0           |

#### 2.02 Initialization Sequence

The initial loading sequence from a cold start is described below. The registers must be program in order shown.

| DEOLOTED    | 23 | 22                                                              | 21 | 20   | 19   | 18    | 17    | 16    | 15    | 14     | 13    | 12     | 11    | 10                     | 9      | 8     | 7     | 6 | 5   | 4 | 3  | 2  | 1  | 0  |

|-------------|----|-----------------------------------------------------------------|----|------|------|-------|-------|-------|-------|--------|-------|--------|-------|------------------------|--------|-------|-------|---|-----|---|----|----|----|----|

| REGISTER    |    |                                                                 |    |      |      |       |       |       |       | DATA   | [19:0 | )]     |       |                        |        |       |       |   |     | • | СЗ | C2 | C1 | C0 |

| R5<br>INIT1 | 1  | 0                                                               | 0  | 0    | 0    | 1     | 0     | 0     | 0     | 0      | 0     | 0      | 0     | 0                      | 0      | 0     | 0     | 0 | 0   | 0 | 0  | 1  | 0  | 1  |

| R5<br>INIT2 | 1  | 0                                                               | 0  | 0    | 0    | 0     | 0     | 0     | 0     | 0      | 0     | 0      | 0     | 0                      | 0      | 0     | 0     | 0 | 0   | 0 | 0  | 1  | 0  | 1  |

| R5          | 1  | 0                                                               | 0  | 0    | 0    | 0     | 0     | 0     | 0     | 0      | 0     | 0      | 0     | 1                      | 1      | 1     | 1     | 1 | 1   | 1 | 0  | 1  | 0  | 1  |

| R12         | 0  | 0                                                               | 0  | 0    | 0    | 0     | 0     | 1     | 0     | 0      | 0     | 0      | 0     | 1                      | 0      | 0     | 1     | 0 | 0   | 0 | 1  | 1  | 0  | 0  |

| R9          |    |                                                                 |    |      | See  | indiv | /idua | l sec | tion  | for R  | 9 pro | ograr  | nmin  | g info                 | orma   | tion. |       |   |     |   | 1  | 0  | 0  | 1  |

| R8          |    | Re                                                              | _  | r R8 | only | need  | ls to | be p  | rogra | amm    | ed fo | r a fe | ew ol | nmin<br>otion:<br>grea | s of t | the L | MX2   |   | and |   | 1  | 0  | 0  | 0  |

| R7          |    |                                                                 |    | See  | indi | /idua | l sec | tion  | for R | legist | er R  | 7 pro  | gran  | nmin                   | g info | orma  | tion. |   |     |   | 0  | 1  | 1  | 1  |

| R6          |    |                                                                 |    | See  | indi | /idua | l sec | tion  | for R | legist | er R  | 6 pro  | gran  | nmin                   | g info | orma  | tion. |   |     |   | 0  | 1  | 1  | 0  |

| R4          |    |                                                                 |    |      |      |       |       |       |       | •      |       | •      | •     | nmin<br>stLo           | _      |       |       |   |     |   | 0  | 1  | 0  | 0  |

| R3          |    | See individual section for Register R3 programming information. |    |      |      |       |       |       | 0     | 0      | 1     | 1      |       |                        |        |       |       |   |     |   |    |    |    |    |

| R2          |    | See individual section for Register R2 programming information. |    |      |      |       |       |       |       | 0      | 0     | 1      | 0     |                        |        |       |       |   |     |   |    |    |    |    |

| R1          |    | See individual section for Register R1 programming information. |    |      |      |       |       |       |       | 0      | 0     | 0      | 1     |                        |        |       |       |   |     |   |    |    |    |    |

| R0          |    |                                                                 |    | See  | indi | /idua | l sec | tion  | for R | legist | er R  | 0 pro  | gran  | nmin                   | ginfo  | orma  | tion. |   |     |   | 0  | 0  | 0  | 0  |

Note: There must be a minimum of 10 mS between the time when R5 is last loaded and when R1 is loaded to ensure time for the LDOs to power up properly.

#### 2.03 Complete Register Content Map

| (Continued)     |

|-----------------|

| Information     |

| Programming Inf |

| 2.0 General     |

| _  | _          |               |                |               |                 |                |                       |                      |                  |             |              |     |

|----|------------|---------------|----------------|---------------|-----------------|----------------|-----------------------|----------------------|------------------|-------------|--------------|-----|

| 0  | CO         | 0             | -              | 0             | -               | 0              | <del>-</del>          | 0                    | -                | 0           | <del>-</del> | 0   |

| -  | 5          | 0             | 0              | -             | -               | 0              | 0                     | <del>-</del>         | -                | 0           | 0            | 0   |

| 2  | CZ         | 0             | 0              | 0             | 0               | -              | <del>-</del>          | -                    | -                | 0           | 0            | 1   |

| က  | C3         | 0             | 0              | 0             | 0               | 0              | 0                     | 0                    | 0                | -           | -            | -   |

| 4  |            |               |                |               |                 |                | EN_PLL                | C3_4_ADJ<br>[2:0]    | 0                | XTL<br>MAN2 | 0            | 0   |

| 2  |            |               |                |               |                 |                | EN <sup>-</sup> ACO   | 33_4<br>[2:          | 0                | 0           | -            | 0   |

| 9  |            |               |                |               |                 |                | EN <sup>O</sup> CC    |                      | 0                | 0           | 0            | 0   |

| 7  |            |               |                | R<br>[5:0]    |                 |                | EN <sup>-</sup> ACOFD | R3_ADJ_FL<br>[1:0]   | 0                | 0           | +            | -   |

| ω  |            |               | M<br>12]       |               | Z [2            |                | EN_PLLLDO1            | R3_AI                | XTLDIV<br>[1:0]  | 0           | -            | 0   |

| 6  |            | <b>∑</b> [0   | NUM<br>[21:12] |               | DEN<br>[21:12]  |                | EN_PLLLDO2            | NDV                  | × _              | 0           | -            | 0   |

| 10 |            | NUM<br>[11:0] |                |               |                 | TOC<br>[13:0]  | EN_DIGLDO             | R3_ADJ<br>[1:0]      |                  | 0           | 0            | -   |

| =  |            |               |                |               |                 | T [            | 0                     | J_FL<br>J]           |                  | 0           | -            | 0   |

| 12 | :0]        |               |                |               |                 |                | 0                     | R4_ADJ_FL<br>[1:0]   |                  | 0           | 0            | 0   |

| 13 | DATA[19:0] |               |                |               |                 |                | 0                     | R4_ADJ<br>[1:0]      |                  | 0           | 0            | 0   |

| 41 |            |               |                |               |                 |                | 0                     | R4                   | _                | 0           | 0            | 0   |

| 15 |            |               | N<br>[10:8]    | DEN<br>[11:0] | FoLD<br>[3:0]   |                | 0                     | BTJ=qJ_N3            | XTLMAN<br>[11:0] | 0           | 0            | 0   |

| 16 |            |               |                |               | ල<br>ව          |                | 0                     |                      | ×                | -           | 0            | 1   |

| 17 |            |               |                |               |                 |                | 0                     | J_SEL                |                  | -           | LDDIV4       | 0   |

| 18 |            |               | 0]             |               | en<br>0]        |                | REG_RST               | VCO_ACI_SEL<br>[3:0] |                  | 0           | 0            | 0   |

| 19 |            |               | ICP<br>[3:0]   |               | ORDER<br>[1:0]  | <u>ا</u> ت     | 0                     | ×                    |                  | 0           | 0            | 0   |

| 20 |            | N<br>[7:0]    |                |               | ER<br>0]        | ICPFL<br>[3:0] | 0                     |                      |                  | 0           | 0            | 0   |

| 21 |            |               | PRESC16        |               | DITHER<br>[1:0] |                | 0                     | XTLSEL<br>[2:0]      |                  | 0           | 0            | 0   |

| 22 |            |               | 0              | -             | FDM             | 0              | 0                     | ×                    | 0                | 0           | 0            | 0   |

| 23 |            |               | 0              | 0             | DIV2            | 0              | <del>-</del>          | 0                    | 0                | 0           | 0            | 0   |

| 0  | אבוסוסובא  | R0            | R1             | R2            | R3              | R4             | R5                    | R6                   | R7               | R8          | R9           | R12 |

#### 2.1 REGISTER R0

Note that the action of programming the R0 register activates a calibration routine for the VCO. This calibration is necessary to get the VCO to center the tuning voltage for optimal performance. If the temperature drifts considerably, then the PLL should stay in lock, provided that the temperature drift specification is not violated.

#### 2.1.1 NUM[10:0] and NUM[21:12] -- Fractional Numerator

The NUM word is split between the R0 register and R1 register. The Numerator bits determine the fractional numerator for the delta sigma PLL. This value can go from 0 to 4095 when the FDM bit (R3[22]) is 0 (the other bits in this register are ignored), or 0 to 4194303 when the FDM bit is 1.

|            |   |   |   | N | MUM[ | 21:12 | 2] |   |   |   |   |   |   |   |   | NUM | [11:0] | ] |   |   |   |   |

|------------|---|---|---|---|------|-------|----|---|---|---|---|---|---|---|---|-----|--------|---|---|---|---|---|

| Fractional |   |   |   |   |      |       |    |   |   |   |   |   |   |   |   |     |        |   |   |   |   |   |