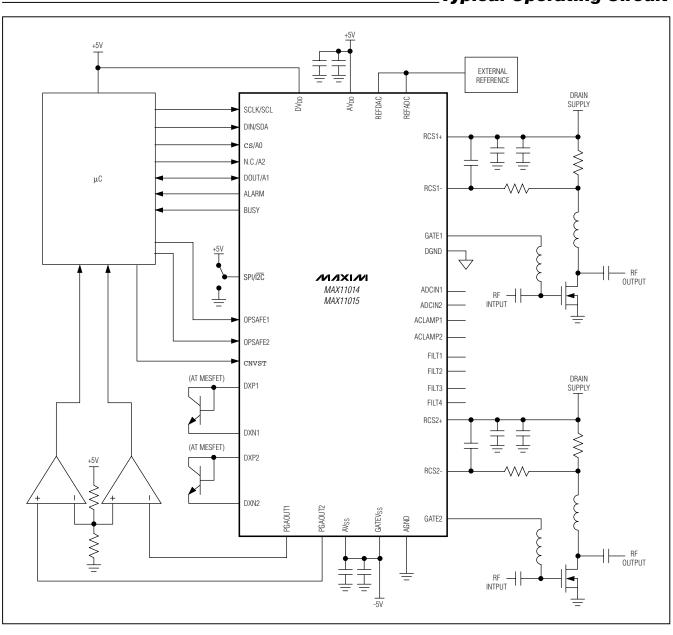

### **General Description**

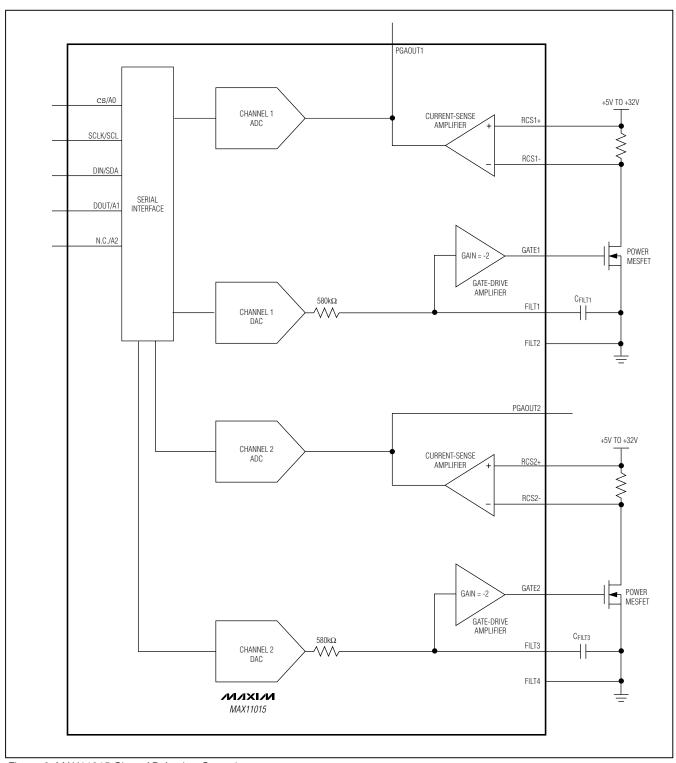

The MAX11014/MAX11015 set and control bias conditions for dual MESFET power devices found in point-topoint communication and other microwave base stations. The MAX11014 integrates complete dual analog closed-loop drain-current controllers for Class A MESFET amplifier operation, while the MAX11015 targets Class AB operation. Both devices integrate SRAM lookup tables (LUTs) that can be used to store temperature and drain-current compensation data.

Each device includes dual high-side current-sense amplifiers to monitor the MESFET drain currents through the voltage drop across the sense resistors in the 0 to 625mV range. External diode-connected transistors monitor the MESFET temperatures while an internal temperature sensor measures the local die temperature of the MAX11014/MAX11015. The internal DAC sets the voltages across the current-sense resistors by controlling the GATE voltages. The internal 12-bit SAR ADC digitizes internal and external temperature, internal DAC voltages, current-sense amplifier voltages, and external GATE voltages. Two of the 11 ADC channels are available as general-purpose analog inputs for analog system monitoring.

The MAX11014's gate-drive amplifier functions as an integrator for the Class A drain-current control loop while the MAX11015's gate-drive amplifier functions with a gain of -2 for Class AB applications. The currentlimited gate-drive amplifier can be fast clamped to an external voltage independent of the digital input from the serial interface. Both the MAX11014 and the MAX11015 include self-calibration modes to minimize error over time, temperature, and supply voltage.

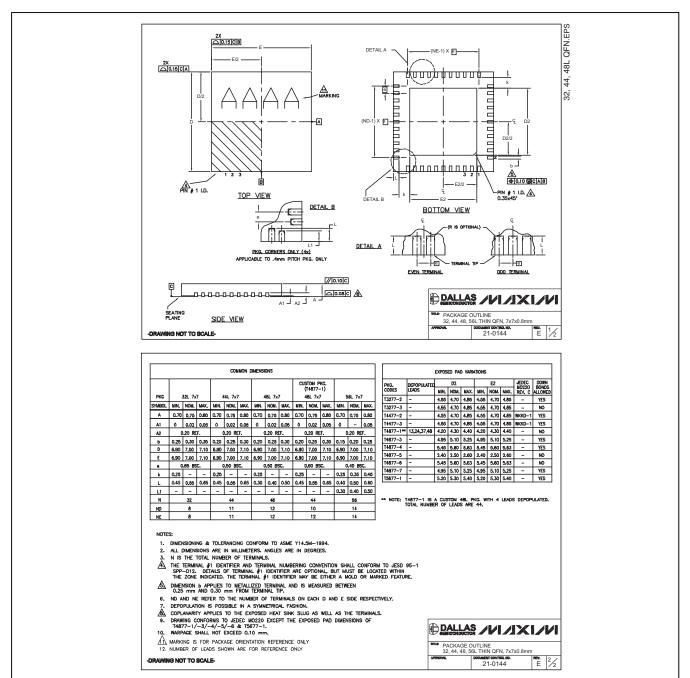

The MAX11014/MAX11015 feature an internal reference and can operate from separate ADC and DAC external references. The internal reference provides a well-regulated, low-noise +2.5V reference for the ADC, DAC, and temperature sensors. These integrated circuits operate from a 4-wire 20MHz SPITM-/MICROWIRETM-compatible or 3.4MHz I<sup>2</sup>C\*-compatible serial interface (pin-selectable). Both devices operate from a +4.75V to +5.25V analog supply (2.8mA typical supply current), a +2.7V to +5.25V digital supply (1.5mA typical supply current), and a -4.5V to -5.5V negative supply (1.1mA supply current). The MAX11014/MAX11015 are available in a 48-pin thin QFN package specified over the -40°C to +105°C temperature range.

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc. or one of its sublicensed Associated Companies, conveys a license under the Phillips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Phillips.

#### **Features**

- **♦ Dual Drain-Current-Sense Gain Amplifier** Preset Gain of 4 ±0.5% Accuracy for Sense Voltages Between 75mV and 625mV (MAX11014)

- **♦** Common-Mode Sense-Resistor Voltage Range 0.5V to 11V (MAX11014) 5V to 32V (MAX11015)

- ♦ Low-Noise Output GATE Bias with ±10mA GATE Drive

- **♦** Fast Clamp and Power-On Reset

- **♦ 12-Bit DAC Controls MESFET GATE Voltage**

- ♦ Internal Temperature Sensor/Dual Remote Diode **Temperature Sensors**

- ♦ Internal 12-Bit ADC Measures Temperature and Voltage

- ♦ Pin-Selectable Serial Interface 3.4MHz I<sup>2</sup>C-Compatible Interface 20MHz SPI-/MICROWIRE-Compatible Interface

## **Ordering Information**

| PART                   | PIN-PACKAGE      | PKG<br>CODE | AMPLIFIER |

|------------------------|------------------|-------------|-----------|

| MAX11014BGTM+          | 48 Thin QFN-EP** | T4877-6     | Class A   |

| <b>MAX11015</b> BGTM+* | 48 Thin QFN-EP** | T4877-6     | Class AB  |

<sup>+</sup> Denotes a lead-free package.

Note: All devices are specified over the -40°C to +105°C operating temperature range.

Pin Configuration and Typical Operating Circuit appear at end of data sheet.

## **Applications**

Cellular Base-Station RF MESFET Bias Controllers Point-to-Point or Point-to-Multipoint Links Industrial Process Control

SPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

MIXIM

Maxim Integrated Products 1

<sup>\*</sup>Future product—contact factory for availability.

<sup>\*\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND                        | 0.3V to +6V                     |

|-------------------------------------------------|---------------------------------|

| DV <sub>DD</sub> to DGND                        | 0.3V to +6V                     |

| AGND to DGND                                    | 0.3V to +0.3V                   |

| AVSS to AGND                                    |                                 |

| RCS1+, RCS1-, RCS2+, RCS2- to GATEVSS           |                                 |

| (MAX11014)                                      | 0.3V to +13V                    |

| RCS1+, RCS1-, RCS2+, RCS2- to AGND              |                                 |

| (MAX11015)                                      | 0.3V to +34V                    |

| RCS1- to RCS1+                                  | 6V to +0.3V                     |

| RCS2- to RCS2+                                  | 6V to +0.3V                     |

| GATEVSS to AGND                                 | +0.3V to -6V                    |

| GATE1, GATE2 to AGND(GATEV <sub>SS</sub> - 0.3V | ') to (AV <sub>DD</sub> + 0.3V) |

| DV <sub>DD</sub> to AV <sub>DD</sub> 0.3        | V to $(AV_{DD} + 0.3V)$         |

| All Other Analog Inputs to AGND0.3              | V to $(AV_{DD} + 0.3V)$         |

|                                                 |                                 |

| PGAOUT1, PGAOUT2 to AGND0.3V to (AV <sub>DD</sub> + 0.3V) SCLK/SCL, DIN/SDA, CS/A0, N.C./A2, CNVST, OPSAFE1, |

|--------------------------------------------------------------------------------------------------------------|

| OPSAFE2 to DGND0.3V to (DV <sub>DD</sub> + 0.3V)                                                             |

| DOUT/A1, SPI/I2C, ALARM, BUSY                                                                                |

| to DGND0.3V to (DV <sub>DD</sub> + 0.3V)                                                                     |

| Maximum Current into Any Pin50mA                                                                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                                                        |

| 48-Pin Thin QFN (derate 27.0mW/°C                                                                            |

| above +70°C)2162.2mW                                                                                         |

| Operating Temperature Range40°C to +105°C                                                                    |

| Storage Temperature Range60°C to 150°C                                                                       |

| Junction Temperature+150°C                                                                                   |

| Lead Temperature (soldering, 10s)+300°C                                                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{\text{GATEVSS}} = V_{\text{AVSS}} = -5.5 \text{V to } -4.75 \text{V}, \ V_{\text{AVDD}} = +4.75 \text{V to } +5.25 \text{V}, \ V_{\text{DVDD}} = +2.7 \text{V to } \ V_{\text{AVDD}}, \ \text{external } \ V_{\text{REFADC}} = +2.5 \text{V}, \ \text{C}_{\text{REFADC}} = -5.5 \text{V}, \ \text{C}_{\text{REFADC}} = -5.5 \text{V}, \ \text{C}_{\text{REFADC}} = -5.5 \text{V}, \ \text{C}_{\text{FILT1}} = -5.5 \text{V}, \ \text{C}_{\text{FILT2}} = -5.5 \text{V}, \ \text{C}_{\text{FILT3}} = -5.5 \text{V}, \ \text{C}_{\text{FILT4}} = -5.5 \text{V}, \ \text{C}_{\text{FILT5}} = -$

| PARAMETER                      | SYMBOL             | CONDITIONS                                                 | MIN | TYP  | MAX  | UNITS   |

|--------------------------------|--------------------|------------------------------------------------------------|-----|------|------|---------|

| CURRENT-SENSE AMPLIFIER (I     | Note 1)            |                                                            |     |      |      |         |

| Common-Mode Input Voltage      | \/p.o.o            | MAX11014                                                   | 0.5 |      | 11.0 | V       |

| Range                          | V <sub>RCS+</sub>  | MAX11015                                                   | 5   |      | 32   | ]       |

| Common-Mode Rejection Ratio    | CMRR               | 0.5V < V <sub>RCS_+</sub> < 11V for the MAX11014           |     | 90   |      | dB      |

| Common-Mode nejection natio    | CIVINN             | 5V < V <sub>RCS_+</sub> < 32V for the MAX11015             |     | 90   |      | αБ      |

| Input Dice Current             | I <sub>RCS+</sub>  | V <sub>SENSE</sub> < 100mV over the common-mode            |     |      | 200  |         |

| Input-Bias Current             | I <sub>RCS</sub> - | range                                                      |     |      | ±2   | μΑ      |

| Full-Scale Sense Voltage       | VSENSE             | V <sub>SENSE</sub> = V <sub>RCS+</sub> - V <sub>RCS-</sub> |     |      | 625  | mV      |

|                                |                    | To within ±0.5% accuracy                                   | 75  |      | 625  |         |

| Sense Voltage Range            |                    | To within ±2% accuracy                                     | 20  |      | 625  | mV      |

|                                |                    | To within ±20% accuracy                                    | 2   |      | 625  |         |

| Total Current Set Error        |                    | V <sub>SENSE</sub> = 75mV                                  |     | ±0.1 | ±0.5 | %       |

| Current-Sense Settling Time    | tHSCS              | Settles to within ±0.5% of final value                     |     | < 25 |      | μs      |

| Saturation Recovery Time       |                    | Settles to within ±0.5% accuracy, from VSENSE = 1.875V     |     | < 45 |      | μs      |

| CLASS AB INPUT CHANNEL         |                    |                                                            |     |      |      |         |

| Untrimmed Offset               |                    |                                                            |     | 19   |      | Bits    |

| Offset Temperature Coefficient |                    |                                                            |     | 0    |      | Bits/°C |

| Gain                           |                    |                                                            |     | 4    |      |         |

| Gain Error                     |                    |                                                            |     | 0.1  |      | %       |

\_\_ /N/XI/M

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{GATEVSS} = V_{AVSS} = -5.5V \ to \ -4.75V, \ V_{AVDD} = +4.75V \ to \ +5.25V, \ V_{DVDD} = +2.7V \ to \ V_{AVDD}, \ external \ V_{REFADC} = +2.5V, \ external \ V_{REFADC} = -5.5V, \ C_{REFADC} = -5.5V, \ C_{REFADC}$

| PARAMETER                               | SYMBOL             | CONDITIONS                                                                                                                                                                                             | MIN        | TYP    | MAX   | UNITS  |

|-----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------|--------|

| CLASS AB OUTPUT CHANNEL                 | •                  | ·                                                                                                                                                                                                      |            |        |       |        |

| Untrimmed Offset                        |                    | (Note 1)                                                                                                                                                                                               |            | 50     |       | μV     |

| Offset Temperature Coefficient          |                    |                                                                                                                                                                                                        |            | 0      |       | mV/°C  |

| Gain                                    |                    |                                                                                                                                                                                                        |            | -2     |       |        |

| Gain Error                              |                    |                                                                                                                                                                                                        |            | 0.1    |       | %      |

| GATE-DRIVE AMPLIFIER/INTEGR             | RATOR              |                                                                                                                                                                                                        |            |        |       |        |

|                                         |                    | IGATE = -1mA                                                                                                                                                                                           | VGATEVSS 1 | -      |       | V      |

| Output Gate-Drive Voltage Range         | M                  | IGATE = +1mA                                                                                                                                                                                           |            | -0.15  | -4    | mV     |

| (Note 2)                                | VGATE              | IGATE = -10mA                                                                                                                                                                                          | VGATEVSS + | -      |       | V      |

|                                         |                    | IGATE = +10mA                                                                                                                                                                                          |            | -1     | -20   | mV     |

| Gate Voltage Settling Time—<br>MAX11015 | tgate              | Settles to within $\pm 0.5\%$ of final value, R <sub>S</sub> = $50\Omega$ , C <sub>GATE</sub> = $15\mu$ F, see GATE Output Resistance vs. GATE Voltage in the <i>Typical Operating Characteristics</i> |            | 1.1    |       | ms     |

| Outside Consolition Local (Notes O)     | 0.5                | No series resistance, $R_S = 0\Omega$                                                                                                                                                                  | 0          |        | 0.5   |        |

| Output Capacitive Load (Note 3)         | CGATE              | $R_S = 500\Omega$                                                                                                                                                                                      | 0          | 15,000 |       | nF     |

| Gate Voltage Noise                      |                    | RMS noise, 1kHz to 1MHz                                                                                                                                                                                |            | 250    |       | nV/√Hz |

| Maximum Power-On Transient              |                    | C <sub>LOAD</sub> = 1nF                                                                                                                                                                                |            | ±100   |       | mV     |

| Output Short-Circuit Current Limit      | Isc                | Sinking or sourcing                                                                                                                                                                                    |            | ±25    |       | mA     |

| Output Safe Switch On-<br>Resistance    | Ropsw              | Clamp GATE1 to ACLAMP1, GATE2 to ACLAMP2 (Note 4)                                                                                                                                                      |            |        | 3.6   | kΩ     |

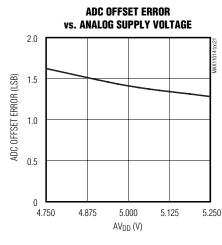

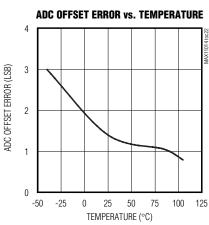

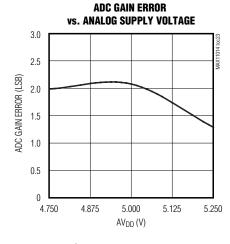

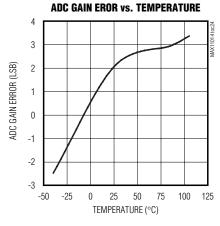

| ADC DC ACCURACY                         |                    |                                                                                                                                                                                                        |            |        |       |        |

| Resolution                              |                    |                                                                                                                                                                                                        | 12         |        |       | Bits   |

| Differential Nonlinearity               | DNL <sub>ADC</sub> | No missing codes                                                                                                                                                                                       |            |        | ±1    | LSB    |

| Integral Nonlinearity                   | INL <sub>ADC</sub> | (Note 5)                                                                                                                                                                                               |            |        | ±1.25 | LSB    |

| Offset Error                            |                    |                                                                                                                                                                                                        |            | ±2     | ±4    | LSB    |

| Gain Error                              |                    | (Note 6)                                                                                                                                                                                               |            | ±2     | ±4    | LSB    |

| Gain Temperature Coefficient            |                    |                                                                                                                                                                                                        |            | ±0.4   |       | ppm/°C |

| Offset Temperature Coefficient          |                    |                                                                                                                                                                                                        |            | ±0.4   |       | ppm/°C |

| Channel-to-Channel Offset Matching      |                    |                                                                                                                                                                                                        |            | ±0.1   |       | LSB    |

| Channel-to-Channel Gain<br>Matching     |                    |                                                                                                                                                                                                        |            | ±0.1   |       | LSB    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{GATEVSS} = V_{AVSS} = -5.5V \text{ to } -4.75V, V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +2.7V \text{ to } V_{AVDD}, \text{ external } V_{REFADC} = +2.5V, C_{REFADC} = -2.5V, C_{REFADC} =$

| PARAMETER                                          | SYMBOL          | CONDITIONS                                                    | MIN    | TYP    | MAX     | UNITS  |

|----------------------------------------------------|-----------------|---------------------------------------------------------------|--------|--------|---------|--------|

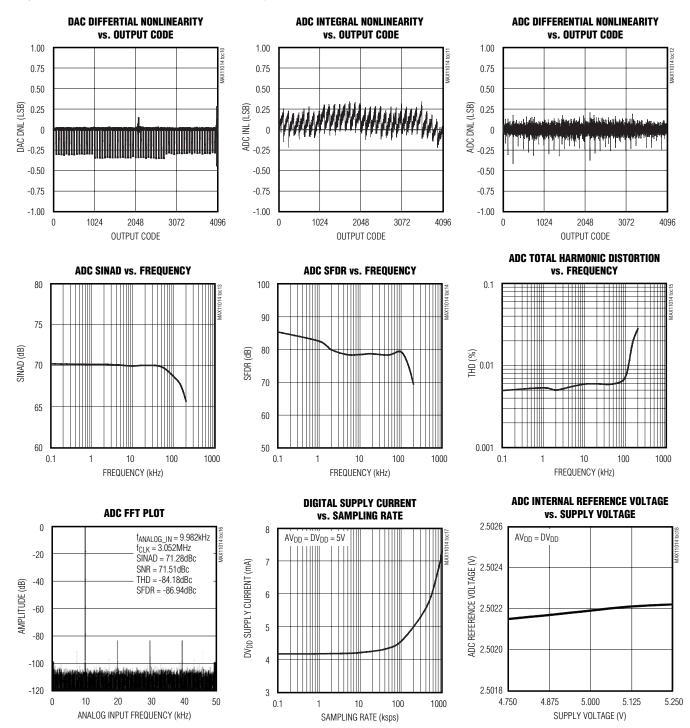

| ADC DYNAMIC ACCURACY (1ki                          | dz sine-wave    | input, -0.5dB from full scale, 94.4ksps)                      |        |        |         |        |

| Signal-to-Noise Plus Distortion                    | SINAD           |                                                               |        | 70     |         | dB     |

| Total Harmonic Distortion                          | THD             | Up to the 5th harmonic                                        |        | -84    |         | dB     |

| Spurious-Free Dynamic Range                        | SFDR            |                                                               |        | 86     |         | dB     |

| Intermodulation Distortion                         | IMD             | $f_{IN1} = 9.9kHz$ , $f_{IN2} = 10.2kHz$                      |        | 76     |         | dB     |

| Full-Power Bandwidth                               |                 | -3dB point                                                    |        | 1      |         | MHz    |

| Full-Linear Bandwidth                              |                 | S/(N + D) > 68dB                                              |        | 100    |         | kHz    |

| ADC CONVERSION RATE                                |                 |                                                               |        |        |         |        |

| Power-Up Time                                      | +               | External reference                                            |        | 0.8    |         |        |

| Power-op Time                                      | t <sub>PU</sub> | Internal reference                                            |        | 50     |         | μs     |

| Acquisition Time (Note 3)                          | t. 0.0          | GATE_ and sense voltage measurements                          | 40     |        |         |        |

| Acquisition Time (Note 3)                          | tacq            | All other measurements                                        | 1.5    |        |         | μs     |

| Conversion Time                                    | tconv           | Internally clocked                                            |        |        | 6.5     | μs     |

| Aperture Delay                                     |                 |                                                               |        | 30     |         | ns     |

| ADCIN1, ADCIN2 INPUTS                              |                 |                                                               |        |        |         |        |

| Input Range                                        | VADCIN_         | Relative to AGND (Note 7)                                     | 0      |        | VREFADC | V      |

| Input Leakage Current                              |                 | VADCIN_ = 0V or VAVDD                                         |        | ±0.01  | ±1      | μΑ     |

| Input Capacitance                                  | CADCIN_         |                                                               |        | 34     |         | pF     |

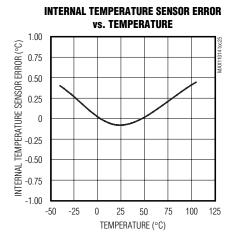

| TEMPERATURE MEASUREMEN                             | TS              |                                                               |        |        |         |        |

|                                                    |                 | $T_J = +25^{\circ}C$                                          |        | ±0.25  |         |        |

| Internal Sensor Measurement Error                  |                 | $T_J = -40$ °C to $+85$ °C (Note 3)                           |        | ±1.0   | ±2.5    | °C     |

|                                                    |                 | $T_J = -40^{\circ}\text{C to} + 105^{\circ}\text{C (Note 3)}$ |        | ±1.0   | ±3.5    |        |

| External Sensor Measurement                        |                 | $T_J = +25^{\circ}C$                                          |        | ±1.0   |         | °C     |

| Error (Note 8)                                     |                 | $T_{J} = -40^{\circ}\text{C to } +105^{\circ}\text{C}$        |        | ±3     |         |        |

| Temperature Resolution                             |                 |                                                               |        | 0.125  |         | °C/LSB |

| External Diode Drive                               |                 |                                                               | 3.26   |        | 75.00   | μΑ     |

| External Temperature Sensor<br>Drive Current Ratio |                 |                                                               |        | 16.6   |         |        |

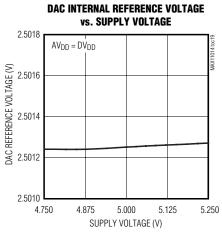

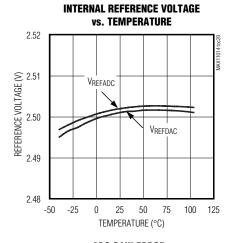

| INTERNAL REFERENCE                                 |                 |                                                               |        |        |         |        |

| Reference Output Voltage                           |                 | VREFADC = VREFDAC                                             | +2.490 | +2.500 | +2.510  | V      |

| Reference Output Temperature<br>Coefficient        |                 |                                                               |        | ±15    |         | ppm/°C |

| Reference Output Impedance                         |                 |                                                               |        | 6.5    |         | kΩ     |

| Power-Supply Rejection Ratio                       | PSRR            | V <sub>AVDD</sub> = +5V ±5%                                   |        | -83    |         | dB     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{GATEVSS} = V_{AVSS} = -5.5V \ to \ -4.75V, \ V_{AVDD} = +4.75V \ to \ +5.25V, \ V_{DVDD} = +2.7V \ to \ V_{AVDD}, \ external \ V_{REFADC} = +2.5V, \ external \ V_{REFADC} = -5.5V, \ C_{REFADC} = -5.5V, \ C_{REFADC$

| PARAMETER                  | SYMBOL              | CONDITIONS                                                                                                   | MIN                       | TYP                        | MAX                       | UNITS |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|---------------------------|-------|

| EXTERNAL REFERENCES        | •                   |                                                                                                              | ч                         |                            |                           |       |

| REFADC Input Voltage Range | VREFADC             |                                                                                                              | +1.0                      |                            | V <sub>A</sub> VDD        | V     |

| DEEADOL 10                 |                     | VREFADC = +2.5V, fSAMPLE = 178ksps                                                                           |                           | 60                         |                           |       |

| REFADC Input Current       | IREFADC             | Acquisition/between conversions                                                                              |                           | ±0.01                      |                           | μΑ    |

| REFDAC Input Voltage Range | VREFDAC             |                                                                                                              | +0.50                     |                            | +2.52                     | V     |

| REFDAC Input Current       |                     |                                                                                                              |                           | 26                         |                           | μΑ    |

| DAC DC ACCURACY            |                     |                                                                                                              | •                         |                            |                           |       |

| Resolution                 |                     |                                                                                                              | 12                        |                            |                           | Bits  |

| Integral Nonlinearity      | INLDAC              | Measured at FILT_                                                                                            |                           | ±1                         |                           | LSB   |

| Differential Nonlinearity  | DNLDAC              | Measured at FILT_, guaranteed monotonic                                                                      |                           | ±0.4                       | ±1                        | LSB   |

| POWER SUPPLIES             |                     |                                                                                                              | •                         |                            |                           |       |

| Analog Supply Voltage      | V <sub>A</sub> VDD  |                                                                                                              | +4.75                     |                            | +5.25                     | V     |

| Digital Supply Voltage     | V <sub>DVDD</sub>   |                                                                                                              | +2.7                      |                            | AV <sub>DD</sub>          | V     |

| Negative Supply Voltage    | VGATEVSS,<br>VAVSS  | VGATEVSS = VAVSS                                                                                             | -5.50                     |                            | -4.75                     | V     |

| Analog Supply Current      | I <sub>AVDD</sub>   | $V_{AVDD} = +5.25V$                                                                                          |                           | 2.8                        | 5                         | mA    |

| Digital Supply Current     | I <sub>DVDD</sub>   | V <sub>DVDD</sub> = +5.25V                                                                                   |                           | 1.5                        | 5                         | mA    |

| Negative Supply Current    | IGATEVSS<br>+ IAVSS | VGATEVSS = VAVSS = -5.5V                                                                                     |                           | 1.1                        | 1.7                       | mA    |

| Analog Shutdown Current    |                     | V <sub>AVDD</sub> = +5.25V                                                                                   |                           | 0.8                        |                           | μΑ    |

| Digital Shutdown Current   |                     | V <sub>DVDD</sub> = +5.25V                                                                                   |                           | 0.2                        |                           | μΑ    |

| Negative Shutdown Current  |                     | VGATEVSS = VAVSS = -5.5V                                                                                     |                           | 0.6                        |                           | μA    |

| SERIAL-INTERFACE SUPPLIES  | ;<br>;              |                                                                                                              | •                         |                            |                           |       |

| Leave A Wallana            | VIL                 |                                                                                                              |                           |                            | 0.3 x<br>DV <sub>DD</sub> | V     |

| Input Voltage              | VIH                 |                                                                                                              | 0.7 x<br>DV <sub>DD</sub> |                            |                           | V     |

| Input Hysteresis           | VHYS                |                                                                                                              |                           | 0.05 x<br>DV <sub>DD</sub> |                           | ٧     |

| Output Low Voltage         | VoL                 | BUSY: I <sub>SINK</sub> = 0.5mA;<br>DOUT, ALARM: I <sub>SINK</sub> = 3mA                                     |                           |                            | 0.4                       | V     |

| Output High Voltage        | Voн                 | SPI/IZC = DV <sub>DD</sub> ;<br>BUSY: I <sub>SOURCE</sub> = 0.5mA;<br>DOUT, ALARM: I <sub>SOURCE</sub> = 2mA | DV <sub>DD</sub> - 0.5V   |                            |                           | V     |

| Input Current              | I <sub>IN</sub>     |                                                                                                              |                           | ±0.01                      | ±10                       | μΑ    |

|                            |                     |                                                                                                              |                           |                            |                           |       |

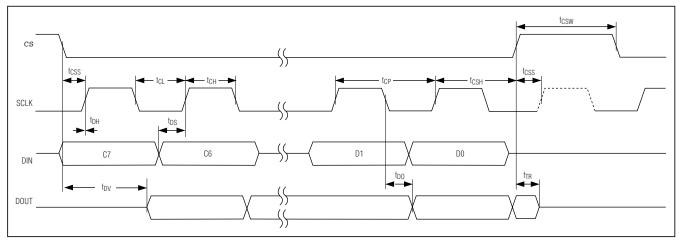

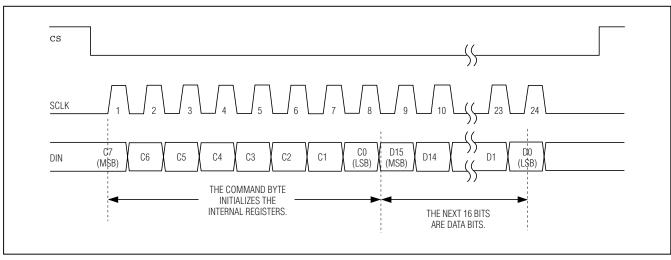

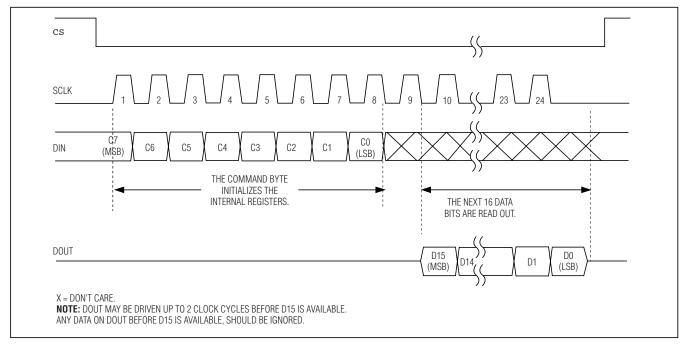

### **SPI-INTERFACE TIMING CHARACTERISTICS**

(Note 9) (See Figure 1.)

| PARAMETER                    | SYMBOL          | CONDITIONS                      | MIN | TYP | MAX | UNITS |

|------------------------------|-----------------|---------------------------------|-----|-----|-----|-------|

| SCLK Clock Period            | tcp             |                                 | 40  |     |     | ns    |

| SCLK High Time               | tсн             |                                 | 16  |     |     | ns    |

| SCLK Low Time                | tCL             |                                 | 16  |     |     | ns    |

| DIN to SCLK Rise Setup Time  | t <sub>DS</sub> |                                 | 10  |     |     | ns    |

| DIN to SCLK Rise Hold Time   | tDH             |                                 | 0   |     |     | ns    |

| SCLK Fall to DOUT Transition | t <sub>DO</sub> | $C_L = 30pF$                    |     |     | 20  | ns    |

| CS Fall to DOUT Enable       | t <sub>DV</sub> | C <sub>L</sub> = 30pF (Note 3)  |     |     | 40  | ns    |

| CS Rise to DOUT Disable      | t <sub>TR</sub> | C <sub>L</sub> = 30pF (Note 10) |     |     | 40  | ns    |

| CS Rise or Fall to SCLK Rise | tcss            |                                 | 10  |     |     | ns    |

| CS Pulse-Width High          | tcsw            | (Note 3)                        | 40  |     |     | ns    |

| Last SCLK Rise to CS Rise    | tcsh            | (Note 3)                        | 0   |     |     | ns    |

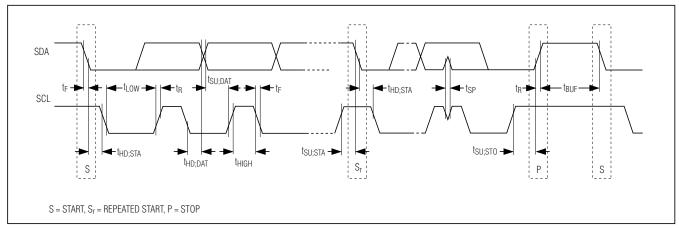

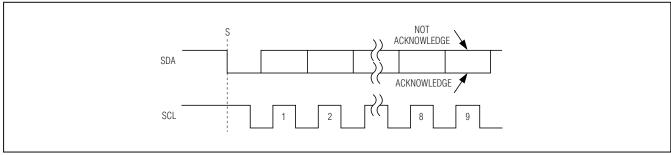

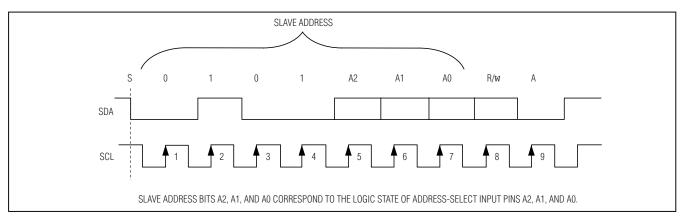

## I<sup>2</sup>C-INTERFACE SLOW-/FAST-MODE TIMING CHARACTERISTICS

(Note 9) (See Figure 2.)

| PARAMETER                                               | SYMBOL         | CONDITIONS                                            | MIN                       | TYP MAX | UNITS |

|---------------------------------------------------------|----------------|-------------------------------------------------------|---------------------------|---------|-------|

| SCL Clock Frequency                                     | fscl           |                                                       | 0                         | 400     | kHz   |

| Bus Free Time Between a STOP and START Condition        | tBUF           |                                                       | 1.3                       |         | μs    |

| Hold Time (Repeated) for START Condition                | thd;sta        | After this period, the first clock pulse is generated | 0.6                       |         | μs    |

| Setup Time for a Repeated START Condition               | tsu;sta        |                                                       | 0.6                       |         | μs    |

| SCL Pulse-Width Low                                     | tLOW           |                                                       | 1.3                       |         | μs    |

| SCL Pulse-Width High                                    | thigh          |                                                       | 0.6                       |         | μs    |

| Data Setup Time                                         | tsu;dat        |                                                       | 100                       |         | ns    |

| Data Hold Time                                          | thd;dat        | (Note 11)                                             | 0                         | 0.9     | μs    |

| SDA, SCL Rise Time, Receiving                           | t <sub>R</sub> | (Notes 3, 12)                                         | 0                         | 300     | ns    |

| SDA, SCL Fall Time, Receiving                           | t <sub>F</sub> | (Notes 3, 12)                                         | 0                         | 300     | ns    |

| SDA Fall Time, Transmitting                             | t <sub>F</sub> | (Notes 3, 12, 13)                                     | 20 + 0.1 x C <sub>B</sub> | 250     | ns    |

| Setup Time for STOP Condition                           | tsu;sto        |                                                       | 0.6                       |         | μs    |

| Capacitive Load for Each Bus Line                       | CB             | (Notes 3, 14)                                         |                           | 400     | рF    |

| Pulse Width of Spikes Suppressed<br>By the Input Filter | tsp            | (Note 15)                                             |                           | 50      | ns    |

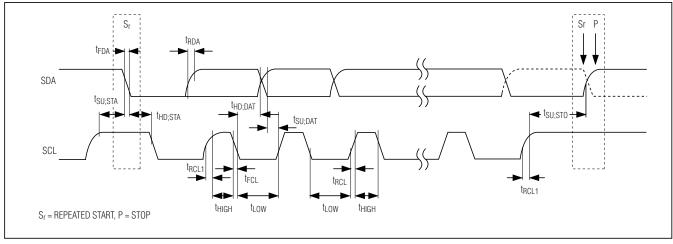

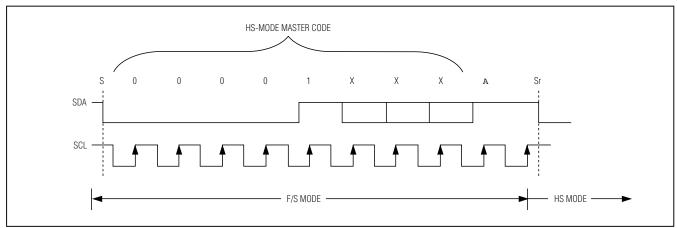

## I<sup>2</sup>C-WIRE-INTERFACE HIGH-SPEED-MODE TIMING CHARACTERISTICS

(Note 9) (See Figure 3.)

| PARAMETER                                                                          | SYMBOL           | CONDITIONS | C <sub>B</sub> = 10 | 0pF max | C <sub>B</sub> = | 400pF | UNITS |

|------------------------------------------------------------------------------------|------------------|------------|---------------------|---------|------------------|-------|-------|

| PARAMETER                                                                          | SYMBOL           | CONDITIONS | MIN                 | MAX     | MIN              | MAX   | UNITS |

| Serial Clock Frequency                                                             | fscl             |            | 0                   | 3.4     | 0                | 1.7   | MHz   |

| Setup Time (Repeated) START Condition                                              | tsu;sta          |            | 160                 |         | 160              |       | ns    |

| Hold Time (Repeated) START<br>Condition                                            | thd;sta          |            | 160                 |         | 160              |       | ns    |

| SCL Pulse-Width Low                                                                | tLOW             |            | 160                 |         | 320              |       | ns    |

| SCL Pulse-Width High                                                               | tHIGH            |            | 60                  |         | 120              |       | ns    |

| Data Setup Time                                                                    | tsu;dat          |            | 10                  |         | 10               |       | ns    |

| Data Hold Time                                                                     | thd;dat          | (Note 11)  | 0                   | 70      | 0                | 150   | ns    |

| SCL Rise Time                                                                      | tRCL             | (Note 3)   | 10                  | 40      | 20               | 80    | ns    |

| SCL Rise Time, After a Repeated<br>START Condition and After an<br>Acknowledge Bit | tRCL1            | (Note 3)   | 10                  | 80      | 20               | 160   | ns    |

| SCL Fall Time                                                                      | tFCL             | (Note 3)   | 10                  | 40      | 20               | 80    | ns    |

| SDA Rise Time                                                                      | t <sub>RDA</sub> | (Note 3)   | 10                  | 80      | 20               | 160   | ns    |

| SDA Fall Time                                                                      | t <sub>FDA</sub> | (Note 3)   | 10                  | 80      | 20               | 160   | ns    |

| Setup Time for STOP Condition                                                      | tsu;sto          |            | 160                 |         | 160              |       | ns    |

| Capacitive Load for Each Bus Line                                                  | CB               | (Note 14)  |                     | 100     |                  | 400   | рF    |

| Pulse Width of Spikes Suppressed<br>By the Input Filter                            | tsp              | (Note 15)  | 0                   | 10      | 0                | 10    | ns    |

## **MISCELLANEOUS TIMING CHARACTERISTICS**

| PARAMETER                                                                                           | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

| Minimum Time to Wait After a<br>Write Command Before<br>Reading Back Data from the<br>Same Location | tRDBK               | (Note 16)  |     | 1   |     | μs    |

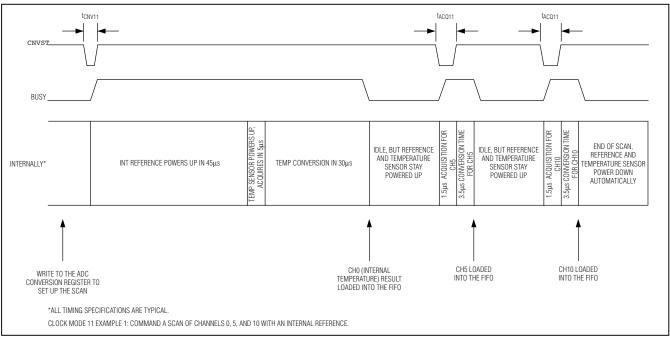

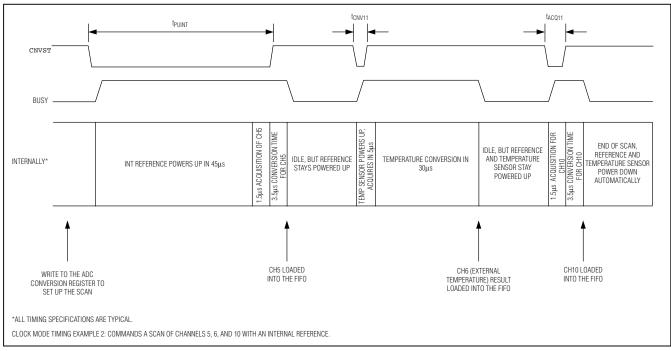

| CNVST Active-Low Pulse<br>Width in ADC Clock Mode 01                                                | tCNV01              | (Note 3)   | 20  |     |     | ns    |

| CNVST Active-Low Pulse Width in ADC Clock Mode 11 to Initiate a Temperature Conversion              | <sup>†</sup> CNV11  | (Note 3)   | 20  |     |     | ns    |

| CNVST Active-Low Pulse<br>Width in ADC Clock Mode 11<br>for ADCIN1/2 Acquisition                    | tACQ11A             | (Note 3)   | 1.5 |     |     | μs    |

| ADC Power-Up Time (External Reference)                                                              | tapuext             |            |     | 0.8 |     | μs    |

| ADC Power-Up Time (Internal Reference)                                                              | tapuint             |            |     | 50  |     | μs    |

| DAC Power-Up Time (External Reference)                                                              | t <sub>DPUEXT</sub> |            |     | 2   |     | μs    |

| DAC Power-Up Time (Internal Reference)                                                              | tdpuint             |            |     | 50  |     | μs    |

| Acquisition Time (Internally<br>Timed in ADC Clock Modes<br>00 or 01)                               | tACQ                |            |     |     | 0.6 | μs    |

| Conversion Time (Internally Clocked)                                                                | tCONV               |            |     |     | 6.5 | μs    |

| Delay to Start of Conversion<br>Time                                                                | tCONVW              | (Note 17)  |     | 1   |     | μs    |

| Temperature Conversion Time (Internally Clocked)                                                    | tCONVT              |            |     | 30  |     | μs    |

## **MISCELLANEOUS TIMING CHARACTERISTICS (continued)**

- **Note 1:** All current-sense amplifier specifications are tested after a current-sense calibration (valid when drain current = 0mA). See RCS Error vs. GATE Current in the *Typical Operating Characteristics*. The calibration is valid only at one temperature and supply voltage and must be repeated if either the temperature or supply voltage changes.

- Note 2: The hardware configuration register's CH\_OCM1 and CH\_OCM0 bits are set to 0. See Table 10a. The max specification is limited by tester limitations.

- Note 3: Guaranteed by design. Not production tested.

- Note 4: At power-on reset, the output safe switch is closed. See the ALMHCFG (Read/Write) section.

- **Note 5:** Integral nonlinearity is the deviation of the analog value at any code from its theoretical value after the gain and offset errors have been calibrated out.

- Note 6: Offset nulled.

- **Note 7:** Absolute range for analog inputs is from 0 to V<sub>AVDD</sub>.

- Note 8: Device and sensor at the same temperature. Verified by the current ratio (see the Temperature Measurements section).

- **Note 9:** All timing specifications referred to V<sub>IH</sub> or V<sub>IL</sub> levels.

- Note 10: DOUT goes into tri-state mode after the  $\overline{\text{CS}}$  rising edge. Keep  $\overline{\text{CS}}$  low long enough for the DOUT value to be sampled before it goes to tri-state.

- Note 11: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

- Note 12: t<sub>R</sub> and t<sub>F</sub> measured between 0.3 x DV<sub>DD</sub> and 0.7 x DV<sub>DD</sub>.

- Note 13: C<sub>B</sub> = total capacitance of one bus line in pF. For bus loads between 100pF and 400pF, the timing parameters should be linearly interpolated.

- **Note 14:** An appropriate bus pullup resistance must be selected depending on board capacitance. For more information, refer to the I<sup>2</sup>C documentation on the Philips website.

- Note 15: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

- **Note 16:** When a command is written to the serial interface, it is passed to the internal oscillator clock to be executed. There is a small synchronization delay before the new value is written to the appropriate register. If the user attempts to read the new value back before transfer to harm will be caused to the data, but the read command may not yet show the new value.

- Note 17: This is the minimum time from the end of a command before CNVST should be asserted. The time allows for the data from the preceding write to arrive and set up the chip in preparation for the CNVST. The time need only be observed when the write affects the ADC controls. Failure to observe this time may lead to incorrect conversions (for example, conversion of the wrong ADC channel).

Figure 1. SPI Serial-Interface Timing Diagram

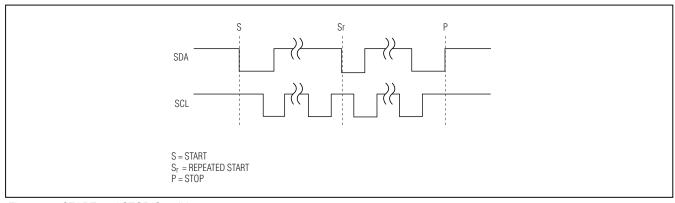

Figure 2. Slow-/Fast-Speed Timing Diagram

Figure 3. High-Speed Timing Diagram

00 \_\_\_\_\_\_\_ **/\| \| X\| /\|**

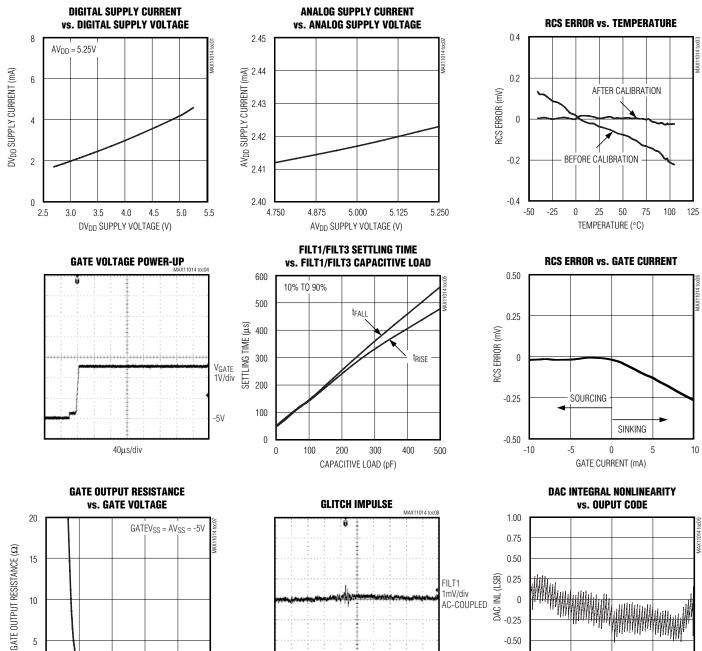

## Typical Operating Characteristics

-0.75 -1.00

0

1024

2048

OUTPUT CODE

$(V_{GATEVSS} = -5.5V; V_{AVDD} = V_{DVDD} = +5V, GATEV_{SS} = AV_{SS} = -5V, external V_{REFADC} = +2.5V; external V_{REFDAC} = +2.5V; C_{REF} = 0.1 \mu F; T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)$

1μs/div

-3

V<sub>GATE</sub> (V)

-2

0

4096

3072

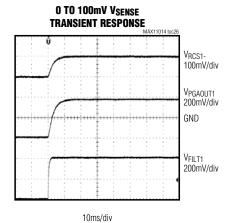

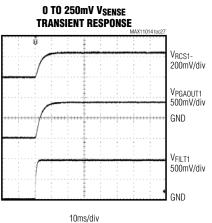

## Typical Operating Characteristics (continued)

$(V_{GATEVSS} = -5.5V; V_{AVDD} = V_{DVDD} = +5V, GATEV_{SS} = AV_{SS} = -5V, external V_{REFADC} = +2.5V; external V_{REFDAC} = +2.5V; C_{REF} = 0.1 \mu F; T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{GATEVSS} = -5.5V; V_{AVDD} = V_{DVDD} = +5V, GATEV_{SS} = AV_{SS} = -5V, external V_{REFADC} = +2.5V; external V_{REFDAC} = +2.5V; C_{REF} = 0.1 \mu F; T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)$

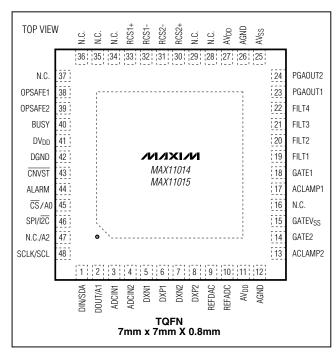

## Pin Description

| PIN                  | NAME                | FUNCTION                                                                                                                                                                                                                                                                       |

|----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | DIN/SDA             | Serial Data Input. Data is latched into the serial interface on the rising edge of SCLK in SPI mode. Connect a pullup resistor to SDA in I <sup>2</sup> C mode.                                                                                                                |

| 2                    | DOUT/A1             | Serial Data Output in SPI Mode/Address Select 1 in I <sup>2</sup> C Mode. Data transitions on the falling edge of SCLK. DOUT is high impedance when $\overline{\text{CS}}$ is high. Connect A1 to DV <sub>DD</sub> or DGND to set the device address to I <sup>2</sup> C mode. |

| 3                    | ADCIN1              | Analog Input 1                                                                                                                                                                                                                                                                 |

| 4                    | ADCIN2              | Analog Input 2                                                                                                                                                                                                                                                                 |

| 5                    | DXN1                | Remote-Diode Current Sink. Connect the emitter of a base-emitter junction remote npn transistor to DXN1.                                                                                                                                                                       |

| 6                    | DXP1                | Remote-Diode Current Source. Connect DXP1 to the base/collector of a remote temperature-sensing npn transistor. <b>Do not leave DXP1 open</b> ; connect to DXN1 if no remote diode is used.                                                                                    |

| 7                    | DXN2                | Remote-Diode Current Sink. Connect the emitter of a base-emitter junction remote npn transistor to DXN2.                                                                                                                                                                       |

| 8                    | DXP2                | Remote-Diode Current Source. Connect DXP2 to the base/collector of a remote temperature-sensing npn transistor. <b>Do not leave DXP2 open</b> ; connect to DXN2 if no remote diode is used.                                                                                    |

| 9                    | REFDAC              | DAC Reference Input/Output. Connect a 0.1µF capacitor to AGND in external reference mode. See the HCFG (Read/Write) section.                                                                                                                                                   |

| 10                   | REFADC              | ADC Reference Input/Output. Connect a 0.1µF capacitor to AGND in external reference mode. See the HCFG (Read/Write) section.                                                                                                                                                   |

| 11, 27               | AV <sub>DD</sub>    | Positive Analog Supply Voltage. Set AV <sub>DD</sub> between +4.75V and +5.25V. Bypass with a 1µF and a 0.1µF capacitor in parallel to AGND.                                                                                                                                   |

| 12, 26               | AGND                | Analog Ground                                                                                                                                                                                                                                                                  |

| 13                   | ACLAMP2             | MESFET2 External Clamping Voltage Input                                                                                                                                                                                                                                        |

| 14                   | GATE2               | MESFET2 Gate Connection. See the <i>Gate-Drive Amplifiers</i> section.                                                                                                                                                                                                         |

| 15                   | GATEV <sub>SS</sub> | Gate-Drive Amplifier Negative Power-Supply Input. Set GATEVSS between -4.75V and -5.5V. Connect externally to AVSS. Bypass with a $1\mu F$ and a $0.1\mu F$ capacitor in parallel to AGND.                                                                                     |

| 16, 28, 29,<br>34–37 | N.C.                | No Connection. Not internally connected.                                                                                                                                                                                                                                       |

| 17                   | ACLAMP1             | MESFET1 External Clamping Voltage Input                                                                                                                                                                                                                                        |

| 18                   | GATE1               | MESFET1 Gate Connection. See the Gate-Drive Amplifiers section.                                                                                                                                                                                                                |

| 19                   | FILT1               | Channel 1 Filter 1 Input. See Figures 5 and 6.                                                                                                                                                                                                                                 |

| 20                   | FILT2               | Channel 1 Filter 2 Input. See Figures 5 and 6.                                                                                                                                                                                                                                 |

| 21                   | FILT3               | Channel 2 Filter 3 Input. See Figures 5 and 6.                                                                                                                                                                                                                                 |

| 22                   | FILT4               | Channel 2 Filter 4 Input. See Figures 5 and 6.                                                                                                                                                                                                                                 |

| 23                   | PGAOUT1             | Channel 1 Amplifier Voltage Output. See the PGAOUT Outputs section and Figures 5 and 6.                                                                                                                                                                                        |

| 24                   | PGAOUT2             | Channel 2 Amplifier Voltage Output. See the <i>PGAOUT Outputs</i> section and Figures 5 and 6.                                                                                                                                                                                 |

| 25                   | AVSS                | Negative Analog Supply Voltage. Set AV <sub>SS</sub> between -4.75V and -5.5V. Connect externally to GATEV <sub>SS</sub> . Bypass with a 1µF and a 0.1µF capacitor in parallel to AGND.                                                                                        |

## \_Pin Description (continued)

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                        |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | RCS2+            | Channel 2 Current-Sense-Resistor Connection. Connect to the external supply powering channel 2's MESFET drain, in the range of +0.5V to +11V (MAX11014) or +5V to +32V (MAX11015). Bypass with a 1µF and a 0.1µF capacitor in parallel to AGND. If unused, connect to RCS1+.                                                    |

| 31  | RCS2-            | Channel 2 Current-Sense-Resistor Connection. Connect to the channel 2 MESFET drain. Decouple as required by the application. If unused, connect to RCS2+.                                                                                                                                                                       |

| 32  | RCS1-            | Channel 1 Current-Sense-Resistor Connection. Connect to the channel 1 MESFET drain. Decouple as required by the application. If unused, connect to RCS1+.                                                                                                                                                                       |

| 33  | RCS1+            | Channel 1 Current-Sense-Resistor Connection. Connect to the external supply powering channel 1's MESFET drain, in the range of +0.5V to +11V (MAX11014) or +5V to +32V (MAX11015). Bypass with a 1µF and a 0.1µF capacitor in parallel to AGND. If unused, connect to RCS2+.                                                    |

| 38  | OPSAFE1          | Operating Safe Channel 1 Input. Set OPSAFE1 high to clamp GATE1 to ACLAMP1 for fast protection of enhancement FET power transistors.                                                                                                                                                                                            |

| 39  | OPSAFE2          | Operating Safe Channel 2 Input. Set OPSAFE2 high to clamp GATE2 to ACLAMP2 for fast protection of enhancement FET power transistors.                                                                                                                                                                                            |

| 40  | BUSY             | BUSY Output. BUSY asserts high under certain conditions when the device is busy. See the <i>BUSY Output</i> section.                                                                                                                                                                                                            |

| 41  | DV <sub>DD</sub> | Digital Supply Voltage. Set DV <sub>DD</sub> between +2.7V and AV <sub>DD</sub> . Bypass with a 1 $\mu$ F and a 0.1 $\mu$ F capacitor in parallel to DGND.                                                                                                                                                                      |

| 42  | DGND             | Digital Ground                                                                                                                                                                                                                                                                                                                  |

| 43  | CNVST            | Active-Low Conversion Start Input. Set $\overline{\text{CNVST}}$ low to begin a conversion in clock modes 01 and 11. Connect $\overline{\text{CNVST}}$ to $\overline{\text{DV}}_{\text{DD}}$ when issuing conversion commands through the serial interface.                                                                     |

| 44  | ALARM            | Alarm Output. ALARM asserts when the temperature or voltage measurements exceed their preset high or low thresholds.                                                                                                                                                                                                            |

| 45  | CS/A0            | Chip-Select Input in SPI Mode/Address Select 0 in I <sup>2</sup> C Mode. $\overline{CS}$ is an active-low input. When $\overline{CS}$ is low, the serial interface is enabled. When $\overline{CS}$ is high, DOUT is high impedance. Connect A0 to DV <sub>DD</sub> or DGND to set the device address in I <sup>2</sup> C mode. |

| 46  | SPI/Ī2C          | SPI-/I <sup>2</sup> C-Interface Select Input. Connect SPI/I  DGND to select SPI mode. Connect SPI/I  to DVDD to select SPI mode. Connect SPI/I  to DGND to select I <sup>2</sup> C mode.                                                                                                                                        |

| 47  | N.C./A2          | No Connection in SPI Mode/Address Select 2 in I <sup>2</sup> C Mode. Connect A2 to DV <sub>DD</sub> or DGND to set the device address in I <sup>2</sup> C mode.                                                                                                                                                                 |

| 48  | SCLK/SCL         | Serial Clock Input. Clocks data in and out of the serial interface. (Duty cycle must be 40% to 60%.) Connect a pullup resistor to SCL in I <sup>2</sup> C mode. See Table 10 for details on programming the clock mode.                                                                                                         |

| _   | EP               | Exposed Pad. Connect to AGND and a large copper plane to meet power dissipation specifications. Do not use as a ground connection.                                                                                                                                                                                              |

## **Detailed Description**

The MAX11014/MAX11015 set and monitor the bias conditions for dual MESFET power devices found in cellular base stations and point-to-point microwave links. The internal DAC sets the voltage across the current-sense resistor by controlling the GATE voltage. These devices integrate a 12-bit ADC to measure voltage, internal and external temperature, and communicate through a 4-wire 20MHz SPI-/MICROWIRE-compatible serial interface or 2-wire 3.4MHz I<sup>2</sup>C-compatible serial interface (pin-selectable).

The MAX11014/MAX11015 operate from an internal +2.5V reference or individual ADC and DAC external references. The external current-sense resistors monitor voltages over the 0 to (VDACREF / 4) range. Two current-sense amplifiers with a preset gain of four monitor the voltage across the sense resistors. The MAX11014/MAX11015 accurately measure their internal die temperature and two external remote diode temperature sensors. The remote pn junctions are typically the base-emitter junction of an npn transistor, either discrete or integrated on a CPU, FPGA, or ASIC.

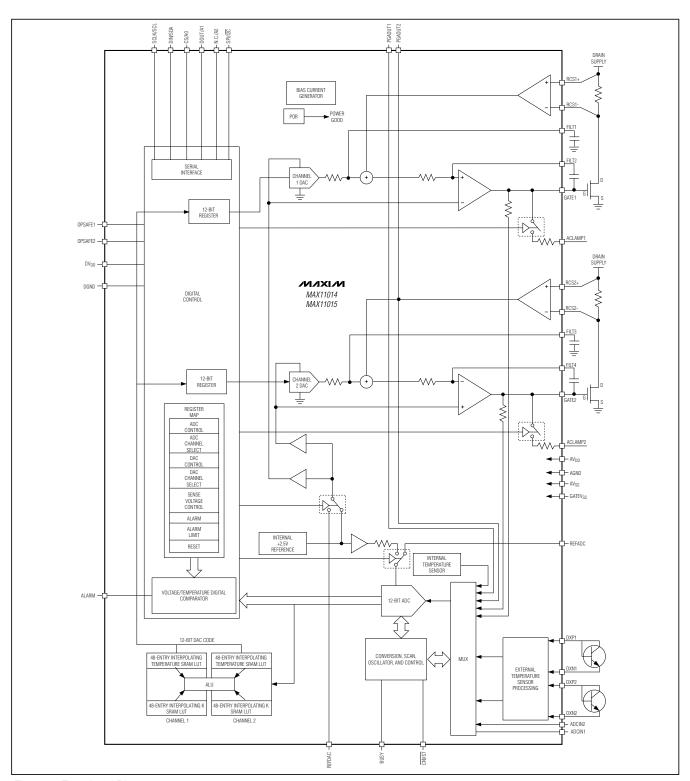

The MAX11014/MAX11015 also feature an alarm output that can be triggered during an internal or external overtemperature condition, an excessive current-sense voltage, or an excessive GATE voltage. Figure 4 shows the MAX11014's functional diagram.

The MAX11014 integrates complete dual analog closed-loop drain-current controllers for Class A MESFET amplifier operation. See the *MAX11014 Class A Control Loop* section. The analog control loop sets the drain current through the current-sense resistors. The MESFET gate-drive amplifier can vary the DAC code accordingly if the temperature or other system variables change.

Implement Class A amplifier operation with the following three steps:

#### 1) Characterization

Characterize the MESFET over temperature to determine the amplifier's set of drain-current values, assuming the part-to-part calibration curve is consistent. There may be an offset shift, but no important change in the shape of the function. Load these values into the MAX11014 LUTs at power-up. In operation, there is a linear interpolation between the values stored in the LUTs.

Adjust the drain current for other variables such as output power or drain voltage by loading values into the numerical K LUTs.

#### 2) Calibration

In production of the power amplifier, measure the quiescent drain current at a fixed calibration temperature (probably room) and adjust the VSET(CODE) value until the drain current is within the specified limits for that temperature. The VSET(CODE) value is stored for loading after power-up. Prior to operation, command a PGA calibration after powering up by writing to the PGA calibration control register, setting the TRACK bit to 0 and the DOCAL bit to 1 (see Table 18).

#### 3) Operation

Upon request, the MAX11014 measures the temperature of the MESFET and compares it with the previous reading. If the temperature reading has changed, the MAX11014 reads the LUTs with the characterization data and updates the DAC to correct the drain current. Setting the TRACK, DOCAL, and SELFTIME bits to 1 in the PGA calibration control register starts automatic monitoring and adjustment of drain current for variations in temperature.

Also, if the K LUTs are used, their values are monitored for changes. A DAC correction is then made if necessary.

For Class AB operation with the MAX11015, measure the MESFET temperature and set the GATE\_ voltage through the LUTs and DAC to control the drain current. See the *MAX11015 Class AB Control* section. Implement Class AB amplifier operation with the same three steps as Class A operation, with the exception that the LUTs set the GATE\_ voltage for constant drain current with varying temperature.

#### **Power-On Reset**

On power-up, the MAX11014/MAX11015 are in full power-down mode (see the *SHUT (Write)* section). To change to normal power mode, write two commands to the shutdown register. Set the FULLPD bit to 0 (other bits in the shutdown register are ignored) on the first command. A second command to this register then activates the internal blocks.

### **MAX11014 Class A Control Loop**

The MAX11014 is designed to set and continuously control the drain current for MESFET power amplifiers configured to operate in Class A. Set the DAC code to control the voltage across the RCS\_+ and RCS\_- current-sense resistor connections. The MAX11014 internal control loop automatically keeps the voltage across the current-sense resistor to the value set by the DAC. See the *12-Bit DAC* section.

Figure 4. Functional Diagram

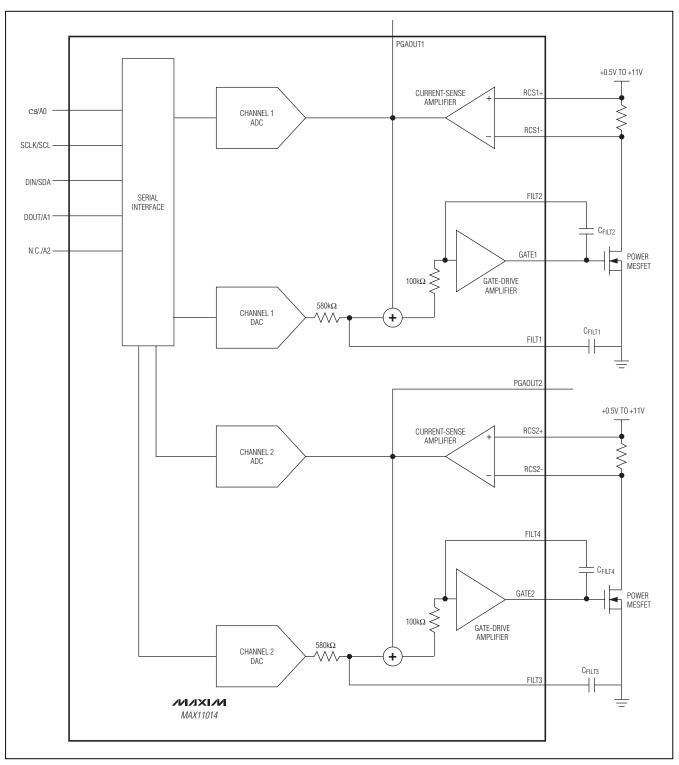

Once the control loop has been set, the MAX11014 automatically maintains the drain-current value. Figure 5 details the amplifiers that bias the channel 1 and channel 2 control loops.

The dual current-sense amplifiers amplify the voltage between RCS\_+ and RCS\_- by four and add an offset voltage (+12mV nominally). These current-sense amplifiers amplify sense voltages between 0 and 625mV when VREFDAC = +2.5V. See the *Current-Sense Amplifiers* section.

The current-sense amplifier output injects a scaled-down replica of the MESFET drain current at the summing node to complete the internal analog feedback loop. The summing node drives the gate-drive amplifier through a  $100 \mbox{k}\Omega$  series resistor. The gate-drive amplifier is configured as an integrator by the external capacitor connected between GATE1/GATE2 and FILT2/FILT4. The gate-drive amplifier includes automatic offset cancellation between 0 and 24mV to null the 12mV offset from the current-sense amplifier. See the *Register Descriptions* and *PGACAL (Write)* sections.

The MAX11014's analog control loop setpoint is described by the following equation:

$$V_{RCS+} - V_{RCS-} = \frac{V_{FILT}(CODE = 000h) - V_{FILT}}{4}$$

where:

VFILT(CODE = 000h) = VFILT1 (channel 1) and VFILT3 (channel 2) when the THRUDAC1/THRUDAC2 register code is set to 000h.

VFILT = VFILT1 (channel 1) and VFILT3 (channel 2).

$V_{RCS+}$  -  $V_{RCS-}$  = the voltage drop across the current-sense resistor.

Connect a capacitor from FILT2 to GATE1 to form an integrator (setting the control-loop dominant pole) with the channel 1 internal  $100 k\Omega$  resistor. Connect a capacitor from FILT4 to GATE2 to form an integrator (setting the control-loop dominant pole) with the channel 2 internal  $100 k\Omega$  resistor. The gate-drive amplifier's output drives the MESFET gates. See the <code>Gate-Drive Amplifiers</code> section.

The channel 1 DAC voltage is output to FILT1 through a series  $580 \mathrm{k}\Omega$  resistor. The channel 2 DAC voltage is output to FILT3 through a series  $580 \mathrm{k}\Omega$  resistor. Connect a capacitor from FILT1 to AGND and FILT3 to AGND to set the filter's time constant for the respective channel.

#### **MAX11015 Class AB Control**

The MAX11015 is designed to be used with a Class AB amplifier configuration to independently measure the drain current and set the GATE\_ output voltages through the serial interface. After sensing the drain current with no RF signal applied, set the DAC code to obtain the desired GATE\_ voltage. Figure 6 details the amplifiers that bias the channel 1 and channel 2 control.

The MAX11015 internal 12-bit DAC voltage is applied to the gate-drive amplifier, which has a preset gain of -2. See the *Gate-Drive Amplifiers* section. Setting the DAC code between FFFh and 000h typically produces a GATE\_ voltage between 0 and (-2 x VREFDAC). See the *HCFG* (*Read/Write*) section for details on adjusting the GATE\_ maximum voltage.

The channel 1 DAC voltage is output to FILT1 through a series  $580k\Omega$  resistor. The channel 2 DAC voltage is output to FILT3 through a series  $580k\Omega$  resistor. Connect a capacitor from FILT1 to AGND and FILT3 to AGND to set the filter's time constant for the respective channel. Connect FILT2 and FILT4 to AGND (MAX11015 only).

The dual current-sense amplifiers amplify the voltage between RCS\_+ and RCS\_- by four and add an offset voltage (+12mV nominally). The current-sense amplifiers amplify sense voltages between 0 and 625mV when  $V_{REFDAC}$  = +2.5V. See the *Current-Sense Amplifiers* section.

#### **Current-Sense Amplifiers**

The dual current-sense amplifiers amplify the voltage between RCS\_+ and RCS\_- and add an offset voltage. Connect a resistor between RCS\_+ and RCS\_- to sense the MESFET drain current. The current-sense amplifiers scale the sense voltage by four. These amplifiers also reject the drain supply voltage that appears as a DC common-mode level on the current signal.

The gate-drive amplifier includes automatic offset cancellation between 0 and 24mV to null the 12mV offset from the current-sense amplifier. See the *PGACAL* (*Write*) section.

#### **Gate-Drive Amplifiers**

The gate-drive amplifiers control the MESFET gate bias settings. The MAX11014's channel 1 and channel 2 DAC voltages are routed through a summing node and into the gate-drive amplifiers. The MAX11015's channel 1 and channel 2 DAC voltages are routed directly to the gate-drive amplifiers, which have a preset gain of -2. See the *12-Bit DAC* section for details on setting the DAC codes.

Figure 5. MAX11014 Class A Analog Control Loop

Figure 6. MAX11015 Class AB Analog Control

| MESFET      | GATE<br>VOLTAGE | USER<br>ENTERED<br>DAC CODE | ADC CODE<br>READ<br>FROM<br>THE FIFO | RCS_+ TO<br>RCS SENSE<br>VOLTAGE | PGAOUT<br>VOLTAGE | GATE VOLTAGE<br>ALARM<br>THRESHOLDS |                            |

|-------------|-----------------|-----------------------------|--------------------------------------|----------------------------------|-------------------|-------------------------------------|----------------------------|

| FULLY<br>ON | 0V              | FFFh                        | FFFh                                 | 0mV                              | VREFDAC           | DEFAULT<br>VH = FFFh                |                            |

|             |                 |                             |                                      |                                  |                   | TOO HIGH                            | NEW HIGH GATE              |

|             |                 |                             |                                      |                                  |                   | VGATE<br>WITHIN<br>THRESHOLDS       | VOLTAGE ALARM<br>THRESHOLD |

|             |                 |                             |                                      |                                  |                   | ₩                                   | NEW LOW GATE VOLTAGE ALARM |

|             |                 |                             |                                      |                                  |                   | TOO LOW                             | THRESHOLD                  |

| OFF         | -2 x VREFDAC    | 000h                        | 000h                                 | VREFDAC / 4                      | OV                | DEFAULT<br>V <sub>L</sub> = 000h    |                            |

Figure 7. DAC Code Range

Connect the MESFET drain to the RCS\_- input. Connect the MESFET's gate to the GATE\_ output. Set the GATE\_ voltage to -2 x VREFDAC to turn the MESFET fully off. Set the GATE\_ voltage to 0V to turn the MESFET fully on. See Figure 7.

The MAX11014/MAX11015 GATE\_ output voltage can be clamped to the external voltage applied at ACLAMP\_. Setting OPSAFE\_ high clamps the GATE\_ voltage unconditionally. The GATE\_ can also be clamped by different commands issued through the serial interface. These devices can also monitor the alarms through the software to modify the clamping mechanism. See the *Automatic GATE Clamping* and *ALMHCFG (Read/Write)* sections.

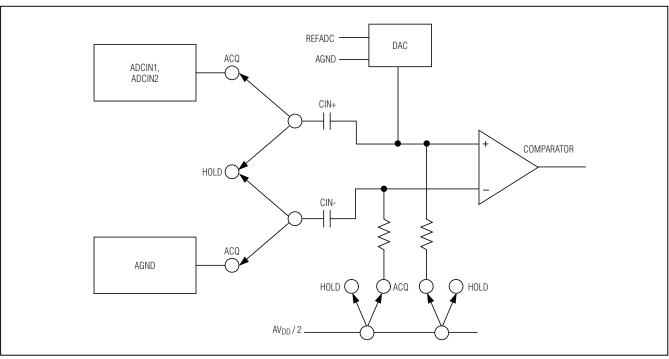

#### 12-Bit ADC Description

The MAX11014/MAX11015 ADCs use a fully differential successive-approximation register (SAR) conversion technique and on-chip track-and-hold (T/H) circuitry to convert temperature and voltage signals into 12-bit digital results. The analog inputs accept single-ended input signals. Single-ended signals are converted using a unipolar transfer function. See the *ADC Transfer Function* section for more details.

The internal ADC block converts the results of the internal die temperature, remote diode temperature readings, current-sense voltages, and ADCIN\_ voltages. The ADC block also reads back the GATE\_ analog output voltage and converts it to a 12-bit digital result. The

conversion results are written to the FIFO memory. The FIFO holds up to 15 words (each word of 16 bits) with a leading 4-bit channel tag to indicate which channel the 12-bit data comes from. See Table 25. The FIFO reads back data words either one at a time or continuously. See the *ADCCON (Write)* section. The FIFO always stores the most recent conversion results and allows the oldest data to be overwritten. The FIFO indicates an overflow condition and underflow condition (read of an empty FIFO) through the flag register. See the *FLAG (Read)* section.

#### Analog Input Track and Hold

The equivalent circuit of Figure 8 details the MAX11014/MAX11015's ADCIN\_ input architecture. In track mode, a positive input capacitor is connected to ADCIN1/ADCIN2. A negative input capacitor is connected to AGND. After the T/H enters hold mode, the difference between the sampled input voltages and AGND is converted. The input-capacitance charging rate determines the time required for the T/H to acquire an input signal. The required acquisition time lengthens with the increase of the input signal's source impedance. Any source impedance below  $300\Omega$  does not significantly affect the ADC's AC performance. A highimpedance source can be accommodated either by placing a 1µF capacitor between ADCIN\_ and AGND. The combination of the analog-input source impedance and the capacitance at the analog input creates an RC filter that limits the analog-input bandwidth.

Figure 8. ADC Equivalent Input Circuit

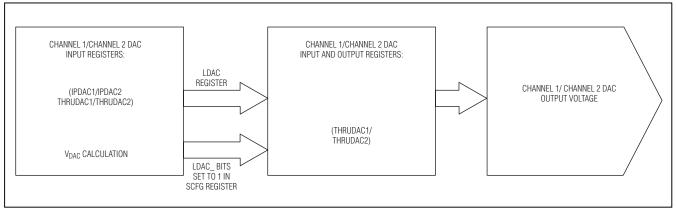

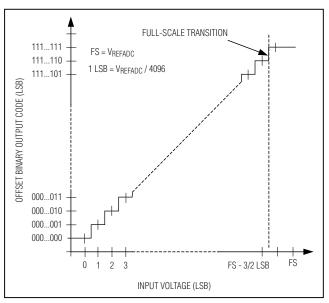

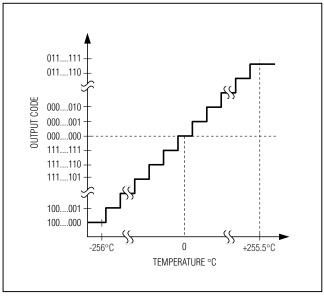

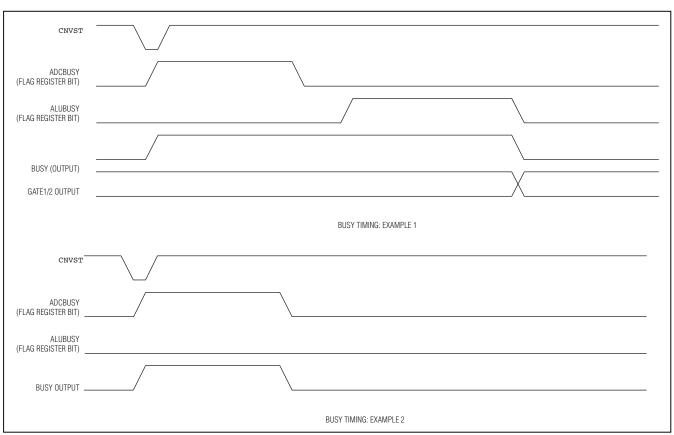

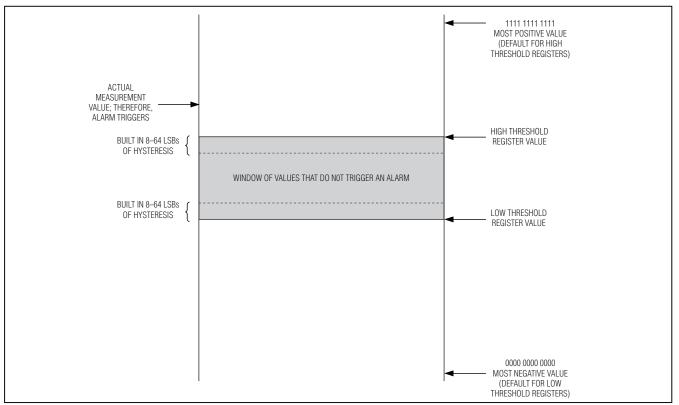

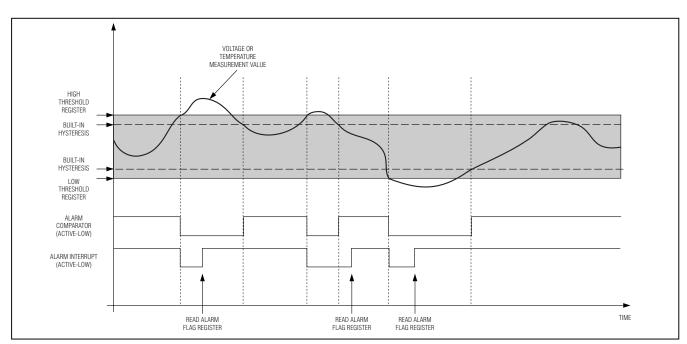

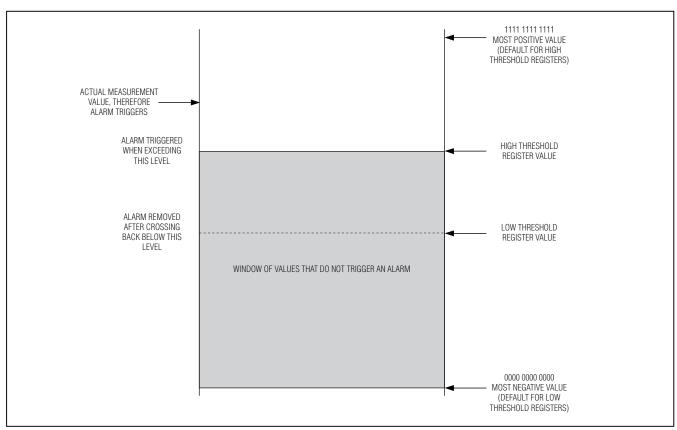

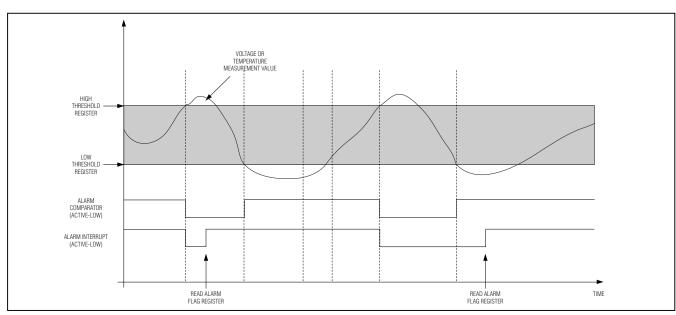

#### Analog Input Protection