#

# 3A, Low-Voltage, Step-Down Regulator with Synchronous Rectification and Internal Switches

## General Description

The MAX1623 switch-mode buck regulator with synchronous rectification provides local CPU and bus-termination power in notebook and desktop computers. An internal  $55m\Omega$  (typ), 3A PMOS power switch and  $60m\Omega$  (typ), 3A NMOS synchronous-rectifier switch deliver continuous load currents up to 3A from a 5V supply with 95% typical efficiency. Output accuracy is ±1%, including line and load regulation.

The MAX1623 features constant-off-time, current-mode pulse-width-modulation (PWM) control with switching frequencies as high as 350kHz. An external resistor at the TOFF pin sets the off-time, allowing optimum design flexibility in terms of switching frequency, output switching noise, and inductor size. This device is available in a space-saving 20-pin SSOP package.

## **Applications**

5V to 3.3V Conversion Notebook Computer CPU I/O Supply Desktop Computer Bus-Termination Supply **CPU Daughter Card Supply DSP Supply**

### **Features**

- ±1% Output Accuracy, Including Line and Load Regulation

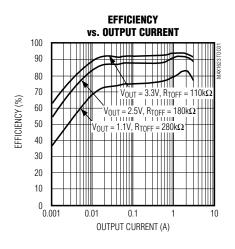

- ♦ 94% Efficiency

- Internal Switches 55mΩ PMOS Power Switch 60m $\Omega$  NMOS Synchronous-Rectifier Switch

- ♦ Guaranteed 3A Load Capability

- ♦ Minimal External Components

- ♦ Pin-Selectable Fixed 3.3V, 2.5V, or Adjustable (1.1V to 3.8V) Output Voltage

- → +4.5V to +5.5V Input Voltage Range

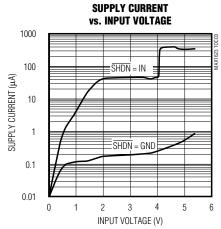

- ♦ 400µA (typ) Supply Current

- ♦ <1µA Shutdown Supply Current

</p>

- ♦ Constant-Off-Time PWM Operation

- Switching Frequencies Up to 350kHz

- **♦** Idle Mode<sup>™</sup> Operation at Light Loads

- ♦ Thermal Shutdown Protection

- Available in 20-Pin SSOP

## **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1623EAP | -40°C to +85°C | 20 SSOP     |

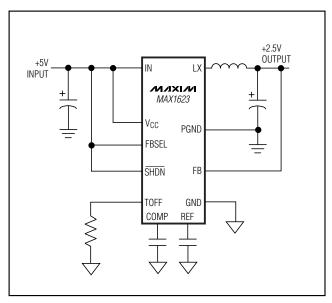

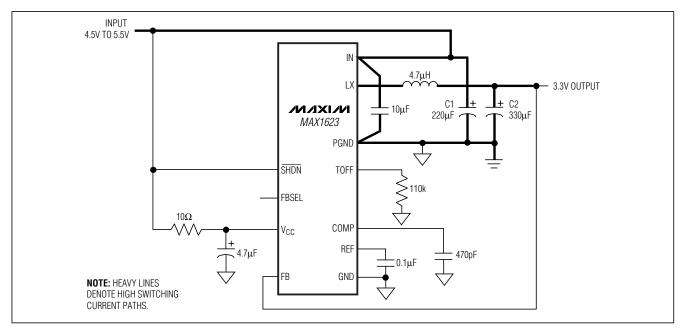

# Typical Operating Circuit

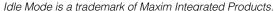

# **Pin Configuration**

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{CC} = +5V, FBSEL unconnected, R_{TOFF} = 110k\Omega, T_A = 0^{\circ}C \text{ to } +85^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$

| PARAMETER                      | CONDITIONS                                                     |                             | MIN   | TYP   | MAX   | UNITS |

|--------------------------------|----------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|

| Input Voltage Range            |                                                                |                             | 4.5   |       | 5.5   | V     |

| Output Voltage                 | V <sub>IN</sub> = 4.5V to 5.5V,<br>I <sub>LOAD</sub> = 0 to 3A | FBSEL = unconnected         | 3.296 | 3.330 | 3.366 | V     |

|                                |                                                                | FBSEL = V <sub>CC</sub>     | 2.49  | 2.525 | 2.550 |       |

|                                |                                                                | FBSEL = GND or REF          | 1.089 | 1.100 | 1.110 |       |

| Output Adjustment Range        | FBSEL = GND or REF (                                           | FBSEL = GND or REF (Note 1) |       |       | 3.80  | V     |

| Reference Output Voltage       | I <sub>REF</sub> = 0                                           |                             | 1.089 | 1.100 | 1.110 | V     |

| Reference Load Regulation      | IREF = -1μA to 10μA                                            |                             |       |       | 1     | mV    |

| Current-Limit Threshold        |                                                                |                             | 3.65  |       | 4.65  | А     |

| PMOS Switch On-Resistance      | V <sub>IN</sub> = 4.5V                                         |                             |       | 55    | 100   | mΩ    |

| NMOS Switch On-Resistance      | V <sub>IN</sub> = 4.5V                                         | V <sub>IN</sub> = 4.5V      |       |       | 100   | mΩ    |

| Maximum Switching Frequency    | I <sub>LOAD</sub> ≥ 1.5A (Note 1)                              |                             |       | 350   | kHz   |       |

| Idle Mode Threshold (Note 2)   |                                                                | 1                           | 1.25  | 1.5   | А     |       |

| No-Load Supply Current         | Does not include switch                                        |                             | 400   | 525   | μΑ    |       |

| Shutdown Supply Current        | SHDN = GND                                                     |                             | 0.5   | 10    | μΑ    |       |

| LX Leakage Current             | $V_{IN} = 5.5V$ , $V_{LX} = 5.5V$ or 0                         |                             |       |       | ±20   | μΑ    |

| Thermal Shutdown Threshold     |                                                                |                             |       | 145   |       | °C    |

| Undervoltage Lockout Threshold | V <sub>CC</sub> falling, 100mV hysteresis                      |                             | 4.1   | 4.2   | 4.3   | V     |

| FB Input Bias Current          | FBSEL = GND, adjustable output mode, VFB = 1.2V                |                             | -25   |       | 25    | nA    |

| Error-Amplifier Gain Bandwidth | (Note 1)                                                       |                             | 500   |       |       | kHz   |

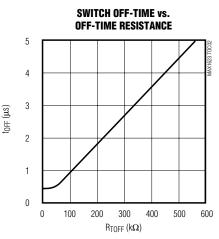

| Off-Time Adjustment Range      |                                                                |                             | 0.5   |       | 4     | μs    |

| Off-Time Default Period        |                                                                | 0.85                        | 1.00  | 1.15  | μs    |       |

| 400 - 11 - 15 - 11             | FBSEL = GND<br>FBSEL = REF                                     |                             |       | 1     |       | %     |

| AC Output Load Regulation      |                                                                |                             |       | 2     |       | /0    |

| SHDN Input Current             | SHDN = GND or V <sub>CC</sub>                                  |                             |       | 0.03  | 1     | μΑ    |

| SHDN Input Low Voltage         |                                                                |                             |       |       | 0.8   | V     |

| SHDN Input High Voltage        |                                                                |                             |       |       |       | V     |

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{CC} = +5V, FBSEL unconnected, R_{TOFF} = 110k\Omega, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.)$  (Note 3)

| PARAMETER                      | CONDITIONS                                                     |                         | MIN              | TYP | MAX   | UNITS |

|--------------------------------|----------------------------------------------------------------|-------------------------|------------------|-----|-------|-------|

| Input Voltage Range            |                                                                |                         | 4.5              |     | 5.5   | V     |

| Output Voltage                 | V <sub>IN</sub> = 4.5V to 5.5V,<br>I <sub>LOAD</sub> = 0 to 3A | FBSEL = unconnected     | 3.234            |     | 3.366 | V     |

|                                |                                                                | FBSEL = V <sub>CC</sub> | 2.450            |     | 2.550 |       |

|                                | ILOAD - 0 to or t                                              | FBSEL = GND or REF      | 1.075            |     | 1.110 |       |

| Output Adjustment Range        | FBSEL = GND or REF (1                                          | Note 1)                 | V <sub>REF</sub> |     | 3.8   | V     |

| Reference Output Voltage       | IREF = 0                                                       |                         | 1.075            |     | 1.110 | V     |

| Current-Limit Threshold        |                                                                |                         |                  |     | 4.75  | А     |

| PMOS Switch On-Resistance      | V <sub>IN</sub> = 4.5V                                         |                         |                  |     | 0.1   | Ω     |

| NMOS Switch On-Resistance      | VIN = 4.5V                                                     |                         |                  |     | 0.1   | Ω     |

| No-Load Supply Current         | Does not include switching losses                              |                         |                  |     | 600   | μΑ    |

| Shutdown Supply Current        | SHDN = GND                                                     |                         |                  |     | 10    | μΑ    |

| LX Leakage Current             | $V_{IN} = 5.5V$ , $V_{LX} = 5.5V$ or 0                         |                         | -20              |     | 20    | μΑ    |

| Undervoltage Lockout Threshold | V <sub>CC</sub> falling, 100mV hysteresis                      |                         | 4.0              |     | 4.3   | V     |

| FB Input Bias Current          | FBSEL = GND, adjustable output mode, V <sub>FB</sub> = 1.2V    |                         | -50              |     | 50    | nA    |

| Off-Time Adjustment Range      |                                                                |                         | 0.55             |     | 4     | μs    |

| Off-Time Default Period        |                                                                |                         | 0.85             |     | 1.25  | μs    |

| SHDN Input Current             | SHDN = GND or V <sub>CC</sub>                                  |                         | -1               |     | 1     | μΑ    |

| SHDN Input Low Voltage         |                                                                |                         |                  |     | 0.8   | V     |

| SHDN Input High Voltage        |                                                                |                         | 2.2              |     |       | V     |

Note 1: Guaranteed by design, not production tested.

Note 2: Idle Mode threshold is defined as the transition point in the load-current range between Idle Mode and constant-off-time operation.

Note 3: Specifications to -40°C are guaranteed by design, not production tested.

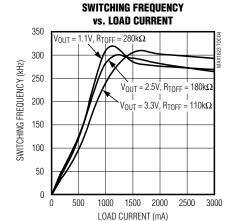

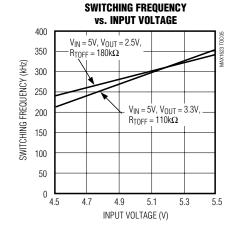

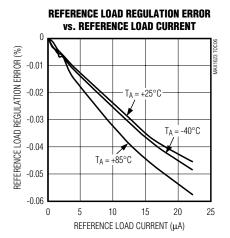

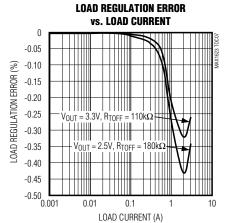

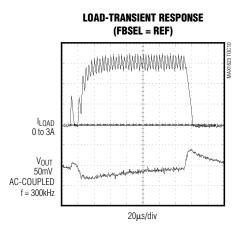

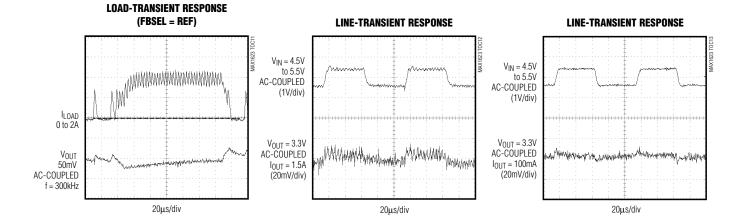

## **Typical Operating Characteristics**

(Circuit of Figure 2,  $T_A = +25$ °C, unless otherwise noted.)

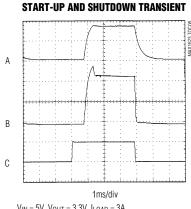

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 2,  $T_A = +25$ °C, unless otherwise noted.)

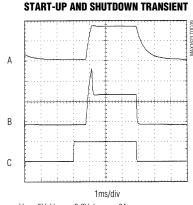

$$\begin{split} &V_{IN} = 5V,\, V_{OUT} = 3.3V,\, I_{LOAD} = 3A,\\ &WAVEFORM\,\, AVERAGED\\ &A:\, V_{OUT},\, 2V/div\\ &B:\, I_{IN},\, 1A/div\\ &C:\, V_{SHDIN},\, 5V/div \end{split}$$

$V_{IN} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $I_{LOAD} = 2A$ , WAVEFORM AVERAGED A:  $V_{OUT}$ , 2V/div B:  $I_{IN}$ , 1A/div C:  $V_{\overline{SHDN}}$ , 5V/div

## **Pin Description**

| PIN                   | NAME  | FUNCTION                                                                                                                                                                                                            |

|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5,<br>16,18, 20 | LX    | Connection to the internal power switches.                                                                                                                                                                          |

| 2, 4, 6               | IN    | Power Input. Internally connected to the PMOS switch source. Connect to +5V.                                                                                                                                        |

| 7                     | SHDN  | Active-Low Shutdown Input. Connect to VCC for normal operation.                                                                                                                                                     |

| 8                     | FBSEL | Feedback Select Input. See Table 1.                                                                                                                                                                                 |

| 9                     | TOFF  | Off-Time Select Input. Connect a resistor from TOFF to GND to adjust the switch off-time, and therefore the frequency: $t_{OFF} = \frac{R_{TOFF}}{110k\Omega}$ (µs). See <i>Typical Operating Characteristics</i> . |

| 10                    | FB    | Feedback input for both fixed-output and adjustable operating modes. Connect to the output directly for fixed-voltage operation or to a resistor-divider for adjustable operating modes.                            |

| 11                    | GND   | Analog Ground                                                                                                                                                                                                       |

| 12                    | REF   | Reference Output. Bypass with a minimum 0.1µF capacitor to GND. See Internal Reference.                                                                                                                             |

| 13                    | COMP  | Integrator Capacitor Connection. Connect a 470pF (470pF to 2000pF range) capacitor to GND to set the typical integration time-constant. See <i>Integrator Amplifier</i> .                                           |

| 14                    | Vcc   | Analog Supply-Voltage Input. Supplies internal analog circuitry. Connect to +5V. Bypass VCC with $10\Omega$ and $4.7\mu$ F (Figure 2).                                                                              |

| 15, 17, 19            | PGND  | Power Ground. Internally connected to the NMOS synchronous rectifier source.                                                                                                                                        |

### **General Description**

The MAX1623 current-mode, PWM, DC-DC regulator is designed for 5V-input step-down applications. It features a  $55m\Omega$  (typ) PMOS switch and a  $60m\Omega$  (typ) NMOS synchronous-rectifier switch. Simple constant-offtime control allows switching frequencies up to 350kHz. Adjust the off-time with an external resistor RTOFF to optimize performance trade-offs among efficiency, component size, output switching noise, and cost. Idle Mode operation enhances light-load efficiency by switching to a pulse-skipping mode that reduces transition and gatecharge losses. The power-switching circuit consists of the IC and an LC output filter. The output voltage is the average of the AC voltage at the switching node (LX). The MAX1623 regulates the output voltage by changing the PMOS switch on-time relative to the constant offtime, thereby adjusting the duty cycle.

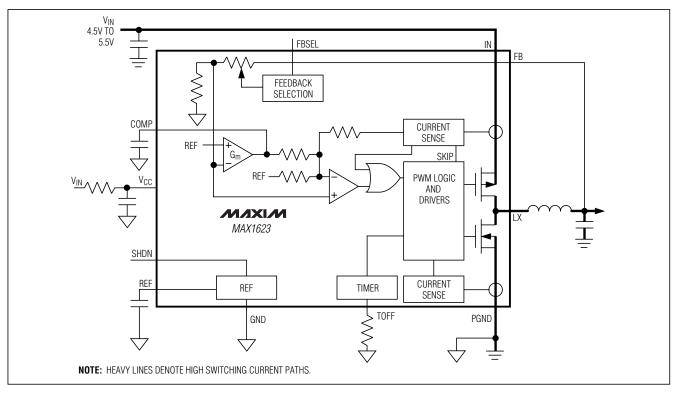

The MAX1623 contains six major circuit blocks (Figure 1): a PWM comparator, a current-sense circuit, a PWM logic block, an internal feedback mux, an off-time control block, and a 1.1V precision reference. The input supply directly powers the internal blocks.

#### Modes of Operation

The load current determines the mode of operation: Idle Mode (load currents less than 0.625A) or PWM mode for inductor currents of 1.25A (which corresponds to load currents greater than 0.625A). The PWM current limit is continuously adjusted by the PWM comparator and can vary from 0A to the maximum current limit (4A). If the inductor current falls below the Idle Mode threshold (1.25A), skip mode takes over. Whenever the P-channel switch turns on, it stays on until the sensed current reaches the active current limit. The PWM current limit automatically adjusts with the PMOS switch duty cycle required to generate the desired output voltage. When the active current limit is met, the PMOS switch turns off for the programmed minimum off-time, and the N-channel synchronous rectifier turns on. The synchronous rectifier stays on until the P-channel switch turns back on or until the inductor current reaches zero. At the end of the off-time, the Pchannel switch turns on again if the output voltage indicates that energy is required at the output.

Figure 1. Functional Diagram

#### Idle Mode

At light loads, the device goes into skip mode (because the load current is below the skip threshold), and Idle Mode operation (1.25A current limit) begins. This allows both switches to remain off at the end of the off-time, skipping cycles to reduce switching losses. At lighter loads, the inductor current is discontinuous because the inductor current reaches zero. In Idle Mode, the operating frequency varies with output load current. There is no major shift in circuit behavior as the PWM limit falls below the skip limit. The effective off-time simply increases, resulting in a seamless transition between PWM mode and Idle Mode.

#### **PWM Mode**

PWM operation occurs whenever the load current is greater than the skip threshold. In this mode, the PWM comparator adjusts the current limit to the desired output current, so that the P-channel turns on at the end of each off-time.

Three signals are resistively summed at the input of the PWM comparator (Figure 1): an output voltage error signal relative to the reference voltage, an integrated output voltage error correction signal, and the sensed

PMOS switch current. The integrated error signal is provided by a transconductance amplifier with an external capacitor at the COMP pin. This integrator provides high DC accuracy without the need for a high-gain error amplifier. Connecting a capacitor at COMP modifies the overall loop response (see *Integrator Comparator* section).

#### **Setting the Output Voltage**

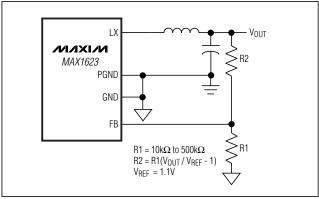

There are two preset output voltages (2.525V and 3.33V), or the output voltage can be adjusted from the reference voltage (nominally 1.1V) up to 3.8V. For a preset output voltage (Figure 2), connect FB to the output voltage, and connect FBSEL to VCC (2.525V output) or leave it unconnected (3.33V output). For an adjustable output, connect FBSEL to GND or REF, and connect FB to the midpoint of a resistor divider between the output voltage and ground (Figure 3). Regulation is maintained when VFB equals VREF. Select R1 in the  $10k\Omega$  to  $500k\Omega$  range. R2 is given by:

$$R2 = (R1)(V_{OUT} / V_{REF} - 1)$$

where VREF is typically 1.1V.

Figure 2. Standard 3.3V/3A Application Circuit

### **Setting the AC Loop Gain**

The internal integrator amplifier effectively eliminates anv long-term error within the time constant set by the G<sub>m</sub> of the transconductance amplifier and the capacitor connected to COMP. However, there remains a short-term load-regulation error in response to load current changes. Proper FBSEL connection selects the relative level of current feedback to voltage feedback, which results in an AC load-regulation error of either 1% or 2% of the output voltage (Table 1). The 2% setting is automatically selected in preset output voltage mode (FBSEL connected to VCC or unconnected). This gain setting minimizes the size and cost of the output filter capacitor required. For extremely tight specifications that cannot tolerate 2% short-term errors, connect FBSEL to ground (adjustable mode) for 1% AC load regulation. (See Input and Output Filter Capacitors (C1, C2) section.)

### **Synchronous Rectification**

Synchronous rectification improves efficiency by 3% to 5% at heavy loads when compared to a conventional Schottky rectifier. To prevent cross-conduction or "shoot-through," the synchronous rectifier turns on following a short delay (dead time) after the P-channel power MOS-FET turns off. In discontinuous (light-load) mode, the synchronous rectifier switch turns off as the inductor current approaches zero. The synchronous rectifier works under all operating conditions, including Idle Mode.

**Table 1. Output Voltage Selection**

| FBSEL PIN        | AC LOAD<br>REGULATION (%) | OUTPUT<br>VOLTAGE (V) |  |

|------------------|---------------------------|-----------------------|--|

| IN               | 2                         | 2.525                 |  |

| Unconnected      | 2                         | 3.33                  |  |

| GND              | 1                         | Adjustable            |  |

| V <sub>REF</sub> | 2                         | Adjustable            |  |

#### Integrator Amplifier (COMP)

An internal transconductance amplifier fine tunes the output DC accuracy. The transconductance amplifier is compensated at COMP. A capacitor from COMP to ground determines the gain-bandwidth product and the overall loop response. This integrator effectively eliminates any long-term error within the time constant set by the G<sub>m</sub> of the transconductance amplifier and the capacitor connected to COMP.

For stability, choose COMP as follows:

$$C_{COMP} \ge \frac{G_{m} \cdot R_{LOAD} \cdot C_{OUT}}{4}$$

where  $G_m = 9.1 \mu \sigma$ .

Figure 3. Adjustable Output Voltage

A high capacitor value maintains a constant average output voltage but slows the loop response to changes in output voltage. A low capacitor value speeds up the loop response to changes in output voltage. Choose the capacitor value that results in optimal performance.

### **Current Limiting**

The current-sense circuit enables when the PMOS power switch is on. This circuit's corresponding output voltage feeds three separate comparators: the skip current comparator (1.25A), the maximum current comparator (4.15A), and the PWM current comparator (see *Modes of Operation* section).

# Oscillator Frequency and Programming the Off-Time

The MAX1623 features a programmable off-time that is set by RTOFF connected from TOFF to GND. Connecting a 110k $\Omega$  resistor from TOFF to GND achieves a 1 $\mu$ s (nominal) off-time. The off-time is inversely proportional to RTOFF according to the formula:

$$toff = Rtoff / 110k (\mu s)$$

tOFF is adjustable between 0.5µs to 4µs (see *Typical Operating Characteristics*). To set the switching frequency when the inductor operates in continuous-conduction mode, the off-time has to be set to:

$$t_{OFF} = \frac{V_{I} - V_{O} - V_{PCH}}{f(V_{I} - V_{PCH} + V_{NCH})}$$

where:

toff = the programmed off-time

V<sub>I</sub> = input voltage

$V_{\Omega}$  = output voltage

f = desired switching frequency during continuous inductor current

V<sub>PCH</sub> = the voltage drop across the internal P-channel switch

V<sub>NCH</sub> = the voltage drop across the internal N-channel synchronous rectifier

Switching frequency decreases as load current is decreased below the 625mA Idle Mode trip point.

#### **Internal Reference**

The 1.10V internal reference (available at REF) is accurate to  $\pm 1.5\%$  over the -40°C to +85°C operating range, making it useful as a precision system reference. Bypass the reference to ground with a minimum 0.1µF ceramic capacitor. For low noise and jitter performance, use a 0.47µF ceramic capacitor. The reference can supply up to 10µA for external loads. However, if tight accuracy specifications for either reference or the main output are essential, avoid reference loads in excess of 5µA. Loading the reference reduces the main output voltage slightly, according to the reference-voltage load-regulation error.

### Start-Up

To prevent the MAX1623 from false output regulation, the internal PMOS and NMOS switches will not switch on until all of the following conditions are true: the supply voltage is above the undervoltage lockout threshold, \$\overline{SHDN}\$ is pulled high, the internal reference voltage is at 75% of its nominal (1.1V) value, and the die temperature is below +145°C. When the above conditions are satisfied, the MAX1623 will regulate the output voltage to the selected level. The MAX1623 typically starts up in 1ms for full output load.

### Thermal Shutdown and Overload Conditions

Thermal overload protection limits the MAX1623's total power dissipation. When the junction temperature reaches  $T_j = +145\,^{\circ}\text{C}$ , the device turns off, allowing it to cool down. Switching resumes after the IC's junction temperature decreases by 20°C. If the thermal overload condition persists, the output pulses on and off.

Thermal overload protection is designed to protect the MAX1623 during fault conditions, such as an output short circuit.

#### **Thermal Resistance**

Junction to ambient thermal resistance ( $\theta_{JA}$ ) strongly depends on the amount of copper area immediately surrounding the IC's leads. The MAX1623 evaluation kit has  $0.8in^2$  of copper area.  $\theta_{JA}$  on this board was measured to have  $45^{\circ}\text{C/W}$  of thermal resistance with no air

flow. A copper area of  $0.4 \mathrm{in}^2$  showed thermal resistance of  $60^{\circ}\mathrm{C/W}$ .

Airflow over the IC can significantly reduce  $\theta_{JA}$ .

### **Power Dissipation**

The MAX1623's power dissipation consists mostly of conduction losses in the two internal power switches. Power dissipation due to supply current in the control section and average current used to charge and discharge the gate capacitance of the two power switches is less than 30mW at 300kHz. This number is reduced when switching frequency is reduced as the part enters Idle Mode.

Combined conduction loss in the two power switches is calculated by:

$$PD = ILOAD^2 (RON)$$

where  $R_{ON} = 100 \text{m}\Omega$  (max).

The  $\theta_{\text{JA}}$  required to deliver this amount of power is calculated by:

$$\theta_{JA} = (T_{J(MAX)} - T_{A(MAX)}) / P_{D}$$

where:

T<sub>J</sub>(MAX) = maximum allowed junction temperature T<sub>A</sub>(MAX) = maximum ambient temperature expected

# \_Applications Information

### **Inductor L1**

The inductor value can be adjusted to optimize the design for size, cost, and efficiency. Three key inductor parameters must be specified: inductance value (L), peak current (IPEAK), and DC resistance (RDC). The following equation includes a constant, denoted as LIR, which is the ratio of inductor peak-to-peak AC current to DC load current. A higher value of LIR allows smaller inductance, but results in higher losses and ripple. A good compromise between size and losses is found at a 30% ripple current to load current ratio (LIR = 0.3), which corresponds to a peak inductor current 1.15 times the DC load current:

$$L = \frac{V_{OUT}(V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \cdot f \cdot (I_{OUT}) (LIR)}$$

where:

f = switching frequency

IOUT = maximum DC load current

LIR = ratio of AC to DC inductor current, typically 0.3

Table 2. Suggested Values ( $V_{IN} = 5V$ ,  $I_O = 3A$ , f = 300kHz)

| Vout<br>(V) | T <sub>OFF</sub><br>(µs) | R <sub>TOFF</sub> ( $k\Omega$ ) | L<br>(µH) |

|-------------|--------------------------|---------------------------------|-----------|

| 3.3         | 1.10                     | 120                             | 4.7       |

| 2.5         | 1.67                     | 180                             | 4.7       |

| 1.8         | 2.16                     | 240                             | 4.7       |

| 1.5         | 2.38                     | 260                             | 3.9       |

| 1.1         | 2.68                     | 280                             | 3.3       |

The peak inductor current at full load is 1.15 • IOUT if the above equation is used; otherwise, the peak current can be calculated by:

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT}(V_{IN(MAX)} - V_{OUT})}{2 \cdot f \cdot L \cdot V_{IN(MAX)}}$$

The inductor's DC resistance is a key parameter for efficiency and must be minimized, preferably to less than  $25\text{m}\Omega$  at  $\text{I}_{\text{OUT}}=3\text{A}$ . To reduce EMI, use a shielded inductor.

# Input and Output Filter Capacitors (C1, C2)

Use a low-ESR input capacitor according to the input ripple-current requirements and voltage rating.

$$I_{RIPPLE} = I_{LOAD} \left( \sqrt{\frac{V_{OUT} (V_{IN} - V_{OUT})}{V_{IN}}} \right)$$

In addition to C1, place a 10µF ceramic bypass capacitor from the power input (pin 2, 4, 6) to power ground (pin 15, 17, 19) within 5mm of the IC.

The output filter capacitor determines the output voltage ripple and output load-transient response, as well as the loop's stability.

The output ripple in continuous-conduction mode is:

$$V_{OUT(RPL)} = I_{OUT(MAX)} \cdot LIR \left( ESR_{C2} + \frac{1}{2\pi \cdot f \cdot C2} \right)$$

where f is the switching frequency.

### **Loop Stability**

Stable operation requires the right output filter capacitor. When choosing the output capacitor, ensure the following conditions are met:

$$C_2 \ge 80 \cdot t_{OFF} \cdot \frac{V_{REF}}{V_{OUT}}$$

and

$10m\Omega \le RESR, C_2 \le 50m\Omega$

### **Circuit Layout and Grounding**

Good layout is necessary to achieve the intended output power level, high efficiency, and low noise. Good layout includes the use of a ground plane, appropriate component placement, and correct routing of traces using appropriate trace widths. For heatsinking purposes, copper area connected at the IC should be evenly distributed among the high-current pins.

1) Minimize high-current ground loops. Connect the input capacitor's ground, output capacitor's ground, and IC PGND together.

- 2) A ground plane is essential for optimum performance. In most applications, the circuit will be located on a multilayer board, and full use of the four or more copper layers is recommended. Use the top and bottom layers for interconnections and the inner layers for an uninterrupted ground plane.

- Place the LX node components as close together as possible. This reduces resistive and switching losses and confines noise due to ground inductance.

- 4) Connect the input filter capacitor less than 10mm away from IN. The connecting copper trace carries large currents and must be at least 2mm wide, preferably 5mm.

- Connect GND directly to PGND at only one point near the IC.

\_\_\_Chip Information

TRANSISTOR COUNT: 1220

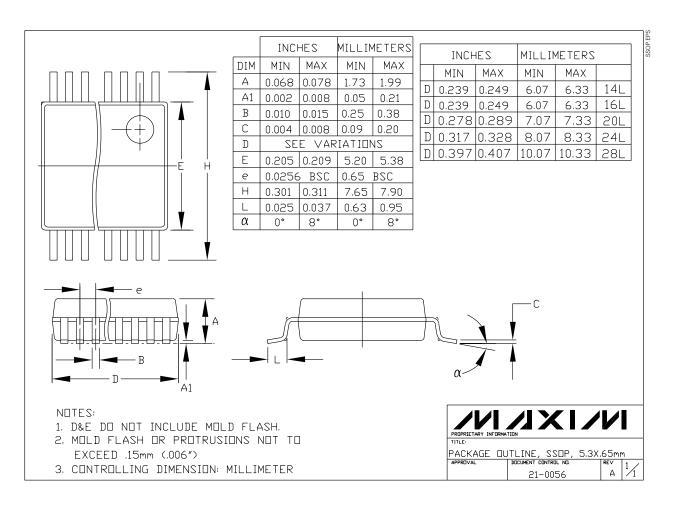

## **Package Information**