#### **General Description**

The MAX9973/MAX9974 fully integrated, high-performance, dual-channel pin electronics driver/comparator/load (DCL) with built-in level-setting digital-to-analog converters (DACs) are ideally suited for memory and SOC automatic test equipment (ATE) applications. Each channel includes a three-level pin driver, a window comparator, dynamic clamps, a 1k $\Omega$  load, and seven independent level-setting DACs.

The driver features a wide voltage range and high-speed operation, includes high-impedance and active-termination (3rd-level drive) modes, and is highly linear even at low voltage swings. Additionally, the driver provides highspeed differential multiplexer control inputs, with internal termination resistors that are compatible with ECL, LV-PECL, LVDS, and GTL. The window comparators provide extremely low timing variation over changes in slew rate, pulse width, or overdrive voltage, and have open-collector outputs. When high-impedance mode is selected, the dynamic clamps provide damping of high-speed deviceunder-test (DUT) waveforms. The load facilitates fast contact testing when used in conjunction with the comparators, and functions as a pullup for open-drain/collector DUT outputs. The MAX9973/ MAX9974 are configured through a serial interface.

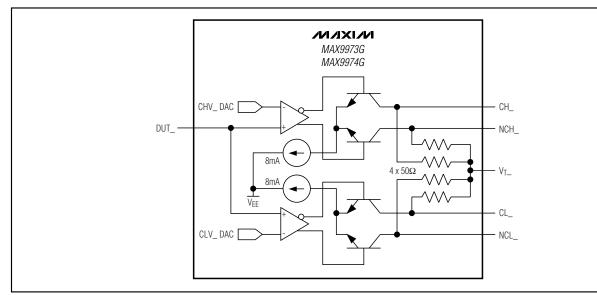

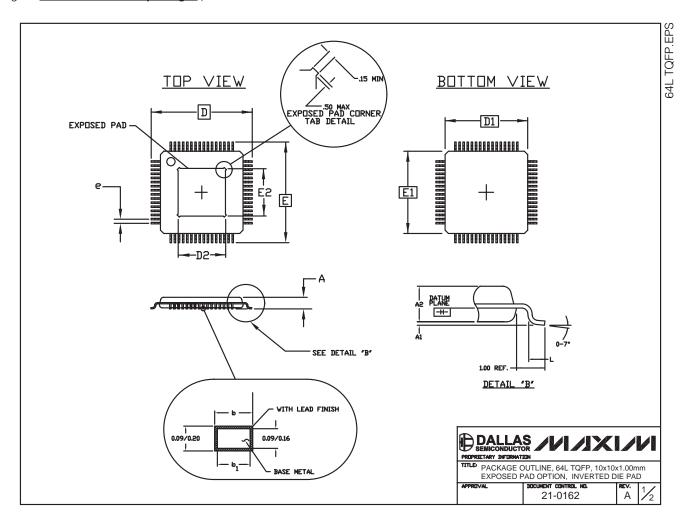

The MAX9973/MAX9974 differ in two aspects: the position of the exposed heat slug and the pin arrangement. The MAX9973G/MAX9974G comparator outputs sink 8mA (typ), while the MAX9973H/MAX9974H comparator outputs sink 16mA (typ). The devices are available in a 64-pin (10mm x 10mm x 1.00mm) TQFP-EP package with an exposed paddle on top (MAX9973) or bottom (MAX9974) for heat removal. Power dissipation is only 700mW per channel. The full operating voltage range is -1.5V to +6.5V. Operation is specified at an internal die temperature of +40°C to +100°C, and features a temperature monitor output.

#### **Applications**

Memory Testers SOC Testers

SPI is a trademark of Motorola Inc.

#### **\_Features**

- ♦ 600Mbps at 3V High Speed

- 700mW per Channel Extremely Low Power Dissipation

- ♦ -1.5V to +6.5V Wide Voltage Range

- ♦ 200mV to 8V Wide Voltage Swing Range

- 10nA (max) Low-Leakage Mode

- Integrated Termination On-the-Fly (3rd-Level Drive)

- Integrated Voltage Clamps

- Passive Load or Pullup

- Very Low Timing Dispersion

- Minimal External Component Count

- ♦ SPI<sup>TM</sup>-Compatible Serial Control Interface

|                     |                                               | 5           |                           |

|---------------------|-----------------------------------------------|-------------|---------------------------|

| PART                | PIN-PACKAGE                                   | PKG<br>CODE | OUTPUT<br>SINK<br>CURRENT |

| <b>MAX9973</b> GCCB | 64 TQFP-EP-IDP**<br>(10mm x 10mm x<br>1.00mm) | C64E-13R    | 8mA                       |

| MAX9973HCCB*        | 64 TQFP-EP-IDP**<br>(10mm x 10mm x<br>1.00mm) | C64E-13R    | 16mA                      |

| MAX9974GCCB*        | 64 TQFP-EP†<br>(10mm x 10mm x<br>1.00mm)      | _           | 8mA                       |

| MAX9974HCCB*        | 64 TQFP-EP†<br>(10mm x 10mm x<br>1.00mm)      | _           | 16mA                      |

**Ordering Information**

**Note:** Devices are available in both leaded and lead-free packages. Specify lead free by adding a + symbol at the end of the part number when ordering. \*Future product—contact factory for availability. \*\*EP-IDP = Exposed paddle (inverted die paddle). †EP = Exposed paddle.

Pin Configuration appears at end of data sheet.

# MAX9973/MAX9974

####

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                   | 0.3V to +11V  |

|------------------------------------------|---------------|

| VEE to GND                               | 6V to +0.3V   |

| V <sub>CC</sub> - V <sub>EE</sub>        | 0.3V to +17V  |

| V <sub>DD</sub> to GND                   | 0.3V to +5V   |

| V <sub>T0</sub> , V <sub>T1</sub> to GND | 0.3V to +5V   |

| DGS to GND                               | ±0.7V         |

| DUT_ to GND                              | 2.5V to +7.5V |

| DATA_, NDATA_, RCV_, NRCV_ to GND        | 2.5V to +5V   |

| DATA_ to NDATA_, RCV_ to NRCV            | ±1V           |

| DATA_, NDATA_, RCV_, NRCV_ to VTERM_     | ±1.5V         |

| 0.3V to (V <sub>DD</sub> + 0.3V)       |

|----------------------------------------|

| 0.2V to +5V                            |

| EE - 0.3V) to (V <sub>CC</sub> + 0.3V) |

| Continuous                             |

|                                        |

| above +70°C)10.0W*                     |

| 65°C to +150°C                         |

| +150°C                                 |

| +300°C                                 |

|                                        |

\*Dissipation wattage values are based on still air with no heat sink. Actual maximum power dissipation is a function of heat extraction technique and may be substantially higher.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_{T_} = +1.8V, R_T = 50\Omega$  II 1pF, T<sub>J</sub> = +70°C, unless otherwise noted. All temperature coefficients are measured at T<sub>J</sub> = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                                              | SYMBOL                  | CONDITIONS                                                                            | MIN   | ТҮР | MAX   | UNITS |

|--------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------|-------|-----|-------|-------|

| DRIVER                                                 |                         |                                                                                       |       |     |       |       |

| DC CHARACTERISTICS ( $R_L \ge 10$                      | DM $\Omega$ , unless of | otherwise noted; includes DAC error)                                                  |       |     |       |       |

|                                                        | V <sub>DHV</sub> _      | $V_{DLV_} = -1.5V, V_{DTV_} = +1.5V$                                                  | -1.45 |     | +6.50 |       |

| Output Voltage Range                                   | V <sub>DLV</sub> _      | V <sub>DHV</sub> = +6.5V, V <sub>DTV</sub> = +1.5V                                    | -1.50 |     | +6.45 | V     |

|                                                        | V <sub>DTV</sub> _      | $V_{DHV} = +6.5V, V_{DLV} = -1.5V$                                                    | -1.50 |     | +6.50 |       |

|                                                        | V <sub>DHV</sub> _      | V <sub>DHV</sub> = +3V, V <sub>DLV</sub> = -1.5V, V <sub>DTV</sub> = +1.5V            |       |     | ±50   |       |

| Output Offset Voltage                                  | V <sub>DLV</sub> _      | V <sub>DLV</sub> = 0V, V <sub>DHV</sub> = +6.5V, V <sub>DTV</sub> = +1.5V             |       |     | ±50   | mV    |

|                                                        | V <sub>DTV</sub> _      | $V_{DTV} = +1.5V, V_{DHV} = +6.5V, V_{DLV} = -1.5V$                                   |       |     | ±50   |       |

| Output-Voltage Temperature<br>Coefficient (Notes 2, 3) |                         | DHV_, DLV_, DTV_                                                                      |       | ±75 | ±400  | µV/°C |

|                                                        | V <sub>DHV</sub> _      | $V_{DLV_} = -1.5V, V_{DTV_} = +1.5V, V_{DHV_} = 0 and +4.5V$                          | 0.998 | 1   | 1.002 |       |

| Gain                                                   | V <sub>DLV</sub> _      | V <sub>DHV</sub> = +6.5V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DLV</sub> = 0 and +4.5V | 0.998 | 1   | 1.002 | V/V   |

|                                                        | V <sub>DTV</sub> _      | $V_{DHV} = +6.5V, V_{DLV} = -1.5V, V_{DTV} = 0 and +4.5V$                             | 0.998 | 1   | 1.002 |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T = +1.8V, R_T = 50\Omega$  II 1pF, TJ = +70°C, unless otherwise noted. All temperature coefficients are measured at TJ = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                        | SYMBOL |                                                                                             | CONDITIONS                                                                                                            | MIN  | ТҮР | MAX  | UNITS |  |

|----------------------------------|--------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|--|

|                                  |        | $V_{DLV_{-}} = -1.5V, V_{DTV_{-}} = V_{DHV_{-}} = 0, +0.75V, +1.5$<br>0 to 3V +2.25V, +3V   |                                                                                                                       |      |     | ±5   |       |  |

|                                  |        | relative to calibration points at 0                                                         | V <sub>DHV</sub> = +6.5V, V <sub>DTV</sub> = +1.5V,<br>V <sub>DLV</sub> = 0, +0.75V, +1.5V,<br>+2.25V, +3V            |      |     | ±5   |       |  |

| Linearity Error                  |        | and 3V                                                                                      | V <sub>DLV</sub> = -1.5V, V <sub>DHV</sub> = +6.5V,<br>V <sub>DTV</sub> = 0, +0.75V, +1.5V,<br>+2.25V, +3V            |      |     | ±5   | mV    |  |

|                                  |        | Full range                                                                                  | $V_{DLV_} = -1.5V, V_{DTV_} = +1.5V, V_{DHV_} = -1.25V \text{ and } +6.5V$                                            |      |     | ±5   |       |  |

|                                  |        | relative to<br>calibration<br>points at 0                                                   | $V_{DHV_}$ = +6.5V, $V_{DTV_}$ = +1.5V, $V_{DLV_}$ = -1.5V and +6.25V                                                 |      |     | ±5   |       |  |

|                                  |        | and 3V                                                                                      | $V_{DLV_} = -1.5V, V_{DHV_} = +6.5V, V_{DTV_} = -1.5V \text{ and } +6.5V$                                             |      |     | ±5   |       |  |

|                                  |        | $V_{DHV}$ to $V_{DLV}$ , $V_{DLV} = 0$ ,<br>$V_{DTV} = 1.5V$ , $V_{DHV} = 0.2V$ and 6.5V    |                                                                                                                       |      |     | ±2   |       |  |

|                                  |        | $V_{DLV}$ to $V_{DHV}$ , $V_{DHV}$ = +5V,<br>$V_{DTV}$ = +1.5V, $V_{DLV}$ = -1.5V and +4.8V |                                                                                                                       |      |     | ±2   |       |  |

| Crosstalk                        |        |                                                                                             | $V_{\rm DHV}, V_{\rm DHV} = +3V, V_{\rm V} = -1.5V$ and +6.5V                                                         |      |     | ±2   | mV    |  |

|                                  |        |                                                                                             | v, V <sub>DTV</sub> _ = +1.5V,<br>⊣v_ = +1.6V and +3.0V                                                               |      |     | ±3   |       |  |

|                                  |        |                                                                                             | /, V <sub>DTV</sub> _ = +1.5V,<br>√ <sub>DLV</sub> _ = 0 and +1.4V                                                    |      |     | ±3   | _     |  |

| Term Voltage Dependence on DATA_ |        |                                                                                             | V, $V_{DHV} = +3V$ ,<br>ATA_ = 0 and 1                                                                                |      |     | ±2   | mV    |  |

|                                  |        |                                                                                             | V <sub>DHV</sub> , V <sub>DHV</sub> = 3V, V <sub>CC</sub> and V <sub>EE</sub><br>independently varied over full range |      |     |      |       |  |

| DC Power-Supply Rejection        |        |                                                                                             | = 0, V <sub>CC</sub> and V <sub>EE</sub><br>y varied over full range                                                  | 40   |     |      | dB    |  |

|                                  |        |                                                                                             | = 1.5V, V <sub>CC</sub> and V <sub>EE</sub><br>y varied over full range                                               | 40   |     |      |       |  |

|                                  |        | V <sub>DLV</sub> _/V <sub>DUT</sub> _                                                       | = -1.5V/+6.5V, DATA_ = 0                                                                                              | -120 |     | -60  |       |  |

| DC Drive Current Limit           |        | $V_{DHV}/V_{DUT} = +6.5V/-1.5V, DATA_ = 1$                                                  |                                                                                                                       | +60  |     | +120 | m^    |  |

|                                  |        |                                                                                             | = -1.5V/+6.5V, RCV_ = 1                                                                                               | -120 |     | -60  | - mA  |  |

|                                  |        |                                                                                             | = +6.5V/-1.5V, RCV_ = 1                                                                                               | +60  |     | +120 |       |  |

| DC Output Resistance             |        | (Note 4)                                                                                    |                                                                                                                       | 48   | 50  | 52   | Ω     |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T = +1.8V, R_T = 50\Omega$  II 1pF, T<sub>J</sub> = +70°C, unless otherwise noted. All temperature coefficients are measured at T<sub>J</sub> = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL                | CONDITIONS                                                                                      | MIN | ТҮР  | MAX | UNITS |

|-----------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DC Output Resistance Variation                |                       | DATA_ = 1, $V_{DHV}$ = 3V, $V_{DLV}$ = 0,<br>$V_{DTV}$ = 1.5V, $I_{DUT}$ = 1mA to 40mA          |     | 1    | 2   | Ω     |

|                                               |                       | DATA_ = 0, $V_{DHV}$ = 3V, $V_{DLV}$ = 0,<br>$V_{DTV}$ = 1.5V, $I_{DUT}$ = -1mA to -40mA        |     | 1    | 2   | 52    |

| AC CHARACTERISTICS (RDUT_ =                   | : 50 $\Omega$ to grou | und) (Note 5)                                                                                   |     |      |     |       |

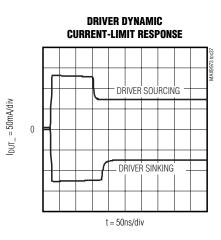

| Dynamic Drive Current                         |                       | (Note 6)                                                                                        |     | 60   |     | mA    |

|                                               |                       | $V_{DLV_{}} = 0, V_{DHV_{}} = 0.1V$                                                             |     | 30   |     |       |

| Drive Made Oversheet                          |                       | $V_{DLV_} = 0, V_{DHV_} = 1V$ (Note 2)                                                          |     | 40   | 75  |       |

| Drive-Mode Overshoot                          |                       | V <sub>DLV</sub> = 0, V <sub>DHV</sub> = 3V (Note 2)                                            |     | 50   | 175 | mV    |

|                                               |                       | $V_{DLV_} = 0, V_{DHV_} = 5V$ (Note 2)                                                          |     | 50   | 275 |       |

| Termination-Mode Overshoot                    |                       | (Note 7)                                                                                        |     | 0    |     | mV    |

|                                               |                       | To within 100mV, $V_{DHV} = 5V$ , $V_{DLV} = 0$                                                 |     | 0.25 |     |       |

| Settling Time (Note 8)                        |                       | To within 50mV, $V_{DHV} = 3V$ , $V_{DLV} = 0$                                                  |     | 0.25 |     | ns    |

|                                               |                       | To within 25mV, $V_{DHV} = 0.5V$ , $V_{DLV} = 0$                                                |     | 0.25 |     | ]     |

| TIMING CHARACTERISTICS (Not                   | es 5, 9)              | •                                                                                               |     |      |     |       |

|                                               |                       | Data to output; $V_{DHV} = 3V$ , $V_{DLV} = 0$                                                  |     | 2    | 3   |       |

| Prop Delay (Note 2)                           |                       | Drive to high impedance, high impedance to drive (Note 10); $V_{DHV} = +1V$ , $V_{DLV} = -1V$   |     | 1.7  | 4   | ns    |

|                                               |                       | Drive to term                                                                                   |     | 2.7  | 4   | -     |

|                                               |                       | Term to drive                                                                                   |     | 1.7  | 4   |       |

| Prop Delay Match                              |                       | tLH vs. tHL                                                                                     |     | 50   | 100 |       |

| (Note 2)                                      |                       | Drivers within package; same edge                                                               |     | 40   | 100 | ps    |

| Prop-Delay Temperature Coefficient            |                       | (Note 2)                                                                                        |     | 1    | 5   | ps/°C |

|                                               |                       | $V_{DHV}$ = 1V, $V_{DLV}$ = 0, 2ns to 23ns pulse width                                          |     | 10   | 100 |       |

| Prop Delay Change vs.<br>Pulse Width (Note 2) |                       | $V_{DHV}$ = 3V, $V_{DLV}$ = 0, 3ns to 22ns pulse width                                          |     | 10   | 100 | ps    |

|                                               |                       | $V_{DHV} = 5V$ , $V_{DLV} = 0$ , 4ns to 21ns pulse width                                        |     | 20   | 100 |       |

| Prop Delay Change vs.<br>Common Mode          |                       | $V_{DHV} - V_{DLV} = 1V$ , $V_{DHV} = 0$ to 6V,<br>(using a DC block)                           |     | 25   |     | ps    |

|                                               |                       | Drive to high impedance vs. high impedance to drive; $V_{DHV} = 1V$ , $V_{DLV} = -1V$ (Note 11) |     | 0.2  |     |       |

| Delay Matab                                   |                       | High impedance vs. data (Note 2)                                                                |     | 0.4  |     | 1     |

| Delay Match                                   |                       | Drive to term vs. term to drive; $V_{DHV} = 3V$ ,<br>$V_{DLV} = 0$ , $V_{DTV} = 1.5V$ (Note 12) |     | 1    |     | ns    |

|                                               |                       | Terminate vs. data                                                                              |     | 0.7  |     | 1     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T_ = +1.8V, R_T = 50\Omega$  II 1pF, T<sub>J</sub> = +70°C, unless otherwise noted. All temperature coefficients are measured at T<sub>J</sub> = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                         | SYMBOL |                                                                                                          | CONDITIONS                                                                                                 | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------|--------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                   |        | 0.2VP-P programmed, V <sub>DHV</sub> = 0.2V, V <sub>DLV</sub> = 0, 20% to 80%                            |                                                                                                            |      | 0.20 |      |       |

| Rise and Fall Time                |        | 1V <sub>P-P</sub> program<br>10% to 90%                                                                  | mmed, $V_{DHV} = 1V$ , $V_{DLV} = 0$ ,                                                                     | 0.35 | 0.50 | 0.75 |       |

|                                   |        |                                                                                                          | ammed, $V_{DHV} = 3V$ , $V_{DLV} = 0$ , trim condition                                                     | 1.0  | 1.2  | 1.5  | ns    |

|                                   |        | 5V <sub>P-P</sub> progra<br>10% to 90%                                                                   | ammed $V_{DHV} = 5V$ , $V_{DLV} = 0$ ,                                                                     |      | 2.0  |      |       |

|                                   |        | 0.2V <sub>P-P</sub> progr<br>20% to 80%                                                                  | rammed, $V_{DHV} = 0.2V$ , $V_{DLV} = 0$ ,                                                                 |      | 40   |      |       |

| Diag and Fall Time Matching       |        | 1V <sub>P-P</sub> program<br>10% to 90%                                                                  | mmed, $V_{DHV} = 1V$ , $V_{DLV} = 0$ ,                                                                     |      |      | 150  |       |

| Rise and Fall Time Matching       |        | 3V <sub>P-P</sub> progra<br>10% to 90                                                                    | ammed, $V_{DHV} = 3V$ , $V_{DLV} = 0$ ,                                                                    |      |      | 200  | ps    |

|                                   |        | $5V_{P-P}$ programmed, $V_{DHV_} = 5V$ , $V_{DLV_} = 0$ ,<br>10% to 90% (Note 2)                         |                                                                                                            |      |      |      |       |

|                                   | to SC  | Relative<br>to SC1 =<br>SC0 = 0                                                                          | $\begin{split} SC1 &= 0,  SC0 = 1,  V_{DHV\_} = 3V, \\ V_{DLV\_} &= 0,  20\% \text{ to } 80\% \end{split}$ |      | 75   |      | %     |

| Slew Rate                         |        |                                                                                                          | $SC1 = 1, SC0 = 0, V_{DHV_} = 3V, V_{DLV_} = 0, 20\%$ to 80%                                               |      | 50   |      |       |

|                                   |        |                                                                                                          | $SC1 = 1, SC0 = 1, V_{DHV} = 3V, V_{DLV} = 0, 20\% to 80\%$                                                |      | 25   |      |       |

|                                   |        |                                                                                                          | $0.2V_{P-P}$ programmed,<br>$V_{DHV} = 0.2V$ , $V_{DLV} = 0$                                               |      | 0.4  |      | - ns  |

|                                   |        | Positive or                                                                                              | $1V_{P-P}$ programmed $V_{DHV_} = 1V$ ,<br>$V_{DLV_} = 0$ (Note 2)                                         |      | 0.7  | 2    |       |

| Minimum Pulse Width (Note 13)     |        | negative                                                                                                 | $3V_{P-P}$ programmed $V_{DHV_} = 3V$ ,<br>$V_{DLV_} = 0$ (Note 2)                                         |      | 1.5  | 2.5  |       |

|                                   |        |                                                                                                          | 5VP-P programmed $V_{DHV} = 5V$ ,<br>V <sub>DLV</sub> = 0 (Note 2)                                         |      | 2.4  | 3.5  |       |

|                                   |        | 0.2V <sub>P-P</sub> prog                                                                                 | rammed, $V_{DHV} = 0.2V$ , $V_{DLV} = 0$                                                                   |      | 2900 |      |       |

| Data Data (Nata 14)               |        | 1VP-P progra                                                                                             | ammed, $V_{DHV} = 1V$ , $V_{DLV} = 0$                                                                      |      | 1300 |      | Mbr - |

| Data Rate (Note 14)               |        | 3V <sub>P-P</sub> progra                                                                                 | ammed, $V_{DHV} = 3V$ , $V_{DLV} = 0$                                                                      |      | 600  |      | Mbps  |

|                                   |        | $5V_{P-P}$ programmed, $V_{DHV} = 5V$ , $V_{DLV} = 0$                                                    |                                                                                                            |      | 400  |      |       |

| Rise and Fall Time, Drive to Term |        | V <sub>DHV</sub> = 3V, V <sub>DLV</sub> = 0, V <sub>DTV</sub> = 1.5V,<br>measured 10% to 90% of waveform |                                                                                                            |      | 1.6  |      | ns    |

| Rise and Fall Time, Term to Drive |        |                                                                                                          | V <sub>DLV</sub> = 0, V <sub>DTV</sub> = 1.5V,<br>0% to 90% of waveform                                    |      | 0.7  |      | ns    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                         | SYMBOL           | CONDITIONS                                                                             | MIN  | ТҮР  | MAX              | UNITS |

|---------------------------------------------------|------------------|----------------------------------------------------------------------------------------|------|------|------------------|-------|

| COMPARATOR                                        |                  |                                                                                        |      |      |                  |       |

| DC CHARACTERISTICS                                |                  |                                                                                        |      |      |                  |       |

| Input Voltage Range                               |                  |                                                                                        | -1.5 |      | +6.5             | V     |

| Differential Input Voltage                        |                  |                                                                                        |      |      | ±8               | V     |

| Minimum Hysteresis                                |                  | RHYST_ = open                                                                          |      | 0    |                  | mV    |

| Maximum Hysteresis                                |                  | $R_{RHYST} = 2.5k\Omega$                                                               |      | 10   |                  | mV    |

| Input Offset Voltage                              |                  | V <sub>DUT</sub> = 1.5V                                                                |      |      | ±50              | mV    |

| Input-Voltage Temperature<br>Coefficient          |                  | (Notes 2, 15)                                                                          |      | ±75  | ±400             | µV/°C |

| Common-Mode Rejection Ratio                       | CMRR             | V <sub>DUT</sub> = -1.5V, +6.5V                                                        | 50   | 70   |                  | dB    |

| Linearity Error, 0 to 3V                          |                  | V <sub>DUT</sub> = 0, 1.5V, 3V (Note 16)                                               |      | ±1   | ±5               | mV    |

| Linearity Error, Full Range                       |                  | V <sub>DUT</sub> = -1.5V, 0, +1.5V, +3V, +6.5V (Note 16)                               |      | ±1   | ±10              | mV    |

| Power-Supply Rejection Ratio                      | PSRR             | V <sub>DUT</sub> = -1.5V and +6.5V                                                     | 50   | 75   |                  | dB    |

| AC CHARACTERISTICS (Notes 1                       | 7–20)            | ·                                                                                      |      |      |                  | •     |

| Minimum Pulse Width                               |                  | (Note 21)                                                                              |      | 0.85 |                  | ns    |

| Prop Delay                                        |                  |                                                                                        |      | 1.2  | 2                | ns    |

| Prop-Delay Temperature<br>Coefficient             |                  | (Note 2)                                                                               |      | 2.6  | 5                | ps/°C |

| Prop Delay Match                                  |                  | High/low vs. low/high; absolute value of delta for each comparator (Note 2)            |      | 40   | 100              | ps    |

| Prop Delay Dispersion vs.<br>Common-Mode Input    |                  | Common-mode input -1.4V to +6.4V<br>(Note 22)                                          |      | 20   |                  | ps    |

| Prop Delay Dispersion vs. Pulse<br>Width (Note 2) |                  | 3ns to 22ns pulse width, 500ps t <sub>RISE</sub> , positive and negative pulses        |      | 10   | 60               | ps    |

| Width (Note 2)                                    |                  | 2ns to 23ns pulse width                                                                |      | 10   | 100              |       |

| Prop Delay Dispersion vs.<br>Slew Rate            |                  | Slew rate = 0.5V/ns to 2V/ns                                                           |      | 10   |                  | ps    |

|                                                   |                  | 100mV < V <sub>C_V</sub> < 900mV, driver in term mode, peak-to-peak within this window |      | 40   |                  |       |

| Waveform Tracking<br>(Note 23)                    |                  | $50mV < V_{C_V} < 950mV$ , driver in term mode, peak-to-peak within this window        |      | 60   |                  | ps    |

|                                                   |                  | 100mV < $V_{C_V}$ < 900mV, driver in high impedance, peak-to-peak within this window   |      | 100  |                  |       |

| LOGIC OUTPUTS (CH_, NCH_, C                       | L_, NCL_)        |                                                                                        |      |      |                  |       |

| Termination Voltage                               | V <sub>T</sub> _ |                                                                                        | 0    |      | 3.5              | V     |

| Output Voltage Compliance                         |                  | Set by $I_{OUT}$ , $R_{TERM}$ , and $V_{T}$                                            | -0.5 |      | V <sub>T</sub> _ | V     |

| Differential Rise Time                            |                  | 20% to 80% (Note 2)                                                                    |      | 200  | 400              | ps    |

| Differential Fall Time                            |                  | 20% to 80% (Note 2)                                                                    |      | 200  | 400              | ps    |

M/X/W

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T_ = +1.8V, R_T = 50\Omega$  II 1pF, TJ = +70°C, unless otherwise noted. All temperature coefficients are measured at TJ = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL | CONDITIONS                                                                      | MIN                        | ТҮР                        | MAX              | UNITS  |  |

|-------------------------------------------|--------|---------------------------------------------------------------------------------|----------------------------|----------------------------|------------------|--------|--|

| Termination Resistor Value                |        | VT_ to CH_, NCH_, CL_, NCL_                                                     | 48                         |                            | 52               | Ω      |  |

| Output High Voltage                       |        | V <sub>T</sub> = 0, 3.5V                                                        | V <sub>T</sub> _<br>- 0.1  | V <sub>T</sub> _<br>- 0.02 | V <sub>T</sub> _ | V      |  |

| Output Low Voltage                        |        | V <sub>T</sub> _ = 0, 3.5V                                                      | V <sub>T</sub> _<br>- 0.55 | V <sub>T_</sub><br>- 0.4   | VT_<br>- 0.35    | V      |  |

| Output Voltage Swing                      |        | V <sub>T</sub> _ = 0, 3.5V                                                      | 350                        | 400                        | 450              | mV     |  |

| DYNAMIC CLAMPS                            |        | · · ·                                                                           |                            |                            |                  |        |  |

| Eurotional Clarge Dange                   |        | CPHV_; I <sub>DUT</sub> _ = -1mA, CPHV_ = -0.4V and<br>+6.6V, CPLV_ = -1.5V     | -0.3                       |                            | +6.5             | V      |  |

| Functional Clamp Range                    |        | CPLV_; I <sub>DUT</sub> _ = 1mA, CPLV_ = -1.6V and<br>+5.4V, CPHV_ = +6.5V      | -1.5                       |                            | +5.3             | V      |  |

| Maximum Programmable CPHV_                |        | I <sub>DUT</sub> = 0mA (Note 24)                                                | 7.2                        | 7.5                        |                  | V      |  |

| Minimum Programmable CPLV_                |        | I <sub>DUT</sub> = 0mA (Note 24)                                                |                            | -2.5                       | -2.2             | V      |  |

| Offact Voltage                            |        | I <sub>DUT</sub> = -1mA, CPHV = +1.5V, CPLV = -1.5V                             |                            |                            | ±50              | m\/    |  |

| Offset Voltage                            |        | I <sub>DUT</sub> = +1mA, CPLV_ = +1.5V, CPHV_ = +6.5V                           |                            |                            | ±50              | mV     |  |

| Offset-Voltage Temperature<br>Coefficient |        |                                                                                 |                            | 0.5                        |                  | mV/°C  |  |

| Power-Supply Rejection                    |        | I <sub>DUT</sub> = -1mA, CPHV_ = +1.5V, CPLV_ = -1.5V                           | 40                         |                            |                  | ٩D     |  |

|                                           |        | I <sub>DUT</sub> = +1mA, CPLV_ = +1.5V, CPHV_ = +6.5V                           | 40                         |                            |                  | dB     |  |

| High-Clamp Voltage Gain                   |        | CPHV_ = 0, +6.5V, CPLV_ = -1.5V                                                 | 0.99                       |                            | 1.01             | V/V    |  |

| Low-Clamp Voltage Gain                    |        | CPLV_ = -1.5V, +5.3V, CPHV_ = +6.5V                                             | 0.99                       |                            | 1.01             | V/V    |  |

| Voltage Gain Matching                     |        |                                                                                 |                            |                            | 1                | %      |  |

| Voltage-Gain Temperature<br>Coefficient   |        |                                                                                 |                            | 100                        |                  | ppm/°C |  |

|                                           |        | I <sub>DUT</sub> = -1mA, CPHV = 0, +1.5V, +3.25V,<br>+5V, +6.5V                 |                            |                            | ±30              |        |  |

| Linearity                                 |        | I <sub>DUT</sub> = +1mA, CPLV = -1.5V, +0.5V, +2.25V,<br>+4V, +5.3V             |                            |                            | ±30              | - mV   |  |

|                                           |        | CPHV_ = 0, CPLV_ = -1.5V, $R_L = 0\Omega$ to +6.5V                              | -120                       |                            | -60              |        |  |

| Static Output Current                     |        | CPLV_ = +5V, CPHV_ = +6.5V, R <sub>L</sub> = $0\Omega$ to -1.5V                 | 60                         |                            | 120              | mA     |  |

|                                           |        | High clamp, $V_{CPHV} = 2.5V$ ,<br>IDUT_ = -5mA and -15mA                       | 48                         |                            | 55               |        |  |

| DC Impedance                              |        | Low clamp, V <sub>CPLV</sub> = 2.5V,<br>I <sub>DUT</sub> = 5mA and 15mA         | 48                         |                            | 55               | Ω      |  |

| DC Impedance Variation                    |        | High clamp, I <sub>DUT</sub> = -20mA and -30mA,<br>CPHV_ = +2.5V, CPLV_ = -1.5V |                            | ±5                         |                  |        |  |

| (Note 25)                                 |        | Low clamp, I <sub>DUT</sub> = 20mA and 30mA,<br>CPLV_ = 2.5V, CPHV_ = 6.5V      |                            | ±5                         |                  | Ω      |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T = +1.8V, R_T = 50\Omega$  II 1pF, TJ = +70°C, unless otherwise noted. All temperature coefficients are measured at TJ = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                        | SYMBOL          | CONDITIONS                                         | MIN                       | ТҮР  | MAX                       | UNITS |

|----------------------------------|-----------------|----------------------------------------------------|---------------------------|------|---------------------------|-------|

| Overshoot and Undershoot         |                 | (Note 26)                                          |                           | 650  |                           | mV    |

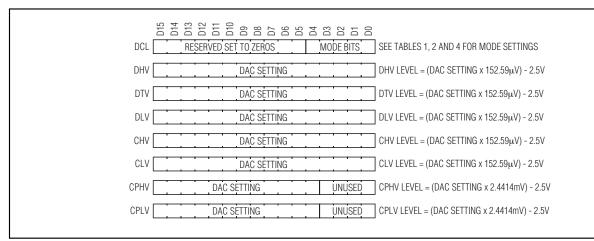

| LEVEL-SETTING DACs               |                 |                                                    |                           |      |                           |       |

| Desclution                       | N               | DHV_, DLV_, DTV_, CHV_, CLV_                       |                           | 16   |                           | Dite  |

| Resolution                       | N               | CPLV_, CPHV_                                       |                           | 12   |                           | Bits  |

| Differential Nonlinearity        | DNL             |                                                    |                           |      | ±1                        | mV    |

| Voltage Settling Time            |                 | Full-scale change to ±2.5mV                        |                           | 20   |                           | μs    |

| GROUND SENSE (DGS)               | 7               |                                                    |                           |      |                           |       |

| Input Range                      | V <sub>GS</sub> | Relative to AGND_, verified by functional test     | -250                      |      | +250                      | mV    |

| Gain                             |                 |                                                    |                           | 1    |                           | V/V   |

| Input Resistance                 |                 |                                                    | 1                         |      |                           | MΩ    |

| Reference Input                  |                 | (Note 27)                                          |                           | 2.5  |                           | V     |

| 1k TRI-STATE LOAD (PULLUP        | /PULLDOWN)      | 1                                                  |                           |      |                           | -     |

| Source Impedance When<br>Enabled |                 | Tested at -5mA, 0, +5mA using a 0.5mA step         | 950                       |      | 1050                      | Ω     |

| Maximum Source Current           |                 | V <sub>DUT</sub> = +6.1V, V <sub>DTV</sub> = -1.1V | 6.9                       | 7.2  |                           | mA    |

| Maximum Sink Current             |                 | $V_{DUT} = -1.1V, V_{DTV} = +6.1V$                 | 6.9                       | 7.2  |                           | mA    |

| Turn-On Time                     |                 |                                                    |                           | 60   |                           | ns    |

| Turn-Off Time                    |                 |                                                    |                           | 60   |                           | ns    |

| Offset Voltage                   |                 | Output with no load, $V_{DTV_} = 0$ and $3V$       |                           |      | ±50                       | mV    |

| Linearity Error                  |                 | No load, $V_{DTV_}$ = -1.5V to +6.5V               |                           |      | ±25                       | mV    |

| TEMPERATURE MONITOR              |                 |                                                    |                           |      |                           |       |

| Nominal Voltage                  |                 | $T_J = +70^{\circ}C, R_L \ge 10M\Omega$            |                           | 3.43 |                           | V     |

| Temperature Coefficient          |                 |                                                    |                           | 10   |                           | mV/°C |

| Output Resistance                |                 |                                                    |                           | 15   |                           | kΩ    |

| DIFFERENTIAL CONTROL INF         | PUTS (DATA_, N  | NDATA_, RCV_, NRCV_)                               |                           |      |                           |       |

| Input High Voltage               |                 |                                                    | -1.6                      |      | +3.5                      | V     |

| Input Low Voltage                |                 |                                                    | -2.0                      |      | +3.1                      | V     |

| Differential Input Voltage       |                 |                                                    | ±0.15                     |      | ±1.00                     | V     |

| Termination Resistor             |                 | 50 $\Omega$ to VTERM_                              | 48                        |      | 52                        | Ω     |

| VTERM_ Voltage Range             |                 | Verified by functional test                        | -2.0                      |      | +3.5                      | V     |

| SERIAL PORT INPUTS (CS, SO       | CLK, DIN, RST,  | LOAD, V <sub>DD</sub> = 3.3V)                      |                           |      |                           | -     |

| Input High                       |                 |                                                    | 2/3<br>(V <sub>DD</sub> ) |      | V <sub>DD</sub>           | V     |

| Input Low                        |                 |                                                    | -0.1                      |      | 1/3<br>(V <sub>DD</sub> ) | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV_} = +3V, V_{DLV_} = 0, V_{DTV_} = +1.5V, SC1 = SC0 = 0, V_{CHV_} = +2.0V, V_{CLV_} = +1.0V, V_{CPHV_} = +7.2V, V_{CPLV_} = -2.2V, V_{VTERM} = V_T = +1.8V, R_T = 50\Omega$  II 1pF, TJ = +70°C, unless otherwise noted. All temperature coefficients are measured at TJ = +40°C to +100°C, unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL          | CONDITIONS                                                                                                                                              | MIN  | ТҮР   | MAX  | UNITS |

|----------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

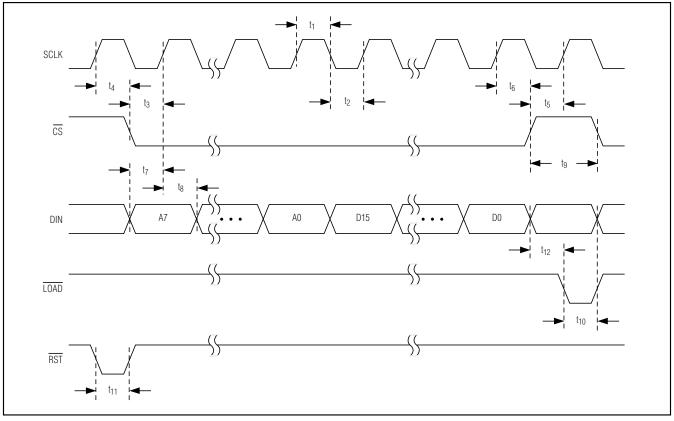

| SERIAL PORT TIMING (Note 28)           |                 | •                                                                                                                                                       | •    |       |      |       |

| SCLK Frequency                         |                 |                                                                                                                                                         |      |       | 50   | MHz   |

| SCLK Pulse-Width High                  | t1              |                                                                                                                                                         | 8    |       |      | ns    |

| SCLK Pulse-Width Low                   | t2              |                                                                                                                                                         | 8    |       |      | ns    |

| CS Low to SCLK High Setup              | t3              |                                                                                                                                                         | 3.5  |       |      | ns    |

| SCLK High to $\overline{CS}$ Low Hold  | t4              |                                                                                                                                                         | 3.5  |       |      | ns    |

| CS High to SCLK High Setup             | t5              |                                                                                                                                                         | 3.5  |       |      | ns    |

| SCLK High to $\overline{CS}$ High Hold | t <sub>6</sub>  |                                                                                                                                                         | 3.5  |       |      | ns    |

| DIN to SCLK High Setup                 | t7              |                                                                                                                                                         | 3.5  |       |      | ns    |

| DIN to SCLK High Hold                  | t8              |                                                                                                                                                         | 3.5  |       |      | ns    |

| CS High Pulse Width                    | t9              |                                                                                                                                                         | 20   |       |      | ns    |

| LOAD Low Pulse Width                   | t10             |                                                                                                                                                         | 20   |       |      | ns    |

| RST Low Pulse Width                    | t11             |                                                                                                                                                         | 20   |       |      | ns    |

| CS High to LOAD Low Hold Time          | t <sub>12</sub> |                                                                                                                                                         | 20   |       |      | ns    |

| COMMON FUNCTIONS                       |                 |                                                                                                                                                         |      |       |      |       |

| Operating Voltage Range                |                 | (Note 29)                                                                                                                                               | -1.5 |       | +6.5 | V     |

|                                        |                 | 0 < V <sub>DUT</sub> < 3V                                                                                                                               |      |       | ±2   |       |

| DUT_ High-Impedance Leakage            |                 | $V_{CLV} = V_{CHV} = +6.5V, V_{DUT} = -1.5V$                                                                                                            |      |       | ±5   | μA    |

|                                        |                 | $V_{CLV_} = V_{CHV_} = -1.5V, V_{DUT_} = +6.5V$                                                                                                         |      |       | ±5   |       |

|                                        |                 | $LEAK = 1, 0 < V_{DUT} < 3V, T_J < +90^{\circ}C$                                                                                                        | -10  |       | +10  |       |

| DUT_ Low-Leakage Mode<br>Leakage       |                 | $\label{eq:LEAK} \begin{array}{l} \mbox{LEAK} = \ 1, \ V_{CLV\_} = \ V_{CHV\_} = \ +6.5V, \\ \ V_{DUT\_} = \ -1.5V, \ T_J < \ +90^{\circ}C \end{array}$ | -10  |       | +10  | nA    |

| Leanage                                |                 | LEAK = 1, $V_{CLV_} = V_{CHV_} = -1.5V$ ,<br>$V_{DUT_} = +6.5V$ , $T_J < +90^{\circ}C$                                                                  | -10  |       | +10  |       |

| DUT Combined Conseitones               |                 | Driver in terminate mode                                                                                                                                |      | 2     |      |       |

| DUT_ Combined Capacitance              |                 | Driver in high impedance                                                                                                                                |      | 4     |      | pF    |

| POWER SUPPLY                           |                 |                                                                                                                                                         |      |       |      |       |

| Positive Supply Voltage                | V <sub>CC</sub> |                                                                                                                                                         | 9.5  | 9.75  | 10.5 | V     |

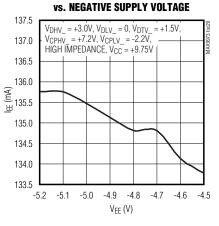

| Negative Supply Voltage                | VEE             |                                                                                                                                                         | -5.2 | -4.75 | -4.5 | V     |

| Logic Supply Voltage                   | V <sub>DD</sub> |                                                                                                                                                         | 2.7  | 3.3   | 5.0  | V     |

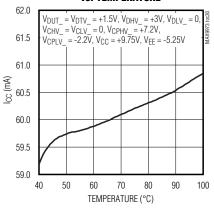

| Positive Supply Current                | ICC             | (Note 30)                                                                                                                                               |      | 70    | 85   | mA    |

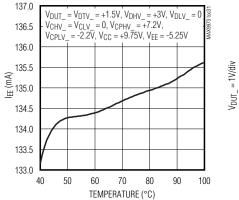

| Negative Supply Current                | IEE             | (Note 30)                                                                                                                                               |      | 150   | 180  | mA    |

| Logic Supply Current                   | IDD             | (Note 30)                                                                                                                                               |      | 1.2   | 2    | mA    |

| Power Dissipation                      |                 | (Notes 30, 31)                                                                                                                                          |      | 1.4   | 1.7  | W     |

| Power Dissipation per Channel          |                 | (Notes 30, 31)                                                                                                                                          |      | 700   |      | mW    |

|                                        | 1               |                                                                                                                                                         |      |       |      |       |

**Note 1:** All minimum and maximum specifications are 100% production tested, unless otherwise noted. All other test limits are guaranteed by design. Tests are performed at nominal supply voltages, unless otherwise noted. Tested with  $T_J = +70^{\circ}C$  with accuracy of  $\pm 15^{\circ}C$ .

**Note 2:** Guaranteed by design and characterization.

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, V_{EE} = -4.75V, V_{DD} = 3.3V, V_{DHV} = +3V, V_{DLV} = 0, V_{DTV} = +1.5V, SC1 = SC0 = 0, V_{CHV} = +2.0V, V_{CLV} = +1.0V, V_{CPHV} = +7.2V, V_{CPLV} = -2.2V, V_{VTERM} = V_T = +1.8V, R_T = 50\Omega$  II 1pF, T<sub>J</sub> = +70°C, unless otherwise noted. All temperature coefficients are measured at T<sub>J</sub> = +40°C to +100°C, unless otherwise noted.) (Note 1)

- **Note 3:** Change in any voltage over operating range. Includes both gain and offset temperature effects. Simulated over entire operating range. Verified at worst-case points, which are the endpoints. V<sub>DHV</sub> V<sub>DLV</sub> > 250mV.

- Note 4: DATA\_ = 1, V<sub>DHV</sub>\_ = 3V, V<sub>DLV</sub>\_ = 0, V<sub>DTV</sub>\_ = 1.5V, I<sub>OUT</sub> = ±30mA. Different values within the range of 48Ω to 52Ω are available by custom trimming (contact factory).

- **Note 5:** Rise time of the differential inputs DATA\_ and RCV\_ is 250ps (10% to 90%). SC1 = SC0 = 0, 40MHz, unless otherwise specified.

- Note 6: 0 to 6V step, current supplied for a minimum of 10ns.

- Note 7:  $V_{DTV_}$  = 1.5V,  $R_S$  = 50 $\Omega$  external signal driven into a transmission line to produce a 0/3V edge at the comparator input with  $\leq$  1.0ns rise time (10% to 90%). Measurement point is at comparator input.

- Note 8: Measured from the 90% point of the driver output (relative to its final value) to the waveform settling to within the specified limit.

- **Note 9:** Propagation delays are measured from the crossing point of the differential input signals to the 50% point of expected output swing.

- Note 10: Measured from crossing point of RCV\_/NRCV\_ to 50% point of the output waveform.

- Note 11: Four measurements are made: DHV\_ to high impedance, DLV\_ to high impedance, high impedance to DHV\_, high impedance to DLV\_. The worst difference is specified.

- Note 12: Four measurements are made: DHV\_ to DTV\_, DLV\_ to DTV\_, DTV\_ to DHV\_, DTV\_ to DLV\_. The worst difference is specified.

- Note 13: At this pulse width, the output reaches at least 95% of its nominal (DC) amplitude. The pulse width is measured at DATA\_ and NDATA\_.

- **Note 14:** Maximum data rate in transitions/second. A waveform that reaches at least 95% of its programmed amplitude may be generated at one-half of this frequency.

- Note 15: Change in offset at any voltage over operating range. Includes both gain (CMRR) and offset temperature effects.

- **Note 16:** Relative to straight line between 0 and 3V.

- Note 17: All propagation delays measured from V<sub>DUT</sub> crossing calibrated CHV\_/CLV\_ threshold to crossing point of differential outputs.

- **Note 18:** Load is a 500ps transmission line terminated with 1pF and  $50\Omega$ .

- Note 19: All AC specifications are measured with DUT\_ (comparator input) as the reference.

- **Note 20:** 40MHz, 0 to 2V input to comparator, reference = 1V, 50% duty cycle, 1ns rise/fall time,  $Z_S = 50\Omega$ , driver in term mode with  $V_{DTV_{-}} = 0$ , unless otherwise noted.

- **Note 21:** At this pulse width, the output reaches at least 90% of its nominal peak-to-peak swing. The pulse width is measured at the crossing points of the differential outputs. 500ps rise and fall time. Timing specs are not guaranteed.

- Note 22:  $V_{DUT_} = 200mV_{P-P}$ , rise/fall time = 150ps, overdrive = 100mV,  $V_{DTV_} = V_{CM}$ . Valid for common-mode ranges where the signal does not exceed the operating range. Specification is worst case (slowest to fastest) over the specified range.

- Note 23: Input to comparator is 40MHz at 0 to 1V, 50% duty cycle, 1ns rise time.

- Note 24: This specification is implicitly tested, by meeting the high-impedance leakage specification.

- **Note 25:** Resistance measurements are made using small-signal voltage changes in the loading instrument. Absolute value of the difference in measured resistance over the specified range, tested separately for each current polarity.

- Note 26: Ripple in the DUT\_ signal after one round-trip delay. Stimulus is 0 to 3V, 2.5V/ns square wave from far end of 3ns transmission line with  $R_S = 25\Omega$ , clamps set to 0 and 3V.

- Note 27: Any deviation from 2.5V affects offset and gain of all levels.

- **Note 28:** Serial port timing specifications are measured at a logic supply voltage (V<sub>DD</sub>) of +3.3V, ensuring operation of the serial port at rated speed for V<sub>DD</sub> from +3.3V to +5.5V.

- **Note 29:** The maximum usable output operating voltage is limited to -1.5V to +6.5V. Externally forced voltages may exceed this range without damage to the device, provided that they are limited per the *Absolute Maximum Ratings*. External clamps must be provided to limit voltages in this range, or damage to the device is likely.

- Note 30: Total for dual device.  $R_L \ge 10M\Omega$ . Worst case of the following conditions: driver enabled, LLEAK = 0; driver disabled, LLEAK = 0; driver disabled, RCV\_ = 1; driver disabled, LLEAK = 1.

- **Note 31:** Excludes dissipation of comparator output supply. A typical output configuration and V+ = 1.8V adds 30mW (typ) per channel to device power.

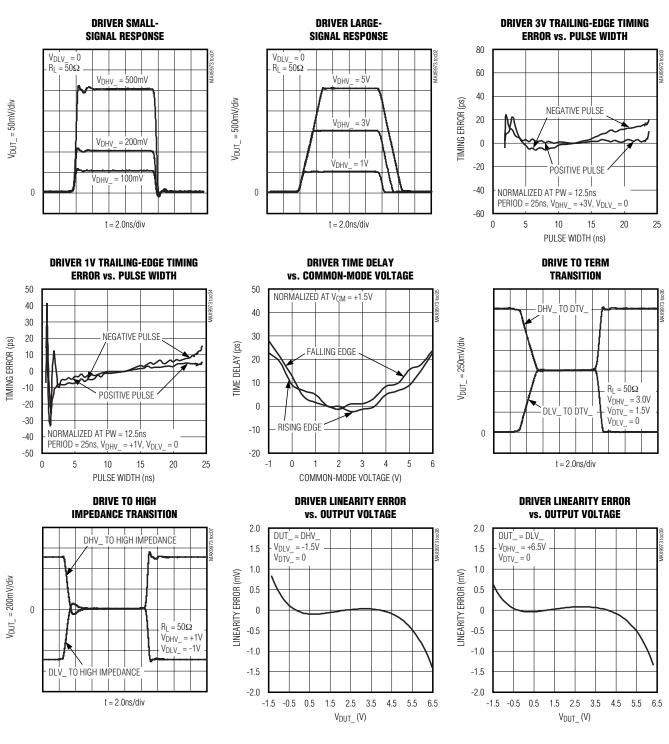

#### **Typical Operating Characteristics**

M/IXI/M

$(T_J = +70^{\circ}C, unless otherwise noted.)$

MAX9973/MAX9974

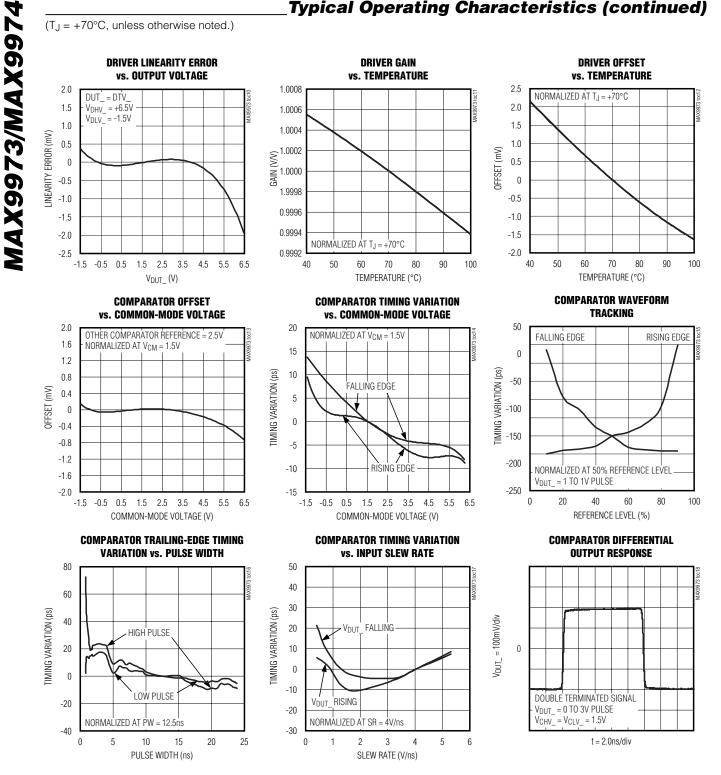

#### **Typical Operating Characteristics (continued)**

M/IXI/M

**Typical Operating Characteristics (continued)**

M/IXI/M

$(T_{1} = +70^{\circ}C, unless otherwise noted.)$

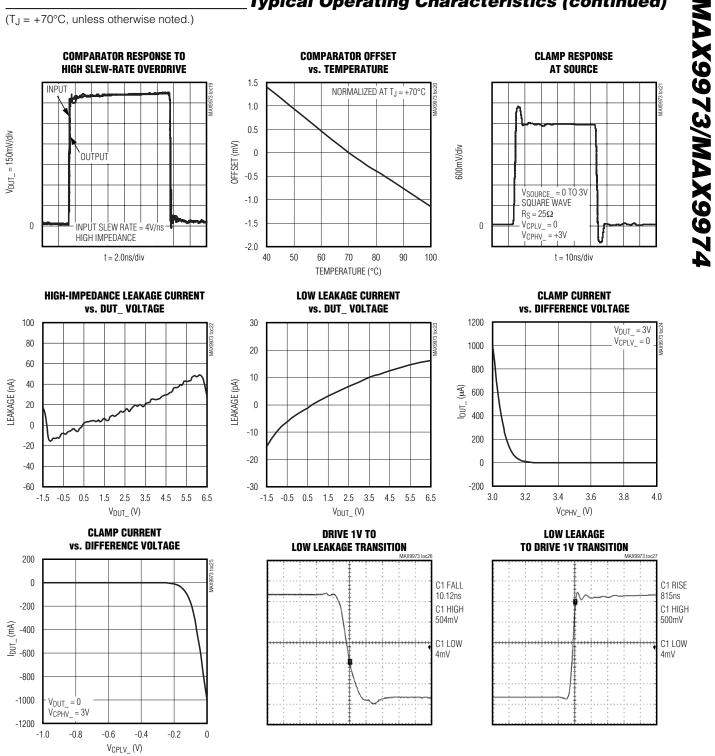

#### Typical Operating Characteristics (continued)

$(T_J = +70^{\circ}C, unless otherwise noted.)$

MAX9973/MAX9974

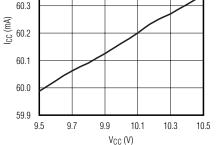

# POSITIVE SUPPLY CURRENT vs. POSITIVE SUPPLY VOLTAGE 60.5 VDHV\_= +3.0V, VDLV\_= 0, VDTV\_= +1.5V, VCPHV\_= +7.2V, VCPLV\_= -2.2V, HIGH IMPEDANCE, VEE = -5.25V 60.4 HIGH IMPEDANCE, VEE = -5.25V

NEGATIVE SUPPLY CURRENT vs. TEMPERATURE

**NEGATIVE SUPPLY CURRENT**

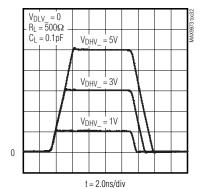

DRIVER LARGE-SIGNAL RESPONSE INTO 500Ω

#### POSITIVE SUPPLY CURRENT vs. TEMPERATURE

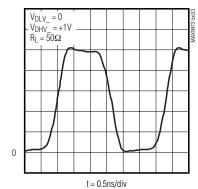

DRIVER 1V 600Mbps SIGNAL RESPONSE

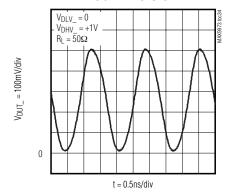

DRIVER 1V 1200Mbps SIGNAL RESPONSE

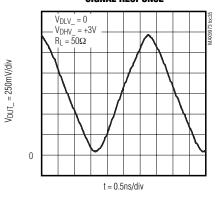

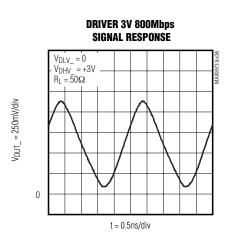

DRIVER 3V 600Mbps SIGNAL RESPONSE

$V_{DUT} = 100 mV/div$

#### Typical Operating Characteristics (continued)

$(T_J = +70^{\circ}C, \text{ unless otherwise noted.})$

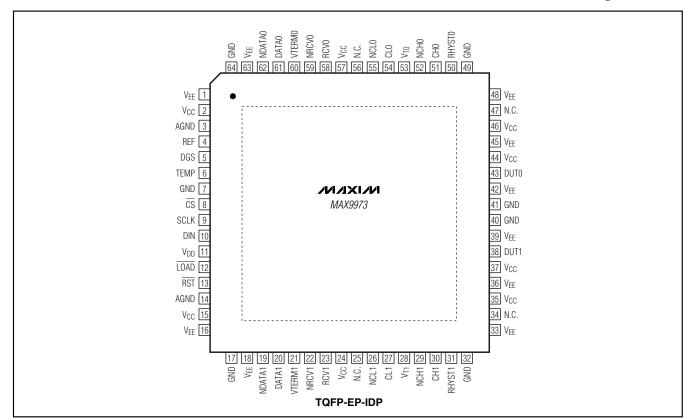

#### **Pin Description**

| PIN (MAX9973)                            | NAME            | F                                                                                                                                                  | UNCTION                                                                              |  |

|------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| 1, 16, 18, 33, 36,<br>39, 42, 45, 48, 63 | VEE             | Negative Power-Supply Input                                                                                                                        |                                                                                      |  |

| 2, 15, 24, 35, 37,<br>44, 46, 57         | V <sub>CC</sub> | Positive Power-Supply Input                                                                                                                        |                                                                                      |  |

| 3, 14                                    | AGND            | Analog Ground Connection                                                                                                                           |                                                                                      |  |

| 4                                        | REF             | DAC Reference Input. Set to 2.5V with r                                                                                                            | espect to DGS.                                                                       |  |

| 5                                        | DGS             | DUT Ground Sense. DGS is the ground ground of the device-under-test.                                                                               | reference for the DACs. Connect DGS to                                               |  |

| 6                                        | TEMP            | Temperature Monitor Output                                                                                                                         |                                                                                      |  |

| 7, 17, 32, 40, 41,<br>49, 64             | GND             | Ground                                                                                                                                             |                                                                                      |  |

| 8                                        | CS              | Chip-Select Input. Serial port activation                                                                                                          | input.                                                                               |  |

| 9                                        | SCLK            | Serial-Clock Input. Clock for serial port.                                                                                                         |                                                                                      |  |

| 10                                       | DIN             | Data Input. Serial port data input.                                                                                                                |                                                                                      |  |

| 11                                       | V <sub>DD</sub> | Digital Interface Power-Supply Input                                                                                                               |                                                                                      |  |

| 12                                       | LOAD            | Load Input. Latches serial register data                                                                                                           | into DACs.                                                                           |  |

| 13                                       | RST             | Reset Input. Asynchronous reset input f                                                                                                            | or the serial register.                                                              |  |

| 19                                       | NDATA1          | Channel 1 Multiplexer Control Input N                                                                                                              | Differential controls DATA1 and NDATA1 select driver 1's input from DHV1 or DLV1.    |  |

| 20                                       | DATA1           | Channel 1 Multiplexer Control Input                                                                                                                | Drive DATA1 above NDATA1 to select DHV1.<br>Drive NDATA1 above DATA1 to select DLV1. |  |

| 21                                       | VTERM1          | Channel 1 RCV/NRCV and DATA/NDATA Termination Voltage Input. Termination voltage input for the RCV1, NRCV1, DATA1, and NDATA1 differential inputs. |                                                                                      |  |

MAX9973/MAX9974

#### Pin Description (continued)

| PIN (MAX9973)  | NAME            |                                                                        | UNCTION                                                                                                                                  |  |  |  |  |

|----------------|-----------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 22             | NRCV1           | Channel 1 Multiplexer Control Input N                                  | Differential controls RCV1 and NRCV1 place<br>channel 1 in receive mode. Drive RCV1 above<br>NRCV1 to place channel 1 into receive mode. |  |  |  |  |

| 23             | RCV1            | Channel 1 Multiplexer Control Input                                    | Drive NRCV1 above RCV1 to place channel 1 into drive mode.                                                                               |  |  |  |  |

| 25, 34, 47, 56 | N.C.            | No Connection. Make no connection.                                     |                                                                                                                                          |  |  |  |  |

| 26             | NCL1            | Channel 1 Low Comparator Output N                                      | Differential outputs of channel 1 low                                                                                                    |  |  |  |  |

| 27             | CL1             | Channel 1 Low Comparator Output                                        | comparator.                                                                                                                              |  |  |  |  |

| 28             | V <sub>T1</sub> | Comparator Termination Voltage Input. pullup resistors for channel 1.  | Termination voltage for the comparator output                                                                                            |  |  |  |  |

| 29             | NCH1            | Channel 1 High Comparator Output N                                     | Differential outputs of channel 1 high                                                                                                   |  |  |  |  |

| 30             | CH1             | Channel 1 High Comparator Output                                       | comparator.                                                                                                                              |  |  |  |  |

| 31             | RHYST1          | Comparator Hysteresis Programming Ir                                   | nput for Channel 1                                                                                                                       |  |  |  |  |

| 38             | DUT1            | Channel 1 Device-Under-Test Input/Ou clamp, and load.                  | tput. Combined I/O for driver, comparator,                                                                                               |  |  |  |  |

| 43             | DUTO            | Channel 0 Device-Under-Test Input/Ou<br>clamp, and load.               | Channel 0 Device-Under-Test Input/Output. Combined I/O for driver, comparator, clamp, and load.                                          |  |  |  |  |

| 50             | RHYST0          | Comparator Hysteresis Programming Ir                                   | nput for Channel 0                                                                                                                       |  |  |  |  |

| 51             | CH0             | Channel 0 High Comparator Output                                       | Differential outputs of channel 0 high                                                                                                   |  |  |  |  |

| 52             | NCH0            | Channel 0 High Comparator Output N                                     | comparator.                                                                                                                              |  |  |  |  |

| 53             | V <sub>TO</sub> | Comparator Termination Voltage Input. pullup resistors for channel 0.  | Termination voltage for the comparator output                                                                                            |  |  |  |  |

| 54             | CLO             | Channel 0 Low Comparator Output                                        | Differential outputs of channel 0 low                                                                                                    |  |  |  |  |

| 55             | NCL0            | Channel 0 Low Comparator Output N                                      | comparator.                                                                                                                              |  |  |  |  |

| 58             | RCV0            | Channel 0 Multiplexer Control Input                                    | Differential controls RCV0 and NRCV0 place<br>channel 0 in receive mode. Drive RCV0 above                                                |  |  |  |  |

| 59             | NRCV0           | Channel 0 Multiplexer Control Input N                                  | NRCV0 to place channel 0 into receive mode.<br>Drive NRCV0 above RCV0 to place channel 0<br>into drive mode.                             |  |  |  |  |

| 60             | VTERMO          | Channel 0 RCV/NRCV and DATA/NDAT voltage input for the RCV0, NRCV0, DA | A Termination Voltage Input. Termination TA0, and NDATA0 differential inputs.                                                            |  |  |  |  |

| 61             | DATA0           | Channel 0 Multiplexer Control Input                                    | Differential controls DATA0 and NDATA0 select driver 0's input from DHV0 or DLV0.                                                        |  |  |  |  |

| 62             | NDATA0          | Channel 0 Multiplexer Control Input N                                  | Drive DATA0 above NDATA0 to select DHV0.<br>Drive NDATA0 above DATA0 to select DLV0.                                                     |  |  |  |  |

| _              | EP              | Exposed Heat Removal Paddle. The pa<br>no electrical connection to EP. | ddle is electrically isolated from the die. Make                                                                                         |  |  |  |  |

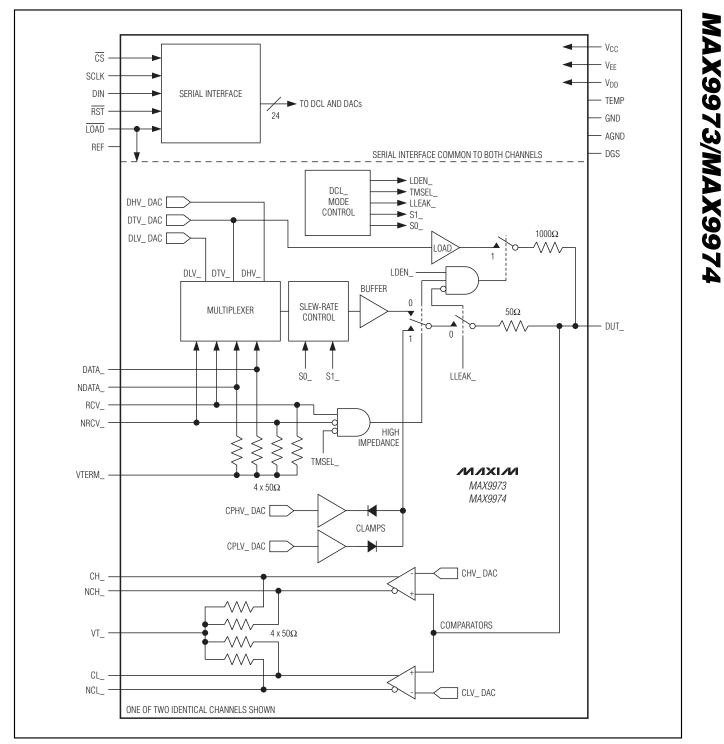

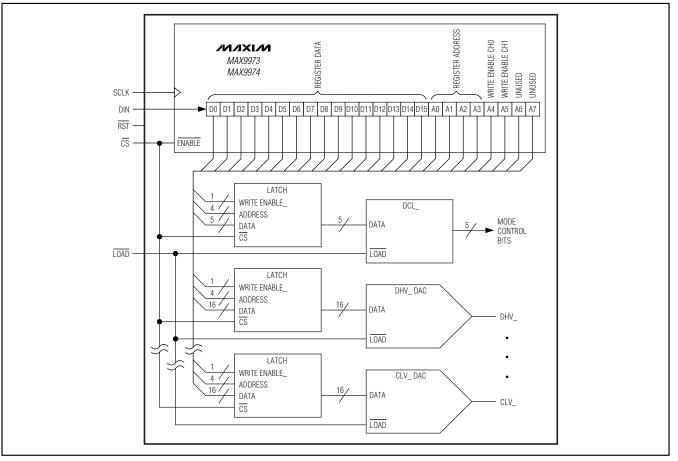

Figure 1. Functional Diagram

#### **Detailed Description**

The MAX9973/MAX9974 are fully integrated, high-performance, dual-channel pin electronics driver/comparator/load (DCL) with built-in level-setting DACs. Each channel includes a three-level pin driver with three levelsetting DACs, a window comparator with two level-setting DACs, two dynamic clamps with two level-setting DACs, and a 1k $\Omega$  load driven by the driver's DTV\_DAC. Figure 1 shows a functional diagram of the MAX9973/MAX9974.

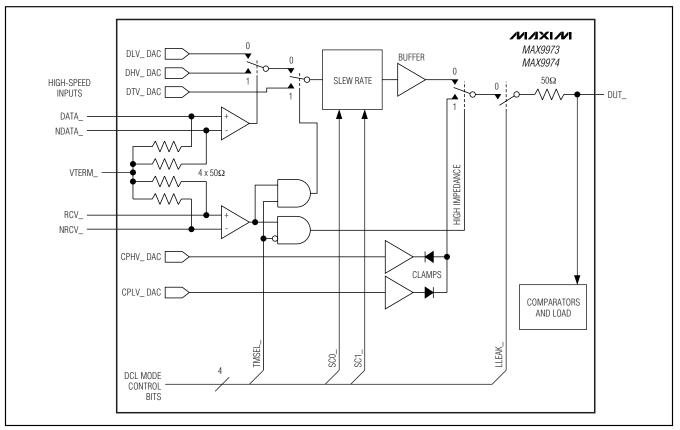

The three-level pin driver features a wide -1.5V to +6.5V voltage range and includes high-impedance and active-termination (3rd-level drive) modes. High-speed differential multiplexer control inputs DATA and RCV with internal termination resistors switch the driver between the three input levels. Figure 2 shows a block diagram of the simplified driver channel.