### Advance Information

MC13181/D Rev. 0, 08/2002

Wireless Power Management Integrated Circuit

# MC13181

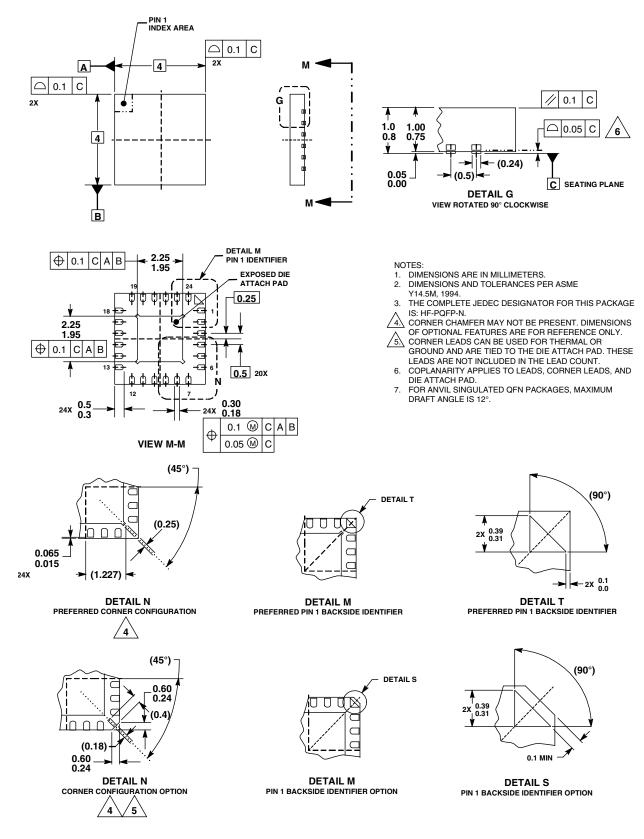

Package Information

Plastic Package Case 1307 (QFN-24)

### **Ordering Information**

| Device    | Marking | Package |  |

|-----------|---------|---------|--|

| MC13181R2 | 13180   | QFN-24  |  |

The MC13181 Wireless Power Management Integrated Circuit (PMIC) is a monolithic IC designed for hand-held electronics products in conjunction with the Motorola Bluetooth™ chipset (the MC13180 Bluetooth Radio and MC71000 Bluetooth Protocol Controller) or stand-alone in other products. The MC13181 is ideal for devices operating from a 3.6 V single-cell Lithium-ion battery or other energy systems in the 2.85 to 6.5 V range. The IC features three independently enabled Low Drop Out (LDO) Linear Voltage Regulators for powering baseband, audio, RF/IF, and interface circuitry. A comparator with logic-enabled hysteresis and one scaled input is provided for use as a low-battery detector to protect against destructive battery discharge; it can alternately be used for general system interfacing. A supervisory circuit is integrated to provide a reset signal to the Protocol Controller indicating valid supply. An over-temperature shutdown function is integrated to protect against excessive power dissipation. A Shutdown input line is provided to allow for disabling of all active circuitry to minimize battery loading and to provide single line master disable. Logic inputs accept V<sub>ih</sub> levels from 1.5 V to V<sub>CC</sub>.

#### **Typical Applications**

- Add-On Bluetooth Adaptor Cards for Cellular Phones

- Cellular Phones

- USB Dongle

- GPS or PDA

- Cordless Headsets

- Other portable devices requiring multiple independent regulators in one package

This document contains information on a pre-production product. Specifications and Pre-production information herein are subject to change without notice. © Motorola, Inc., 2002. All rights reserved.

### **Features**

- Low-Battery Detector

- Three LDO Voltage Regulators:

2.65 V, 65 mA for RF/IF

1.85 V, 30 mA for Baseband

3.0/3.3 V, 60 mA for USB, Audio CODEC, or other circuitry Integrated Pass Device

Independent Enable Lines

Optimized for Low-Cost Bypass Capacitors

- Microprocessor Supervisor Circuit

- General Purpose Inverter, OR Gate and Comparator

- Maximum V<sub>CC</sub> Rated up to 7.0 V (6.5 V recommended)

- Voltage-Robust, Level Shifted Logic Inputs to V<sub>CC</sub> (6.5 V)

- Seamless Integration with Motorola's Bluetooth Chipset

- Thermal Shutdown

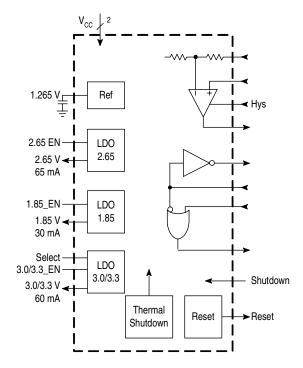

Figure 1. Simplified Block Diagram

# 1 Electrical Specifications

**Table 1. Maximum Ratings**

| Ratings                                 | Symbol              | Value                        | Unit |

|-----------------------------------------|---------------------|------------------------------|------|

| Power Supply Input Voltage              | V <sub>I</sub>      | 0 to 7.0                     | V    |

| Voltage Input                           | V <sub>in</sub>     | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Output Voltage                          | V <sub>out</sub>    | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Output Short Circuit Duration           | -                   | Infinite                     | -    |

| Thermal Resistance, Junction to Ambient | $R_{	hetaja}$       | 115                          | °C/W |

| Storage Temperature Range               | T <sub>stg</sub>    | -40 to 150                   | °C   |

| Operating Junction Temperature          | T <sub>J</sub>      | 125                          | °C   |

| Lead Soldering Temperature @ 260°C      | T <sub>solder</sub> | 10                           | sec  |

NOTE: Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the limits in the Electrical Characteristics tables or

Contact Description section.

## Table 2. Maximum Package Power Dissipation

The power dissipation level at which the junction temperature reaches its maximum operating value, i.e., 125°C.

| Characteristic                   | Symbol | Min | Тур | Max  | Unit |

|----------------------------------|--------|-----|-----|------|------|

| Power Dissipation, in air        | Pd     | -   | -   | 345  | mW   |

| Power Dissipation, 4-layer board | Pd     | -   | -   | 1000 | mW   |

**Table 3. Recommended Operating Conditions**

| Characteristic    | Symbol          | Min  | Тур | Max | Unit |

|-------------------|-----------------|------|-----|-----|------|

| Supply Voltage    | V <sub>CC</sub> | 2.85 | -   | 6.5 | V    |

| Temperature Range | T <sub>A</sub>  | -40  | -   | 85  | °C   |

# **Table 4. Electrical Characteristics**

$(V_{CC} = 3.6 \text{ V}, C_{in} = 1.0 \text{ } \mu\text{F}, C_{out} = 1.0 \text{ } \mu\text{F}, T_{A} = 25^{\circ}\text{C}$  for typical values, unless otherwise noted.)

| Characteristic                                                                 | Symbol              | Min   | Тур  | Max   | Unit |  |

|--------------------------------------------------------------------------------|---------------------|-------|------|-------|------|--|

| LDO_1.85                                                                       |                     |       |      |       |      |  |

| Output Voltage in 1.85 V Mode                                                  | V <sub>out</sub>    | 1.813 | 1.85 | 1.887 | V    |  |

| Line Regulation (V <sub>CC2</sub> = 2.85 V to 6.5 V, I <sub>out</sub> = 15 mA) | REG <sub>line</sub> | -     | 1.0  | 10    | mV   |  |

| Load Regulation (I <sub>out</sub> = 10 μA to 30 mA)                            | REG <sub>load</sub> | -     | 15   | 45    | mV   |  |

# **Electrical Specifications**

# **Table 4. Electrical Characteristics (Continued)**

$(V_{CC} = 3.6 \text{ V}, C_{in} = 1.0 \text{ } \mu\text{F}, C_{out} = 1.0 \text{ } \mu\text{F}, T_A = 25^{\circ}\text{C} \text{ for typical values, unless otherwise noted.})$

| Characteristic                                                                           | Symbol           | Min | Тур | Max | Unit          |

|------------------------------------------------------------------------------------------|------------------|-----|-----|-----|---------------|

| Ripple Rejection (Ripple 0.5 $V_{pp}$ , $V_{CC}$ = 2.95 $V$ , $I_0$ = 15 mA) f = 1.0 kHz | PSRR             | 40  | -   | -   | dB            |

| Output Noise Voltage @ I <sub>o</sub> = 20 mA (f = 10 kHz to 100 kHz)                    | V <sub>n</sub>   | -   | 30  | -   | $\mu V_{rms}$ |

| Short Circuit Current Limit (V <sub>out</sub> = 0 V)                                     | I <sub>lim</sub> | -   | 90  | -   | mA            |

| Supply Current in ON mode (I <sub>out</sub> = 0 mA)                                      | I <sub>SS</sub>  | -   | 30  | 40  | μΑ            |

| Output Capacitor                                                                         | C <sub>out</sub> | 1   | -   | -   | μF            |

| ESR of Output Capacitor                                                                  | ESR              | -   | 5.0 | -   | Ω             |

| Output Voltage Transient Response (10% to 100% of I <sub>max</sub> )                     |                  | -   | 1.0 | -   | %             |

| Output Turn On Time from Enable to 90% of final value                                    | T <sub>on</sub>  | -   | 20  | 100 | μs            |

| Output Voltage Temperature Coefficient                                                   | T <sub>C</sub>   | -   | 100 | -   | ppm /<br>°C   |

# LDO\_2.65

| Output Voltage                                                                                                    | V                                 | 2.60        | 2.65           | 2.70        | V             |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|----------------|-------------|---------------|

| Dropout Voltage                                                                                                   | V <sub>CC</sub> -V <sub>out</sub> | -           | 1.0            | -           | mV/<br>mA     |

| Line Regulation ( $V_{CC1}$ = 2.85 V to 6.5 V, $I_{out}$ = 32.5 mA)                                               | REG <sub>line</sub>               | -           | 3.0            | 10          | mV            |

| Load Regulation (I <sub>out</sub> = 10 μA to 65 mA)                                                               | REG <sub>load</sub>               | -           | 15             | 45          | mV            |

| Ripple Rejection, ( $V_{CC}$ Ripple = 0.5 $V_{pp}$ , $I_{o}$ = 32.5 mA)<br>f = 1.0 kHz<br>f = 10 kHz<br>f = 1 MHz | PSRR                              | -<br>-<br>- | 60<br>41<br>34 | -<br>-<br>- | dB            |

| Output Noise Voltage @ I <sub>o</sub> = 50 mA (f = 10 kHz to 100 kHz)                                             | V <sub>n</sub>                    | -           | 30             | -           | $\mu V_{rms}$ |

| Short Circuit Current Limit (V <sub>out</sub> = 0 V)                                                              | I <sub>lim</sub>                  | -           | 200            | -           | mA            |

| Supply Current in ON mode (I <sub>out</sub> = 0 mA)                                                               | I <sub>SS</sub>                   | -           | 100            | 125         | μА            |

| Output Capacitor                                                                                                  | C <sub>out</sub>                  | 1.0         | -              | -           | μF            |

| ESR of Output Capacitor                                                                                           | ESR                               | -           | 4.0            | -           | W             |

| Output Voltage Transient Response (10% to 100% of I <sub>max</sub> )                                              |                                   | -           | 1.0            | -           | %             |

| Output Turn On Time from Enable to 90% of final value                                                             | T <sub>on</sub>                   | -           | 20             | 100         | μs            |

## **Table 4. Electrical Characteristics (Continued)**

$(V_{CC} = 3.6 \text{ V}, C_{in} = 1.0 \mu\text{F}, C_{out} = 1.0 \mu\text{F}, T_{\Delta} = 25^{\circ}\text{C}$  for typical values, unless otherwise noted.)

| Characteristic                                                                                     | Symbol                            | Min      | Тур                  | Max      | Unit              |

|----------------------------------------------------------------------------------------------------|-----------------------------------|----------|----------------------|----------|-------------------|

| Output Voltage Temperature Coefficient                                                             | T <sub>C</sub>                    | -        | 100                  | -        | ppm /<br>°C       |

| LDO_3.0/3.3                                                                                        |                                   |          | l                    |          |                   |

| Output Voltage in 3.0 V Mode Select High                                                           | V <sub>out</sub>                  | 3.0      | 3.06                 | 3.12     | V                 |

| Output Voltage in 3.3 V Mode Select Low                                                            | V <sub>out</sub>                  | 3.234    | 3.3                  | 3.366    | V                 |

| Dropout Voltage                                                                                    | V <sub>CC</sub> -V <sub>out</sub> | -        | 1.0                  | -        | mV/<br>mA         |

| Line Regulation (V <sub>CC</sub> = 3.5 V to 6.5 V, I <sub>out</sub> = 30 mA)                       | REG <sub>line</sub>               | -        | 2.5                  | 10       | mV                |

| Load Regulation (I <sub>out</sub> = 10 μA to 60 mA)                                                | REG <sub>load</sub>               | -        | 8.0                  | 45       | mV                |

| Ripple Rejection, (Ripple 0.5 $V_{pp}$ , $V_{CC} = V_{out} + 0.6 V$ , $I_{o} = 30$ mA) f = 1.0 kHz | PSRR                              | 40       | -                    | -        | dB                |

| Output Noise Voltage @ $I_0 = 50$ mA (f = 10 kHz to 100 kHz)                                       | V <sub>n</sub>                    | -        | 30                   | -        | μV <sub>rms</sub> |

| Short Circuit Current Limit (V <sub>out</sub> = 0 V)                                               | I <sub>lim</sub>                  | -        | 200                  | -        | mA                |

| Supply Current in ON mode ( $V_{CC} = V_{out} + 0.6 V$ , $I_{out} = 0 \text{ mA}$ )                | Iss                               | -        | 10                   | 65       | μΑ                |

| Output Capacitor                                                                                   | C <sub>out</sub>                  | 1.0      | -                    | -        | μF                |

| ESR of Output Capacitor                                                                            | ESR                               | -        | 4.0                  | -        | W                 |

| Output Voltage Transient Response (10% to 100% of I <sub>max</sub> )                               |                                   | -        | 1.0                  | -        | %                 |

| Output Turn On Time from Enable to 90% of final value                                              | T <sub>on</sub>                   | -        | 50                   | 100      | μs                |

| Output Voltage Temperature Coefficient                                                             | T <sub>C</sub>                    | -        | 100                  | -        | ppm /<br>°C       |

| RESETB Circuit with Programmable Delay                                                             |                                   |          |                      |          | I                 |

| ResetB Threshold                                                                                   | $V_{TH}$                          | 1.65     | 1.70                 | 1.75     | V                 |

| ResetB Active Timeout period with Delay Cap = 5.6 nF with Delay Cap = 68 nF                        | T <sub>reset</sub>                | 8.0<br>- | 14<br>170            | -<br>300 | ms                |

| Output Voltage Low                                                                                 | V <sub>ol</sub>                   | 0        | -                    | 0.1      | V                 |

| Output Voltage High                                                                                | V <sub>oh</sub>                   | -        | V <sub>LDO_1</sub> . | -        | V                 |

|                                                                                                    |                                   |          |                      |          | 1                 |

Output Current RESETB (source or sink)

$|I_0|$

1.0

mΑ

# Table 4. Electrical Characteristics (Continued)

$(V_{CC} = 3.6 \text{ V}, C_{in} = 1.0 \text{ } \mu\text{F}, C_{out} = 1.0 \text{ } \mu\text{F}, T_A = 25^{\circ}\text{C} \text{ for typical values, unless otherwise noted.})$

| Characteristic                                                               | Symbol                | Min   | Тур                   | Max                   | Unit  |  |  |  |

|------------------------------------------------------------------------------|-----------------------|-------|-----------------------|-----------------------|-------|--|--|--|

| Comparator with Programmable Hysteresis                                      |                       |       |                       |                       |       |  |  |  |

| Input Offset Voltage                                                         | V <sub>offset</sub>   | -5.0  | -                     | 5.0                   | mV    |  |  |  |

| Input Impedance (V <sub>in</sub> + and V <sub>in</sub> -)                    | R <sub>in</sub>       | -     | 1600                  |                       | kΩ    |  |  |  |

| Input Voltage Range<br>V <sub>in</sub> +                                     | V <sub>in+</sub>      | 1.0   | -                     | V <sub>CC2</sub> - 1V | V     |  |  |  |

| Input Voltage Range V <sub>in</sub> - (scaling factor of approximately 0.44) | V <sub>in-</sub>      | 1.0   | -                     | V <sub>CC2</sub>      | V     |  |  |  |

| Output Voltage Low                                                           | V <sub>ol</sub>       | 0     | -                     | 0.1                   | V     |  |  |  |

| Output Voltage High                                                          | V <sub>oh</sub>       | -     | V <sub>LDO_1.85</sub> | -                     | ٧     |  |  |  |

| Slew Rate C <sub>L</sub> = 50 pF Positive Slope Negative Slope               | S <sub>R</sub>        | -     | 100<br>200            | -<br>-                | V/µs  |  |  |  |

| Output Current DETECT (source or sink)                                       | I <sub>o</sub>        | 1.0   | -                     | -                     | mA    |  |  |  |

| Hysteresis Voltage Pin HYS SELECT Low (hysteresis enabled)                   |                       | -     | 30                    | -                     | mV    |  |  |  |

| Voltage Reference (C <sub>out</sub> = 470 nF Ceramic)                        | <b>'</b>              |       |                       |                       |       |  |  |  |

| V <sub>CC</sub> Operating Range                                              | V <sub>CC1</sub>      | 2.2   | -                     | 6.5                   | ٧     |  |  |  |

| Output Voltage                                                               | V <sub>ref</sub>      | 1.250 | 1.265                 | 1.278                 | ٧     |  |  |  |

| Temperature Coefficient                                                      | TC <sub>Vref</sub>    | -     | 0.022                 | -                     | mV/°C |  |  |  |

| Line Regulation                                                              | V <sub>REF_LINE</sub> | -     | 0.08                  | -                     | mV/V  |  |  |  |

| Output Capacitor                                                             |                       | -     | 470                   | -                     | nF    |  |  |  |

| Startup Time                                                                 | T <sub>startup</sub>  | -     | 1.0                   | -                     | ms    |  |  |  |

| OR Gate                                                                      |                       |       |                       |                       |       |  |  |  |

| V <sub>CC</sub> Operating Range                                              | V <sub>CC2</sub>      | 2.2   | -                     | 6.5                   | ٧     |  |  |  |

| Output Voltage Low                                                           | V <sub>ol</sub>       | -     | -                     | 0.1                   | ٧     |  |  |  |

| Output Voltage High                                                          | V <sub>oh</sub>       | 1.55  | -                     | V <sub>CC2</sub>      | V     |  |  |  |

| Inverter Gate                                                                | 1                     |       | I                     | ı                     |       |  |  |  |

| Hysteresis Voltage                                                           |                       | -     | 50                    | -                     | mV    |  |  |  |

| Output Voltage Low                                                           | V <sub>ol</sub>       | -     | -                     | 0.1                   | V     |  |  |  |

# Table 4. Electrical Characteristics (Continued)

$(V_{CC} = 3.6 \text{ V}, C_{in} = 1.0 \text{ } \mu\text{F}, C_{out} = 1.0 \text{ } \mu\text{F}, T_A = 25^{\circ}\text{C} \text{ for typical values, unless otherwise noted.})$

| ( OO                                                                    | 71                 | ,   |                      | ,                |      |

|-------------------------------------------------------------------------|--------------------|-----|----------------------|------------------|------|

| Characteristic                                                          | Symbol             | Min | Тур                  | Max              | Unit |

| Output Voltage High                                                     | V <sub>oh</sub>    | -   | V <sub>LDO_1</sub> . | -                | V    |

| Common                                                                  |                    |     |                      |                  |      |

| Quiescent Current V <sub>CC1</sub> (all LDO enables low)                | I <sub>cq1</sub>   | -   | 30                   | 42               | μΑ   |

| Quiescent Current V <sub>CC2</sub> (all LDO enables low)                | I <sub>cq2</sub>   | -   | 7.0                  | 13               | μΑ   |

| Quiescent Current V <sub>CC</sub> (SHUTDOWN_B low)                      | I <sub>cq</sub> sd | -   | 1.8                  | -                | μΑ   |

| Input Voltage Low (enable, shutdown, Q1_B, Q2, hys sel, 3.0/3.3 select) | V <sub>il</sub>    | 0   | -                    | 0.15             | V    |

| Input Voltage High (enable, shutdown, Q1_B, Q2, hys                     | V <sub>ih</sub>    | 1.5 | -                    | V <sub>CC2</sub> | V    |

$R_{pd}$

$V_{CC2}$ - $V_{CC1}$

$V_{\text{CC1}}\text{-}V_{\text{CC2}}$

1.0

0

$M\Omega$

٧

٧

0.3

$V_{CC1}$

sel, 3.0/3.3 select)

Pull Down Resistor (enable, Q2, select)

$V_{CC}$  Differential ( $V_{CC2} > V_{CC1}$ )

$V_{CC}$  Differential ( $V_{CC1} > V_{CC2}$ )

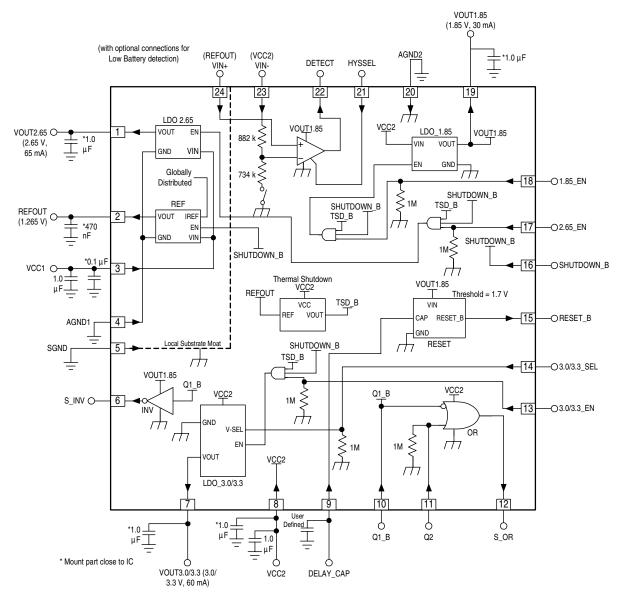

Figure 2. Simplified Functional Diagram

# 2 Pin Function Descriptions

**Table 5. Pin Function Description**

| Pin | Symbol/<br>Type | Description                                                                     | Equivalent Internal Circuit                   | Notes                                                                       |

|-----|-----------------|---------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|

| 1   | VOUT2.65        | VOUT2.65 Regulator<br>Output, LDO_2.65,<br>2.65 V, 65 mA Output                 | V <sub>cc1</sub> V <sub>ref</sub> 162 k 152 k | Bypass with low ESR 1.0 μF tantalum capacitor [Note 1]                      |

| 2   | REFOUT          | REFOUT,1.265 V<br>Reference Voltage<br>Output,                                  | V <sub>CC1</sub> 2.0 k Band Gap               | Bypass with<br>low ESR<br>470 nF<br>[Note 1]                                |

| 3   | VCC1            | VCC1, Positive Supply, Power Supply Input for Reference Generation and LDO_2.65 | to V <sub>CC</sub> 3* Also pin 8 C bypass (2) | Bypass with<br>a 0.1 μF<br>close to the<br>part and a<br>1.0 μF low<br>ESR. |

| 4   | AGND1           | AGND1 Ground, Analog<br>Ground for Reference<br>Generation and<br>LDO_2.65      | A ground 1 ESD                                | Tie to<br>ground                                                            |

| 5   | SGND            | SGND Ground,<br>Substrate for LDO_2.65<br>and Reference<br>Generator            | 5 S ground ESD                                | Tie to<br>ground                                                            |

| 6   | S_INV           | S_INV, Inverter Output                                                          | ESD _ also pins 15 & 22                       | referenced<br>to V <sub>LDO_1.85</sub>                                      |

NOTES: 1. All capacitors are assumed to be low ESR tantalum. De-rating factor on capacitance value is assumed to be -20% to 10% over all cases of tolerance and temperature.

<sup>2.</sup> Contact assignments are subject to change.

Table 5. Pin Function Description (Continued)

| Pin | Symbol/<br>Type | Description                                                                     | Equivalent Internal Circuit                           | Notes                                                        |

|-----|-----------------|---------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|

| 7   | VOUT3.0/3.3     | VOUT3.0/3.3 Regulator,<br>LDO_3.0/3.3, 60 mA<br>Output                          | V <sub>cc2</sub> 7  23 k  160 k  115 k                | Bypass with low ESR 1.0 µF tantalum capacitor [Note 1]       |

| 8   | VCC2            | VCC2, Positive Supply,<br>Power Supply Input for<br>non-V <sub>CC1</sub> blocks | same as pin 3                                         | Bypass with a 0.1 µF close to the part and a 1.0 µF low ESR. |

| 9   | DELAY_CAP       | DELAY_CAP, Reset<br>Delay Cap Input                                             | C <sub>dolay</sub> = 9 500 nA                         |                                                              |

| 10  | Q1_B            | Q1_B, Input to Inverter<br>and Complementary<br>Input to OR Gate                | V <sub>CC2</sub> ▼ 500 nA  ESD * also pins 16 & 21    | can tolerate<br>high to V <sub>CC</sub>                      |

| 11  | Q2              | Q2, Input to OR Input                                                           | V <sub>CC2</sub> ▼ 500 nA  ■ 11* ■ 20* ■ 314, 17 & 18 | can tolerate<br>high to V <sub>CC</sub>                      |

NOTES: 1. All capacitors are assumed to be low ESR tantalum. De-rating factor on capacitance value is assumed to be -20% to 10% over all cases of tolerance and temperature.

Contact assignments are subject to change.

**Table 5. Pin Function Description (Continued)**

| Pin | Symbol/<br>Type | Description                                                              | Equivalent Internal Circuit                         | Notes                                                  |

|-----|-----------------|--------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|

| 12  | S_OR            | S_OR, OR Output                                                          |                                                     | referenced to V <sub>CC2</sub>                         |

| 13  | 3.0/3.3_EN      | <b>3.0/3.3_EN</b> , LDO_3.0/<br>3.3 Enable                               | same as pin 11                                      | high =<br>enable                                       |

| 14  | 3.0/3.3_SEL     | 3.0/3.3_SEL, Input logic<br>control for 3.0 or 3.3 V<br>from LDO_3.0/3.3 | same as pin 11                                      | high = 3.0 V,<br>low =<br>3.3 V                        |

| 15  | RESET_B         | RESET_B, Reset Push-<br>Pull Output                                      | same as pin 6                                       | referenced<br>to V <sub>LDO_1.85</sub>                 |

| 16  | SHUTDOWN<br>_B  | SHUTDOWN_B, Single<br>Pin Master Disable                                 | same as pin 10                                      | Low = IC<br>Shutdown                                   |

| 17  | 2.65_EN         | <b>2.65_EN</b> , LDO_2.65<br>Enable                                      | same as pin 11                                      | high =<br>enable                                       |

| 18  | 1.85_EN         | <b>1.85_EN</b> , LDO_1.85<br>Enable                                      | same as pin 11                                      | high =<br>enable                                       |

| 19  | VOUT1.85        | VOUT1.85 Regulator,<br>LDO_1.85, 1.85 V, 30<br>mA Output,                | V <sub>CC2</sub> V <sub>ret</sub> 19 90 k ESD 200 k | Bypass with low ESR 1.0 μF tantalum capacitor [Note 1] |

| 20  | AGND2           | AGND2 Ground, Analog<br>Ground                                           | Ground                                              | Tie to<br>ground                                       |

| 21  | HYSSEL          | HYSSEL, Input logic<br>control for Comparator<br>Hysteresis              | same as pin 10                                      | Low = hysteresis enabled, High = hysteresis disabled   |

| 22  | DETECT          | <b>DETECT</b> , Comparator<br>Push-Pull Output                           | same as pin 6                                       | referenced<br>to V <sub>LDO_1.85</sub>                 |

NOTES: 1. All capacitors are assumed to be low ESR tantalum. De-rating factor on capacitance value is assumed to be -20% to 10% over all cases of tolerance and temperature.

2. Contact assignments are subject to change.

Table 5. Pin Function Description (Continued)

| Pin | Symbol/<br>Type | Description                                                      | Equivalent Internal Circuit            | Notes                                                                                                 |

|-----|-----------------|------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|

| 23  | VIN-            | VIN-, Inverting Input to<br>Comparator through<br>divider string | to V <sub>CC</sub> O 23<br>ESD en Hys. | Typically, VIN- will be connected to V <sub>CC</sub> and VIN+ to the reference to detect low battery. |

| 24  | VIN+            | VIN+, Non-inverting Input to Comparator                          |                                        |                                                                                                       |

NOTES: 1. All capacitors are assumed to be low ESR tantalum. De-rating factor on capacitance value is assumed to be -20% to 10% over all cases of tolerance and temperature.

2. Contact assignments are subject to change.

# 3 Circuit Features

# 3.1 Low Drop Out Regulators (LDO)

All three regulators are designed for use with low-value, low-cost bypass capacitors. Low ESR tantalum capacitors are recommended (high performance ceramic capacitors with extremely low ESR, « $1\Omega$ , should be avoided at regulator outputs to ensure stability, see Table 4 (Electrical Characteristics) for allowable ESR range for each regulator). The output capacitors should be  $1.0~\mu F$  minimum and should be mounted close to the IC. Better transient performance can be achieved with a larger output capacitor. In general turn-on and turn-off time will increase in proportion to the capacitor value, the regulators may not meet specified turn-on time with a larger capacitor.

| LDO         | Voltage<br>(V) | Current<br>(mA) | SEL  | <b>C<sub>out</sub></b><br>(μF) |

|-------------|----------------|-----------------|------|--------------------------------|

| LDO_1.85    | 1.85           | 30              | -    | 1.0                            |

| LDO_2.65    | 2.65           | 65              | -    | 1.0                            |

| LDO_3.0/3.3 | 3.0            | 60              | high | 1.0                            |

| LDO_3.0/3.3 | 3.3            | 60              | low  | 1.0                            |

Table 6. LDO Regulators

Additional filter capacitors should be placed across each  $V_{CC}$  input. A 0.1  $\mu$ F ceramic close to the IC and a 1.0  $\mu$ F tantalum (placement is less critical) are recommended.

All three regulators are designed for high Power Supply Rejection Ratio, low standby current, good line and load regulation, and fast turn on.

The first regulator, LDO\_1.85, supplies 1.85 V. It is capable of a nominal output current of 30 mA. This regulator is ideal for powering low-voltage digital or baseband circuitry.

The second regulator, LDO\_2.65, supplies 2.65 V at up to 65 mA. This regulator is intended to supply power for RF/IF circuitry. This regulator is optimized for slightly better close-in PSRR performance, and derives its power from the VCC1 input pin. The input to the MC13180, which this LDC supplies current, requires at least 2.55 V. The additional voltage of LDO\_2.65 allows for a series resistor, shunt capacitor filter into incorporate to further improve PSRR on that line. The resistor must be 0.220  $\Omega$  minimum, and the capacitor 1.0 to 2.2  $\mu$ F. The maximum resistor value should be chosen so that maximum current will result in a voltage drop of 0.1 V or less.

The third regulator, LDO\_3.0/3.3, can be set to either 3.0 V out to 3.3 V out through a single select line. This output can source 60 mA. This regulator can be used to supply USB power or power an audio CODEC or some other peripheral as needed. If the input voltage drops below the overhead needed for regulation, the output of this regulator will track the input down to 2.7 V.

The LDO\_1.85 and LDO\_3.0/3.3 regulators derive their power from the VCC2 input pin. This allows filtering to be tailored for the load circuitry, and to isolate the noisy digital (1.85 V) peripheral (3.0/3.3 V) from the RF (2.65 V) and reference of the IC.

Each regulator has an independent, active-high enable line. This line can accept a "high" (to turn on the regulator) input of 1.5 V up to either  $V_{CC}$ , and can be tied directly to  $V_{CC}$  if the enable function is not to be used (shutdown will still function). If a given regulator is not needed in the application, the appropriate enable input can be tied low (<1.5 V) and the output capacitor eliminated. Care should be taken if the enable pin is to be driven from a processor powered by the corresponding regulator.

# 3.2 Reference Regulator

The Reference Regulator supplies a precise 1.265 V for use by the other on-chip regulators. To maintain spectral purity on the LDO regulators, this internal reference is not intended for external loading. A pin is provided for an off-chip 0.47 µF capacitor for bypassing.

The reference regulator derives its power from the VCC1 pin. Since the reference regulator supplies reference to the other regulators, power should not be applied to  $V_{CC2}$  if  $V_{CC1}$  is unpowered.

### 3.3 Shutdown

The active-low shutdown input disables all regulators and logic. In the shutdown state, the total IC current consumption is  $2.0\,\mu A$ . Shutdown also disconnects the input resistor of the divider on the VIN- input to the comparator. As this would typically be connected to  $V_{CC}$  for battery voltage detection. Shutting down MC13181 removes this approximately  $5.0\,\mu A$  current.

Care should be taken if this pin is to be driven from a processor operating on a voltage supplied by MC13181.

## 3.4 Reset Circuit

The RESET\_B output goes high after a delay, based on the delay capacitor. It is initiated when  $V_{LDO\_1.85}$  rises above the reset threshold of 1.70 V. When  $V_{LDO\_1.85}$  falls below the reset threshold, RESET\_B goes low with no delay.

To calculate the value of the delay capacitor needed for a given delay, the formula C/I = dV/dT can be used. At the start of the delay, the capacitor is shorted nearly to 0 V, and then charged with a 500 nA current source until its voltage reaches the reference voltage, 1.265 V.

```

T delay = C * V / I, simplifies to

T delay (ms) \sim= 2.53 x C (nF)

or,

C (nF) \sim= T / 2.53 (T in ms)

```

Note: The threshold voltage, resistance of the shorting FET and the current source will vary with temperature and  $V_{\rm CC2}$ , so the resulting delay will vary by 2:1 or more.

# 3.5 Comparator with Programmable Hysteresis

The MC13181 includes a general purpose comparator. The IC's VIN- input incorporates internal resistors scaling (by a factor of approximately 0.44) the voltage to the minus input of the comparator. The IC's VIN+ input is directly connected to the plus input of the comparator. A typical application connects the VIN- input to  $V_{CC2}$  and VIN+ to the reference output for Under-Voltage Detection. The scaling resistors thereby set the threshold to 2.88 V with no additional components required.

Hysteresis, of typically 30 mV, can be enabled or disabled via the HYSSEL pin (low is enable), allowing versatility for general purpose applications.

The comparator may be used for general purpose applications, if the fixed divider ratio is accounted for. The inputs should not go lower than 1.0 V. The plus input should not exceed  $V_{CC2}$  - 1.0 V and the minus input should not exceed  $V_{CC2}$ .

The output of the comparator is push-pull, referenced to  $V_{LDO\_1.85}$ .

## 3.6 OR Gate & Inverter

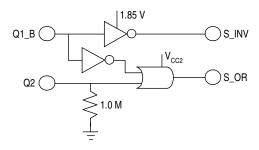

The IC incorporates a general purpose inverter and OR gate. The Q1\_B input is the input to the inverter and one of the OR gate inputs. The S\_INV output will be the logical inversion of the input. The S\_OR output will be the logical OR of the inverse of Q1\_B and Q2. Q2 has an internal pull-down. See Figure 3. A truth table of this function is shown in Table 7:

| Q1_B | Q2 | S_OR | S_INV |

|------|----|------|-------|

| 0    | 0  | 1    | 1     |

| 0    | 1  | 1    | 1     |

| 1    | 0  | 0    | 0     |

| 1    | 1  | 1    | 0     |

Table 7. Inverter/OR Logic Truth Table

Figure 3. Inverter/OR Logic Block Diagram

Both inputs feature voltage robust level shifting and a Vih may range from 1.5 V through  $V_{CC2}$ . The inverter output is referenced to  $V_{LDO\_1.85}$ . The OR gate output is referenced to  $V_{CC2}$ .

## 3.7 Thermal Shutdown

Internal thermal shutdown circuitry is provided to protect the IC and the system in the event that the maximum junction temperature is exceeded. When activated (typical threshold is set at 150°C), the three LDO regulators turn off until they are reactivated. This feature is provided to prevent failures from inadvertent overheating. Hysteresis allows stable thermal recovery.

Care should be taken in design to ensure that regulator loading and ambient thermal conditions are managed to avoid excessive power dissipation and thermal shutdown in normal operation.

PC board layout should include connection to exposed thermal pad on IC and ensure adequate heat dissipation.

# 4 Packaging

Figure 4. Outline Dimensions for QFN-24 (Case 1307-01, Issue B)

## **NOTES**

#### **HOW TO REACH US:**

#### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu Minato-ku, Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

#### **TECHNICAL INFORMATION CENTER:**

1-800-521-6274

#### **HOME PAGE:**

http://www.motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. The Bluetooth trademarks are owned by their proprietor and used by Motorola, Inc., under license. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2002