SGLS116A – JANUARY 2001 – REVISED MAY 2001

- Gate Driver LSI for Active-Matrix LCD

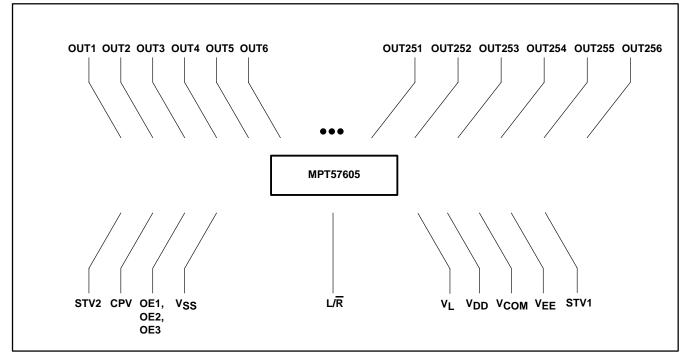

- Liquid-Crystal Control Outputs: 256

- Enables High-Voltage Operation: Liquid-Crystal Control Signal V<sub>L</sub> + 35 V (max)

- Liquid-Crystal Control Signal's Negative-Voltage Output Is Enabled by a Level-Shift Circuit

- On-Chip Bidirectional Shift Registers

- TCP (Tape Carrier Package)

- CMOS-LSI Structure

#### description

The MPT57605 is a gate driver LSI that drives an active-matrix LCD panel and implements a multi-pin configuration, low power consumption, and high voltage. Furthermore, the level-shift circuit enables positive and negative power supplies. Also, it is compatible with various SVGA/XGA panels.

NOTE A: This figure shows the copper foil side and does not describe the TAB outline or show the NC pins.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2001, Texas Instruments Incorporated On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

SGLS116A - JANUARY 2001 - REVISED MAY 2001

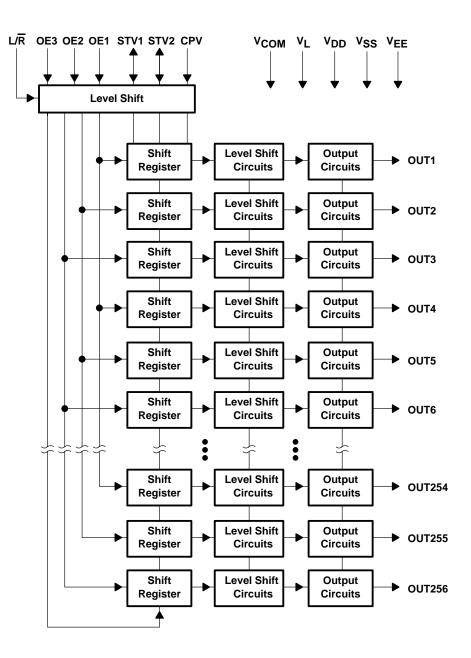

#### block diagram

SGLS116A - JANUARY 2001 - REVISED MAY 2001

#### **Terminal Functions**

| TERMINAL<br>NAME    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPV                 | I   | Vertical shift clock input<br>The shift register's shift clock. Data are shifted in sync with the rising edge of this pin.                                                                                                                                                                                                                                                                                            |

| OE1<br>OE2<br>OE3   | I   | Output enable pins<br>The liquid-crystal control output is held low by setting pins OE1, 2, and 3 High. However, the shift registers<br>are not cleared. OE is async with CPV.<br>Enable control target pin:<br>OE1: OUT1, OUT4, OUT7OUT253, OUT256<br>OE2: OUT2, OUT5, OUT8OUT254<br>OE3: OUT3, OUT6, OUT9OUT255<br>These combinations are generally as above, regardless of the L/R polarity.                       |

| L/R                 | I   | Shift direction switching pin<br>This pin is used to switch the data's shift direction.<br>$L/\overline{R} = L$ : STV1 $\leftarrow$ OUT1 $\leftarrow$ OUT2OUT255 $\leftarrow$ OUT256 $\leftarrow$ STV2<br>$L/\overline{R} = H$ : STV1 $\rightarrow$ OUT1 $\rightarrow$ OUT2OUT255 $\rightarrow$ OUT256 $\rightarrow$ STV2                                                                                             |

| STV1<br>STV2        | I/O | Shift data I/O pins<br>These pins are used to input/output data to/from a shift register. During input, data are captured in sync with<br>the leading edge of CPV. During output, data are output in sync with its trailing edge.<br>L/R = L: STV1 is the next-stage data output pin, and STV2 is the shift data input pin.<br>L/R = H: STV1 is the shift data input pin, and STV2 is the next-stage data output pin. |

| OUT1 thru<br>OUT256 | 0   | Output terminals                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCOM                |     | Power supply for high-withstand-voltage logic                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub>     |     | Power supply for logic input                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>     |     | GND for logic input                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>EE</sub>     |     | GND                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VL                  |     | Negative power supply for liquid-crystal control                                                                                                                                                                                                                                                                                                                                                                      |

SGLS116A – JANUARY 2001 – REVISED MAY 2001

#### detailed description

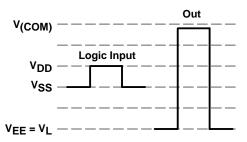

#### liquid-crystal control output voltage

The MPT57605 enables negative-voltage output for the liquid-crystal control output.

$V_{COM} - V_L = 35 \text{ V} \max V_L - V_{EE} = 0.6 \text{ V} \cdot V_{COM} - V_{SS} = 10.25 \text{ V} \cdot V_{COM}$

#### Figure 1. Liquid-Crystal Control Output Voltage

For the input signals (CPV, OE1-3, L/R, STV1 and STV2), input the amplitude of V<sub>DD</sub> from V<sub>SS</sub>.

The next-stage data output pins (STV1, STV2) output the next level:

H level =  $V_{DD}$ L level =  $V_{SS}$

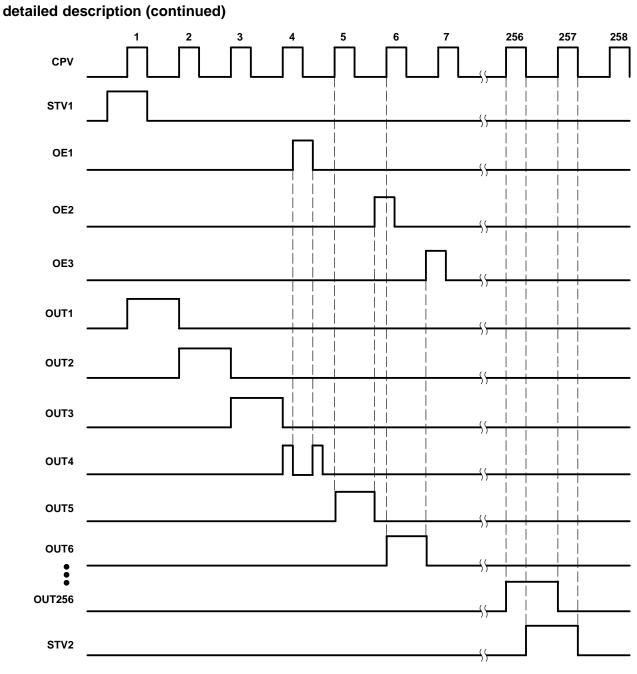

#### details of operation

The liquid-crystal control outputs (OUT1-256) output either a selective signal (H) or a nonselective signal (L), depending on the input signals (STV1 and STV2, CPV, OE1, OE2, OE3).

A right data shift (OUT1  $\rightarrow$  OUT256) or a left data shift (OUT256  $\rightarrow$  OUT1) can be selected by means of the shift direction switching pin (L/ $\overline{R}$ ).

When the  $L/\overline{R}$  pin is H, the vertical shift data (STV1) are captured at the leading edge of the shift clock (CPV), after which they are output to the liquid-crystal control output OUT1. Furthermore, the OUT1 output data are shifted to OUT2 at the leading edge of the next CPV, and the data newly fetched from STV1 are output to OUT1. In this manner, they are shifted successively in sync with the leading edge of CPV, and the OUT256 data are output to STV2 in sync with the trailing edge of CPV.

When the  $L/\overline{R}$  pin is L, the vertical shift data (STV2) are captured at the leading edge of the shift clock (CPV), after which they are output to the liquid-crystal control output OUT256. Furthermore, the OUT256 output data are shifted to OUT255 at the leading edge of the next CPV, and the data newly fetched from STV2 are output to OUT256. In this manner, they are shifted successively in sync with the leading edge of CPV, and the OUT1 data are output to STV1 in sync with the trailing edge of CPV.

Also, while OE1, OE2, and OE3 are H, the corresponding liquid-crystal control outputs (OE1: OUT1, 4, 7,...; OE2: OUT2, 5, 8,...; OE3: OUT 3, 6, 9,...) all become nonselective signals (L). In order to hold the internal data, however, the previous state is restored by again setting to L.

SGLS116A - JANUARY 2001 - REVISED MAY 2001

SGLS116A - JANUARY 2001 - REVISED MAY 2001

## absolute maximum ratings (referenced to $V_{SS} = 0 V$ )<sup>†</sup>

| Supply voltage <sup>‡§</sup> , V <sub>DD</sub> |                                             |

|------------------------------------------------|---------------------------------------------|

| V <sub>EE</sub>                                | –20 to 0.3 V                                |

| $v_L^{}$                                       | <sub>E</sub> – 0.3 to V <sub>EE</sub> + 7 V |

| V <sub>COM</sub> – V <sub>EE</sub>             | – 0.3 to 40 V                               |

| Input voltage, V <sub>IN</sub>                 |                                             |

| Storage temperature, T <sub>STR</sub>          | –55°C to 125°C                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> Unless otherwise indicated, all voltages are with reference to V<sub>SS</sub>.

§ Power up in the following order:  $V_{DD} \rightarrow V_{EE} \rightarrow input signal \rightarrow V_{COM}$ . Power down by reversing the sequence.

#### recommended operating conditions (referenced to V<sub>SS</sub> = 0 V)

|                                                    | MIN                 | TYP | MAX                 | UNIT |

|----------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>DD</sub>                    | 3.0                 | 3.3 | 3.6                 | V    |

| Supply voltage, V <sub>COM</sub>                   | 10                  |     | 25                  | V    |

| Supply voltage, V <sub>EE</sub>                    | -15                 |     | -5                  | V    |

| Supply voltage, $V_L - V_{EE}$                     | 0                   |     | 6                   | V    |

| Supply voltage, V <sub>COM</sub> – V <sub>EE</sub> | 17                  |     | 35                  | V    |

| Low-level input voltage, VIL                       | VSS                 | 0   | $0.1 \times V_{DD}$ | V    |

| High-level input voltage, V <sub>IH</sub>          | $0.9 \times V_{DD}$ |     | V <sub>DD</sub>     | V    |

| Clock frequency, fCPV                              |                     |     | 100                 | kHz  |

| Operating free-air temperature, T <sub>A</sub>     | -55                 |     | 125                 | °C   |

## electrical characteristics over full range of recommended operating conditions, $V_{SS} = 0 V$ (unless otherwise noted)

|                 | PARAMETER                                  | TEST CONDITIONS             | MIN                   | TYP MAX               | UNIT |

|-----------------|--------------------------------------------|-----------------------------|-----------------------|-----------------------|------|

| VOL             | Low-level output voltage (STV1, STV2)      | I <sub>OL</sub> = 40 μA     | VSS                   | V <sub>SS</sub> + 0.4 | V    |

| VOH             | High-level output voltage (STV1, STV2)     | I <sub>OH</sub> = -40 μA    | V <sub>DD</sub> – 0.4 | V <sub>DD</sub>       | V    |

| R <sub>OL</sub> | Low-level output resistance (OUT1–OUT256)  | $V_{OUT} = V_{L} + 0.2 V$   |                       | 1000                  | Ω    |

| ROH             | High-level output resistance (OUT1–OUT256) | $V_{OUT} = V_{COM} - 0.2 V$ |                       | 1000                  | Ω    |

| l               | Input current                              | All input terminals         | -5                    | 5                     | μA   |

| I <sub>DD</sub> | Continuous current dissipation             | See Notes 1 and 2           |                       | 500                   |      |

| Ісом            | Continuous current dissipation             | See Notes 1 and 2           |                       | 100                   | μA   |

NOTES: 1. Current consumption by a 1/768-duty liquid-crystal display.

2. Condition: The outputs are no load. The inputs are VIH = VDD, VIL = VSS, fCPV = 50 kHz, fSTV = 104.2 Hz, and OE1-3 = VIL.

SGLS116A - JANUARY 2001 - REVISED MAY 2001

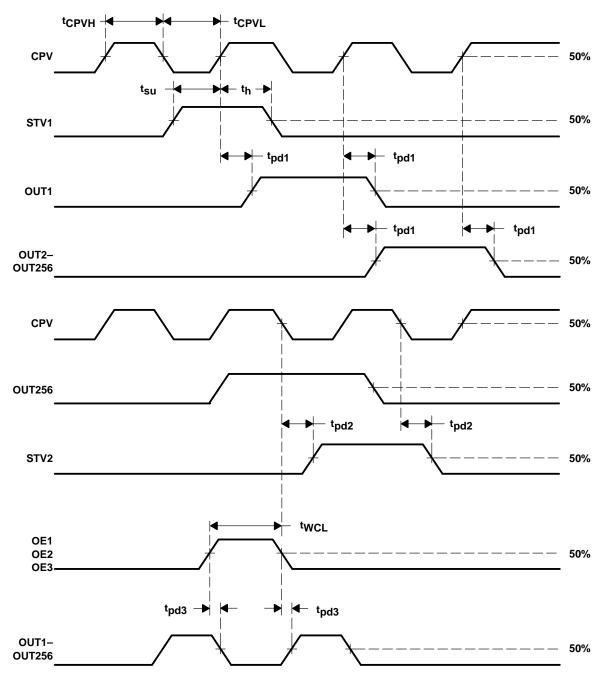

# timing requirements over full range of recommended operating conditions, $V_{SS} = 0 V$ (unless otherwise noted)

|                                                  | PARAMETER             | MIN | MAX | UNIT |

|--------------------------------------------------|-----------------------|-----|-----|------|

| fCP                                              | Operating frequency   |     | 100 | KHz  |

| <sup>t</sup> CPVH <sup>,</sup> <sup>t</sup> CPVL | CPV clock pulse width | 4   |     | μs   |

| tWCL                                             | Clear enable time     | 1   |     | μs   |

| t <sub>su</sub>                                  | Data setup time       | 700 |     | ns   |

| t <sub>h</sub>                                   | Data hold time        | 700 |     | ns   |

# switching characteristics over full range of recommended operating conditions, $V_{SS} = 0 V$ (unless otherwise noted)

|                  | PARAMETER                                         | TEST CONDITIONS         | MIN MAX | UNIT |

|------------------|---------------------------------------------------|-------------------------|---------|------|

| <sup>t</sup> pd1 | Propagation delay time, CPV to outputs            | C <sub>L</sub> = 300 pF | 1500    | ns   |

| tpd2             | Propagation delay time, CPV to STV1, STV2         | C <sub>L</sub> = 30 pF  | 800     | ns   |

| tpd3             | Propagation delay time, output enables to outputs | C <sub>L</sub> = 300 pF | 800     | ns   |

NOTE: The ac timing is 50% of the I/O amplitude, for each signal.

SGLS116A - JANUARY 2001 - REVISED MAY 2001

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated