# OKI Semiconductor MSM7603/7603B

Echo Canceler

## **GENERAL DESCRIPTION**

The MSM7603/7603B is an improved version of the MSM7602 with basically the same configuration, and offers twice the cancelable echo delay time of the MSM7602.

The MSM7603B I/O interface allows switching between  $\mu$ -law PCM and A-law PCM.

The MSM7603/7603B is a low-power CMOS IC device for canceling echo (in an acoustic system or telephone line) generated in a speech path.

Echo is canceled, in digital signal processing, by estimating the echo path and generating a pseudo echo signal.

When used as an acoustic echo canceler, the device can cancel the acoustic echo, between the loud speaker and the microphone, which occur during hands free communication such as on a cellular phone or a conference system phone.

When used as a line echo canceler, the device can cancel the line echo which returns due to impedance mismatching in a hybrid.

In addition, a quality conversation is made possible by controlling the level and by preventing howling through a howling detector, double talk detector, attenuation function and a gain control function, and by controlling the low level noise by means of a center clipping function. The use of a single chip codec, such as the MSM7704 (3 V) and MSM7533 (5 V), allows an economic and efficient echo canceler to be configured.

# FEATURES

- Can handle both acoustic and telephone line echoes.

- Switchable between µ-law PCM and A-law PCM interfaces. (MSM7603B)

- Cancelable echo delay time: MSM7603B-003 ...... 55 ms (max.)

- Echo attenuation : 30 dB (typ.)

- Clock frequency : 19.2 MHz

17.5 MHz to 20 MHz (when internal sync signal not used)

- Power supply voltage : 2.7 V to 5.5 V

- Package:

28-pin plastic SSOP (SSOP28-P-485-0.65-K) (Product name : MSM7603-003GS-K)

(Product name : MSM7603B-003GS-K)

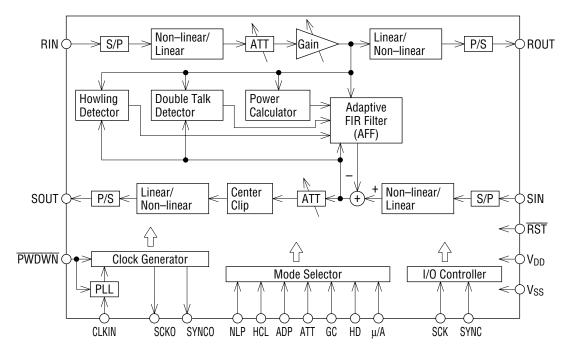

#### BLOCK DIAGRAM MSM7603/7603B

\* For MSM7603B only

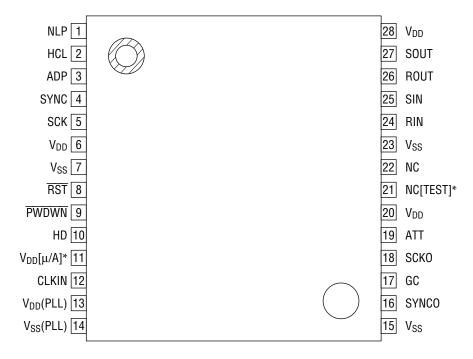

# **PIN CONFIGURATION (TOP VIEW)**

28-Pin Plastic SSOP

\* Pins shown in brackets apply to MSM7603B.

# **PIN DESCRIPTIONS**

| Pin | Symbol | Туре | Description                                                         |

|-----|--------|------|---------------------------------------------------------------------|

| 1   | NLP    | Ι    | This is the control pin for the center clipping function to force   |

|     |        |      | the SOUT output to a minimum value when the SOUT signal is          |

|     |        |      | below –57 dBm0. Effective for reducing low-level noise.             |

|     |        |      | "H": Center clip ON                                                 |

|     |        |      | "L": Center clip OFF                                                |

| 2   | HCL    | I    | This is the through mode control pin.                               |

|     |        |      | When this pin is in the through mode the RIN and SIN data are       |

|     |        |      | output to ROUT and SOUT. At the same time, the coefficient of       |

|     |        |      | the adaptive FIR filter is cleared.                                 |

|     |        |      | "H": Through mode                                                   |

|     |        |      | "L": Normal mode (echo canceler operates)                           |

| 3   | ADP    | I    | This is the AFF coefficient control pin which stops updating the    |

|     |        |      | adaptive FIR filter (AFF) coefficient and sets it to a fixed value, |

|     |        |      | when the pin is configured to be the coefficient fix mode.          |

|     |        |      | Used when holding the AFF coefficient which has been once           |

|     |        |      | converged.                                                          |

|     |        |      | "H": Coefficient fix mode                                           |

|     |        |      | "L": Normal mode (coefficient update)                               |

| 4   | SYNC   | I    | This is the input pin for the sync signal for transmit/receive      |

|     |        |      | serial data. This pin uses the external SYNC or SYNCO.              |

|     |        |      | Inputs the PCM codec transmit/receive sync signal (8 kHz).          |

| 5   | SCK    | I    | This is the clock input pin for transmit/receive serial data. It    |

|     |        |      | uses the external SCK or the SCKO.                                  |

|     |        |      | Input the PCM codec transmit/receive clock (64 to 2048 kHz).        |

# **PIN DESCRIPTIONS (Continued)**

| Pin | Symbol                | Туре | Description                                                                  |

|-----|-----------------------|------|------------------------------------------------------------------------------|

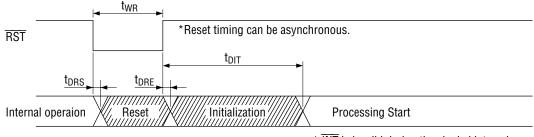

| 8   | RST                   | I    | This is the input pin for the reset signal.                                  |

|     |                       |      | "L": Reset mode                                                              |

|     |                       |      | "H": Normal operation mode                                                   |

|     |                       |      | Due to initialization, input signals are disabled for 100 $\mu s$ after rese |

|     |                       |      | (after RST is returned from "L" to "H").                                     |

|     |                       |      | Input the basic clock during the reset.                                      |

|     |                       |      | Output pins during the reset are in the following sates :                    |

|     |                       |      | High impedance: SOUT, ROUT                                                   |

|     |                       |      | Not affected: SYNCO, SCKO                                                    |

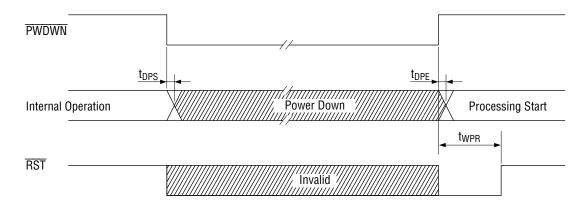

| 9   | PWDWN                 | I    | This is the power-down mode control pin for power down operation             |

|     |                       |      | "L": Power-down mode                                                         |

|     |                       |      | "H": Normal operation mode                                                   |

|     |                       |      | During power-down mode, all input pins are disabled and output               |

|     |                       |      | pins are in the following states :                                           |

|     |                       |      | High impedance : SOUT, ROUT                                                  |

|     |                       |      | "L": SYNCO, SCKO                                                             |

|     |                       |      | Reset after the power-down mode is released.                                 |

| 10  | HD                    | I    | This pin controls the howling detect function that detects and               |

|     |                       |      | cancels a howling generated during hands-free talking for                    |

|     |                       |      | acoustic system.                                                             |

|     |                       |      | This function is used to cancel acoustic echoes.                             |

|     |                       |      | "L": Howling detector ON                                                     |

|     |                       |      | "H": Howling detector OFF                                                    |

| 11  | (μ/Α)                 | I    | Used for MSM7603B only.                                                      |

|     |                       |      | This is the input pin for $\mu$ -law PCM/A-law PCM interface select          |

|     |                       |      | signal.                                                                      |

|     |                       |      | "L": A-law PCM interface                                                     |

|     |                       |      | "H": μ-law PCM interface                                                     |

|     |                       |      | For MSM7603, apply V <sub>DD</sub> .                                         |

| 12  | CLKIN                 | I    | This is the input pin for external input for the basic clock.                |

|     |                       |      | Input the basic clock (17.5 to 20 MHz).                                      |

|     |                       |      | When the internal sync signal (SYNCO, SCKO) is used, input the               |

|     |                       |      | basic clock of 19.2 MHz.                                                     |

| 13  | V <sub>DD</sub> (PLL) | I    | This is the power supply pin for the PLL circuit used for the basic          |

|     |                       |      | clock.                                                                       |

|     |                       |      | Insert a 0.1 $\mu$ F capacitor with excellent high frequency                 |

|     |                       |      | characteristics between $V_{DD}$ (PLL) and $V_{SS}$ (PLL).                   |

| 14  | V <sub>SS</sub> (PLL) | I    | This is the ground pin for the PLL circuit used for the basic clock.         |

| 16  | SYNCO                 | 0    | This is the output pin for the 8 kHz sync signal for the PCM codec           |

|     |                       |      | Connect to the SYNC pin and the PCM codec transmit/receive sync              |

|     |                       |      | pin.                                                                         |

|     |                       |      | Leave open if using an external SYNC.                                        |

# **PIN DESCRIPTIONS (Continued)**

| Pin | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | GC     | 1    | This is the pin for the input signal by which the gain controller<br>for the RIN input is controlled. The pin also controls RIN input<br>level and prevents howling.<br>The gain controller adjusts the RIN input level when it is -20<br>dBm0 or above. RIN input levels from -20 to -11.5 dBm0 will be<br>suppressed to -20 dBm0 in the attenuation range from 0 to 8.5 dB.<br>RIN input levels above -11.5 dBm0 will always be attenuated by<br>8.5 dB.<br>"H": Gain control ON<br>"L": Gain control OFF<br>"H" is recommended for performing echo cancellation.   |

| 18  | SCKO   | 0    | This is the output pin for the transmit clock signal (256 kHz) for the PCM codec.      Connect to the SCK pin and the PCM codec transmit/receive clock pin.      Leave open when using an external SCK.                                                                                                                                                                                                                                                                                                                                                               |

| 19  | ATT    | 1    | This is the control pin for the ATT function which prevents howling<br>by attenuators (ATT) for the RIN input and SOUT output.<br>If there is input only to RIN, then the ATT for the SOUT output is<br>activated.<br>If there is no input to SIN or there is input to both SIN and RIN,<br>then the ATT for the RIN input is activated.<br>Either the ATT for the RIN output or the ATT for the SOUT is<br>always activated in all cases, and the attenuation of ATT is 6 dB.<br>"H": ATT OFF<br>"L": ATT ON<br>"L" is recommended for performing echo cancellation. |

| 21  | (TEST) | 0    | This pin is for MSM7603B only and not used. Should be left open<br>In MSM7603 it is an NC pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24  | RIN    | Ι    | This is the receive serial data input pin.<br>Input the PCM signal synchronized to SYNC and SCK.<br>Data is read at the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25  | SIN    | Ι    | This is the transmit serial data input pin.Input the PCM signal synchronized to SYNC and SCK.Data is read at the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 26  | ROUT   | 0    | This is the output pin for receive serial data.Outputs the PCM signal synchronized to SYNC and SCK.This pin is in high impedance state during the absence of data output.                                                                                                                                                                                                                                                                                                                                                                                             |

| 27  | SOUT   | 0    | This is the output pin for transmit serial data.<br>Outputs the PCM signal synchronized to SYNC and SCK.<br>This pin is in high impedance state during the absence of data output.                                                                                                                                                                                                                                                                                                                                                                                    |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                        | Unit |

|----------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | -0.3 to + 7                   | V    |

| Input Voltage        | VIN              | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation    | PD               |           | 1                             | W    |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                   | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

(V<sub>DD</sub> = 2.7 V to 3.6 V)

| Parameter                | Symbol          | Condition | Min. | Тур. | Max.            | Unit |

|--------------------------|-----------------|-----------|------|------|-----------------|------|

| Power Supply Voltage     | V <sub>DD</sub> | —         | 2.7  | 3.3  | 3.6             | V    |

| Power Supply Voltage     | V <sub>SS</sub> | —         | _    | 0    |                 | V    |

| High Level Input Voltage | VIH             | —         | 2.0  | —    | V <sub>DD</sub> | V    |

| Low Level Input Voltage  | VIL             | _         | 0    |      | 0.5             | V    |

| Operating Temperature    | Та              | —         | -40  | +25  | +85             | °C   |

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$

|                          |                 |           |      | (* 01 |                 | · · · · |

|--------------------------|-----------------|-----------|------|-------|-----------------|---------|

| Parameter                | Symbol          | Condition | Min. | Тур.  | Max.            | Unit    |

| Power Supply Voltage     | V <sub>DD</sub> | —         | 4.5  | 5     | 5.5             | V       |

| Power Supply Voltage     | V <sub>SS</sub> | —         | -    | 0     | —               | V       |

| High Level Input Voltage | VIH             | _         | 2.4  |       | V <sub>DD</sub> | V       |

| Low Level Input Voltage  | VIL             | —         | 0    | _     | 0.8             | V       |

| Operating Temperature    | Та              | —         | -40  | +25   | +85             | °C      |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

| DC Characteristics                  |                  | (V <sub>D</sub>                   | <sub>D</sub> = 2.7 V to | o 3.6 V, Ta | = -40°C to      | +85°C) |

|-------------------------------------|------------------|-----------------------------------|-------------------------|-------------|-----------------|--------|

| Parameter                           | Symbol           | Condition                         | Min.                    | Тур.        | Max.            | Unit   |

| High Level Output Voltage           | V <sub>OH</sub>  | I <sub>0H</sub> = 40 μA           | 2.2                     | _           | V <sub>DD</sub> | V      |

| Low Level Output Voltage            | V <sub>OL</sub>  | l <sub>OL</sub> = 1.6 mA          | 0                       | _           | 0.4             | V      |

| High Level Input Current            | Іін              | $V_{IH} = V_{DD}$                 | —                       | 0.1         | 1               | μA     |

| Low Level Input Current             | Ι <sub>ΙL</sub>  | V <sub>IL</sub> = V <sub>SS</sub> | -1                      | -0.1        | _               | μA     |

| High Level Output Leakage Current   | I <sub>OZH</sub> | V <sub>OH</sub> = V <sub>DD</sub> | _                       | 0.1         | 1               | μA     |

| Low Level Output Leakage Current    | I <sub>OZL</sub> | V <sub>OL</sub> = V <sub>SS</sub> | -1                      | -0.1        | _               | μA     |

| Power Supply Current<br>(Operating) | I <sub>DDO</sub> | _                                 | _                       | 30          | 50              | mA     |

| Power Supply Current<br>(Standby)   | I <sub>DDS</sub> | PWDWN = "L"                       | _                       | 0.5         | 1               | mA     |

| Input Capacitance                   | CI               | _                                 | —                       | _           | 15              | pF     |

| Output Load Capacitance             | CLOAD            |                                   | _                       |             | 20              | pF     |

#### $(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, \text{ Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                           | Symbol            | Condition                         | Min. | Тур. | Max.            | Unit |

|-------------------------------------|-------------------|-----------------------------------|------|------|-----------------|------|

| High Level Output Voltage           | V <sub>OH</sub>   | I <sub>0H</sub> = 40 μA           | 4.2  |      | V <sub>DD</sub> | V    |

| Low Level Output Voltage            | V <sub>OL</sub>   | I <sub>OL</sub> = 1.6 mA          | 0    |      | 0.4             | V    |

| High Level Input Current            | IIH               | $V_{IH} = V_{DD}$                 | —    | 0.1  | 10              | μA   |

| Low Level Input Current             | ١ <sub>١L</sub>   | $V_{IL} = V_{SS}$                 | -10  | -0.1 | _               | μA   |

| High Level Output Leakage Current   | I <sub>OZH</sub>  | $V_{OH} = V_{DD}$                 |      | 0.1  | 10              | μA   |

| Low Level Output Leakage Current    | I <sub>OZL</sub>  | V <sub>0L</sub> = V <sub>SS</sub> | -10  | -0.1 | —               | μA   |

| Power Supply Current<br>(Operating) | I <sub>DDO</sub>  | _                                 | _    | 40   | 70              | mA   |

| Power Supply Current<br>(Standby)   | I <sub>DDS</sub>  | PWDWN = "L"                       | _    | 0.5  | 1               | mA   |

| Input Capacitance                   | CI                |                                   | _    |      | 15              | pF   |

| Output Load Capacitance             | C <sub>LOAD</sub> |                                   |      |      | 20              | рF   |

| Parameter                  | Symbol | Condition                   | Min. | Тур. | Max. | Unit |

|----------------------------|--------|-----------------------------|------|------|------|------|

|                            |        | $R_{IN} = -10 \text{ dBm0}$ |      |      |      |      |

|                            |        | (5 kHz band white noise)    |      |      |      |      |

| Echo Attenuation           | LRES   | E. R. L. (echo return loss) |      | 30   | _    | dB   |

|                            | -neo   | = 6 dB                      |      |      |      |      |

|                            |        | T <sub>D</sub> = 50 ms      |      |      |      |      |

|                            |        | ATT, GC, NLP: OFF           |      |      |      |      |

|                            |        | R <sub>IN</sub> = -10 dBm0  | _    | _    | 55   |      |

| Canaalabla Fabo Dalay Tima | TD     | (5 kHz band white noise)    |      |      |      |      |

| Cancelable Echo Delay Time | ID     | E. R. L. = 6 dB             |      |      |      | ms   |

|                            |        | ATT, GC, NLP: OFF           |      |      |      |      |

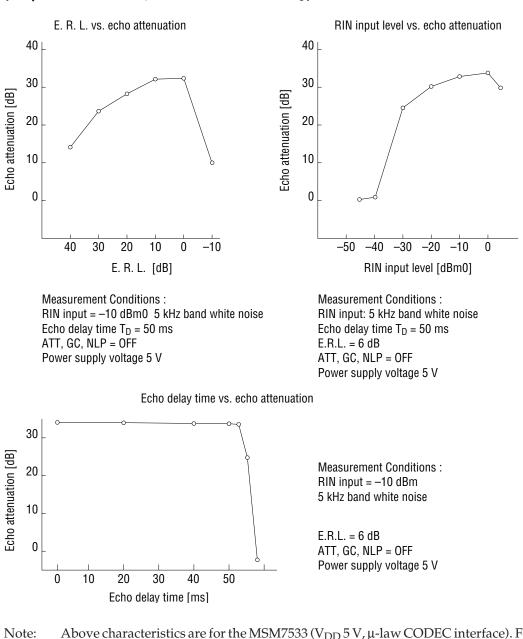

## Echo Canceler Characteristics (Refer to Characteristics Diagram)

#### **AC Characteristics**

$(Ta = -40^{\circ}C \text{ to } +85^{\circ}C)$

| <b>D</b> .                                               |                  | V <sub>DD</sub> = | = 2.7 V to        | 3.6 V                              | V <sub>DD</sub> = | = 4.5 V to        | 5.5 V                              |       |

|----------------------------------------------------------|------------------|-------------------|-------------------|------------------------------------|-------------------|-------------------|------------------------------------|-------|

| Parameter                                                | Symbol           | Min.              | Тур.              | Max.                               | Min.              | Тур.              | Max.                               | Unit  |

| Clock Frequency                                          | 4                | _                 | 19.2              | _                                  | _                 | 19.2              |                                    | N/11- |

| When Internal Sync Signal is not used                    | fc               | 17.5              | _                 | 20.0                               | 17.5              | _                 | 20.0                               | MHz   |

| Clock Cycle Time                                         |                  | _                 | 52.08             | _                                  |                   | 52.08             |                                    |       |

| When Internal Sync Signal is not used                    | t <sub>МСК</sub> | 50.0              | _                 | 57.14                              | 50.0              |                   | 57.14                              | ns    |

| Clock Duty Ratio                                         | t <sub>DMC</sub> | 40                | _                 | 60                                 | 40                |                   | 60                                 | ns    |

| Clock "H" Level Pulse Width<br>f <sub>C</sub> = 19.2 MHz | t <sub>МСН</sub> | 20.8              | _                 | 31.3                               | 20.8              |                   | 31.3                               | ns    |

| Clock "L" Level Pulse Width<br>f <sub>C</sub> = 19.2 MHz | t <sub>MCL</sub> | 20.8              |                   | 31.3                               | 20.8              |                   | 31.3                               | ns    |

| Clock Rise Time                                          | tr               | _                 | _                 | 5                                  | _                 | _                 | 5                                  | ns    |

| Clock Fall Time                                          | t <sub>f</sub>   | _                 |                   | 5                                  | _                 | _                 | 5                                  | ns    |

| Sync Clock Output Time                                   | t <sub>DCM</sub> | _                 |                   | 40                                 | _                 | _                 | 40                                 | ns    |

| Internal Sync Clock Frequency                            | f <sub>CO</sub>  | _                 | 256               | _                                  | _                 | 256               | _                                  | kHz   |

| Internal Sync Clock Output Cycle Time                    | t <sub>CO</sub>  |                   | 3.9               | _                                  |                   | 3.9               | _                                  | μs    |

| Internal Sync Clock Duty Ratio                           | t <sub>DCO</sub> | _                 | 50                | _                                  |                   | 50                |                                    | %     |

| Internal Sync Signal Output Delay Time                   | t <sub>DCC</sub> | _                 |                   | 5                                  | _                 |                   | 5                                  | ns    |

| Internal Sync Signal Period                              | tcyo             |                   | 125               |                                    |                   | 125               |                                    | μs    |

| Internal Sync Signal Output Width                        | t <sub>WSO</sub> |                   | t <sub>CO</sub>   | _                                  |                   | t <sub>CO</sub>   |                                    | μs    |

| Transmit/Receive Sync Clock Frequency                    | f <sub>SCK</sub> | 64                | _                 | 2048                               | 64                | _                 | 2048                               | kHz   |

| Transmit/Receive Sync Clock Cycle Time                   | t <sub>SCK</sub> | 0.488             |                   | 15.6                               | 0.488             | _                 | 15.6                               | μs    |

| Transmit/Receive Sync Clock Duty Ratio                   | t <sub>DSC</sub> | 40                | 50                | 60                                 | 40                | 50                | 60                                 | %     |

| Transmit/Receive Sync Signal Period                      | tcyc             | 123               | 125               |                                    | 123               | 125               |                                    | μs    |

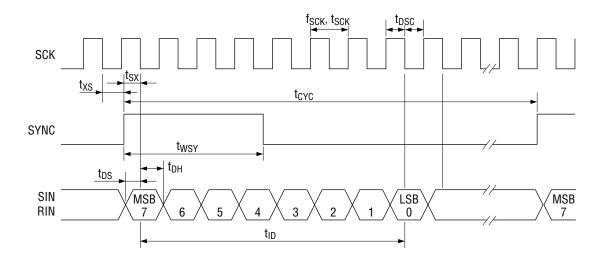

|                                                          | t <sub>XS</sub>  | 45                |                   | _                                  | 45                | _                 |                                    | ns    |

| Sync Timing                                              | t <sub>SX</sub>  | 45                |                   | t <sub>CYC</sub> -t <sub>SCK</sub> | 45                |                   | t <sub>CYC</sub> -t <sub>SCK</sub> | ns    |

| Sync Signal Width                                        | t <sub>WSY</sub> | t <sub>SCK</sub>  |                   | _                                  | t <sub>SCK</sub>  | _                 | _                                  | μs    |

| Receive Signal Setup Time                                | t <sub>DS</sub>  | 45                |                   | _                                  | 45                | _                 |                                    | ns    |

| Receive Signal Hold Time                                 | t <sub>DH</sub>  | 45                |                   |                                    | 45                | _                 |                                    | ns    |

| Receive Data Input Time                                  | t <sub>ID</sub>  | _                 | 7t <sub>SCK</sub> |                                    |                   | 7t <sub>SCK</sub> |                                    | μs    |

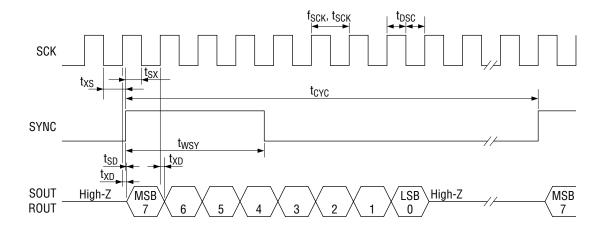

| · · · · · · · · · · · · · · · · · · ·                    | t <sub>SD</sub>  |                   | _                 | 90                                 |                   | _                 | 90                                 | ns    |

| Serial Output Delay Time                                 | t <sub>XD</sub>  | _                 |                   | 90                                 |                   |                   | 90                                 | ns    |

| Reset Signal Input Width                                 | t <sub>WR</sub>  | 1                 |                   |                                    | 1                 |                   |                                    | μs    |

| Reset Start Time                                         | t <sub>DRS</sub> | 5                 |                   | _                                  | 5                 | _                 |                                    | ns    |

| Reset End Time                                           | t <sub>DRE</sub> | _                 |                   | 52                                 |                   | _                 | 52                                 | ns    |

| Processing Operation Start Time                          | t <sub>DIT</sub> | 100               |                   |                                    | 100               |                   |                                    | μs    |

| Power Down Start Time                                    | t <sub>DPS</sub> |                   |                   | 111                                |                   |                   | 111                                | ns    |

| Power Down End Time                                      | t <sub>DPE</sub> | _                 |                   | 15                                 |                   |                   | 15                                 | ns    |

| Reset Pulse Width Immediately after Power Down           |                  | 10                | _                 | _                                  | 10                | _                 |                                    | ns    |

| Control Pin Setup Time (RST)                             | t <sub>DSR</sub> | 20                |                   |                                    | 20                | _                 |                                    | ns    |

| Control Pin Hold Time (RST)                              | t <sub>DHR</sub> | 20                |                   | _                                  | 20                |                   | _                                  | ns    |

| Control Pin Setup Time                                   | t <sub>DTS</sub> | 0                 |                   |                                    | 0                 |                   | _                                  | ns    |

| Control Pin Hold Time                                    | t <sub>DTH</sub> | 160               |                   | _                                  | 160               |                   | <u> </u>                           | ns    |

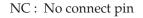

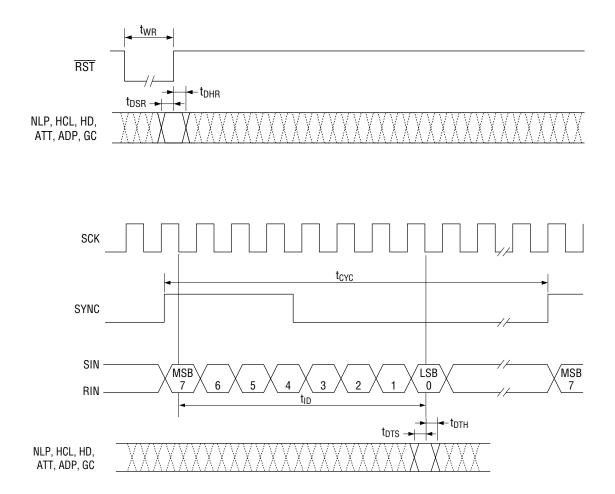

#### TIMING DIAGRAM Clock Timing

# **Serial Input Timing**

#### **Serial Output Timing**

#### **Operation Timing After Reset**

$^{\ast}$   $\overline{\text{INT}}$  is invalid during the shaded interval.

# **Control Pin Load-in Timing**

# HOW TO USE THE MSM7603/7603B

The MSM7603/7603B cancels, based on the RIN signal, the echo which returns to SIN. Connect the base signal to the R side and the echo-generated signal to the S side.

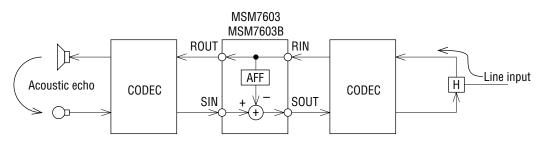

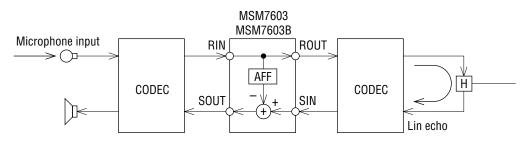

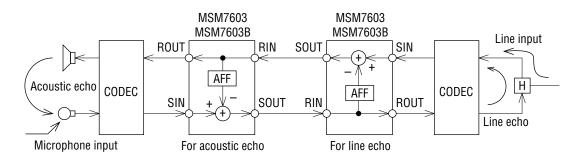

#### **Connection Methods According to Echoes**

Example 1: Canceling acoustic echo (to handle acoustic echo from line input)

Example 2: Canceling line echo (to handle line echo from microphone input)

Example 3: Canceling of both acoustic and line echo (to handle both acoustic echo from line input and line echo from microphone input)

# ECHO CANCELER CHARACTERISTICS DIAGRAM (for μ-law and A-law, and for reference only)

Note: Above characteristics are for the MSM7533 ( $V_{DD}$  5 V,  $\mu$ -law CODEC interface). For the MSM7704 ( $V_{DD}$  3 V,  $\mu$ -law interface) the characteristics are basically the same except for input and output levels. Refer to the PCM CODEC data sheet. MSM7533 (for both transmit and receive) 0 dBm0 = 0.85 Vrms = 0.8 dBm (600  $\Omega$ ) MSM7704 (for transmit side)

$0 \text{ dBm0} = 0.35 \text{ Vrms} = -6.9 \text{ dBm} (600 \Omega)$ (for receive side)

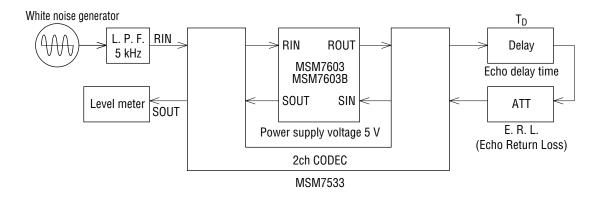

#### Measurement System Block Diagram

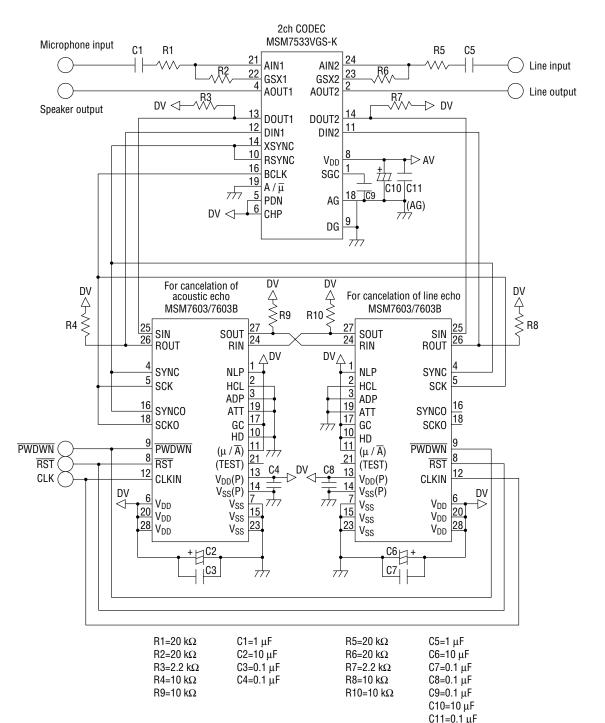

#### APPLICATION CIRCUIT Bidirectional Connection Example

Use the MSM7704-01GS-VK as a PCM CODEC when  $V_{DD}$  3 V is used. The MSM7533 is pin compatible with the MSM7704.

#### NOTES ON USE

- Set echo return loss (ERL) to be attenuated. If the echo return loss is set to be amplified, the echo cannot be eliminated. Refer to the characteristics diagram for E. R. L. vs. echo attenuation quantity.

- 2. Set the level of the analog input so that the PCM codec does not overflow.

- 3. The recommended input level is –10 to –20 dBm0. Refer to the characteristics diagram for the RIN input level vs. echo attenuation quantity.

- 4. Applying the tone signal to this echo canceler for long duration may decrease echo attenuation.

When used with the HD pin "L" (howling detector ON), this echo canceler may operate faultily if, while a signal is input to the RIN pin, a tone signal with a higher level than the signal being input to RIN is input to the SIN pin.

A signal should therefore be input either to the RIN pin or to the SIN pin. If, however, the tone signal is input to the SIN pin while a signal is input to the RIN pin, the ADP, HD, or HCL pin must be set to "H".

For changes in the echo path (retransmit, circuit switching during transmission, and so on), convergence may be difficult.

Perform a reset to make it converge.

If the state of the echo path changes after a reset, convergence may again be difficult.

If the state of the echo path changes after a reset, convergence may again be difficult. In cases such as a change in the echo path, perform a reset each time.

- When turning the power ON, set the PWDWN pin to "1" and input the basic clock simultaneously with power ON.

If the device is put into power down mode immediately after power ON, be sure to input 10 or more clocks of the basic clock before setting to the power down mode.

- 7. After power ON, be sure to reset the device.

- 8. After the power down mode is released (when <u>PWDWN</u> pin is changed to a "1" from a "0"), be sure to reset the device.

- 9. If this canceler is used to cancel acoustic echoes, an echo attenuation may be less than 30 dB.

# **EXPLANATION OF TERMS**

| Attenuating Function :     | This function prevents howling and controls the noise level with<br>the attenuator for the RIN input and SOUT output. Refer to the                                                                                                                                                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | explanation of pins (ATT pin).                                                                                                                                                                                                                                                                                                                         |

| Echo Attenuation :         | If there is talking (input only to RIN) in the path of a rising echo<br>arises, the echo attenuation refers to the difference in the echo<br>return loss (canceled amount) when the echo canceler is not used<br>and when it is used.                                                                                                                  |

|                            | Echo attenuation = (SOUT level during through mode operation)<br>- (SOUT level during echo canceler operation) [dB]                                                                                                                                                                                                                                    |

| Echo Delay Time :          | This is the time from when the signal is output from ROUT until it returns to SIN as an echo.                                                                                                                                                                                                                                                          |

| Acoustic Echo :            | When using a hands-free phone, for example, the signal output<br>from the speaker echoes and is input again to the microphone. The<br>return signal is referred to as acoustic echo.                                                                                                                                                                   |

| Telephone Line Echo :      | This is a signal which is delayed midway in a telephone line and<br>returns as an echo, due to reasons such as a hybrid impedance<br>mismatch.                                                                                                                                                                                                         |

| Gain Control Function :    | This function prevents howling and controls the sound level by with a gain controller for the RIN input. Refer to the explanation of pins (GC pin).                                                                                                                                                                                                    |

| Center Clipping Function : | This function forces the SOUT output to a minimum value when the signal is below –57 dBm0. Refer to the explanation of pins (NLP pin).                                                                                                                                                                                                                 |

| Double Talk Detection :    | Double talk refers to a state in which the SIN and RIN signals are<br>input simultaneously. In a double talk state, a signal other than the<br>echo signal which is to be canceled can be input to the SIN input,<br>resulting in malfunction.                                                                                                         |

| Howling Detection :        | The double talk detector prevents such malfunction of the canceler.<br>This is the oscillating state caused by the acoustic coupling between<br>the loud speaker and the microphone during hands-free talking.<br>Howling not only interferes with talking, but can also cause<br>malfunction of the echo canceler.                                    |

| Echo Return Loss (ERL) :   | The howling detector prevents such malfunction and howling.<br>When the signal output from ROUT returns to SIN as an echo, ERL<br>refers to how much loss there is in the signal level during ROUT.<br>ERL = (ROUT level) – (SIN level of the ROUT signal which returns<br>as an echo) [dB]<br>If ERL is positive (ROUT > SIN), acts as an attenuator. |

|                            | If ERL is negative (ROUT < SIN), acts as an amplifier.                                                                                                                                                                                                                                                                                                 |

| PHS:                       | Personal Handyphone System                                                                                                                                                                                                                                                                                                                             |

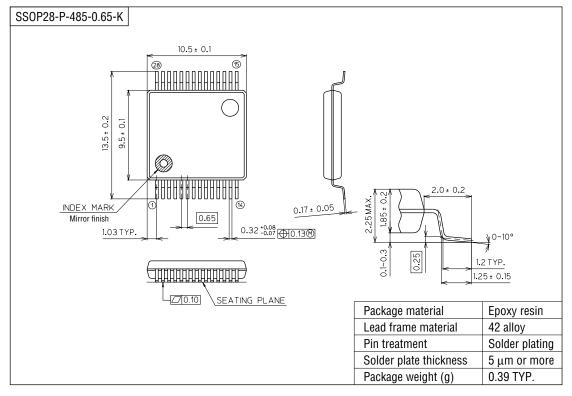

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).