# CMOS ST-BUS<sup>™</sup> Family MT8986 Multiple Rate Digital Switch

Data Sheet

# Features

- 256 x 256 or 512 x 256 switching configurations

- 8-bit or 4-bit channel switching capability

- Guarantees frame integrity for wideband channels

- Automatic identification of ST-BUS/GCI interfaces

- Accepts serial streams with data rates up to 8.192 Mb/s

- Rate conversion from 2.048 Mb/s to 4.096 or 8.192 Mb/s and vice-versa

- Programmable frame offset on inputs

- Per-channel three-state control

- · Per-channel message mode

- Control interface compatible to Intel/Motorola CPUs

- Low power consumption

# Applications

- · Medium size digital switch matrices

- Hyperchannel switching (e.g., ISDN H0)

- MVIP<sup>™</sup> interface functions

- · Serial bus control and monitoring

- · Centralized voice processing systems

- Voice/Data multiplexer

- 32 kbit/s channel switching

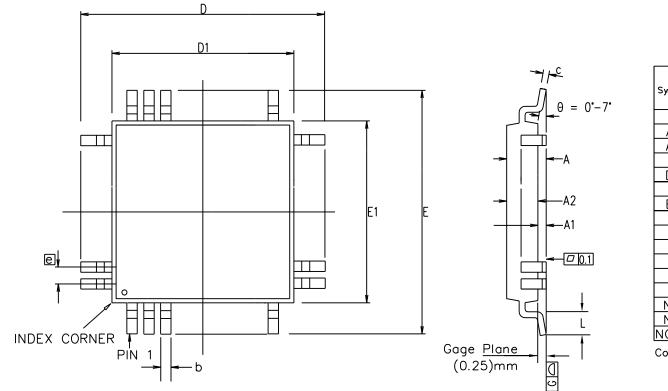

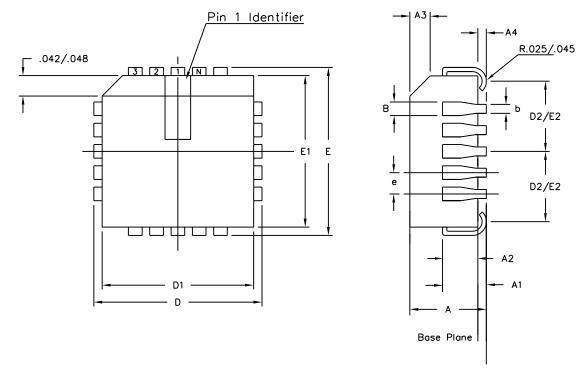

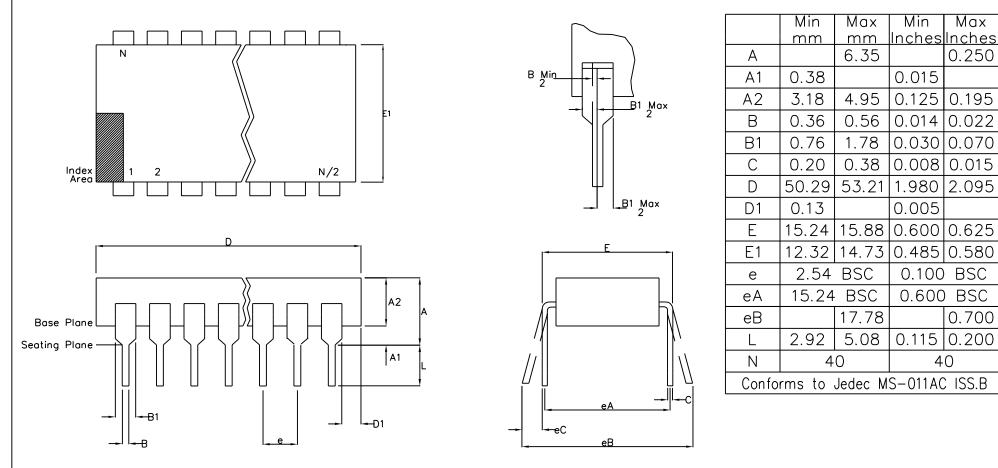

| 0i         | rdering Informat   | lion        |

|------------|--------------------|-------------|

| MT8986AE   | 40 Pin PDIP        | Tubes       |

| MT8986AP   | 44 Pin PLCC        | Tubes       |

| MT8986AL   | 44 Pin MQFP        | Trays       |

| MT8986APR  | 44 Pin PLCC        | Tape & Reel |

| MT8986AP1  | 44 Pin PLCC*       | Tubes       |

| MT8986APR1 | 44 Pin PLCC*       | Tape & Reel |

|            | *Pb Free Matte Tir | 1           |

|            | -40°C to +85°C     |             |

# Description

The Multiple Rate Digital Switch (MRDX) is an upgraded version of Zarlink's MT8980D Digital Switch (DX). It is pin compatible with the MT8980D and retains all of its functionality. This device is designed to provide simultaneous connections (non-blocking) for up to 256 64 kb/s channels or blocking connections for up to 512 64 kb/s channels. The serial inputs and outputs connected to MT8986 may have 32 to 128 64 kb/s channels per frame with data rates ranging from 2048 up to 8192 kb/s. The MT8986 provides per-channel selection between variable and constant throughput delays allowing voice and grouped data channels to be switched without corrupting the data sequence integrity.

In addition, the MT8986 can be used for switching of 32 kb/s channels in ADPCM applications. The MT8986 is ideal for medium size mixed voice and data switching/processing applications.

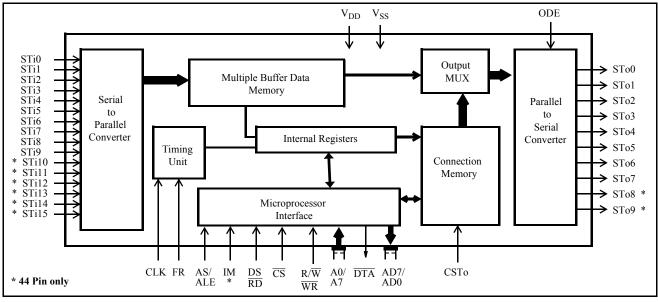

## Figure 1 - Functional Block Diagram

1

February 2005

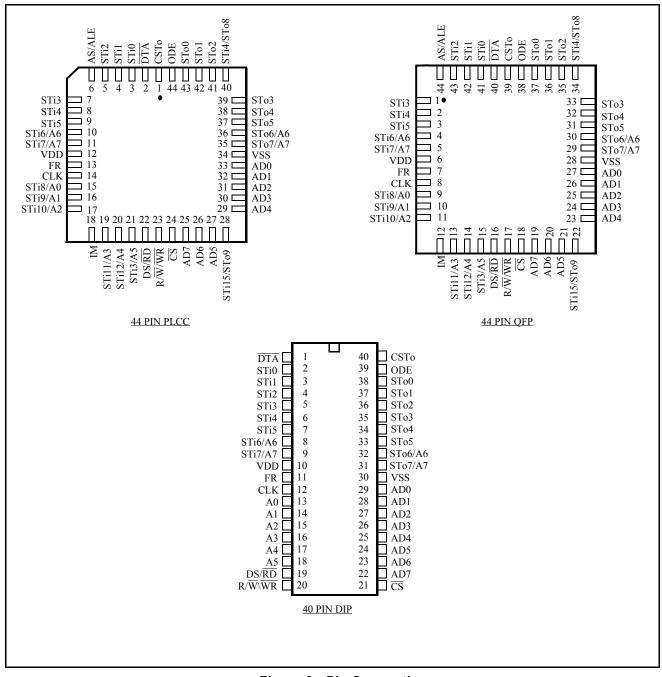

Figure 2 - Pin Connections

# **Pin Description**

|           | Pin #      |              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------|------------|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 40<br>DIP | 44<br>PLCC | 44<br>QFP    | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1         | 2          | 40           | DTA               | <b>Data Acknowledgement</b> (Open Drain Output). This active low output indicates that a data bus transfer is complete. A 10 k $\Omega$ pull-up resistor is required at this output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 2-7       | 3-5<br>7-9 | 41-43<br>1-3 | STi0-5            | <b>ST-BUS Inputs 0 to 5</b> (Inputs). Serial data input streams. These streams may have data rates of 2.048, 4.096 or 8.192 Mbit/s with 32, 64 or 128 channels, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 8         | 10         | 4            | STi6/A6           | <b>ST-BUS Input 6/Addr.6 input</b> (Input). The function of this pin is determined by the switching configuration enabled. If non-multiplexed CPU bus is used along with a higher input rate of 8.192 or 4.096 Mb/s, this pin provides A6 address input function. For 2.048 and 4.096 Mb/s (8x4) applications or when multiplexed CPU bus (44 pin only) is selected, this pin assumes STi6 function. See Control Register bits description and Tables 1, 2, 6 & 7 for more details. Note that for applications where both A6 and STi6 inputs are required simultaneously (e.g., 8 x 4 switching configuration at 4.096 Mb/s) the A6 input should be connected to pin STo6/A6. |  |  |  |  |  |

| 9         | 11         | 5            | STi7/A7           | <b>ST-BUS Input 7/Addr.7 input</b> (Input): The function of this pin is determined by the switching configuration enabled. If non-multiplexed CPU bus is used along with a higher input rate of 8.192 Mb/s, this pin provides A7 address input function.<br>For 2.048 and 4.096 Mb/s (8x4) applications or when multiplexed CPU bus (44 pin only) is selected, this pin assumes STi7 function. See Control Register bits description and Tables 1, 2, 6 & 7 for more details.<br>Note that for applications where both A7 and STi7 inputs are required simultaneously (e.g., 2.048 to 8.192 Mb/s rate conversion) the A7 input should be connected to pin STo7/A7.            |  |  |  |  |  |

| 10        | 12         | 6            | V <sub>DD</sub>   | +5 Volt Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 11        | 13         | 7            | FR                | <b>Frame Pulse</b> (Input). This input accepts and automatically identifies frame synchronization signals formatted according to ST-BUS and GCI interface specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 12        | 14         | 8            | CLK               | <b>Clock</b> (Input). Serial clock for shifting data in/out on the serial streams.<br>Depending on the serial interface speed selected by IMS (Interface Mode Select) register, the clock at this pin can be 4.096 or 8.192 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 13-15     | 15-17      | 9-11         | A0-2/<br>STi8-10  | Address 0-2 / Input Streams 8-10 (Input). When non-multiplexed CPU bus is selected, these lines provide the A0-A2 address lines to MT8986 internal registers. When 16x8 switching configuration is selected (in 44 pin only), then these pins are ST-BUS serial inputs 8 to 10 receiving data at 2.048 Mb/s.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 16-18     | 19-21      | 13-15        | A3-5/<br>STi11-13 | Address 3-5 / Input Streams 11-13 (Input). When non-multiplexed CPU bus is selected, these lines provide the A3-A5 address lines to MT8986 internal registers. When 16x8 switching configuration is selected (in 44 pin only), then these pins are ST-BUS serial inputs 11 to 13 receiving data at 2.048 Mb/s.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

# Pin Description (continued)

|           | Pin #          |                |                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------|----------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 40<br>DIP | 44<br>PLCC     | 44<br>QFP      | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 19        | 22             | 16             | DS/RD           | <b>Data Strobe/Read</b> (Input). When non-multiplexed CPU bus or Motorola multiplexed bus (44 pin only) are selected, this input is DS. This active high input works in conjunction with CS to enable read and write operation. For Intel/National multiplexed bus (44 pin only), this input is RD. This active low input configures the data bus lines (AD0-AD7) as outputs.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 20        | 23             | 17             | R/W\WR          | <b>Read/Write</b> \ <b>Write</b> (Input). In case of non-multiplexed and Motorola multiplexed buses (44 pin only), this input is R/W. This input controls the direction of the data bus lines (AD0-AD7) during a microprocessor access.<br>With Intel/National multiplexed timing (44 pin only), this input is WR. This active low signal configures the data bus lines (AD0-AD7) as inputs.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 21        | 24             | 18             | CS              | <b>Chip Select</b> (Input). Active low input enabling a microprocessor read or write of the control register or internal memories.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 22-29     | 25-27<br>29-33 | 19-21<br>23-27 | AD7-<br>AD0     | <b>Data Bus</b> (Bidirectional): These pins provide microprocessor access to the internal control registers, connection memories high and low and data memories. In multiplexed bus mode (44 pin) these pins also provide the input address to the internal Address Latch circuit.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 30        | 34             | 28             | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 31        | 35             | 29             | STo7/A7         | <b>ST-BUS Output 7/Address 7 input</b> (Three-state output/input). The function of this pin is determined by the switching configuration enabled. If non-multiplexed CPU bus is used along with data rates employing 8.192 Mb/s rates, this pin provides A7 address input function. For 2.048 Mb/s applications or when multiplexed CPU bus (44 pin only) is selected, this pin assumes STo7 function. See Tables 1, 2, 6 & 7 for more details.                                                                                                                                                                                                                                             |  |  |  |  |  |

|           |                |                |                 | Note that for applications where A7 input and STo7 output are required simultaneously (e.g., 8.192 to 2.048 Mb/s rate conversion), the A7 input should be connected to pin STi7/A7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 32        | 36             | 30             | STo6/A6         | <b>ST-BUS Output 6/Address 6 input</b> (Three-state output/input). The function of this pin is determined by the switching configuration enabled. If non-multiplexed CPU bus is used along with a higher data rate employing 8.192 or 4.096 Mb/s, this pin provides the A6 address input function. For 2.048 Mb/s applications or when multiplexed CPU bus (44 pin only) is selected, this pin assumes STo6 function. See Tables 1, 2, 6 & 7 for more details. Note that for applications where both A6 input and STo6 output are required simultaneously (e.g., 4.096 to 2.048 Mb/s or 8.192 to 2.048 Mb/s rate conversion applications), the A6 input should be connected to pin STi6/A6. |  |  |  |  |  |

| 33-38     | 37-39<br>41-43 | 31-33<br>35-37 | STo5-0          | <b>ST-BUS Outputs 5 to 0</b> (Three-state Outputs). Serial data output streams.<br>These serial streams may be composed of 32, 64 and 128 channels at data rates of 2.048, 4.096 or 8.192 Mbit/s, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

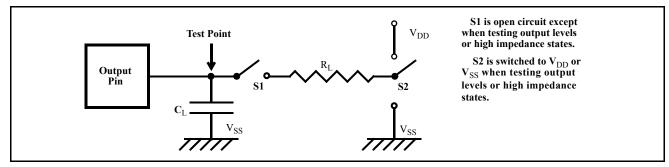

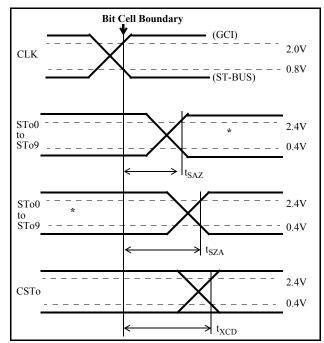

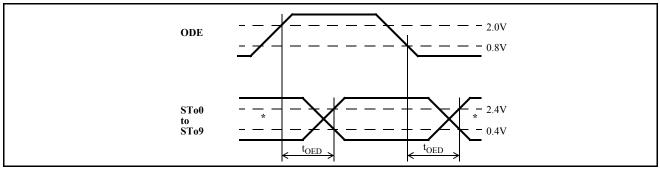

| 39        | 44             | 38             | ODE             | <b>Output Drive Enable</b> (Input). This is the output enable input for the STo0 to STo9 serial outputs. If this input is low STo0-9 are high impedance. If this input is high each channel may still be put into high impedance by using per-channel control bits in Connect Memory High.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

# **Pin Description (continued)**

|           | Pin #      |           |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------|------------|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 40<br>DIP | 44<br>PLCC | 44<br>QFP | Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 40        | 1          | 39        | CSTo           | <b>Control ST-BUS Output</b> (Output). This is a 2.048 Mb/s output containing 256 bits per frame. The level of each bit is determined by the CSTo bit in the Connect Memory high locations.                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| -         | 6          | 44        | AS/ALE         | Address Strobe or Latch Enable (Input). This input is only used if multiplexed<br>bus is selected via the IM input pin (44 pin only).<br>The falling edge of this signal is used to sample the address into the address<br>latch circuit. In case of non-multiplexed bus, this input is not required and should<br>be left open.                                                                                                                                                                                            |  |  |  |

| -         | 18         | 12        | IM             | <b>CPU Interface Mode</b> (Input). If HIGH, this input configures MT8986 in multiplexed microprocessor bus mode. If this input pin is not connected or grounded, the MT8986 assumes non-multiplexed CPU interface.                                                                                                                                                                                                                                                                                                          |  |  |  |

| -         | 28         | 22        | STi15/<br>STo9 | <b>ST-BUS Input 15 / ST-BUS Output 9</b> (Input/three-state output). This pin is only used if multiplexed CPU bus is selected. If 16-input x 8-output switching configuration is enabled in the SCB bits (IMS register), this pin is an input receiving serial ST-BUS stream 15 at a data rate of 2.048 Mbit/s. If Stream Pair Selection capability is enabled (see switching configuration section), this pin is the ST-BUS stream 9 output. When non-multiplexed bus structure is used, this pin should be left open.     |  |  |  |

| -         | 40         | 34        | STi14/<br>STo8 | <b>ST-BUS Input 14 / ST-BUS Output 8</b> (Input/three-state output). This pin is only used if multiplexed CPU bus is selected. If 16-input x 8-output switching configuration is enabled in the SCB bits (IMS register), this pin is an input that receives serial ST-BUS stream 14 at a data rate of 2.048 Mbit/s. If Stream Pair Selection capability is enabled (see switching configuration section), this pin is the ST-BUS stream 8 output. When non-multiplexed bus structure is used, this pin should be left open. |  |  |  |

# **Device Overview**

With the integration of voice, video and data services in the same network, there has been an increasing demand for systems which ensure that data at N x 64 kbit/s rates maintain sequence integrity while being transported through time-slot interchange circuits. This requirement demands time-slot interchange devices which perform switching with constant throughput delay for wideband data applications while guaranteeing minimum delay for voice channels.

The MT8986 device meets the above requirement and allows existing systems based on the MT8980D to be easily upgraded to maintain the data integrity when wideband data is transported. The device is designed to switch 32, 64 or N x 64 kbit/s data. The MT8986 can provide frame integrity for data applications and minimum throughput switching delay for voice applications on a per channel basis.

The serial streams of the MT8986 device can operate at 2.048, 4.096 or 8.192 Mbit/s and are arranged in 125  $\mu$ s wide frames which contain 32, 64 and 128 channels, respectively. In addition, a built-in rate conversion circuit allows the user to interconnect various backplane speeds like 2.048 or 4.096 or 8.192 Mb/s while maintaining the control of throughput delay function on a per-channel basis.

By using Zarlink Message mode capability, the microprocessor can access input and output time-slots on a per channel basis to control external circuits or other ST-BUS devices. The MT8986 automatically identifies the polarity

of the frame synchronization input signal and configures its serial port to be compatible to both ST-BUS and GCI formats.

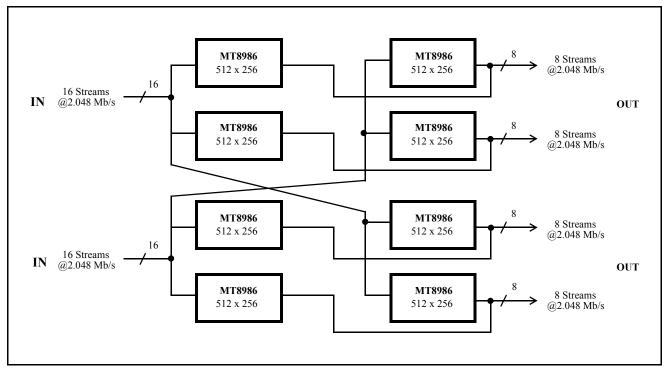

In the 44 pin packages, two different microprocessor bus interfaces can be selected through an input mode pin (IM): Non-Multiplexed or Multiplexed. These interfaces provide compatibility with Intel/National multiplexed and Motorola Multiplexed/Non-Multiplexed buses. In 44 pin, the MT8986 provides a 16 x 8 switching configuration to form a 512 x 256 channel blocking matrix. Also, a flexible Stream Pair Selection operation allows the software selection of which pair of input and output streams can be connected to an internal 128 x 128 matrix. See Switching Configurations section for details.

# **Functional Description**

A functional Block Diagram of the MT8986 device is shown in Figure 1. Depending on the application, the MT8986 device receives TDM serial data at different rates and from different number of serial streams.

# Data and Connect Memories

For all data rates, the received serial data is converted to parallel format by the serial to parallel converters and stored sequentially in a Data Memory. Depending on the selected operation programmed in the IMS (Interface Mode Select) register, the Data Memory may have up to 512 bytes in use. The sequential addressing of the Data Memory is performed by an internal counter which is reset by the input 8 kHz frame pulse (FR) marking the frame boundaries of the incoming serial data streams.

Data to be output on the serial streams may come from two sources: Data Memory or Connect Memory. Locations in the Connect Memory, which is split into HIGH and LOW parts, are associated with particular ST-BUS output streams. When a channel is due to be transmitted on an ST-BUS output, the data for the channel can either be switched from an ST-BUS input as in connection mode or it can be from the Connect Memory Low as in message mode. Data destined for a particular channel on the serial output stream is read from the Data Memory or Connect Memory Low during the previous channel time-slot. This allows enough time for memory access and parallel to serial conversion.

## **Connection and Message Modes**

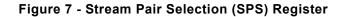

In connection mode, the addresses of the input source data for all output channels are stored in the Connect memories High (CMH) and Low (CML). The CML and CMH are mapped so that each location corresponds to an output channel on the output streams. The number of source address bits in CMH and CML to be utilized varies according to the switching configuration selected in the IMS register. For details on the use of the source address bits are programmed by the CPU, the contents of the Data Memory at the selected address are transferred to the parallel-to-serial converters. By having the output channel specify the source channel through the connect memory, the user can route the same input channel to several output channels, allowing broadcast facility within the switch.

In message mode the CPU writes data to the Connect Memory Low locations corresponding to the output link and channel number. The contents of the Connect Memory Low are transferred directly to the parallel-to-serial converter one channel before it is to be output. The Connect Memory Low data is transmitted on to the output every frame until it is changed by the CPU with a new data.

The features of each output channel in the MT8986 are controlled by the Connect Memory High bits. These bits determine individual output channels to be in message or connection mode, select throughput delay types and enable/disable output drivers. The Connect Memory High also provides additional stream and channel address bits for some configurations. In addition, the Connect Memory High provides one bit to allow the user to control the CSTo output in 2.048 Mb/s applications.

If an output channel is set to high-impedance, the TDM serial stream output will be placed in high impedance during that channel time. In addition to the per-channel control, all channels on the TDM outputs can be placed in high impedance by pulling the ODE input pin LOW. This overrides the individual per-channel programming by the Connect Memory High bits.

The Connect Memory data is received via the Microprocessor Interface through the data I/O lines. The addressing of the MT8986 internal registers, Data and Connect memories is performed through address input pins and some bits of the device's Control register. The higher order address bits come from the Control register, which may be written or read through the microprocessor interface. The lower order address bits come directly from address input pins. For details on the device addressing, see Software Control and Control register bits description (Figure 3 & Tables 5, 6 and 7).

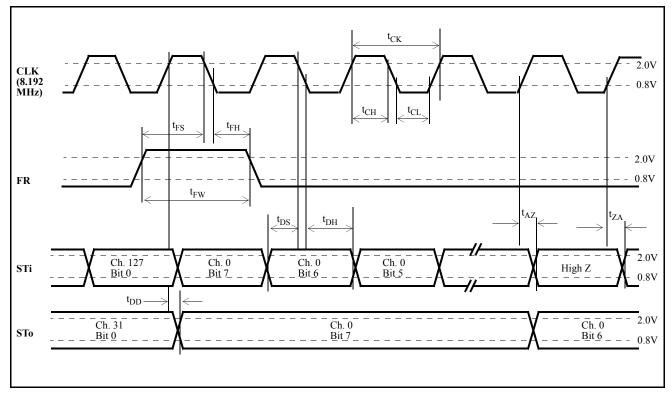

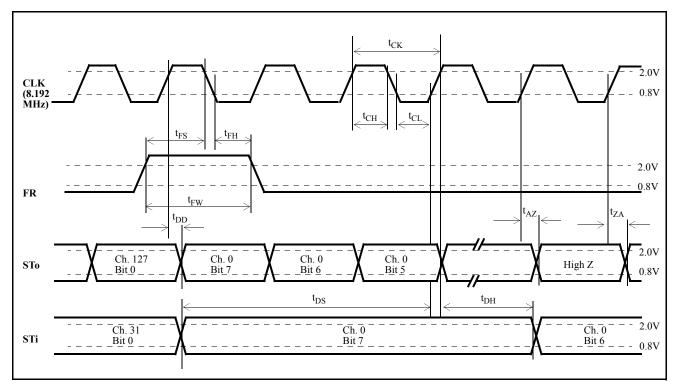

# Serial Data Interface

The master clock (CLK) can be either at 4.096 or 8.192 MHz allowing serial data link operations at 2.048, 4.096 and 8.192 Mb/s. These data rates can be independently selected on input and output streams allowing the MT8986 device to be used in various speed backplanes and in rate conversion applications. The selected data rates apply to the inputs or the output streams. Different bit rates among input streams or among output streams are not allowed. Due to the I/O data rate selection flexibility, two major operations can be selected: Identical or Different I/O data rates.

The DMO bit (Device Main Operation) in the IMS register is used for selecting between Identical I/O rates or Different I/O rates. On system power-up, the CPU should set up the DMO, the IDR (Input Data Rate) and ODR (Output Data Rate) bits located in the IMS register. When Identical I/O data rates are selected by the DMO bit, the switching configuration and the number of the device's input and output streams can be selected through the SCB bits (Switching Configuration Bits) in the IMS register. See Switching Configurations section for details.

Depending on the application, the interface clock can be selected to be twice the data rate or equal to the data rate. This selection is performed through bit CLKM in the IMS register. For applications where both serial inputs and outputs are at 2.048 Mb/s (ST-BUS or GCI format), the CLKM bit should be set LOW enabling the interface clock to be twice the bit rate. In applications where both inputs and outputs are at 4.096 or 8.192 Mb/s, CLKM should be set HIGH enabling the interface clock to be equal to the bit rate. In applications where inputs are at different rates, the CLKM bit has no effect.

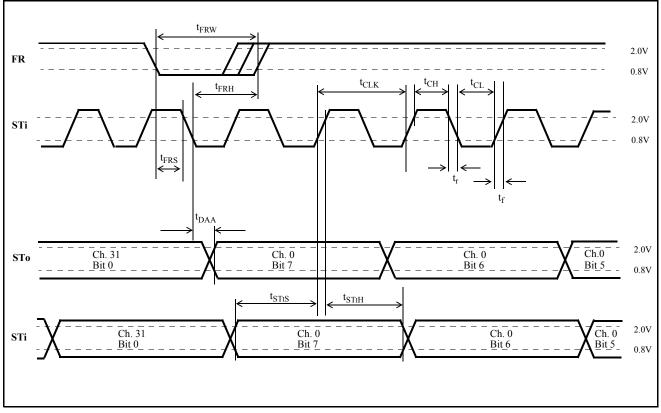

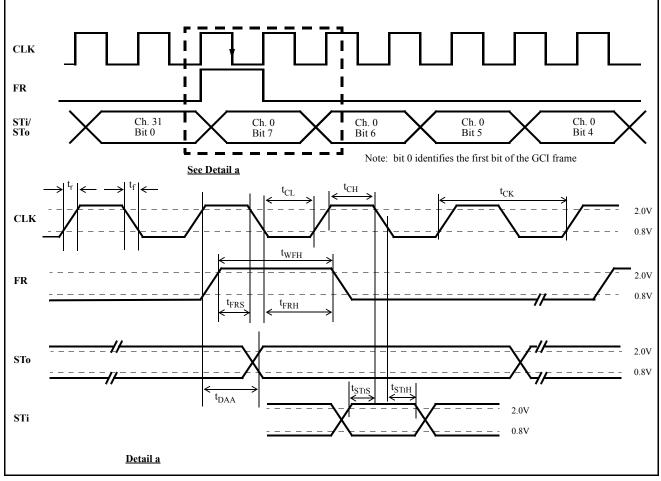

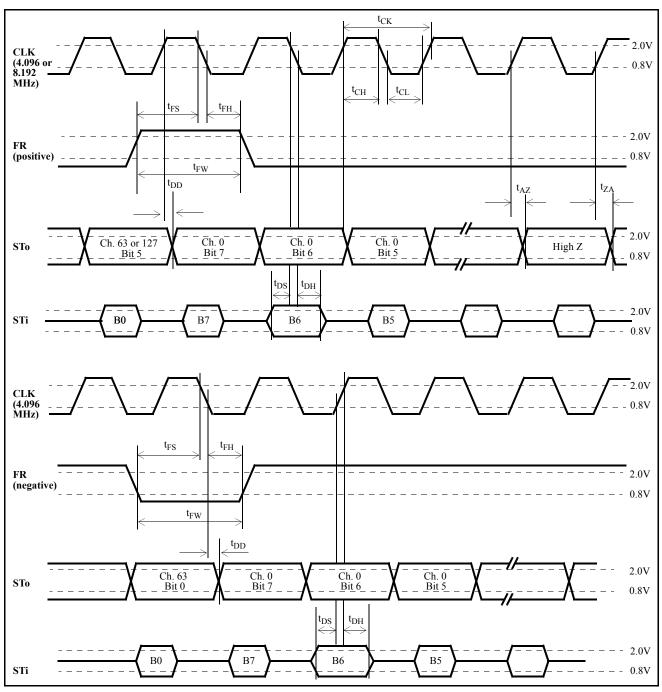

In applications with serial links at 2.048 Mb/s (see Figures 16 to 19), the input 8 kHz frame pulse can be in either ST-BUS or GCI format. The MT8986 device automatically detects the presence of an input frame pulse and identifies what type of backplane is present on the serial interface. Upon determining the interface connected to the serial port, the internal timing unit establishes the appropriate transmit and sampling edges. In ST-BUS format, every second falling edge of the 4.096 MHz clock marks a bit boundary and the input data is clocked in by the rising edge, three quarters of the way into the bit cell. In GCI format, every second rising edge of the 4.096 MHz clock marks the bit boundary while data sampling is performed during the falling edge, at three quarters of the bit boundaries.

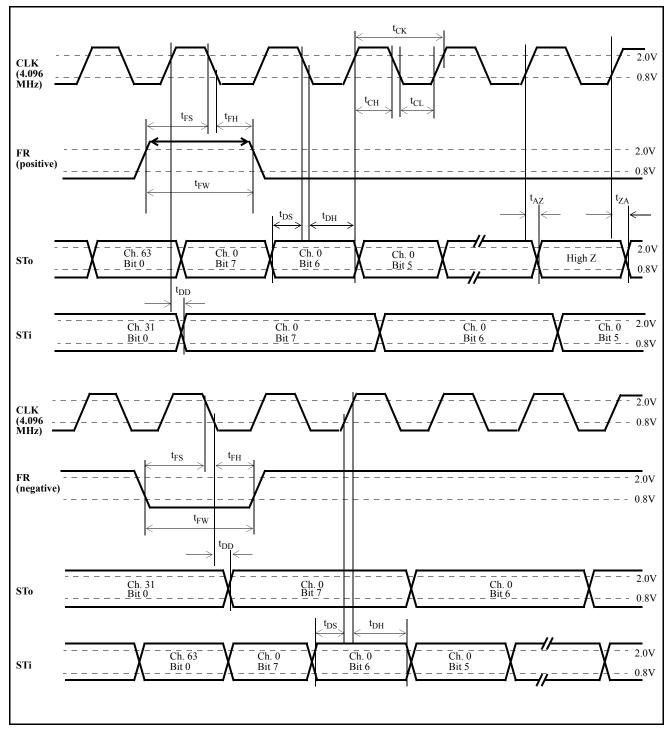

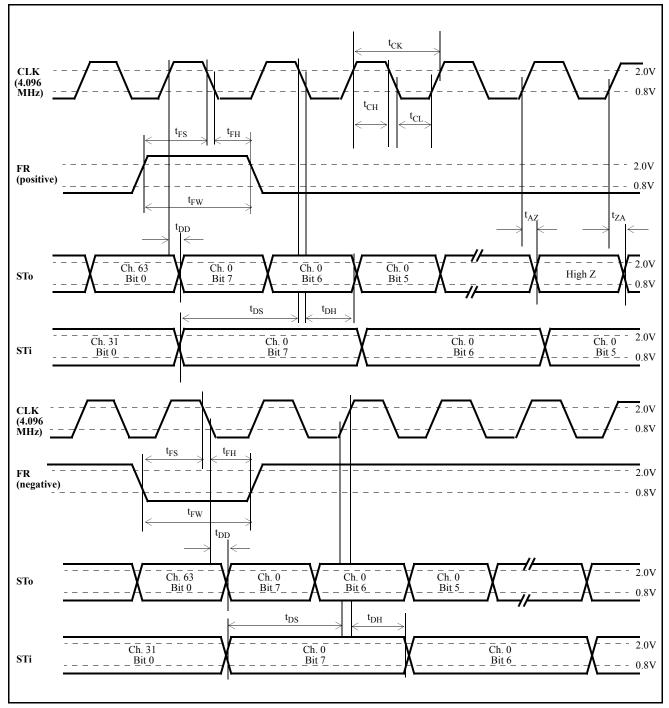

For identical I/O rates at 4.096 and 8.192 Mb/s (see Figure 20), the clock and interface data rates are equal. The bit transmit and sampling edges vary according to the applied frame pulse polarity. For example, if the FR pulse polarity is positive, the bit transmit operation is done on every rising edge of CLK and the bit sampling on every falling edge. If the FR pulse polarity is negative, these edges are inverted. For different I/O rates, the MT8986 side operating at 2.048 Mb/s data rate will comply with ST-BUS or GCI interfaces for transmit and sampling procedures. The MT8986 side operating at 4.096 or 8.192 Mb/s behaves according to the frame pulse polarity applied. See Figures 22 to 25.

# Switching Configurations

Switching configurations are determined basically by the interface rates selected at the serial inputs and outputs. To specify the switching configuration required, the IMS register has to be initialized on system power-up. In case of Identical I/O rates (DMO bit LOW) at both inputs and outputs, the switching configuration is selected by the two SCB bits as shown in Table 8 (see IMS register). In case of different I/O rates (DMO bit HIGH), the switching configuration is always non-blocking with different number of I/O streams which is defined by the IDR and ODR bits (see IMS register).

## Identical Input/Output Data Rates

When identical input/output data rate is selected by the DMO bit, the I/O rate is determined by the IDR0-1 bits, and the ODR0-1 bits are ignored. For each data rate specified by the IDR bits, different switching configurations can be selected in the SCB1-0 bits.

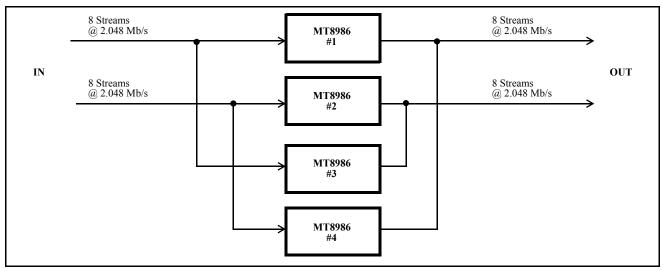

### Serial Links with Data Rates at 2.048 Mb/s

When 2.048 Mb/s data rate is selected at the IDR bits, four different I/O configurations can be selected by the SCB1-0 bits (see Table 8);  $8 \times 8$ ,  $16 \times 8$ ,  $4 \times 4$  with stream pair selection and nibble switching.

If 8 x 8 switching configuration is selected, a 256 x 256 channel non-blocking switching matrix is available. In this configuration, the MT8986 device is configured with 8 input and 8 output data streams with 32 64 Kbit/s channels each. The interface clock for this operation is 4.096 MHz with both ST-BUS and GCI compatibilities and the perchannel selection between variable and constant throughput delay functions is provided. This configuration is available in both the 40 and 44 pin packages.

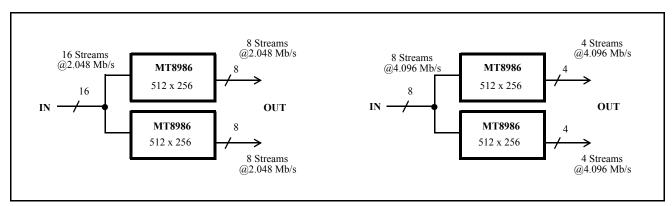

In 16 x 8 switching configuration, a 512 x 256 channel blocking switch matrix is available. This configuration is only provided in the 44 pin package and when the CPU interface is configured in multiplexed bus mode. The device clock in this application is 4.096 MHz, ST-BUS or GCI compatible. This configuration only provides variable throughput delay.

If the stream pair selection switching configuration is selected, only four input and four outputs (4 pairs of serial streams) can be selected by the CPU to be internally connected to the switch matrix, totalling a 128 x 128 channel non-blocking switch. From the 10 serial link pairs available, two pairs are permanently connected to the internal matrix (STi0/STo0 and STi1/STo1). An internal stream pair selection capability allows two additional pairs of serial links to be selected from the remaining 8 pairs (from STi/STo2 to STi9/STo9) and be connected to the internal matrix along with the permanently connected STi0/STo0 and STi1/STo1 streams. The two additional pair of streams called stream pair A and stream pair B, should be selected in the Stream Pair Selection register (SPS). The device clock for this operation is 4.096 MHz compatible to ST-BUS and GCI interfaces. In addition, the per-channel selection between variable or constant throughput delay is available. This configuration is only provided in the 44 pin packages.

In case of nibble switching, 4-bit wide 32 kb/s data channels can be switched within the device. In this case, every serial stream is run at 2.048 Mb/s and transports 64 nibbles per frame. When Nibble Switching is selected at SCB bits, the MT8986 automatically assumes a 8 input x 4 output stream configuration, providing a blocking switch matrix of 512 x 256 nibbles. If a non-blocking switch matrix is required for nibble switching, the switch capacity is reduced to 256 x 256 channel with a 4 input x 4 output configuration; the non-blocking matrix can be arranged by the user by selecting any four of the 8 input streams. In nibble switching the interface clock is 4.096 MHz.

### Serial Links with Data Rates at 4.096 Mb/s

Two I/O configurations can be enabled by the SCB bits when input and output data rates are 4.096 Mb/s on each serial stream: 8 x 4 and 4 x 4. When 8 x 4 switching configuration is selected, a 512 x 256 channel blocking switch is available with serial streams carrying 64, 64 Kb/s channels each. For this operation, a 4.096 MHz interface clock equal to the bit rate should be provided to MT8986. Only variable throughput delay mode is provided.

In case of 4 x 4 switching configuration, a 256 x 256 channel non-blocking switch is available with serial streams carrying 64, 64 Kb/s channels each. In this configuration, the interface clock is 4.096 MHz and the per-channel selection between variable and constant throughput delay operation is provided. Figure 20 shows the timing for 4.096 Mb/s operation.

### Serial Links with Data Rates at 8.192 Mb/s

Only 2 input x 2 output stream configuration is available for 8.192 Mb/s, allowing a 256 x 256 channel non-blocking switch matrix to be implemented. To enable this operation, the IDR bits should be programmed to select 8.192 Mb/s rates and the SCB bits have no effect. At 8.192 Mb/s, every input and output stream provides 128 time-slots per

frame. The interface clock for this operation should be 8.192 MHz. Figure 20 shows the timing for 8.192 Mb/s operation.

| Serial<br>Interface<br>Data Rate | Interface<br>Clock<br>required at<br>CLK Pin<br>(MHz) | Number of<br>Input x<br>Output<br>Streams | Matrix<br>Channel<br>Capacity                                        | Input/Output<br>Streams Used | Variable/<br>Constant<br>throughput<br>Delay<br>Selection |

|----------------------------------|-------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|------------------------------|-----------------------------------------------------------|

| 2 Mb/s                           | 4.096                                                 | 8x8                                       | 256x256 Non-Blocking                                                 | STi0-7/STo0-7                | Yes                                                       |

| 2 Mb/s<br>*                      | 4.096                                                 | 16x8<br>*                                 | 512x256 Blocking                                                     | STi0-15/STo0-7               | No                                                        |

| 2 Mb/s<br>*                      | 4.096                                                 | 10x10<br>*                                | 128x128 Non-Blocking<br>(only 4 input x 4-output<br>can be selected) | STi0-9/STo0-9                | Yes                                                       |

| Nibble<br>Switching<br>(2 Mb/s)  | 4.096                                                 | 8x4                                       | 512x256 Nibbles                                                      | STi0-7/STo0-3                | No                                                        |

| 4 Mb/s                           | 4.096                                                 | 8x4                                       | 512x256 Blocking                                                     | STi0-7/STo0-3                | No                                                        |

| 4 Mb/s                           | 4.096                                                 | 4x4                                       | 256x256 Non-Blocking                                                 | STi0-3/STo0-3                | Yes                                                       |

| 8 Mb/s                           | 8.192                                                 | 2x2                                       | 256x256 Non-Blocking                                                 | STi0-1/STo0-1                | Yes                                                       |

Table 1 summarizes the MT8986 switching configurations for identical I/O data rates.

\* - only in the 44 pin packages

## Different Input/Output Data Rates

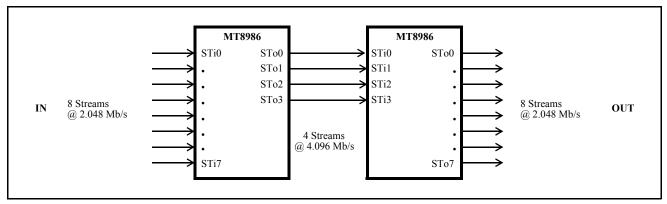

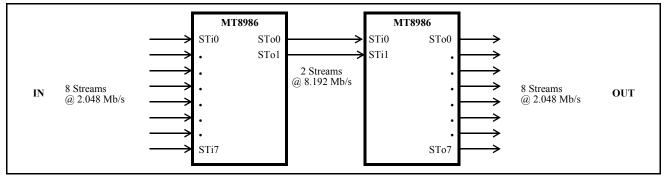

When Different I/O rate is selected by the DMO bit, the input and output data rates should be selected at the IDR and ODR bits, respectively. The Switching Configuration Bits (SCB) are ignored with this operation. This selection allows the user to multiplex conventional 2.048 Mb/s serial streams into two higher rates and vice-versa. In addition to the rate conversion itself, the MT8986 allows for a complete 256 x 256 channel non-blocking switch at different rates. In this operation, the per-channel variable/constant throughput delay selection is provided.

Depending on which data rates are programmed for input and output streams, the number of data streams used on the input and output as well as the serial interface clock (CLK input pin) is different. Once the CPU defines the data rates at the IDR and ODR bits, the MT8986 automatically configures itself with the appropriate number of input and output streams for the desired operation. Table 2 summarizes the four options available when MT8986 is used with different I/O rates. Figures 22 to 25 show the timing for each of the four modes shown in Table 2.

| Input and Output<br>Data Rates | Interface<br>Clock<br>required at<br>CLK Pin<br>(MHz) | Number<br>of Input<br>x Output<br>Streams | Matrix<br>Channel Capacity | Input/Output<br>Streams Used | Variable/<br>Constant<br>throughput<br>Delay Selection |

|--------------------------------|-------------------------------------------------------|-------------------------------------------|----------------------------|------------------------------|--------------------------------------------------------|

| 2 Mb/s to 4 Mb/s               | 4.096                                                 | 8x4                                       | 256x256 Non-Blocking       | STi0-7/STo0-3                | Yes                                                    |

| 2 Mb/s to 8 Mb/s               | 8.192                                                 | 8x2                                       | 256x256 Non-Blocking       | STi0-7/STo0-1                | Yes                                                    |

| 4 Mb/s to 2 Mb/s               | 4.096                                                 | 4x8                                       | 256x256 Non-Blocking       | STi0-3/STo0-7                | Yes                                                    |

| 8 Mb/s to 2 Mb/s               | 8.192                                                 | 2x8                                       | 256x256 Non-Blocking       | STi0-1/STo0-7                | Yes                                                    |

### Table 2 - Switching Configurations for Different I/O Data Rates

## Input Frame Offset Selection

When 4.096 or 8.192 Mb/s serial interfaces are selected, the MT8986 device provides a feature called Input Frame Offset allowing the user to compensate for the varying delays at the incoming serial inputs while building large

Table 1 - Switching Configurations for Identical Input and Output Data Rates

switch matrices. Usually, different delays occur on the digital backplanes causing the data and frame synchronization signals to be skewed at the input of the switch device. This may result in the system frame synchronization pulse to be active at the MT8986 FR input before the first bit of the frame is received at the serial inputs.

When the input frame offset is enabled, an "internal delay" of up to four clock periods is added to the actual data input sampling, providing the MT8986 serial timing unit a new input frame reference. An internal virtual frame is created which is aligned with the framing of the actual serial data coming in at the serial inputs and not with the FR frame pulse input. In this operation, the transmission of the output frame on the serial links is still aligned to the frame pulse input signal (FR).

The selection of the data input sampling delay is defined by the CPU in the Frame Input Offset Register (FIO). If this function is not required in the user's applications, the FIO register should be set up during system initialization to a state where offset functions are disabled.

# **Delay Through the MT8986**

The switching of information from the input serial streams to the output serial streams results in a delay. Depending on the type of information to be switched, the MT8986 device can be programmed to perform time-slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, variable throughput delay can be selected ensuring minimum delay between input and output data. In wideband data applications, constant throughput delay can be selected maintaining the frame integrity of the information through the switch.

The delay through the MT8986 device varies according to the type of throughput delay selected in the  $\overline{V}/C$  bit of the connect memory high.

# Variable Throughput Delay Mode ( $\overline{V}/C$ bit = 0)

# Identical I/O Data Rates

The delay in this mode is dependent on the combination of source and destination channels and it is independent of the input and output streams. The minimum delay achievable in the MT8986 depends on the data rate selected for the serial streams. For instance, for 2.048 Mb/s the minimum delay achieved corresponds to three time-slots. For 4.096 Mb/s it corresponds to five time-slots while for 8.192 Mb/s it is nine time-slots. Switching configurations with input and output channels that provides more than its corresponding minimum throughput delay, will have a throughput delay equal to the difference between the output and input channels; i.e., the throughput delay will be less than one frame period. Table 3a shows the MT8986 throughput delay for each data rate operation.

| Input Rate | Output Channel (# m) |                |              |              |          |  |  |  |  |  |

|------------|----------------------|----------------|--------------|--------------|----------|--|--|--|--|--|

| input Kate | m < n                | m=n, n+1, n+2  | m= n+3, n+4  | m=n+5, n+8   | m > n+8  |  |  |  |  |  |

| 2.048 Mb/s | 32-(n-m) t.s.        | m-n + 32 t.s.  | m-n t.s.     | m-n t.s.     | m-n t.s. |  |  |  |  |  |

| 4.096 Mb/s | 64-(n-m) t.s.        | m-n + 64 t.s.  | m-n+64 t.s.  | m-n t.s.     | m-n t.s. |  |  |  |  |  |

| 8.192 Mb/s | 128-(n-m) t.s.       | m-n + 128 t.s. | m-n+128 t.s. | m-n+128 t.s. | m-n t.s. |  |  |  |  |  |

Table 3a - Variable Throughput Delay Values for Identical I/O Rate Applications

n= input channel, t.s. = time-slot

# **Different I/O Data Rates**

Except for 2 Mb/s to 4 Mb/s and 2 Mb/s to 8 Mb/s rate conversion operations, the throughput delay in the MT8986 may vary according to the output stream used for switching.

Table 3b explains the worst case conditions for the throughput delay when different I/O data rate switching configurations are used.

| I/O Data Rate    | Output Stream Used                                  |                                                                                           |                                                                                           |                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Configuration    | 0, 1                                                | 2, 3                                                                                      | 4, 5                                                                                      | 6, 7                                                                                      |  |  |  |  |  |

| 2 Mb/s to 4 Mb/s | dmin=5x 4Mb/s t.s.<br>dmax=1 fr.+(4x 4Mb/s t.s.)    |                                                                                           | •                                                                                         | •                                                                                         |  |  |  |  |  |

| 2 Mb/s to 8 Mb/s | dmin=9x 8Mb/s t.s.<br>dmax=1 fr.+(8x 8Mb/s t.s.)    |                                                                                           |                                                                                           |                                                                                           |  |  |  |  |  |

| 4 Mb/s to 2 Mb/s | dmin=3x 2Mb/s t.s.<br>dmax=1 fr.+(2x 2Mb/s t.s.)    |                                                                                           | dmin=(2x 2Mb/s t.s.)+(1x 4<br>dmax=1 fr.+(1x 2Mb/s t.s.)                                  | · · · · · · · · · · · · · · · · · · ·                                                     |  |  |  |  |  |

| 8 Mb/s to 2 Mb/s | dmin=3x 2Mb/s t.s.<br>dmax=1 fr.+(2x 2Mb/s<br>t.s.) | dmin=(2x 2Mb/s t.s.)+<br>(3x 8Mb/s t.s.)<br>dmax=1 fr.+(1x 2Mb/s<br>t.s.)+(3x 8Mb/s t.s.) | dmin=(2x 2Mb/s t.s.)+<br>(2x 8Mb/s t.s.)<br>dmax=1 fr.+(1x 2Mb/s<br>t.s.)+(2x 8Mb/s t.s.) | dmin=(2x 2Mb/s t.s.)+<br>(1x 8Mb/s t.s.)<br>dmax=1 fr.+(1x 2Mb/s<br>t.s.)+(1x 8Mb/s t.s.) |  |  |  |  |  |

Table 3b - Min/Max Throughput Delay Values for Different I/O Rate Applications

Notes: dmin and dmax are measured in time-slots and at the point in time when the output channel is completely shifted out. t.s. = time-slot fr. = 125 μs frame 2 Mb/s t.s. = 3.9 μs 4 Mb/s t.s. = 1.95 μs

$8 \text{ Mb/s t.s.} = 0.975 \text{ }\mu\text{s}$

# Constant Throughput Delay mode ( $\overline{V}/C$ bit = 1)

In this mode frame sequence integrity is maintained in both Identical and Different I/O Data Rate operations by making use of a multiple Data-Memory buffer technique. The input channels written in any of the buffers during frame N will be read out during frame N+2. In applications at 2.048 Mb/s for instance, the minimum throughput delay achievable in constant delay mode will be 32 time-slots; for example, when input time-slot 32 (channel 31) is switched to output time-slot 1 (channel 0). Likewise, the maximum delay is achieved when the first time slot in a frame (channel 0) is switched to the last time-slot in the frame (channel 31), resulting in 94 time-slots of delay.

To summarize, any input time-slot from input frame N will always be switched to the destination time-slot on output frame N+2. Table 4 describes the MT8986 constant throughput delay values for different data rates.

| Data Rate  | Throughput Delay (d)                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.048 Mb/s | d=[32 + (32 - IN) + (OUT - 1)]; (expressed in # time-slots)<br>2.048 Mb/s time-slot: 3.9 $\mu$ s<br>IN: input time-slot (from 1 to 32)<br>OUT: output time-slot (from 1 to 32)  |

| 4.096 Mb/s | $d=[64 + (64 - IN) + (OUT - 1)]; (expressed in # time-slots)$ 4.096 Mb/s time-slot: 1.95 $\mu$ s IN: input time-slot (from 1 to 64) OUT: output time-slot (from 1 to 64)        |

| 8.192 Mb/s | d=[128 + (128 - IN) + (OUT - 1)]; (expressed in # time-slots)<br>8.192 Mb/s time-slot: 0.975 μs<br>IN: input time-slot (from 1 to 128)<br>OUT: output time-slot (from 1 to 128) |

### Table 4 - Constant Throughput Delay values

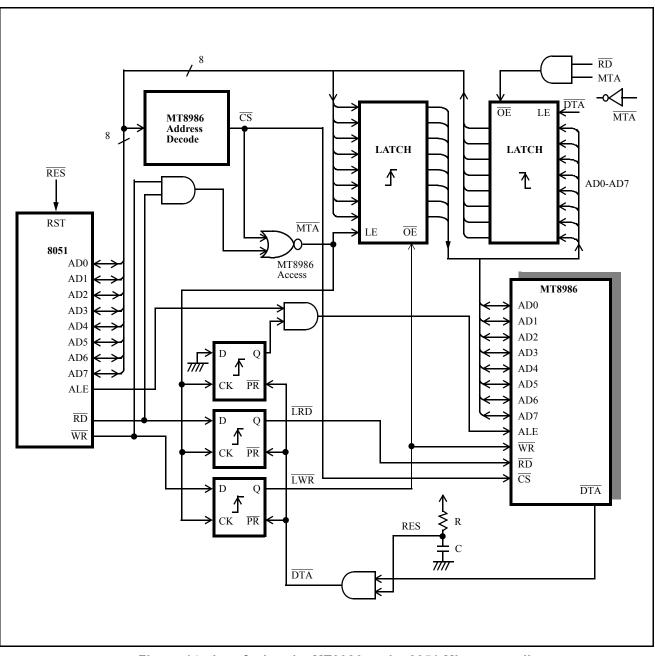

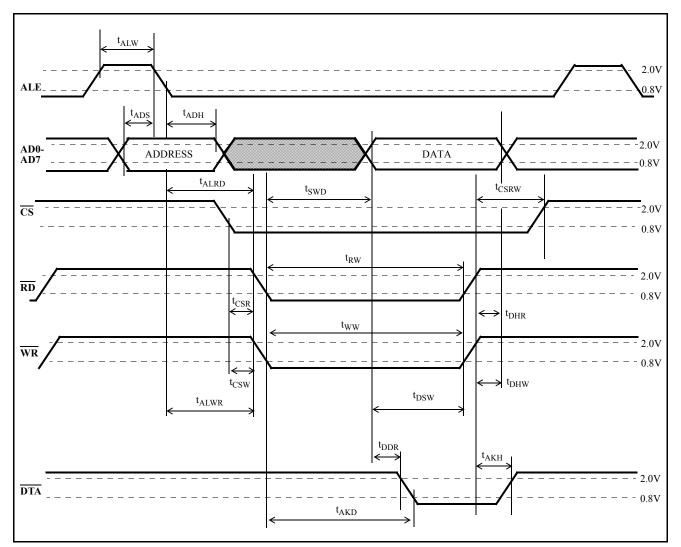

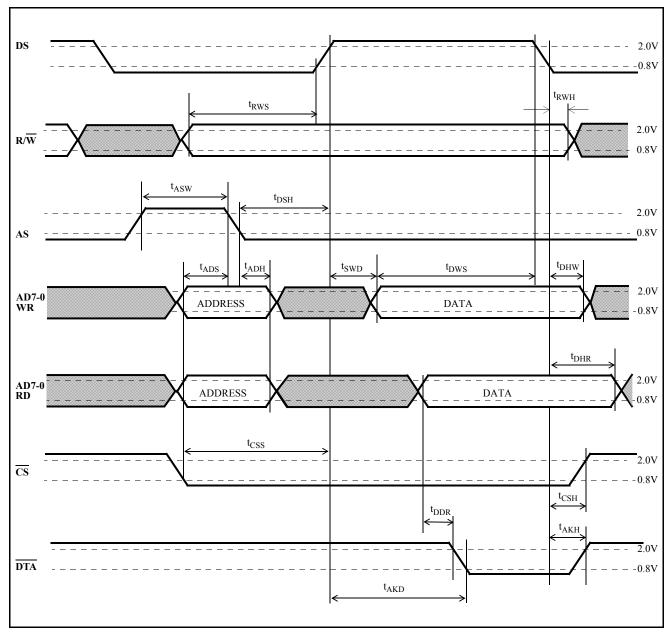

## Microprocessor Port

The non-multiplexed bus interface provided by the MT8986 device is identical to that provided in MT8980 Digital Switch device. In addition to the non-multiplexed bus, the MT8986 device provides an enhanced microprocessor interface with multiplexed bus structure compatible to both Motorola and Intel buses. The multiplexed bus structure is available only in the 44 pin packages and it is selected by the CPU Interface Mode (IM) input pin.

If IM input pin is not connected (left open) or grounded, the MT8986 parallel port assumes its default Motorola nonmultiplexed bus mode identical to that of MT8980. If IM input is connected HIGH, the internal parallel microport provides compatibility to MOTEL interface allowing direct connection to Intel, National and Motorola CPUs.

The MOTEL circuit (**MO**torola and In**TEL** compatible bus) <u>automatically</u> identifies the type of CPU Bus connected to the MT8986 device. This circuit uses the level of the DS/RD input pin at the rising edge of the AS/ALE to identify the appropriate bus timing connected to the MT8986. If DS/RD is LOW at the rising edge of AS/ALE then Motorola bus timing is selected. If DS/RD is HIGH at the rising edge of AS/ALE, then Intel bus timing is selected.

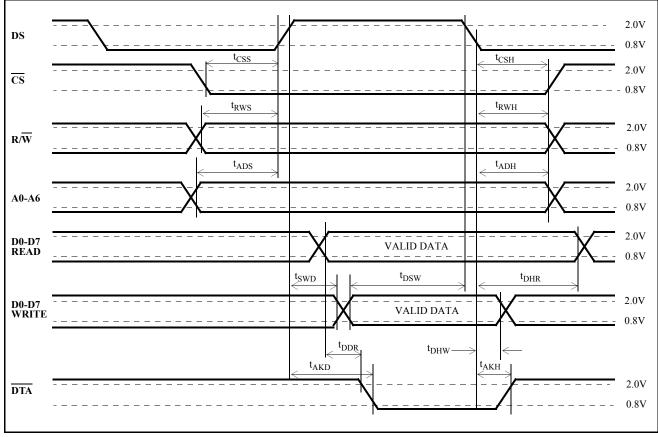

When MT8986 parallel port is operating in Motorola, National or Intel multiplexed bus interfaces, the signals available for controlling the device are: AD0-AD7 (Data and Address), ALE/AS (Address Latch Enable/Address Strobe), DS/RD (Data Strobe/Read), R/W/WR (Read/Write/Write), CS (Chip Select) and DTA (Data Acknowledgement). In Motorola non-multiplexed bus, the interface control signals are: data bus (AD0-AD7), six address input lines (A0-A5) and four control lines (CS, DS, R/W and DTA). See Figures 26 to 28 for each CPU interface timing.

The MT8986 parallel microport provides the access to the IMS, Control registers, the Connection Memory High, the Connection Memory Low and the Data Memory. All locations can be read or written except for the data memory which can be read only.

### Software Control

The address bus on the microprocessor interface selects the internal registers and memories of the MT8986. If the A5 address input is LOW, then the MT8986 Internal Control, Interface Mode, Stream Pair Selection and Frame Input Offset registers are addressed by the A4 to A0 bits according to Table 5. If A5 input is HIGH, then the remaining address input lines are used to select memory subsections of up to 128 locations corresponding to the maximum number of channels per input or output stream. The address input lines and the Stream Address bits (STA) of the Control register give the user the capability of accessing all sections of the MT8986 Data and Connect memories.

The Control and Interface Mode Selection registers together control all the major functions of the device. The Interface Mode Select register should be set up during system power-up to establish the desired switching configuration as explained in the Serial Interface and Switching Configurations sections.

The Control register is dynamically used by the CPU to control switching operations in the MT8986. The Control register selects the device's internal memories and its subsections to specify the input and output channels selected for switching procedures.

The data in the Control register consists of Split memory and Message mode bits, Memory select and Stream Address bits. The memory select bits allow the Connect Memory HIGH or LOW or the Data Memory to be chosen, and the Stream Address bits define an internal memory subsections corresponding to input or output ST-BUS streams.

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Location                       |

|----|----|----|----|----|----|----|----|--------------------------------|

| Х  | Х  | 0  | 0  | 0  | 0  | 0  | 0  | Control Register               |

| Х  | Х  | 0  | 0  | 0  | 0  | 0  | 1  | Interface Mode Select Register |

| Х  | Х  | 0  | 0  | 0  | 0  | 1  | 0  | Stream Pair Select Register    |

| Х  | Х  | 0  | 0  | 0  | 0  | 1  | 1  | Frame Input Offset Register    |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | Channel 0*                     |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | Channel 1*                     |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | Channel 31*                    |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | Channel 32**                   |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | Channel 33**                   |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Channel 63**                   |

| 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | Channel 64***                  |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| •  | •  | 1  | •  | •  | •  | •  | •  | •                              |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Channel 127***                 |

Table 5 - Address Memory Map

channels 0 to 31 are used in 2.048 Mb/s (8 x 8, 16 x 8 and 10 x 10) channels 0 to 63 are used in 4.096 Mb/s (Nibble Switching, 4 x 4, 8 x 4 or Different I/O rates)

\*\*\*: channels 0 to 127 are used in 8.192 Mb/s (2 x 2 or Different I/O rates)

Bit 7 (Slip Memory) of the Control register allows split memory operation whereby reads are from the Data memory and writes are to the Connect Memory LOW.

The Message Enable bit (bit 6) places every output channel on every output stream in message mode; i.e., the contents of the Connect Memory LOW (CML) are output on the ST-BUS output streams once every frame unless the ODE input pin is LOW. If ME bit is HIGH, then the MT8986 behaves as if bits 2 (Message Channel) and 0 (Output Enable) of every Connect Memory HIGH (CMH) locations were set to HIGH, regardless of the actual value. If ME bit is LOW, then bit 2 and 0 of each Connect Memory HIGH location function normally. In this case, if bit 2 of the CMH is HIGH, the associated ST-BUS output channel is in Message mode. If bit 2 of the CMH is LOW, then the contents of the SAB and CAB bits of the CMH and CML define the source information (stream and channel) of the time-slot that is to be switched to an output.

If the ODE input pin is LOW, then all serial outputs are high-impedance. If ODE is HIGH, then bit 0 (Output Enable) of the CMH location enables (if HIGH) or disables (if LOW) the output drivers for the corresponding individual ST-BUS output stream and channel.

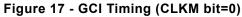

The contents of bit 1 (CSTo) of each Connection Memory High location is output on CSTo pin once every frame. The CSTo pin is a 2048 Mbit/s output which carries 256 bits. If CSTo bit is set HIGH, the corresponding bit on CSTo output is transmitted HIGH. If CSTo bit is LOW, the corresponding bit on the CSTo output is transmitted LOW. The contents of the 256 CSTo bits of the CMH are transmitted sequentially on to the CSTo output pin and are synchronous to the 2.048 Mb/s ST-BUS streams. To allow for delay in any external control circuitry the contents of the CSTo bit is output one channel before the corresponding channel on the ST-BUS streams. For example, the contents of CSTo bit in position 0 (ST0, CH0) of the CMH, is transmitted synchronously with ST-BUS channel 31, bit 7. The contents of CSTo bit in position 32 (ST1, CH0) of the CMH is transmitted during ST-BUS channel 31 bit 6. For more detailed description of the CSTo operation, see section 6 of Application Note MSAN-123.

The Bit V/C (Variable/Constant Delay) of each Connect Memory High location allows the per-channel selection between Variable and Constant throughput delay modes.

## Initialization of the MT8986

On initialization or power up, the contents of the Connection Memory High can be in any state. This is a potentially hazardous condition when multiple MT8986 ST-BUS outputs are tied together to form matrices, as these outputs may conflict. The ODE pin should be held low on power up to keep all outputs in the high impedance condition.

During the microprocessor initialization routine, the microprocessor should program the desired active paths through the matrices, and put all other channels into the high impedance state. Care should be taken that no two ST-BUS outputs drive the bus simultaneously. When this process is complete, the microprocessor controlling the matrices can bring the ODE signal high to relinquish high impedance state control to the  $CMH_bOs$ .

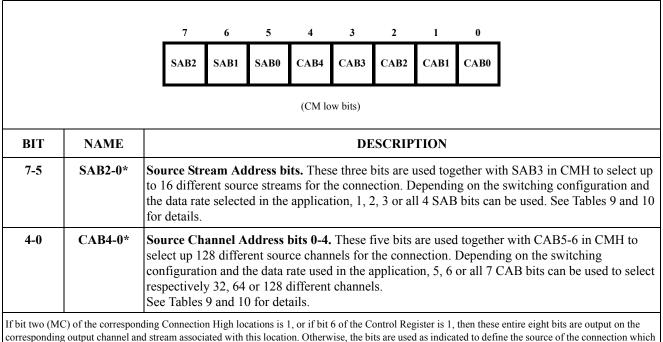

#### 7 6 5 4 3 2 1 0 STA3 MS1 MS0 STA2 SM ME STA1 STA0 BIT NAME DESCRIPTION 7 SM Split Memory. When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory Low, except when the Control Register is accessed again. When 0, the Memory Select bits specify the memory for subsequent operations. In either case, the Stream Address Bits select the subsection of the memory which is made available. 6 ME Message Enable. When 1, the contents of the Connection Memory Low are output on the Serial Output streams except when in High Impedance as set by the ODE input. When 0, the Connection Memory bits for each channel determine what is output. 5 STA3 Stream Address Bit 3. This bit is used in the 44 pin packages when 16 x 8 switching configuration is selected. It is used with STA2-0 to select one of the 16 input data streams whenever the Data Memory is to be read. The programming of this bit has no effect in other switching configurations. 4-3 MS1-0 Memory Select Bits. The memory select bits operate as follows: 0-0 - Not to be used

## **Control Register - Read/Write**

|     |        | 0-1 - Data Memory (read only from the CPU)<br>1-0 - Connection Memory Low<br>1-1 - Connection Memory High                                                                                                                                                        |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0 | STA2-0 | The number expressed in binary notation on these bits refers to the input or output ST-BUS stream which corresponds to the subsection of memory made accessible for subsequent operations.                                                                       |

|     |        | The use of these bits depends on the switching configuration as well as the device's main operation defined by the DMO bit of the Interface Mode Selection register. Tables 6 and 7 show the utilization of these bits according to the device's main operation. |

# Figure 3 - Control Register Description

| Identical<br>I/O<br>Rate | # of Input x<br>Output<br>Streams | STA bits used to<br>select subsections of<br>the Data<br>Memory | STA bits used to<br>select subsections of<br>the Connection<br>Memory | Input Address pins used to<br>select individual Connection<br>and Data Memory positions<br>within the selected subsection |

|--------------------------|-----------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 2 Mb/s                   | 8x8                               | STA2, STA1, STA0                                                | STA2, STA1, STA0                                                      | A4, A3, A2, A1, A0                                                                                                        |

| 2 Mb/s *                 | 4x4 *                             | STA1, STA0                                                      | STA1, STA0                                                            | A4, A3, A2, A1, A0                                                                                                        |

| Identical<br>I/O<br>Rate  | # of Input x<br>Output<br>Streams | STA bits used to<br>select subsections of<br>the Data<br>Memory | STA bits used to<br>select subsections of<br>the Connection<br>Memory | Input Address pins used to<br>select individual Connection<br>and Data Memory positions<br>within the selected subsection |  |  |

|---------------------------|-----------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| 2 Mb/s *                  | 16x8 *                            | STA3, STA2, STA1,<br>STA0                                       | STA2, STA1, STA0                                                      | A4, A3, A2, A1, A0                                                                                                        |  |  |

| 4 Mb/s                    | 4x4                               | STA1, STA0                                                      | STA1, STA0                                                            | A6, A4, A3, A2, A1, A0                                                                                                    |  |  |

| 4 Mb/s                    | 8x4                               | STA2, STA1, STA0                                                | STA1, STA0                                                            | A6, A4, A3, A2, A1, A0                                                                                                    |  |  |

| 8 Mb/s                    | 2x2                               | STA0                                                            | STA0                                                                  | A7, A6, A4, A3, A2, A1, A0                                                                                                |  |  |

| Nibble Switch<br>(2 Mb/s) | 8x4                               | STA2, STA1, STA0                                                | STA1, STA0                                                            | A6, A4, A3, A2, A1, A0 **                                                                                                 |  |  |

# Table 6 - Use of STA Bits for Identical I/O Data Rate Operation

\* - only in the 44 pin packages.

\*\* - for Data Memory Read operations A0 is not required since two nibbles are provided per read access.

| Different<br>I/O<br>Rate | Input x<br>Output<br>Streams<br>Config. | STA bits used to<br>select<br>Data<br>Memory<br>subsections | STA bits used to<br>select<br>Connection<br>Memory<br>subsections | Input Address pins used to<br>access individual Data<br>Memory<br>positions within the<br>selected subsection | Input Address pins used to<br>access individual<br>Connection Memory<br>positions within the<br>selected subsection |

|--------------------------|-----------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 2 Mb/s to 4<br>Mb/s      | 8x4                                     | STA2, STA1,<br>STA0                                         | STA1, STA0                                                        | A4, A3, A2, A1, A0                                                                                            | A6, A4, A3, A2, A1, A0                                                                                              |

| 2 Mb/s to 8<br>Mb/s      | 8x2                                     | STA2, STA1,<br>STA0                                         | STA0                                                              | A4, A3, A2, A1, A0                                                                                            | A7, A6, A4, A3, A2, A1, A0                                                                                          |

| 4 Mb/s to 2<br>Mb/s      | 4x8                                     | STA1, STA0                                                  | STA2, STA1,<br>STA0                                               | A6, A4, A3, A2, A1, A0                                                                                        | A4, A3, A2, A1, A0                                                                                                  |

| 8 Mb/s to 2<br>Mb/s      | 2x8                                     | STA0                                                        | STA2, STA1,<br>STA0                                               | A7, A6, A4, A3, A2, A1, A0                                                                                    | A4, A3, A2, A1, A0                                                                                                  |

### Table 7 - Use of STA Bits for Different I/O Data Rate Operation

Note: In rate conversion applications, Data Memory subsections have different sizes than Connection Memory subsections. This implies that different address inputs are used to select individual positions within the subsections for each type of memory.

# Interface Mode Selection Register - Read/Write

|     |        | 7          | 6          | 5          | 4          | 3         | 2        | 1         | 0         | I                                                                                          |

|-----|--------|------------|------------|------------|------------|-----------|----------|-----------|-----------|--------------------------------------------------------------------------------------------|

|     |        | DMO        | IDR1       | IDR0       | ODR1       | ODR0      | SCB1     | SCB0      | CLKM      |                                                                                            |

| BIT | NAME   |            |            |            |            | DE        | SCRIP    | TION      |           |                                                                                            |

| 7   | DMO    | the MT898  | 6 device   | e. If this | bit is LO  | OW, the   | MT8986   | 5 is conf | igured f  | of the two main operations<br>for identical I/O data rates. F<br>ion through the SCB bits. |

|     |        | combinatio | ns of inj  | put and    | output d   | ata rates | as show  | vn in Ta  | ble 2. Tł | O data rate. This allows<br>ne SCB bits have no effect in<br>tion with a 256 x 256 chann   |

| 6-5 | IDR1-0 |            | n the cas  |            |            |           |          |           |           | ta rates for the inputs of the salso determine the serial                                  |

|     |        |            | IDR:       | <u>1</u> ] | DR0        | In        | put Rat  | <u>e</u>  |           |                                                                                            |

|     |        |            | 0          |            | 0          | 2.0       | 48 Mb/s  | 5         |           |                                                                                            |

|     |        |            | 0          |            | 1          | 4.0       | 96 Mb/s  | 5         |           |                                                                                            |

|     |        |            | 1          |            | 0          | 8.1       | 92 Mb/s  | 5         |           |                                                                                            |

|     |        |            | 1          |            | 1          | res       | erved    |           |           |                                                                                            |

| 4-3 | ODR1-0 |            | 1). Thes   | se two bi  | its select | three di  |          |           |           | rent I/O rates are selected serial outputs of the MT898                                    |

|     |        |            | <u>ODR</u> | 1 (        | ODR0       | Ou        | itput Ra | ate       |           |                                                                                            |

|     |        |            | 0          | ± 1        | 0          |           | 48 Mb/:  |           |           |                                                                                            |

|     |        |            | 0          |            | 1          |           | 96 Mb/   |           |           |                                                                                            |

|     |        |            | 1          |            | 0          | 8.1       | 92 Mb/s  | 5         |           |                                                                                            |

|     |        |            | 1          |            | 1          | res       | erved    |           |           |                                                                                            |

| 2-1 | SCB1-0 |            |            |            |            |           |          |           |           | when DMO is set LOW. The device is described in Tab                                        |

| 0   | CLKM   |            | n set Hig  | gh, this ł | oit select | s the int | erface c |           |           | to operate in identical I/O da<br>to the bit rate. If Low, this b                          |

# Figure 4 - IMS Register Description

| DMO Bit                        | DMO Bit Data Rate Selected<br>at IDR bits (Mb/s) |              | SCB0         | Configuration                                                                                   |

|--------------------------------|--------------------------------------------------|--------------|--------------|-------------------------------------------------------------------------------------------------|

|                                |                                                  | 0            | 0            | 8 inputs x 8 outputs - Non Blocking                                                             |

|                                |                                                  | 0            | 1            | 16 inputs x 8 outputs - Blocking**                                                              |

|                                | 2.048                                            | 1            | 0            | Stream pair selection capability (internal channel capacity<br>= 128 x 128) -<br>Non Blocking** |

| LOW                            |                                                  | 1            | 1            | Nibble Switching - 8 inputs x 4 outputs - Blocking                                              |

| Identical<br>I/O               |                                                  | 0            | 0            | 8 inputs x 4 outputs - Blocking                                                                 |

| Rates                          | 4.006                                            | 0            | 1            | 4 inputs x 4 outputs - Non-Blocking                                                             |