## MV Series

## 14 DIP, 5.0 Volt, HCMOS/TTL, VCXO

- General purpose VCXO for Phase Lock Loops (PLLs), Clock Recovery, Reference Signal Tracking, and Synthesizers

- Frequencies up to 160 MHz

- Tri-state Option Available

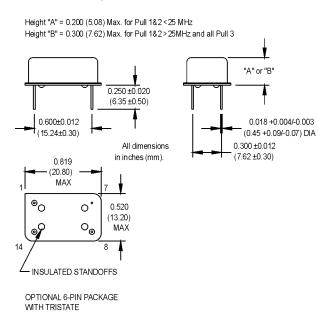

## Pin Connections

0.200 ±0.012 (5.08 ±0.30)

ં

0

| PIN | FUNCTION                   |

|-----|----------------------------|

| 1   | Control Voltage            |

| 3   | Tristate (6-Pin Pkg. Only) |

| 7   | Ground                     |

| 8   | Output                     |

| 12  | N/C (6-Pin Pkg. Only)      |

| 14  | +Vdd                       |

| Ordering Information                              |                |       |   |   |   |   |    | 00.000 |

|---------------------------------------------------|----------------|-------|---|---|---|---|----|--------|

|                                                   | MV 1           | 3     | V | 2 | С | D | -R | MHz    |

|                                                   |                |       |   |   |   |   |    |        |

| Product Series -                                  | <b>-</b>       |       |   |   |   |   |    |        |

| Temperature Range ————                            |                |       |   |   |   |   |    |        |

| 1: 0°C to +70°C 2: -40°                           | °C to +85°C    | ;     |   |   |   |   |    |        |

| 6: -20°C to +70°C                                 |                |       |   |   |   |   |    |        |

| Stability ————                                    |                |       |   |   |   |   |    |        |

| 1: ±1000 ppm 2: ±500 ppm                          | 3: ±100        | ) ppm |   |   |   |   |    |        |

| <b>4</b> : ±50 ppm <b>5</b> : ±35 ppm             | <b>6</b> : ±25 | ppm   |   |   |   |   |    |        |

| *8: ±20 ppm                                       |                |       |   |   |   |   |    |        |

| Output Type — — — — — — — — — — — — — — — — — — — |                |       |   |   |   |   |    |        |

| V: Voltage Controlled T: Trist                    | tate           |       |   |   |   |   |    |        |

| Pull Range (Vc = .5 to 4.5V) —                    |                |       |   | _ |   |   |    |        |

| 1: ±50 ppm min. 2: ±100                           |                |       |   |   |   |   |    |        |

| 3: ±200 ppm min. ("B" package                     |                |       |   |   |   |   |    |        |

| Symmetry/Logic Compatibility                      |                |       |   |   |   |   |    |        |

| A: 40/60 CMOS/TTL C: 45/5                         |                |       |   |   |   |   |    |        |

| Package/Lead Configurations -                     |                |       |   |   |   |   |    |        |

| D: DIP; Nickel Header G: Gul                      |                |       |   |   |   |   |    |        |

| RoHS Compliance                                   |                |       |   |   |   |   |    |        |

| Blank: non-RoHS compliant p                       | рап            |       |   |   |   |   |    |        |

| -R: RoHS compliant part                           | Λ              |       |   |   |   |   |    |        |

| Frequency (customer specified                     | ı) <del></del> |       |   |   |   |   |    |        |

\*Contact factory for availability

| Г        | PARAMETER                                               | Symbol | Min.                | Тур.         | Max.                       | Units    | Condition/Notes                                  |

|----------|---------------------------------------------------------|--------|---------------------|--------------|----------------------------|----------|--------------------------------------------------|

| ı        | Frequency Range                                         | F      | 1.5                 |              | 160                        | MHz      | See Note 1                                       |

| ı        | Operating Temperature                                   | $T_A$  | (See Orde           | ering Infor  | mation)                    |          |                                                  |

| ı        | Storage Temperature                                     | Ts     | -55                 |              | 125                        | °C       |                                                  |

| ı        | Frequency Stability                                     | ΔF/F   | (See Orde           | ering Infor  | mation)                    |          |                                                  |

| ı        | Aging                                                   |        |                     |              |                            |          |                                                  |

| ı        | 1st Year                                                |        | 0.6                 |              | 0.6                        | ppm      | < 52 MHz / ≥ 52 MHz                              |

| ı        | Thereafter (per year)                                   |        | 0.5                 |              | 0.5                        | ppm      | < 52 MHz / ≥ 52 MHz                              |

| ı        | Pullability/APR                                         |        | _                   | ering Infor  |                            |          | Over control voltage                             |

| ı        | Control Voltage                                         | Vc     | 0.5                 | 2.5          | 4.5                        | V        |                                                  |

| L        | Linearity                                               |        |                     |              | 10                         | %        | Positive Monotonic Slope                         |

| ı        | Modulation Bandwidth                                    | fm     | 10                  |              |                            | kHz      |                                                  |

| 1        | Input Impedance                                         | Zin    | 50k                 |              |                            | Ohms     |                                                  |

| L        | Input Voltage                                           | Vdd    | 4.75                | 5            | 5.25                       | V        |                                                  |

| Įφ       | Input Current                                           | ldd    |                     | 25           | 40                         | mA       | 1.5 to 24.999 MHz                                |

| ĮΞ       |                                                         |        |                     | 35           | 60                         | mA       | 25 to 69.999 MHz                                 |

| g        |                                                         |        |                     | 55           | 90                         | mA       | 70 to 160 MHz                                    |

| 5        | Output Type                                             |        |                     |              |                            |          | HCMOS/TTL                                        |

| ical Spe | Output Type Load  Symmetry (Duty Cycle) Logic "1" Level |        | 10 TTL or           |              |                            |          | See Note 2<br>1.5 to 54.999 MHz<br>55 to 160 MHz |

| 늉        | Symmetry (Duty Cycle)                                   |        | (See Orde           | ering Infori | mation)                    |          | See Note 3                                       |

| H        | Logic "1" Level                                         | Voh    | 90% Vdd<br>Vdd -0.5 |              | ·                          | V<br>V   | HCMOS load<br>TTL load                           |

|          | Logic "0" Level                                         | Vol    |                     |              | 10% Vdd<br>0.5             | V<br>V   | HCMOS load<br>TTL load                           |

|          | Rise/Fall Time<br>1.5 to 54.999 MHz<br>55 to 160 MHz    | Tr/Tf  |                     |              | 6 / 10<br>1.5 / 5          | ns<br>ns | See Note 4<br>TTL/HCMOS<br>TTL/HCMOS             |

|          | Tri-state Function                                      |        |                     | ic "0": out  | ating: outp<br>put disable |          |                                                  |

| 1        | Start up Time                                           |        |                     | 5            |                            | ms       |                                                  |

| l        | Phase Jitter                                            | φЈ     |                     |              |                            |          |                                                  |

|          | @ 38.88 MHz                                             |        |                     | 0.3          | 1                          | ps RMS   | Integrated 12 kHz - 20 MHz                       |

| 1        | @ 155.52 MHz                                            |        |                     | 10           | 15                         | ps RMS   | Integrated 12 kHz - 20 MHz                       |

| 1        | Phase Noise (Typical)                                   | 10 Hz  | 100 Hz              | 1 kHz        | 10 kHz                     | 100 kHz  | Offset from carrier                              |

| 1        | @ 38.88 MHz                                             | -71    | -104                | -134         | -151                       | -153     |                                                  |

| L        | @ 155.52 MHz<br>. Frequencies above 90 MHz              | -62    | -93                 | -113         | -115                       | -114     |                                                  |

- Frequencies above 90 MHz utilize a PPL design. Fundamental and PLL designs are available for other frequencies. Contact factory.

- 2. TTL load see load circuit diagram #1. HCMOS load see load circuit diagram #2.

3. Symmetry is measured at 1.4 V with TTL load, and at 50% with HCMOS load.

- Rise/Fall times are measured between 0.5 V and 2.4 V for TTL load, and between 10% Vdd and 90% Vdd for HCMOS load.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.