14 NON-MUXED OUT

13 MUX SELECT

FEATURES

- **EPIC™** (Enhanced-Performance Implanted **CMOS) Submicron Process**

- Useful for Jumperless Configuration of PC Motherboard

- Inputs Accept Voltages to 5.5 V

- **MUX OUT Signals are 2.5-V Outputs**

- NON-MUXED OUT Signal is a 3.3-V Output

- **Minimum of 1000 Write Cycles**

- Minimum of 10 Years Data Retention

- **Package Options Include Plastic** Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages

## **DESCRIPTION/ORDERING INFORMATION**

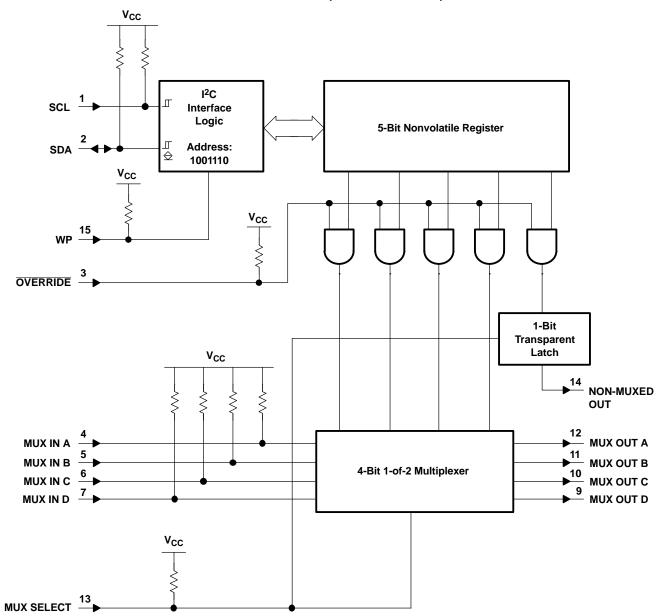

This 4-bit 1-of-2 multiplexer with  $I^2C$  input interface is designed for 3-V to 3.6-V V<sub>CC</sub> operation.

The PCA8550 is designed to multiplex four bits of data from parallel inputs or from I<sup>2</sup>C input data stored in a nonvolatile register. An additional bit of register output also is provided, which is latched to prevent changes in the output value during the write cycle. The factory default for the contents of the register is all low. These stored values can be read from, or written to, using the I<sup>2</sup>C bus. The ability to control writing to the register is provided by the write protect (WP) input. The override (OVERRIDE) input forces all the register outputs to a low.

This device provides a fast-mode (400 kbit/s) or standard-mode (100 kbit/s) I<sup>2</sup>C serial interface for data input and output. The implementation is as a slave. The device address is specified in the I<sup>2</sup>C interface definition table. Both of the I<sup>2</sup>C Schmitt-trigger inputs (SCL and SDA) provide integrated pullup resistors and are 5-V tolerant.

The PCA8550 requires a monotonic power-supply ramp at start-up in the region of 1.1 V to 2.5 V. The nonvolatile registers and I<sup>2</sup>C state machine initialize to their default states after this V<sub>CC</sub> level is passed.

The PCA8550 is characterized for operation from 0°C to 70°C.

## **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> |              | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|------------------------|--------------|-----------------------|------------------|--|

|                | SOIC – D               | Tube of 40   | PCA8550D              |                  |  |

| 0°C to 70°C    | 30IC - D               | Reel of 2500 | PCA8550DR             |                  |  |

| 0°C to 70°C    | SSOP – DB              | Reel of 2000 | PCA8550DBR            | PCA8550          |  |

|                | TSSOP – PW             | Reel of 2000 | PCA8550PWR            | -                |  |

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at (1)www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. EPIC is a trademark of Texas Instruments.

16 Vcc

15 WP

D, DB, OR PW PACKAGE

(TOP VIEW)

1<sup>2</sup>C SCL

OVERRIDE 3

MUX IN A 4

I<sup>2</sup>C SDA **[**] 2

TEXAS INSTRUMENTS www.ti.com

# FUNCTION TABLE

| INPL       | ITS      | OUTPUTS              |                                      |  |

|------------|----------|----------------------|--------------------------------------|--|

| MUX SELECT | OVERRIDE | MUX OUT              | NON-MUXED OUT                        |  |

| L          | L        | L                    | L                                    |  |

| L          | Н        | Nonvolatile register | Nonvolatile register                 |  |

| Н          | Х        | MUX IN               | Latched NON-MUXED OUT <sup>(1)</sup> |  |

(1) The latched NON-MUXED OUT state is the value present on the NON-MUXED OUT output at the time the MUX SELECT input transitions from the low to the high state.

#### LOGIC DIAGRAM (POSITIVE LOGIC)

### I<sup>2</sup>C Interface

$I^2C$  communication with this device is initiated by a master sending a start condition, a high-to-low transition on the serial data (SDA) input/output while the serial clock (SCL) input is high. After the start condition, the device address byte is sent, MSB first, including the data-direction bit (R/W). This device does not respond to the general call address. After receiving the valid address byte, this device responds with an acknowledge, a low on the SDA input/output during the high of the acknowledge-related clock pulse.

The data byte follows the address acknowledge. If the  $R/\overline{W}$  bit is high, the data from this device are the values read from the nonvolatile register. If the  $R/\overline{W}$  bit is low, the data are from the master, to be written into the register. A valid data byte is one in which the three high-order bits are low. The first valid data byte that is received is written into the register, following the stop condition. If an invalid data byte is received, it is acknowledged, but is not written into the register. The data byte is followed by an acknowledge sent from this device. If other data bytes are sent from the master, following the acknowledge, they are ignored by this device.

A stop condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master. If the WP input is low during the falling edge of the first valid data byte acknowledge on the SCL input and the  $R/\overline{W}$  bit is low, the stop condition causes the I<sup>2</sup>C interface logic to write the data byte value into the nonvolatile register. Data are written only if complete bytes are received and acknowledged. Writing to the register takes time (t<sub>wr</sub>), during which the device does not respond to its slave address. If the WP input is high, the I<sup>2</sup>C interface logic does not write to the register.

| BYTE    | BIT     |   |   |                   |           |           |           |           |  |  |

|---------|---------|---|---|-------------------|-----------|-----------|-----------|-----------|--|--|

| DTIE    | 7 (MSB) | 6 | 5 | 4                 | 3         | 2         | 1         | 0 (LSB)   |  |  |

| Address | Н       | L | L | Н                 | Н         | Н         | L         | R/W       |  |  |

| Data    | L       | L | L | NON-<br>MUXED OUT | MUX OUT D | MUX OUT C | MUX OUT B | MUX OUT A |  |  |

#### I<sup>2</sup>C Interface Definition Table

### Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                            |                                                     | MIN  | MAX                   | UNIT |

|------------------|--------------------------------------------|-----------------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage range                       | -0.5                                                | 6.5  | V                     |      |

| VI               | Input voltage range <sup>(2)</sup>         |                                                     | -0.5 | 6.5                   | V    |

|                  |                                            | SDA <sup>(2)</sup>                                  | -0.5 | 6.5                   |      |

| Vo               | Output voltage range                       | MUX OUT outputs <sup>(2)</sup>                      | -0.5 | 2.9                   | V    |

| -                |                                            | NON-MUXED OUT output <sup>(2)(3)</sup>              | -0.5 | V <sub>CC</sub> + 0.5 |      |

| I <sub>IK</sub>  | Input clamp current                        | V <sub>1</sub> < 0                                  |      | -50                   | mA   |

| I <sub>ОК</sub>  | Output clamp current                       | $V_{\rm O}$ < 0 or $V_{\rm O}$ > $V_{\rm CC}^{(3)}$ |      | -50, +10              | mA   |

| I <sub>IOK</sub> | Input/output clamp current                 | V <sub>0</sub> < 0                                  |      | -50                   | mA   |

| I <sub>O</sub>   | Continuous output current                  | $V_{O} = 0$ to $V_{CC}^{(3)}$                       |      | ±15                   | mA   |

|                  | Continuous current through $V_{CC}$ or GND |                                                     |      | ±30                   | mA   |

|                  |                                            | D package                                           |      | 113                   |      |

| $\theta_{JA}$    | Package thermal impedance <sup>(4)</sup>   | DB package                                          | 131  |                       | °C/W |

|                  |                                            | PW package                                          |      | 149                   |      |

| T <sub>stg</sub> | Storage temperature range                  |                                                     | -65  | 85                    | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

(3) The value of  $V_{CC}$  is provided in the recommended operating conditions table.

(4) The package thermal impedance is calculated in accordance with JESD 51.

## PCA8550 NONVOLATILE 5-BIT REGISTER WITH I<sup>2</sup>C INTERFACE

SCPS050C-MARCH 1999-REVISED MAY 2005

## **Recommended Operating Conditions**

|                          |                                    |                                  | MIN  | MAX | UNIT |  |

|--------------------------|------------------------------------|----------------------------------|------|-----|------|--|

| V <sub>CC</sub>          | Supply voltage                     |                                  | 3    | 3.6 | V    |  |

| V                        | High-level input voltage           | SCL, SDA                         | 2.7  | 4   |      |  |

| VIH                      | High-level linput voltage          | OVERRIDE, MUX IN, MUX SELECT, WP | 2    | 4   | V    |  |

| V <sub>IL</sub> Low-leve |                                    | SCL, SDA                         | -0.5 | 0.9 | V    |  |

|                          | Low-level input voltage            | OVERRIDE, MUX IN, MUX SELECT, WP | -0.5 | 0.8 | v    |  |

| I <sub>OH</sub>          | High-level output current          | MUX OUT, NON-MUXED OUT           |      | -2  | mA   |  |

|                          |                                    | SDA                              |      | 6   | ~ ^  |  |

| IOL                      | Low-level output current           | MUX OUT, NON-MUXED OUT           |      | 2   | mA   |  |

| $\Delta t/\Delta v$      | Input transition rise or fall rate | OVERRIDE, MUX IN, MUX SELECT, WP |      | 10  | ns/V |  |

| T <sub>A</sub>           | Operating free-air temperature     |                                  | 0    | 70  | °C   |  |

### **Electrical Characteristics**

over recommended operating free-air temperature range, V\_{CC} = 3.3 V  $\pm$  0.3 V (unless otherwise noted)

| PARAMETER                       |                                | TEST                                  | MIN                          | MAX    | UNIT  |    |

|---------------------------------|--------------------------------|---------------------------------------|------------------------------|--------|-------|----|

| V <sub>IK</sub>                 | Input diode clamp voltage      | I <sub>I</sub> = -18 mA               |                              | -1.5   |       | V  |

| V <sub>hys</sub> <sup>(1)</sup> | SCL, SDA                       |                                       |                              | 0.19   |       | V  |

|                                 |                                | I <sub>OH</sub> = −100 μA             |                              | 2      | 2.625 |    |

| V                               | MUX OUT                        | I <sub>OH</sub> = -1 mA               |                              | 1.7    | 2.625 | V  |

| V <sub>OH</sub>                 | NON-MUXED OUT                  | I <sub>OH</sub> = −100 μA             |                              | 2.4    | 3.6   | v  |

|                                 | NON-MOXED OUT                  | I <sub>OH</sub> = -2 mA               |                              | 2      | 3.6   | 1  |

|                                 | MUX OUT                        | I <sub>OL</sub> = 100 μA              |                              | -0.3   | 0.4   |    |

|                                 | MOX OUT                        | I <sub>OL</sub> = 2 mA                | -0.3                         | 0.7    | V     |    |

| V                               | NON-MUXED OUT                  | I <sub>OL</sub> = 100 μA              | -0.5                         | 0.4    |       |    |

| V <sub>OL</sub>                 | NON-MOXED OUT                  | I <sub>OL</sub> = 2 mA                | -0.5                         | 0.7    |       |    |

|                                 | SDA                            | I <sub>OL</sub> = 3 mA                |                              | 0.4    |       |    |

|                                 |                                | I <sub>OL</sub> = 6 mA                |                              |        | 0.6   | 1  |

|                                 | SCL, SDA                       |                                       |                              | -1.5   | -12   |    |

| I <sub>IH</sub>                 | OVERRIDE, MUX SELECT, WP       | V <sub>IH</sub> = 2.4 V               | -20                          | -100   | μΑ    |    |

|                                 | MUX IN                         |                                       |                              | -0.166 | -0.75 | mA |

|                                 | SCL, SDA                       |                                       |                              | -7     | -32   | ۸  |

| I <sub>IL</sub>                 | OVERRIDE, MUX SELECT, WP       | V <sub>IL</sub> = 0.4 V               |                              | -86    | -267  | μA |

|                                 | MUX IN                         |                                       |                              | -0.72  | -2    | mA |

|                                 | During read or write cycle     | $V_{I} = 0$ to $V_{CC}$ , $I_{O} = 0$ | $V_{\rm CC} = 3.3 \ {\rm V}$ |        | 10    | mA |

| I <sub>CC</sub>                 | Not during read or write cycle | $V_{I} = V_{CC},$ $I_{O} = 0$         | )                            |        | 500   | μA |

| Ci                              |                                | $V_I = V_{CC}$ or GND                 |                              |        | 10    | pF |

(1)  $V_{hys}$  is the hysteresis of Schmitt-trigger inputs.

### **Nonvolatile Storage Specifications**

| PARAMETER                                  | SPECIFICATIONS       |

|--------------------------------------------|----------------------|

| Write time (t <sub>wr</sub> )              | 10 ms, typical       |

| Memory-cell data retention                 | 10 years, minimum    |

| Maximum number of memory-cell write cycles | 1000 cycles, minimum |

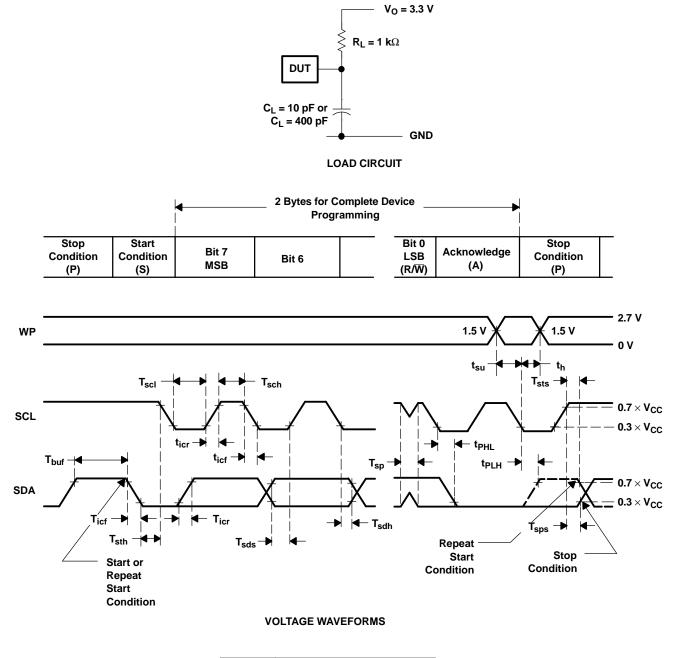

## I<sup>2</sup>C Interface Timing Requirements

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 1)

|                               |                                                          | $V_{CC}$ = 3.3 V $\pm$                 | 0.3 V | UNIT |

|-------------------------------|----------------------------------------------------------|----------------------------------------|-------|------|

|                               |                                                          | MIN                                    | MAX   | UNIT |

| f <sub>scl</sub>              | I <sup>2</sup> C clock frequency                         | 10                                     | 400   | kHz  |

| t <sub>sch</sub>              | I <sup>2</sup> C clock high time                         | 600                                    |       | ns   |

| t <sub>scl</sub>              | I <sup>2</sup> C clock low time                          | 1.3                                    |       | μs   |

| t <sub>sp</sub>               | I <sup>2</sup> C spike time                              | 0                                      | 50    | ns   |

| t <sub>sds</sub>              | I <sup>2</sup> C serial data setup time                  | 100                                    |       | ns   |

| t <sub>sdh</sub>              | I <sup>2</sup> C serial data hold time                   | 0                                      | 900   | ns   |

| t <sub>icr</sub>              | I <sup>2</sup> C input rise time                         | 20                                     | 300   | ns   |

| t <sub>icf</sub>              | I <sup>2</sup> C input fall time                         | 20                                     | 300   | ns   |

| t <sub>ocf</sub>              | I <sup>2</sup> C output fall time (10-pF to 400-pF bus)  | 20 + 0.1 C <sub>b</sub> <sup>(1)</sup> | 250   | ns   |

| t <sub>buf</sub>              | I <sup>2</sup> C bus free time between stop and start    | 1.3                                    |       | μs   |

| t <sub>sts</sub>              | I <sup>2</sup> C start or repeated start condition setup | 600                                    |       | ns   |

| t <sub>sth</sub>              | I <sup>2</sup> C start or repeated start condition hold  | 600                                    |       | ns   |

| t <sub>sps</sub>              | I <sup>2</sup> C stop condition setup                    | 600                                    |       | ns   |

| C <sub>b</sub> <sup>(1)</sup> | I <sup>2</sup> C bus capacitive load                     |                                        | 400   | pF   |

(1)  $C_b$  = capacitance of one bus line in pF

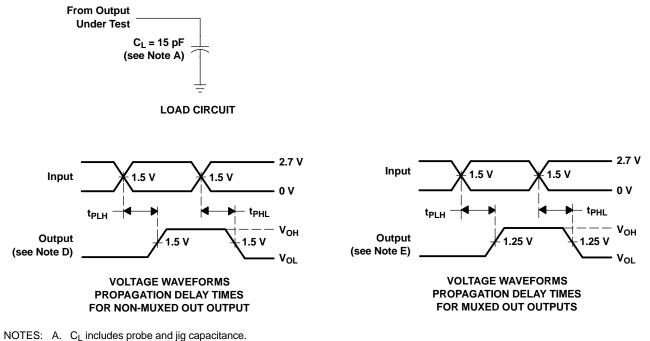

#### **Switching Characteristics**

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 2)

| PARAMETER        |                                        |            | FROM TO<br>(INPUT) (OUTPUT)                                           |      | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |      |

|------------------|----------------------------------------|------------|-----------------------------------------------------------------------|------|------------------------------------|------|

|                  |                                        | (INFOT)    | (001-01)                                                              | MIN  | MAX                                |      |

| t <sub>mpd</sub> | Mux input to output propagation delay  | MUX IN     | MUX OUT                                                               |      | 20                                 | ns   |

| t <sub>sov</sub> | MUX SELECT to output valid             | MUX SELECT | Output valid                                                          |      | 22                                 | ns   |

| t <sub>ovn</sub> | OVERRIDE to NON-MUXED OUT output delay | OVERRIDE   | NON-MUXED OUT                                                         |      | 15                                 | ns   |

| t <sub>ovm</sub> | OVERRIDE to MUX OUT output delay       | OVERRIDE   | MUX OUT                                                               |      | 25                                 | ns   |

| t <sub>su</sub>  | Setup time                             | WP         | Falling edge of first valid data byte<br>acknowledge on the SCL input | 30   |                                    | ns   |

| t <sub>h</sub>   | Hold time                              | WP         | Falling edge of first valid data byte<br>acknowledge on the SCL input | 120  |                                    | ns   |

| t <sub>r</sub>   | Output rise time                       |            |                                                                       | 1    | 3                                  | ns/V |

| t <sub>f</sub>   | Output fall time                       | 1          | 3                                                                     | ns/V |                                    |      |

SCPS050C-MARCH 1999-REVISED MAY 2005

#### PARAMETER MEASUREMENT INFORMATION

| BYTE | DESCRIPTION               |  |  |  |

|------|---------------------------|--|--|--|

| 1    | I <sup>2</sup> C address  |  |  |  |

| 2    | Nonvolatile register data |  |  |  |

Figure 1. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

## PCA8550 NONVOLATILE 5-BIT REGISTER WITH I<sup>2</sup>C INTERFACE

SCPS050C-MARCH 1999-REVISED MAY 2005

### PARAMETER MEASUREMENT INFORMATION

- B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>O</sub> = 50  $\Omega$ , t<sub>r</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

- C. The outputs are measured one at a time, with one transition per measurement.

- D.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{sov}$  and  $t_{ovn}$ .

- E.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{mpd}$ ,  $t_{sov}$ , and  $t_{ovm}$ .

#### Figure 2. Load Circuit and Voltage Waveforms

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| PCA8550D         | ACTIVE                | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550DBR       | ACTIVE                | SSOP            | DB                 | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550DBRE4     | ACTIVE                | SSOP            | DB                 | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550DE4       | ACTIVE                | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550DR        | ACTIVE                | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550DRE4      | ACTIVE                | SOIC            | D                  | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550PWR       | ACTIVE                | TSSOP           | PW                 | 16                  | TBD                     | Call TI          | Call TI                      |

| PCA8550PWRE4     | ACTIVE                | TSSOP           | PW                 | 16                  | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

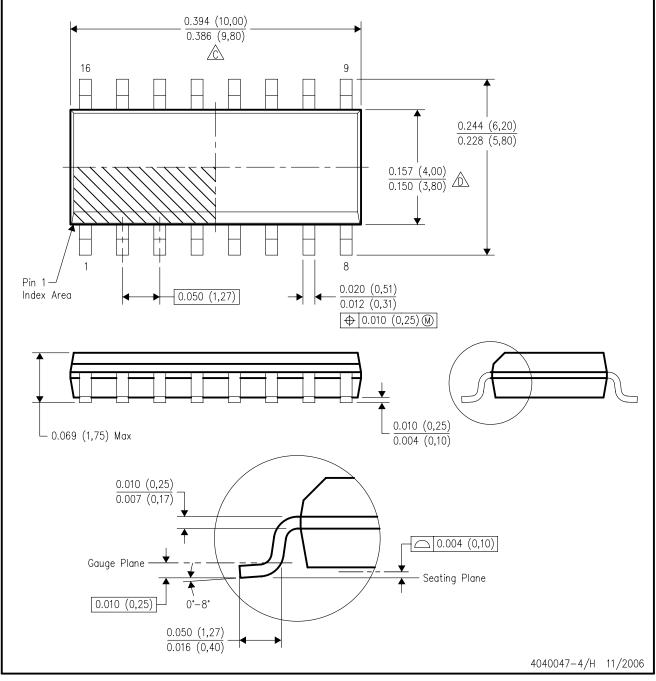

D (R-PDSO-G16)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AC.

## **MECHANICAL DATA**

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

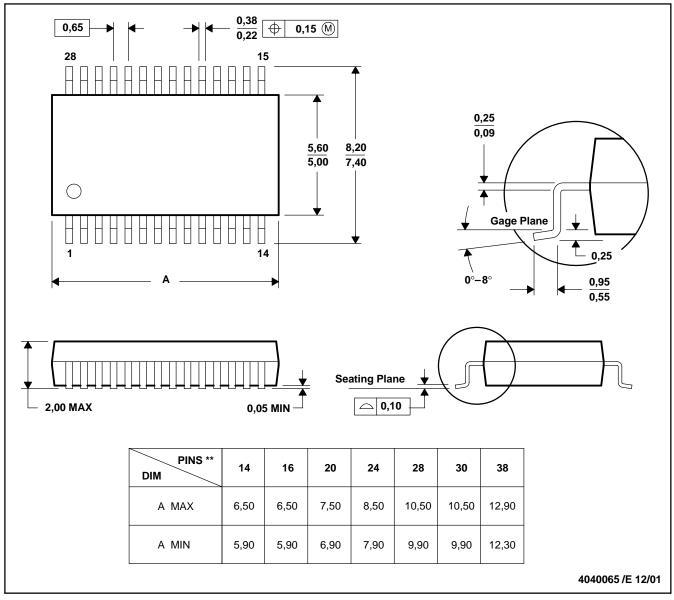

## DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

## **MECHANICAL DATA**

MTSS001C - JANUARY 1995 - REVISED FEBRUARY 1999

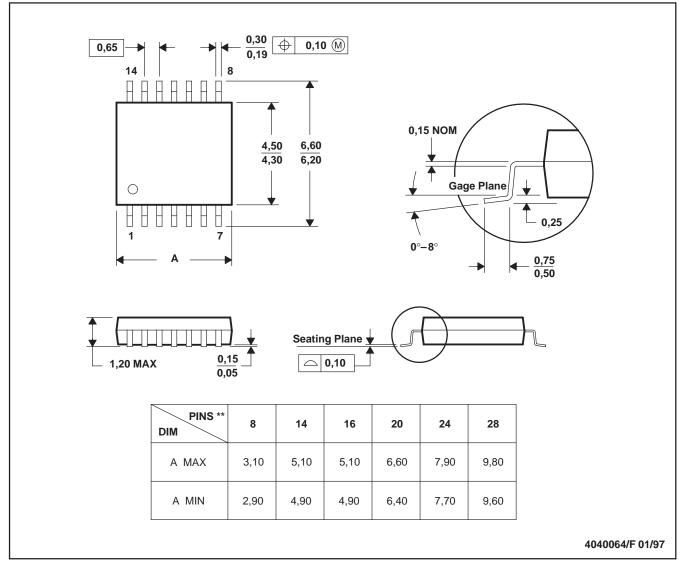

## PW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

14 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated