National Semiconductor

# PCM16C02 Configurable Multiple Function PC Card Interface Chip

# **General Description**

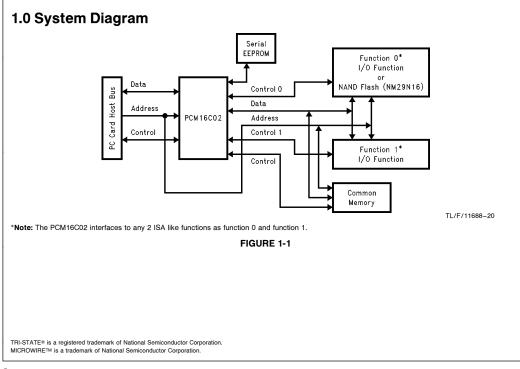

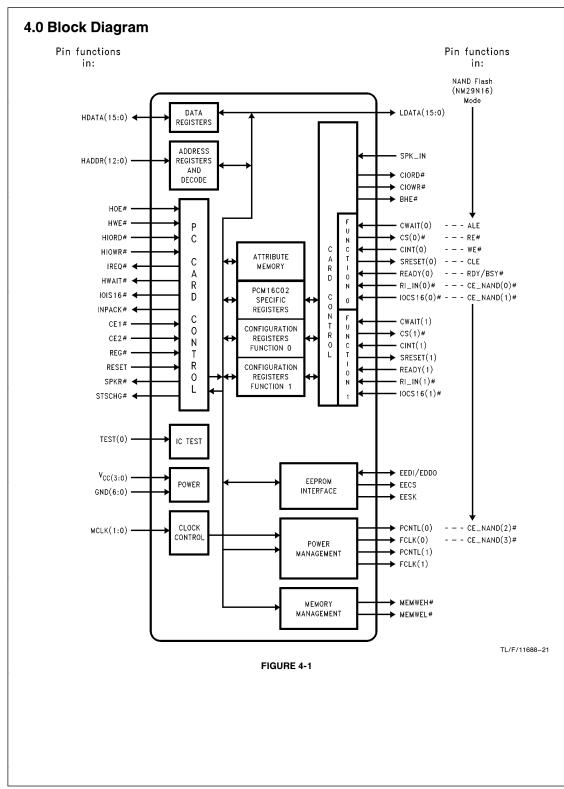

National's PCM16C02 acts as a standard interface between the PC Card Host bus and local card busses found on I/O and memory PC Cards. This device allows the card designer to focus on the design of the I/O functions while providing a one-chip solution for I/O memory window control, EEPROM interfacing, and power management. The PCM16C02 was specifically designed to take advantage of those functions that don't require card-side bus arbitration, while not giving up any of the non-arbitration related functionality. However, if card-side bus arbitration is required refer to the PCM16C00 datasheet.

The PCM16C02 provides a PC Card interface for any two ISA like functions as function 0 and function 1 which allows two functions to be placed on a single PC Card.

In addition, the PCM16C02 provides the capability to configure function 0 as a NAND Flash (NM29N16) interface; supporting all of the necessary control signals required to handshake with NAND Flash (NM29N16) memory devices.

The PCM16C02 is fully compliant with the PC Card Standard. This multi-function IC allows the system software to setup I/O decode windows and provides the Attribute memory decode control that allow attribute read and write data transfers.

Note, PC Card refers to technology developed to the PC Card Standards determined by the PCMCIA Standards Committee.

## Features

## PC Card bus interface

- PC Card Standard configuration registers

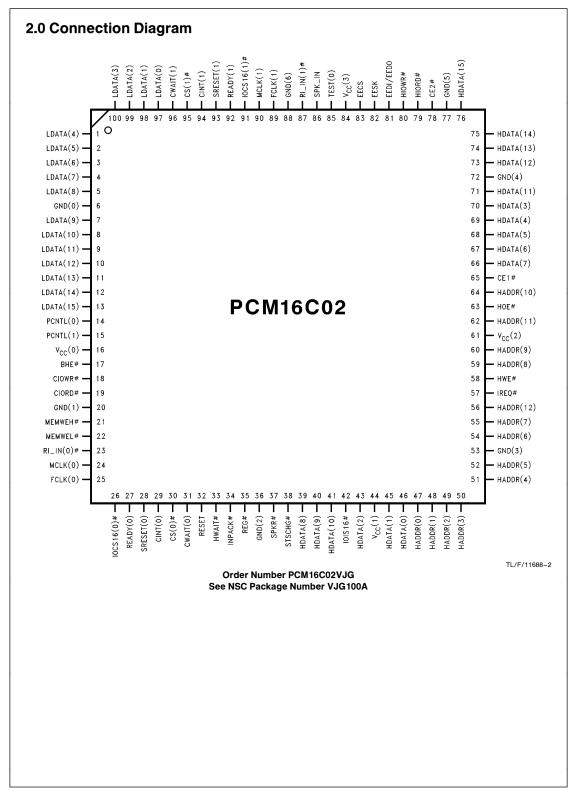

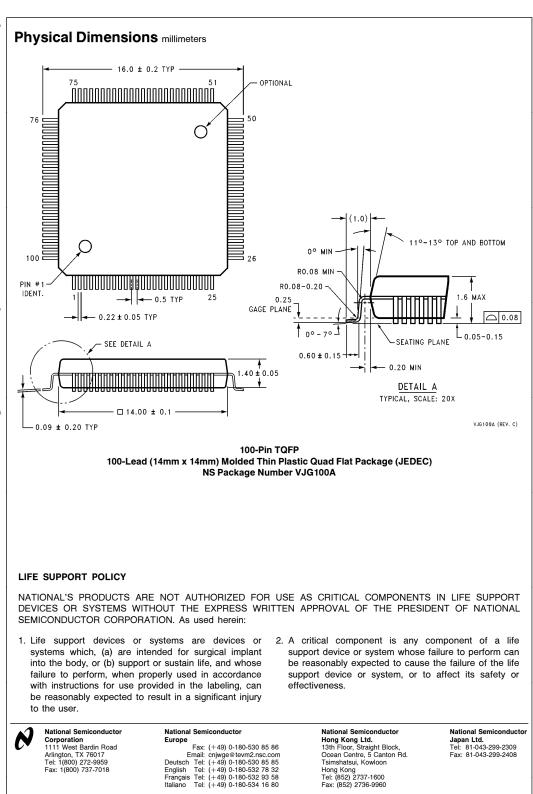

- 100 pin TQFP package

- Function 0 configurable as NAND Flash (NM29N16) interface

- Serial EEPROM Interface compatible with MICROWIRE<sup>TM</sup> EEPROM protocol

- 1-kbyte on chip RAM for attribute memory which shadows the CIS and is used for loading static registers

- Address decoding and control for 2 I/O functions

- Logic to support two interrupt capable ISA like I/O functions on a PC card

- Power management and clock control

- Common memory logic for common memory devices including NOR Flash devices

- Operating voltage range = V<sub>CC</sub>(opr) = 3V~5.0V

PCM 16C02 Configurable Multiple Function PC Card Interface Chip

© 1995 National Semiconductor Corporation TL/F/11688

RRD-B30M125/Printed in U. S. A.

# **Table of Contents**

| GENERAL DESCRIPTION AND PRODUCT FEATURES 1                                                             |

|--------------------------------------------------------------------------------------------------------|

| 1.0 SYSTEM DIAGRAM                                                                                     |

| 2.0 CONNECTION DIAGRAM                                                                                 |

| 3.0 PINOUT DESCRIPTION AND DETAILED TABLES                                                             |

| 4.0 BLOCK DIAGRAM                                                                                      |

|                                                                                                        |

| 5.0 FUNCTIONAL DESCRIPTION                                                                             |

| 5.1 Address Maps                                                                                       |

| 5.1.1 Attribute Memory Addressing                                                                      |

| 5.1.2 I/O Memory Addressing                                                                            |

| 5.1.3 Common Memory Addressing                                                                         |

| 5.2 CIS (Card Information Structure)                                                                   |

| 5.3 Registers                                                                                          |

| 5.3.1 PCM16C02 Specific Registers                                                                      |

| 5.3.2 PC Card Register                                                                                 |

| 5.4 Logic Descriptions                                                                                 |

| 5.4.1 I/O Card Interface Logic for PC Card Host I/O Access                                             |

| 5.4.2 EEPROM Interface                                                                                 |

| 5.4.3 Power Management                                                                                 |

| 5.4.4 NAND Flash (NM29N16) Interface15                                                                 |

| NAND Flash (NM29N16) Mode Register Set (Table 5-2)                                                     |

| NAND Flash (NM29N16) Interface Block Diagram (Figure 5-2)                                              |

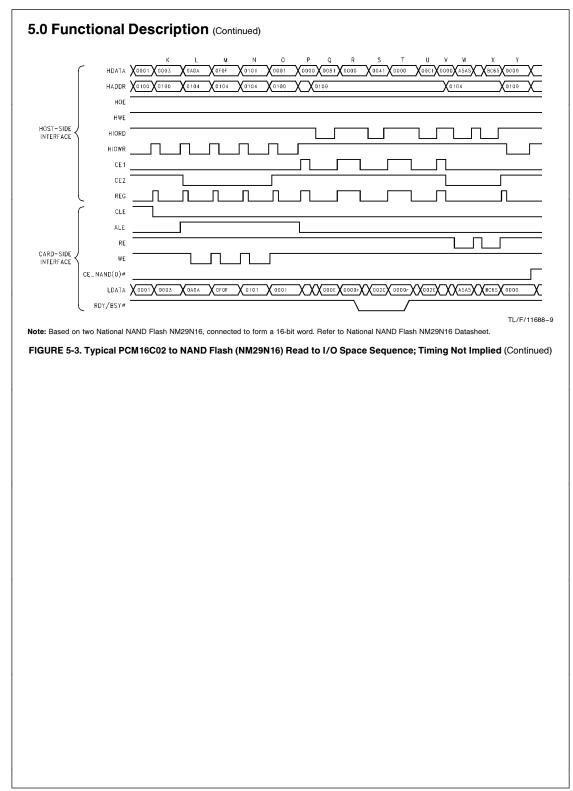

| Typical PCM16C02 to NAND Flash (NM29N16) Read to I/O Space Sequence (Figures 5-3, 5-4 and Table 5-3)18 |

| 6.0 OPERATIONAL MODES                                                                                  |

| 6.1 Initial Setup (Reset) and Configuration                                                            |

| 6.2 Reset Conditions                                                                                   |

| 6.3 Interrupt Control                                                                                  |

| 6.4 Functional Concurrency                                                                             |

| 6.5 16-Bit/8-Bit Operation                                                                             |

| 6.6 Special Testability Modes                                                                          |

| SOFTWARE                                                                                               |

| ABSOLUTE MAXIMUM RATINGS                                                                               |

| RECOMMENDED OPERATING CONDITIONS                                                                       |

| RELIABILITY REQUIREMENTS                                                                               |

| DC ELECTRICAL CHARACTERISTICS                                                                          |

| TIMING SPECIFICATIONS AND DIAGRAMS                                                                     |

| CAPACITANCE                                                                                            |

| TYPICAL APPLICATIONS                                                                                   |

| REFERENCES                                                                                             |

| PHYSICAL DIMENSIONS                                                                                    |

|                                                                                                        |

| Pin<br>Name | Pin<br>Type | Pin<br>No.                         | Level<br>Compatibility | Internal<br>Resistor      | Description                                                                                                                                                                                                                  |

|-------------|-------------|------------------------------------|------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDATA(15:0) | I/O         | 39–41, 43, 45,<br>46, 66–71, 73–76 | TTL 6 mA               | >100k to GND              | PC Card Host Data Bus.                                                                                                                                                                                                       |

| HADDR(12:0) | Ι           | 47–52, 54–56,<br>59, 60, 62, 64    | TTL                    | >100k to GND              | PC Card Host Address Bus.                                                                                                                                                                                                    |

| HOE#        | I           | 63                                 | TTL                    | > 100k to V <sub>CC</sub> | PC Card Host uses this pin to read common or attribute memory space.                                                                                                                                                         |

| HWE#        | I           | 58                                 | TTL                    | > 100k to V <sub>CC</sub> | PC Card Host uses this pin to write common or attribute memory space.                                                                                                                                                        |

| HIORD#      | Ι           | 79                                 | TTL                    | $>\!$ 100k to $V_{CC}$    | PC Card Host uses this pin to read I/O memory space.                                                                                                                                                                         |

| HIOWR#      | I           | 80                                 | TTL                    | $>\!$ 100k to $V_{CC}$    | PC Card Host uses this pin to write I/O memory space.                                                                                                                                                                        |

| REQ#        | 0           | 57                                 | CMOS 6 mA              |                           | Interrupt Request signal to PC Card Hos                                                                                                                                                                                      |

| HWAIT#      | 0           | 33                                 | CMOS 6 mA              |                           | This pin allows the PCM16C02 to insert wait states in a PC Card transaction.                                                                                                                                                 |

| OIS16#      | 0           | 42                                 | CMOS 6 mA              |                           | Low indicates this I/O access to the carries capable of 16-bit access. Function 0 and 1 may use their IOCS16(1:0) $\#$ respectively to control this signal and inform the host if a 16-bit access to the target is feasible. |

| NPACK#      | 0           | 34                                 | CMOS 6 mA              |                           | Signals a valid I/O read.                                                                                                                                                                                                    |

| CE1#        | I           | 65                                 | TTL                    | > 100k to V <sub>CC</sub> | Indicates even address byte. Odd<br>addresses are not released. CE1 # and<br>CE2 # assertion encodings are specified<br>by the PC Card Standard.                                                                             |

| CE2#        | Ι           | 78                                 | TTL                    | > 100k to V <sub>CC</sub> | Indicates odd addressing only. CE1# ar<br>CE2# assertion encodings are specified<br>by the PC Card Standard.                                                                                                                 |

| REG#        | I           | 35                                 | TTL                    | > 100k to V <sub>CC</sub> | Indicates access to attribute memory<br>space or I/O address space. REG # must<br>be high to access common memory<br>space.                                                                                                  |

| RESET       | I           | 32                                 | TTL Schmitt            | $>\!$ 100k to V_{CC}      | Asynchronously resets the PCM16C02.                                                                                                                                                                                          |

| SPKR#       | 0           | 37                                 | CMOS 6 mA              |                           | If Audio bits are set in the Card<br>Configuration Status Register and in<br>either of the Function Configuration<br>Status Registers 0,1, then SPKR# is<br>invert of SPK_IN pin, else SPKR# is<br>high.                     |

| STSCHG#     | 0           | 38                                 | CMOS 6 mA              |                           | STSCHG # is asserted when the<br>Changed bit and SigChg bit are set in the<br>Card Configuration Status Register.                                                                                                            |

|                                                                                                                                                                                                              |             |            |                   | TABLE   | 3-2. Seri        | al EEPROM Inte           | erface Pins                                                                                                                                                                                                                                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------------|---------|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>Name                                                                                                                                                                                                  | Pin<br>Type | Pin<br>No. | Lev<br>Compa      |         | Intern<br>Resist |                          | Description                                                                                                                                                                                                                                   |  |  |  |

| EEDI/EEDO                                                                                                                                                                                                    | I/O         | 81         | TTL 6 n           | пA      |                  | Serial Dat               | Serial Data in from/out to EEPROM.                                                                                                                                                                                                            |  |  |  |

| EECS                                                                                                                                                                                                         | 0           | 83         | CMOS              | 6 mA    |                  | EEPROM                   | Chip Select.                                                                                                                                                                                                                                  |  |  |  |

| EESK                                                                                                                                                                                                         | 0           | 82         | CMOS              | 6 mA    |                  | EEPROM                   | Clock. Freq = $MCLK(0)/32$ .                                                                                                                                                                                                                  |  |  |  |

| Note: The Enable EEPROM function is performed in software by writing to the EEPROM Control Register. The Enable EEPROM bit will default to low (disabled) upon power on. TABLE 3-3. Card-Side Interface Pins |             |            |                   |         |                  |                          |                                                                                                                                                                                                                                               |  |  |  |

| Pin                                                                                                                                                                                                          | Pin         |            | Pin               | Lev     | vel              | Internal                 | Description                                                                                                                                                                                                                                   |  |  |  |

| Name                                                                                                                                                                                                         | Туре        |            | No.               | Compa   | tibility         | Resistor                 | Description                                                                                                                                                                                                                                   |  |  |  |

| LDATA(15:0)                                                                                                                                                                                                  | 1/0         |            | 5, 7–13,<br>7–100 | TTL 6 n | nA               | Hold Circuit<br>(Note 1) | Card-side Data Bus.                                                                                                                                                                                                                           |  |  |  |

| SPK_IN                                                                                                                                                                                                       | I           |            | 86                | TTL Sc  | hmitt            |                          | Input Audio Signal.                                                                                                                                                                                                                           |  |  |  |

| RI_IN(0)#                                                                                                                                                                                                    | I (Note 2)  |            | 23                | TTL Sc  | hmitt            |                          | Ring Indicator for function 0.                                                                                                                                                                                                                |  |  |  |

| RI_IN(1)#                                                                                                                                                                                                    | I           |            | 87                | TTL Sc  | hmitt            |                          | Ring Indicator for function 1.                                                                                                                                                                                                                |  |  |  |

| CIORD#                                                                                                                                                                                                       | 0           |            | 19                | CMOS    | 6 mA             |                          | I/O read signals are passed through from HIORD#<br>according to the expression shown below when a<br>valid address is decoded.<br>CIORD# = HIORD# + REG# + (CE1# * CE2#                                                                       |  |  |  |

| CIOWR#                                                                                                                                                                                                       | 0           |            | 18                | CMOS    | 6 mA             |                          | I/O write signals are passed through from HIOWR #<br>according to the expression shown below when a<br>valid address is decoded.<br>CIOWR # = HIOWR # + REG # + (CE1 # * CE2                                                                  |  |  |  |

| CWAIT(1:0)                                                                                                                                                                                                   | I (Note 2)  | 9          | 96, 31            | TTL     |                  |                          | Card-side transaction wait state inputs.                                                                                                                                                                                                      |  |  |  |

| CS(1:0)#                                                                                                                                                                                                     | 0           | 9          | 95, 30            | CMOS    | 6 mA             |                          | Chip select for each function.                                                                                                                                                                                                                |  |  |  |

| BHE#                                                                                                                                                                                                         | 0           |            | 17                | CMOS    | 6 mA             |                          | Byte high enable. When de-asserted and CS()#<br>asserted, an 8-bit access on LDATA(7:0) is in<br>progress. This holds for both odd and even<br>addresses. When asserted and CS()# asserted, a<br>16-bit access on LDATA(15:0) is in progress. |  |  |  |

| READY(1:0)                                                                                                                                                                                                   | I           | Ş          | 92, 27            | TTL     |                  | $>\!$ 100k to $V_{CC}$   | Indicates that the function is either READY or $\sim$ READY (i.e Busy). This signal is used to assent the Rdy/Bsy# bit in Pin Replacement Registers.                                                                                          |  |  |  |

| CINT(1:0)                                                                                                                                                                                                    | I (Note 2)  | 9          | 94, 29            | TTL Sc  | hmitt            |                          | Card-side interrupt input signals.                                                                                                                                                                                                            |  |  |  |

| SRESET(1:0)                                                                                                                                                                                                  | 0           |            | 93, 28            | CMOS    | 6 mA             |                          | Signals reset to Card-side functions.                                                                                                                                                                                                         |  |  |  |

| IOCS16(1:0)#                                                                                                                                                                                                 | I (Note 2)  | ç          | 91, 26            | TTL     |                  |                          | This pin is asserted during an access to a function that function is capable of a 16-bit access.                                                                                                                                              |  |  |  |

| PCNTL(1:0)                                                                                                                                                                                                   | 0           | 1          | 15, 14            | CMOS    | 6 mA             |                          | Power management control signals or general outputs.                                                                                                                                                                                          |  |  |  |

| MCLK(1:0)                                                                                                                                                                                                    | I           | 9          | 90, 24            | TTL Sc  | hmitt            |                          | Input clocks for function 0 and function 1.                                                                                                                                                                                                   |  |  |  |

| FCLK(1:0)                                                                                                                                                                                                    | 0           | 8          | 89, 25            | CMOS    | 6 mA             |                          | Output clock signals for function 0 and function 1.<br>These may be gated on/off or be a divided value or<br>MCLK(1:0).                                                                                                                       |  |  |  |

| MEMWEH#                                                                                                                                                                                                      | O Tri       |            | 21                | CMOS    | 6 mA             | $>\!$ 10k to V_{CC}      | Common Memory write output for upper byte of dat word.                                                                                                                                                                                        |  |  |  |

| MEMWEL#                                                                                                                                                                                                      | O Tri       |            | 22                | CMOS    | 6 mA             | $>\!$ 10k to $V_{CC}$    | Common Memory write output for lower byte of dat word.                                                                                                                                                                                        |  |  |  |

Note 2: The CWAIT(0), CINT(0), RI\_IN(0) and IOCS16(0) # pins are outputs (O) when function 0 is configured for the NAND Flash (NM29N16) Mode.

|                                                                    |                                     |                         |                   | TABL                 | E 3-4. | . Miscellaneo        | us F | Pins                                                             |

|--------------------------------------------------------------------|-------------------------------------|-------------------------|-------------------|----------------------|--------|----------------------|------|------------------------------------------------------------------|

| Pin<br>Name                                                        | Pin<br>Type                         | Pin<br>No.              | Co                | Level<br>mpatibility |        | Internal<br>Resistor |      | Description                                                      |

| TEST(0)                                                            | I                                   | 85                      |                   | TTL                  | >1(    |                      |      | st pin. This pin should be left disconnected for rmal operation. |

| V <sub>CC</sub> (3:0)                                              | Power                               | 84, 61<br>44, 16        |                   |                      |        |                      | Po   | wer Voltage.                                                     |

| GND(6:0)                                                           | Power                               | 88, 77, 7<br>53, 36, 20 |                   |                      |        |                      | Re   | turn Voltage.                                                    |

|                                                                    |                                     |                         | т.                | ABLE 3-5. N          | AND    | Flash (NM29N         | N16) | Mode Pins                                                        |

| Pin<br>Nam                                                         |                                     | Pin<br>Type             | Pin<br>No.        | Level<br>Compatib    |        | Internal<br>Resistor |      | Description                                                      |

| ALE                                                                |                                     | O<br>(Note 1)           | 31                | CMOS 6 m             | hΑ     |                      |      | Address Latch Enable                                             |

| CLE                                                                |                                     | 0                       | 28                | CMOS 6 m             | ۱A     |                      |      | Command Latch Enable                                             |

| NE#                                                                |                                     | O<br>(Note 1)           | 29                | CMOS 6 m             | hΑ     |                      |      | Write Enable                                                     |

| RE#                                                                |                                     | 0                       | 30                | CMOS 6 m             | ۱A     |                      |      | Read Enable                                                      |

| RDY/BSY                                                            | #                                   | I                       | 27                | TTL                  |        | >100k to V           | СС   | Ready/Busy Input                                                 |

| CE_NANE                                                            | 0 (3:0)#                            | O<br>(Note 1)           | 23, 26,<br>14, 25 | CMOS 6 m             | hΑ     |                      |      | Chip Enables for NAND Flash (NM29N16) Device                     |

| Pin Total:<br>Host-Side                                            | Interface                           | Pins                    | 2                 | 14                   |        |                      |      |                                                                  |

| Host-Side<br>EEPROM<br>Card-Side<br><u>Miscellan</u><br>Total Pins | Interface<br>Interface<br>eous Pins | Pins<br>Pins            | 2                 | 14<br>40<br>2<br>200 |        |                      |      |                                                                  |

| Host-Side<br>EEPROM<br>Card-Side<br>Miscellan                      | Interface<br>Interface<br>eous Pins | Pins<br>Pins            | 1                 | 4<br>10<br>12        |        |                      |      |                                                                  |

# **5.0 Functional Description**

The PCM16C02 provides an integrated solution to interfacing dual function I/O cards with the PC Card Bus. The part has a contiguous 1-kbyte RAM block to store attribute memory. The IC also provides an EEPROM interface to serial EEPROMs that use the MICROWIRE protocol. At a minimum, a 16-kbit serial EEPROM is required. The part allows I/O address windows to be programmed independently for each function.

## 5.1 ADDRESS MAPS

#### 5.1.1 Attribute Memory Addressing

The Attribute Memory space contains both the Card Information Structure (CIS), PC Card Registers for both I/O functions, and PCM16C02 implementation specific registers. Note that PC Card Standard specifies that Attribute memory may only be accessed on even address byte boundaries. The Attribute Memory space fragmentation is shown in Table 5-1.

| Register Description                     | Register Type     | Address (Hex) | EEPRON   |

|------------------------------------------|-------------------|---------------|----------|

| Card Information Structure               | PC Card CIS       | 0x000-0x03E2  | Yes      |

| Pin Polarity Register                    | PCM16C02 Specific | 0x03E4        | Yes      |

| PMGR and Clock Register                  | PCM16C02 Specific | 0x03E6        | Yes      |

| CTERM0 Register                          | PCM16C02 Specific | 0x03E8        | Yes      |

| CTERM1 Register                          | PCM16C02 Specific | 0x03EA        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific | 0x03EC-0x03EE | Yes      |

| Miscellaneous Register                   | PCM16C02 Specific | 0x03F0        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific | 0x03F2-0x03F4 | Yes      |

| Wait State Timer Registers               | PCM16C02 Specific | 0x03F6        | Yes      |

| NAND Flash (NM29N16) Config Register     | PCM16C02 Specific | 0x03F8        | Yes      |

| Reserved for Future Use Register         | PCM16C02 Specific | 0x03FA        | Yes      |

| Watchdog Timer Register                  | PCM16C02 Specific | 0x03FC        | Yes      |

| Reserved for Future Use Registers        | PCM16C02 Specific | 0x03FE        | Yes      |

| Card Information Structure               | PC Card CIS       | 0x0400-0x07FE | Optional |

| ID Register                              | PCM16C02 Specific | 0x1000        | No       |

| EEPROM Control Register                  | PCM16C02 Specific | 0x1002        | No       |

| EEPROM Security Register                 | PCM16C02 Specific | 0x1004        | No       |

| Reserved for Future Use Registers        | PCM16C02 Specific | 0x1006-0x101E | No       |

| Function 0 Configuration Option Register | PC Card           | 0x1020        | No       |

| Function 0 Configuration Status Register | PC Card           | 0x1022        | No       |

| Function 0 Pin Replacement Register      | PC Card           | 0x1024        | No       |

| Unused                                   | PC Card           | 0x1026        | No       |

| Function 0 I/O Event Register            | PC Card           | 0x1028        | No       |

| Function 0 Base A Register               | PC Card Extension | 0x102A        | No       |

| Function 0 Base B Register               | PC Card Extension | 0x102C        | No       |

| Unused                                   | PC Card Extension | 0x102E-0x1030 | No       |

| Function 0 Limit Register                | PC Card Extension | 0x1032        | No       |

| Reserved for Future Use Registers        | PC Card Extension | 0x1034-0x103E | No       |

| Function 1 Configuration Option Register | PC Card           | 0x1040        | No       |

| Function 1 Configuration Status Register | PC Card           | 0x1042        | No       |

| Function 1 Pin Replacement Register      | PC Card           | 0x1044        | No       |

| Unused                                   | PC Card           | 0x1046        | No       |

| Function 1 I/O Event Register            | PC Card           | 0x1048        | No       |

| 5.0 Functional Description (Continued)      |                   |               |        |  |  |  |  |

|---------------------------------------------|-------------------|---------------|--------|--|--|--|--|

| TABLE 5-1. Attribute Memory Map (Continued) |                   |               |        |  |  |  |  |

| Register Description                        | Register Type     | Address (Hex) | EEPROM |  |  |  |  |

| Function 1 Base A Register                  | PC Card Extension | 0x104A        | No     |  |  |  |  |

| Function 1 Base B Register                  | PC Card Extension | 0x104C        | No     |  |  |  |  |

| Unused                                      | PC Card Extension | 0x104E-0x1050 | No     |  |  |  |  |

| Function 1 Limit Register                   | PC Card Extension | 0x1052        | No     |  |  |  |  |

| Reserved for Future Use Registers           | PC Card Extension | 0x1054-0x105E | No     |  |  |  |  |

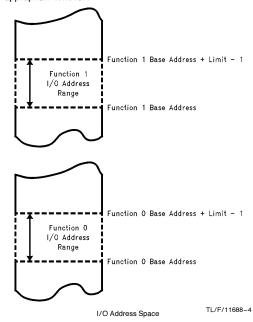

#### 5.1.2 I/O Memory Addressing

National's PCM16C02 uses a pair of address base and limit registers to fragment the I/O Address space. This allows I/O transactions from the PC Card Host to be steered to the appropriate function.

#### FIGURE 5-1. I/O Address Decoding for Two Functions on a PC Card

#### 5.1.3 Common Memory Addressing

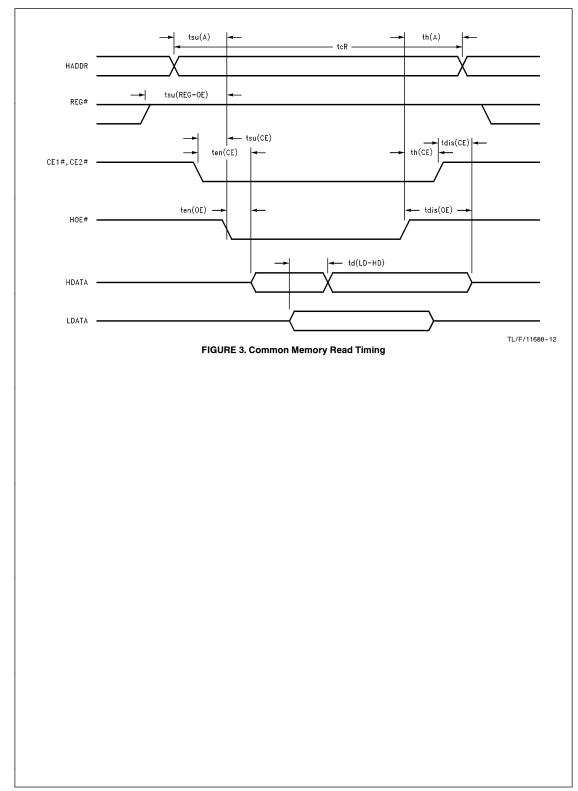

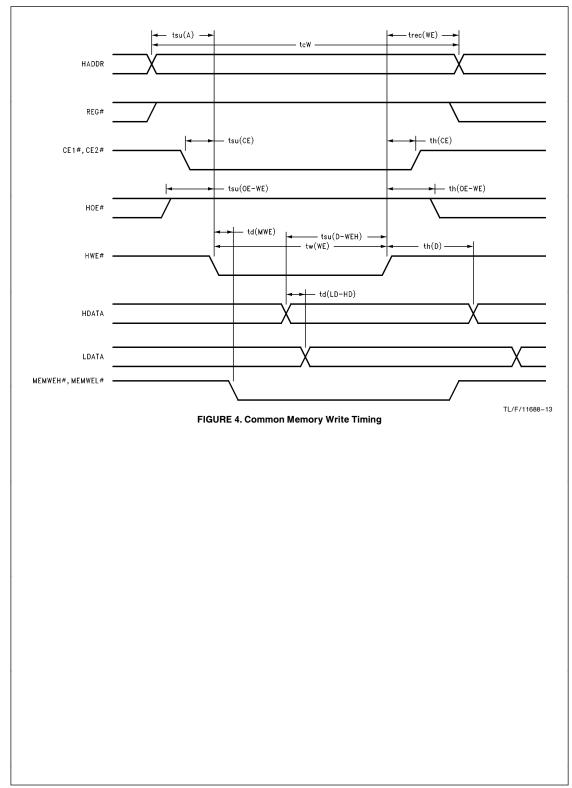

The NSC PCM16C02 does not specifically decode common memory address accesses initiated by the host. Rather, it will pass a host access of HDATA(15:0) through to LDATA(15:0) while passing the address lines around the PCM16C02. In addition, PCM16C02 will pass the host HWE# signal assertion to the MEMWEH#/ MEMWEL# signals appropriately based upon the proper assertion of CE1#, CE2#, and REG#. The assertion of MEMWEH#, MEMWEL#, or both is determined by an 8-bit or 16-bit access as specified in the PC Card Standard.

If a function is mapped to common memory, and requires further address lines, it may use the HADDR(25:13) lines from the PC Card socket as additional address lines around the PCM16C02. The card design is free to use external decoding logic for common memory.

## 5.2 CIS (CARD INFORMATION STRUCTURE)

# [0x000-0x03E2]

[0x03E4]

When the PCM16C02 powers on, the contents of the lower 1-kbyte of the EEPROM are loaded into the device's shadow RAM. This not only allows attribute memory accesses to the CIS, but, it also provides defaults for 9 PCM16C02 specific registers to be loaded. This allows default loading of parameters that are transparent to system or device software. The best use is for the card manufacturer to determine what values these should be and program them into the EEPROM when the CIS is programmed. Either system software such as Card Services/Socket Services or device software may read and parse the CIS by accessing attribute memory on the PC Card. If desired, this software agent may write to the CIS or default EEPROM registers and, if desired, have these new values saved to the EEPROM. The actual contents of the CIS and the static registers is PC Card design dependent.

#### 5.3 REGISTERS

Separate PC Card Registers exist for function (0,1). Each function (0,1) has its own set of Configuration Registers so that each function may be configured and operated on independently from a programming model viewpoint.

## 5.3.1 PCM16C02 Specific Registers

These registers are defined specifically for National's PCM16C02 IC, allowing the PCM16C02 to perform its base functionality of supporting two general functions on a PC Card. These registers are not part of the PC Card Standard.

#### Pin Polarity Register

This register sets the polarity of the card side interface sig-

| nals. | -     |         | -       |     |        |        | -      |

|-------|-------|---------|---------|-----|--------|--------|--------|

| D7    | D6    | D5      | D4      | D3  | D2     | D1     | D0     |

| CIOWR | CIORD | SRESET1 | SRESET0 | BHE | Memls8 | CWAIT1 | CWAIT0 |

**CIOWR, CIORD**—Sets the polarity of the CIOWR # and CIORD # pins respectively. A high indicates active high. The default polarity is active-low.

SRESET1, SRESET0—Sets the polarity of the SRESET(1) and SRESET(0) pins respectively. When this bit is set to a zero (0), the output signal is asserted in the high (1) state. When this bit is set to a one (1), the output signal is asserted in the low (0) state. The bit default is zero (0), i.e. the SRESET() signal is active high.

**BHE**—Sets the polarity of the BHE # pin. A high indicates active-high. The default polarity is active-low.

**Memls8**—This bit is set to one (1) if common memory is organized for 8-bit access. This bit is set to zero (0) if common memory is organized for 16-bit access. The default value is zero (0). This information allows the PCM16C02 to properly access memory using the MEMWEH#, and MEMWEL#, signals.

**CWAIT1, CWAIT0**—When this bit is set to one (1), the PCM16C02 interprets this input signal active when it is low (0). When this bit is set to zero (0), the PCM16C02 interprets this input signal as active when it is high (1). The default bit value is zero (0), i.e. the CWAIT() input signal is asserted high (1).

#### PMGR and Clock Register

The Power Manager (PMGR) and Clock Register is used for controlling the PCNTL(1:0) and FCLK(1:0) pins for power management purposes.

[0x03E6]

Hardware power management is enabled using the Function Configuration Option Register's PMGMT\_EN(D3) bit. Its use is intended for functions that can be sequenced on/ off or into idle or sleep states with a quick (< 10  $\mu$ s) response time when powered on again. That is, the function may use its CWAIT() signal to extend a transaction that caused the PCM16C02 to turn it on. Use of the READY() signal in a dynamic hardware power managed environment to set the RRdy/Bsy bits in order to achieve > 10  $\mu$ s response times for power on is not guaranteed to work since system software may not inspect the RRdy/Bsy bit in all such instances.

| D7      | D6   | D5    | D4       | D3             | D2   | D1    | D0       |  |

|---------|------|-------|----------|----------------|------|-------|----------|--|

| F1CLKEN | DIV1 | PPOL1 | PCNTL(1) | <b>F0CLKEN</b> | DIV0 | PPOL0 | PCNTL(0) |  |

F1CLKEN, F0CLKEN—If set, these enable the pins FCLK(1:0) to receive a clock out. If clear, the respective pins FCLK(1:0) will be forced low. These are set and cleared by software if desired or statically loaded upon card power up from the EEPROM.

**DIV1, DIV0**—If set, the respective clock output from FCLK(1:0) will be divided by 32 from the input clocks MCLK(1:0). If clear, the clock output FCLK(1:0) will equal the respective clock input MCLK(1:0). These are set and cleared by software if desired or statically loaded upon card power up from the EEPROM.

**PPOL1, PPOL0**—Sets the active polarity of the PCNTL(1) and PCNTL(0) signals such that the function is asserted. If PPOL is set to zero (0), PCNTL() is asserted when in the high state. If set to one (1), PCNTL() is asserted when in the low state. The default is set to zero (0), i.e. PCNTL() defaults to active high.

**PCNTL(1), PCNTL(0)**—These bits control the pins PCNTL(1) and PCNTL(0) respectively. If hardware power management is not selected in the Function Configuration Option Register's Function Configuration Index, then these bits may be used as output signals by software for general purposes. If the hardware power management configuration is selected, these bits are de-asserted (defined by PPOL1, 0) when the PCM16C02's CTERM 1 or 0 counter expires. These bits will be asserted if a transaction occurs to the function through an I/O window or the function requests service by issuing a RI\_IN(). In either strategy, software may always write and read back these bits. These bits default to zero (0) during power-on until the PMGR and Clock Register can be loaded from the EEPROM.

#### CTERM Registers 0, 1

[0x03E8, 0x03EA]

These registers are used to define the value of function 0's and function 1's power time-out counters respectively. If a function's power time-out counter expires, the PCNTL bit for that function in the PMGR and Clock Register is de-asserted. This will occur if a function is in-active long enough for it's power time-out counter to expire. Active is defined as having either an I/O access from the host or receiving a RI\_I()#. Devices that may operate for long periods of time without a host I/O access should follow a software controlled power management strategy that uses the PwrDn bits in the Function Configuration Status Registers 0, 1.

Each function's terminal counter is 8 bits wide and counts at a rate of  $MCLK(0)/(2^{17})$ . For example, if the MCLK(0) frequency is 30 MHz the device can be programmed to timeout between 0.0s to 1.114s. The general formula is:

#### Time = $(1/mclk(0)) * 2^{17} * N$ , where N = {0, 1, 2, ..., 255}

For a 5 MHz MCLK(0) frequency, the equation is:

Time = N (26.2144 ms) where N =  $\{0, 1, 2, \dots, 255\}$

**Note:** A value of zero implies the function is powered down.

#### Miscellaneous Register

|        | •   |     |                 |

|--------|-----|-----|-----------------|

| D7     | D6  | D5  | D4-D0           |

| FastEE | RFU | RFU | EEPROMStartAddr |

FastEE—If this bit is set to one (1), then the clock used to access the EEPROM shall be MCLK(0)/2. If this bit is set to zero (0), the clock used to access the EEPROM shall be MCLK(0)/32.

**EEPROMStartAddr**—This field contains a starting address for EEPROM read or write access. This is ordinarily set to zero and is used for debug/test purposes.

#### Wait State Timer Register

[0x03F6]

[0x03F0]

This register allows the insertion of default wait states from the PCM16C02 using HWAIT #. It is intended to be used in situations where either the function is too slow to respond with a CWAIT() or the unique wait timing constraints between the system and PC Card design necessitate a default wait state.

| D7-D4    | D3-D2     | D1-D0     |

|----------|-----------|-----------|

| Reserved | Func1Wait | Func0Wait |

**Func1Wait, Func0Wait—**This value is the number (0, 1, 2, or 3) of MCLK(0) time periods that the PCM16C02 will assert HWAIT# during a valid access to a particular function. For Zero wait states, program these values to 00b.

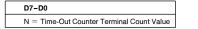

| NAND Flash ( | (NM29N16)      | Configuration | Register [0x03]  | F81      |

|--------------|----------------|---------------|------------------|----------|

| INAND Flash  | 141012 314 10) | ooninguration | Tregister [0x00] | <b>U</b> |

| D7-D4    | D3           | D1          | D0 |         |

|----------|--------------|-------------|----|---------|

| Reserved | mem_io_space | NAND_IOCS16 | BC | NAND_EN |

|          |              |             |    |         |

mem\_io\_space—Mem\_io\_space selects whether NAND Read/Write strobes are generated by accesses to common memory space or I/O space. When Function 0 is configured for NAND Flash (NM29N16) Mode, if mem\_io\_ space is set to 0, NAND (NM29N16) Read/Write strobes are generated by an I/O access to the function 0 base address + 4. If mem\_io\_space is set to 1, Read/Write strobes are generated by any read/write access to common memory.

NAND\_IOCS16—When Function 0 is configured for NAND Flash (NM29N16) Mode, D2 replaces the external pin IOCS16(0) # to allow the host to know if the NAND (NM29N16) is organized for 8- or 16-bit accesses. If Function 0 is NOT configured for NAND Flash (NM29N16) Mode, the bit performs no function. This register gets downloaded during EEPROM reads.

**BC**—If set to zero (0), PCM16C02 will assert only one of the four external CE # pins at a time, (based on the value of bits D0 and D1 in the Device Select Register), allowing up to four unique enable control lines. If set to one (1), PCM16C02 will place on the external CE # lines the exact binary number placed in bits D0–D3 of the Device Select Register. This will allow external decoding to produce up to 15 unique CE # control lines which can control up to 30 pairs of NAND Flash (NM29N16) devices. (Reference table in Section 5.4.4 for details.)

**NAND\_EN**—This bit, if set to one (1), configures function 0 as a NAND Flash (NM29N16) interface (see Section 5.4.4 for specific function details). If set to zero (0), function 0 assumes normal I/O interface functionality.

| Watchdog Tim | e-Out Register   | [0x03FC] |

|--------------|------------------|----------|

| D7           | D6               | D5-D0    |

| RFU          | Wait_Tout Enable | RFU      |

**Wait\_Tout Enable**—When this bit is set to a one (1), the HWAIT # time-out watchdog timer is enabled. In addition, the ability to set *Intr* in the Function Configuration Option Register 0, *Intr* in the Card Configuration Register, and IREQ # is enabled once the watchdog timer expires. The watchdog timer may expire if HWAIT # is asserted for more than approximately 11.2  $\mu$ s when MCLK(0) is set to 20 MHz. This prevents the system from hanging due to prolonged HWAIT # assertions. If this bit is reset to zero (0), Wait\_Tout and its associated interrupt capability is disabled during HWAIT assertions.

#### ID Register [0x1000]

This read only register provides the software with IC revision information.

| D7-D3                  | D2-D0                |

|------------------------|----------------------|

| PCM16C02 Code = 00010b | Revision Code = 000b |

| ·                      |                      |

**NSC PCM16C02 Code**—This code will may be used to identify the NSC PCM16C02 IC. The value of bits D7-D3 of this register is 00010, which when appended to the three bits of the revision code produce: 00010 xxx; which is 1x hex.

**Revision Code**—This will uniquely identify the silicon version of the PCM16C02 IC as 000b.

## EEPROM Access

In order to avoid accidental EEPROM overwrite, the PCM16C02 utilizes two registers that must be written with the proper byte sequence in order to enable EEPROM writes. In order to initiate an EEPROM write, the following register write sequence must be executed:

| Register        | Attribute Register Address | Hex Data |

|-----------------|----------------------------|----------|

| EE Control Reg  | 1002                       | 2E       |

| EE Security Reg | 1004                       | B7       |

| EE Control Reg  | 1002                       | 91       |

#### Failure to initiate the exact sequence will disable writes regardless of the value placed in the WriteEEPROM or EEPROMWriteEn bits of the EEPROM Control Register.

#### EEPROM Control Register

[0x1002]

This register (in conjunction with the EEPROM Security Register for writes) controls reading and writing the EEPROM as well as the EEPROM enable.

| D7          | D6         | D5-D1    | D0            |

|-------------|------------|----------|---------------|

| WriteEEPROM | ReadEEPROM | Reserved | EEPROMWriteEn |

WriteEEPROM—When set, this tells the EEPROM controller to copy the contents of the PCM16C02 Shadow RAM to the EEPROM, provided the proper write security sequence listed above has been executed. Once the EEPROM write has completed, the EEPROM controller clears this bit.

**ReadEEPROM**—When set, this tells the EEPROM controller to copy the contents of the EEPROM to the shadow RAM. Once done, the EEPROM controller clears this bit. Any data modified in the Shadow RAM that has not first been written back to the EEPROM will be lost. The EEPROM may be read independent of the value in the EEPROMWriteEnable bit.

**EEPROMWriteEn**—This must be set to allow EEPROM writes. If clear, the EEPROM may not be written. The default value at reset is low. The EEPROM may be read independent of the value of this bit.

- Note 1: Upon power-up, the PCM16C02 EEPROM controller copies the entire contents of the lower 1 kbytes of the EEPROM into the Shadow RAM independent of writing to the EEPROM Control Register.

- Note 2: The PCM16C02 EEPROM controller stores data in a 16-bit organized EEPROM in low/high format. Although Attribute Memory is on even byte boundaries only, the entire EEPROM's address space is used. This eliminates waste of EEPROM memory. Therefore the Attribute space used by the Shadow RAM is double the actual size of the EEPROM. For example, if a 16-bit EEPROM will be shadowed at Attribute location 0x0000 and the high byte will be shadowed at Attribute location 0x0002. The low byte at EEPROM word 1 will be shadowed to Attribute location 0x0004, etc.

#### **EEPROM Security Register**

[0x1004]

This register in conjunction with the EEPROM Control Register is used to prevent accidental EEPROM overwriting. When written in the proper sequence as outlined above with hex data B7, it allows EEPROM write access.

#### 5.3.2 PC Card Register

#### **Function Configuration Option Registers 0,1**

| 40] | [0x1020,0x104                |         |        |

|-----|------------------------------|---------|--------|

|     | D5-D0                        | D6      | D7     |

|     | Function Configuration Index | LevIREQ | SRESET |

**SRESET**—If the host sets this field to one (1), the PCM16C02 shall place the given function in the reset state. When the host returns this field to zero (0), the function shall enter the same unconfigured, reset state as it does following a power-up and hardware reset. Note that SRESET does not reset the PCM16C02 thus the Attribute memory is not reloaded.

LevIREQ—When the PCM16C02 is being used as a PC Card I/O interface and this field is set to one (1), the PCM16C02 shall generate Level Mode interrupts for the function using the IREQ # signal. If the PCM16C02 is being used as a PC Card I/O interface and this field is set to zero (0), the PCM16C02 shall generate Pulse Mode interrupts for the function. Use of Level Mode interrupts for both functions when the PCM16C02 is configured for multi-function operation is strongly recommended. Since there is only one PC Card Bus interface, the LevIREQ bits for Function 0 Configuration Option Register and Function 1 Configuration Option Register are aliased. The PCM16C02 will also only allow a write to the LevIREQ bit value to change the interfaces Interrupt level mode if the given function is configured using ConfFunc and interrupts are enabled using EnbIREQ.

In addition, the PCM16C02 provides an enhanced interrupt protocol scheme described by the IntrReset bit in the Function Configuration Status Registers 0, 1. The PCM16C02 implements a shared interrupt scheme in multi-function operation. Single function configurations may use Level Mode or Pulse Mode interrupt schemes. Pulsed Mode interrupt width is given by:

## TwidthIREQ = 16/(FreqMCLK(0))

Using MCLK(0) from 5 MHz-30 MHz will insure pulse widths from 0.53  $\mu$ s-3.2  $\mu$ s which exceed the 0.5  $\mu$ s minimum requirement for the PC Card Standard.

Function Configuration Index—When the host system sets this field to the value of the Configuration Entry Number field of a Configuration Table Entry Tuple, the function shall enter the configuration described by that tuple. This field shall be reset to zero (0) by the PCM16C02 when the host sets the SRESET field to one (1) or the host asserts RESET. If this field is set to zero (0) explicitly by the host or implicitly by SRESET or RESET, the function shall use the Memory Only interface and I/O cycles from the host shall be ignored by the function.

The following configurations are supported by the Function Configuration Index 0, 1:

**ConfFunc (D0)**—If this is set to one (1), then the PC Card is configured for that function.

EnbBase\_Limit (D1)-If this is set to a one (1), the base and limit register pair for the function is enabled. That is, the PCM16C02 will only pass I/O transactions whose address falls within the I/O window specified by the base and limit pair. If this is set to a zero (0), the PCM16C02 will not test transactions' addresses against the base and limit pair for that function and will, therefore, pass all I/O transactions to the function. For single function operation, the EnbBase Limit would be enabled for operation with host controllers that support overlapping windowing and the INPACK# signal. For host controllers that do not support INPACK # but are capable of windowing granularity required for the function, EnbBase\_Limit may be set to zero (0) so that all I/O transactions are passed to the function. For multifunction operation, the EnbBase\_Limit bits for both functions should be set to one (1).

**EnbIREQ (D2)**—When the PCM16C02 is being used as a PC Card I/O interface and this field is set to one (1), the PCM16C02 shall enable this function to interrupt the host using the IREQ# signal. Normally this bit would be set to one (1). In environments where the function's software driver will use a polling technique for status information, this bit could be set to zero (0) to disable interrupts from that function.

**PMGMT\_\_EN (D3)**—This bit, if set to a one (1), enables the hardware power management controller to control the PCNTL() pin for that function. See the PMGR and Clock Register description.

TEST\_MODE(D4) (For Function 1 ONLY!)—The TEST\_MODE bit is defined for function 1 only and *MUST* be set to zero (0) for function 1 to operate in the normal I/O mode (default state). TEST\_MODE is for NSC factory use only. Normal card functionallity is not guaranteed in TEST\_MODE.

#### (D5) is reserved.

#### Function Configuration Status Registers 0,1

#### [0x1022,0x1042]

These PC Card registers are used for function control/ status information.

| D7      | D6     | D5    | D4       | D3    | D2    | D1   | D0        |

|---------|--------|-------|----------|-------|-------|------|-----------|

| Changed | SiaCha | IOis8 | Reserved | Audio | PwrDn | Intr | IntrReset |

**Changed**—If one or more of the state change signals in the Function Pin Replacement Register are set to one (1), the PCM16C02 shall set this field to a one (1). If the PCM16C02 is being operated as a I/O interface, (PC Card using I/O Interface), and both the Changed and SigChg fields are set to one (1), the PCM16C02 shall assert the STSCHG# signal. If the PC Card, and hence PCM16C02, is not using the I/O interface, this field is undefined and ignored.

SigChg—This field serves as a gate for asserting the STSCHG signal. If the PCM16C02 is operated as an I/O interface, and both the Changed and SigChg fields are set to one (1), the PCM16C02 shall assert the PC Card STSCHG # signal. If the PCM16C02 is operated as an I/O interface and this field is reset to a zero (0), the PCM16C02

shall not assert the STSCHG # signal. If the PCM16C02 is not operated as an I/O interface, this field is undefined and should be ignored. Either Function Configuration Status Register 0 or 1 is capable of asserting STSCHG # if it satisfies the above requirements.

**IOis8**—When the host can only provide I/O cycles with an 8-bit D0–D7 path, the host shall set this bit to a one (1). The card is guaranteed that accesses to 16-bit registers will occur as two byte accesses rather than a single 16-bit access. This information is useful when 16-bit and 8-bit registers overlap.

Audio—Sampling of the signal SPK\_IN and control of SPKR # is accomplished using the Audio bit. SPKR # will equate to SPK\_IN anytime either of the Audio bits is set to one (1) and the function is configured.

**PwrDn**—When the host sets this field to one (1), the PCM16C02 shall set the given function to a power-down state by de-asserting the PCNTL() signal for that function. While this field is a one (1), the host shall not access the function on the PC Card. The host shall return this field to zero (0) before attempting to access the function. The system shall not place the card into a power-down state while the card's RDY/BSY# line is in the low (Busy) state. All input/output signals particular to the function are TRI-STATE.

Intr—If the function is requesting interrupt servicing (CINT() asserted), the PCM16C02 shall set this field to one (1). The PCM16C02 shall reset this field to zero (0) when the interrupt request has been serviced (CINT() de-asserted).

IntrReset-If IntrReset is set to zero (0), Intr shall be set to one (1) when an interrupt condition occurs and shall be reset to zero (0) when the interrupt condition has been serviced. A write to the Intr bit will do nothing. If IntrReset is set to one (1), Intr shall be set to one (1) when an interrupt condition occurs (CINT() pin) and be cleared to a zero (0) when the interrupt (CINT() pin) is serviced, however, a write of value zero (0) to any FCSR's Intr bit where IntrReset is set to one (1) shall cause the PCM16C02 to evaluate all CINT() signals and generate another interrupt to the system if an interrupt is pending. Note that the write of zero (0) to any FCSR's Intr bit where IntrReset is set to one (1) is an indication to the PCM16C02 that it must evaluate all CINT() pins and generate a specified pulse to the system on the IREQ line. This protocol will work in either pulse or level mode (state of aliased LevIREQ controlling IREQ # PC Card signal mode). Functions operate by asserting their CINT() signal when an interrupt condition occurs. If interrupts are enabled for a given function, then that function's CINT() pin, when asserted, may generate an interrupt within the PCM16C02.

National's PCM16C02 has access to an internal interrupt line that represents the OR of all interrupts that have been asserted and enabled. Since functions use a level mode interrupt approach, this OR'd internal interrupt signal represents a level mode ORing of the interrupts. When the OR'd signal is asserted, the PCM16C02 will generate either a pulse mode or level mode interrupt on the IREQ# line. Before EOI processing by the functions ISR, the function's interrupt condition will be cleared and its CINT() pin will deassert. If no other interrupts are being asserted, the PCM16C02's internal line will de-assert IREQ#. If other interrupts are pending, the internal line remains asserted (and hence IREQ#). Since the standard PC compatible interrupt controller requires a positive edge to trigger an interrupt system software based on using the IntrReset protocol for the PCM16C02 may write a zero (0) to any Intr bit where IntrReset is set to one (1) after EOI processing is done. This will cause the PCM16C02 to generate a pulse on the IREQ# line if any CINT() that's enabled is still asserted. In other words, if the internal line is still asserted at this point. If in pulse mode, this is a single pulse that goes high-low-high with at least 0.5  $\mu$ s low time. If in level mode, this pulse is a low-high-low pulse to trigger the interrupt controller and then remain low (IREQ# asserted) and be maintained low by the level mode interrupt. This protocol solves both the need for two positive edges during level mode interrupts when an interrupt occurs during an interrupt that do not overlap during two interrupt events close in time.

Note: For consistency, the PCM16C02 will alias all IntrReset bits on a write to insure that both functions operate in the same mode. Also, the Intr bits are aliased on writes as an indicator to the PCM16C02 that interrupt status must be checked and pulses generated per the above protocol.

#### Function Pin Replacement Registers 0,1 [0x1024,0x1044]

These PC Card registers replace the signals missing from a PC Card Memory Card interface due to using the PC Card I/O interface.

| D7    | D6    | D5       | D4     | D3    | D2    | D1       | D0     |

|-------|-------|----------|--------|-------|-------|----------|--------|

| CBVD1 | CBVD2 | CRdy/Bsy | CWProt | RBVD1 | RBVD2 | RRdy/Bsy | RWProt |

CBVD1,CBVD2-These bits are not implemented.

**CRdy/Bsy**—This bit is set to one (1) when RRdy/Bsy bit changes state. The value of 02h must be written to the Pin Replacement Registers in order to clear the CRdy/Bsy bit. **CWProt**—This bit is not implemented.

**RBVD1,RBVD2,RRdy/Bsy,RWProt**—Only RRdy/Bsy is implemented for each function. This bit reflects the state of the functions READY() input pin on the PCM16C02.

| Function I/O Event Registers 0,1 | [0x1028,0x1048] |

|----------------------------------|-----------------|

|----------------------------------|-----------------|

|          |       | , -      | , -    |

|----------|-------|----------|--------|

| D7-D5    | D4    | D3-D1    | D0     |

| Reserved | RIEvt | Reserved | RIENAB |

**RIEvt**—PCM16C02 latches a one (1) to the Card I/O Event Register's RIEvt bit when  $R|_{IN}() \neq pin$  is asserted for Function 0 or Function 1 provided the RIEnab bit is set. The value of 10h must be written to the I/O Event Register in order to clear the RIEvt bit (D4).

**RIEnab**—When this bit is set to a one (1), a latched value of one (1) on the RIEvt bit shall cause the Changed bit in the Function's Configuration Status Register to be set to a one (1).

## Function Base Address Registers 0,1

[0x102A-0x102C,0x104A-0x104C] The base address for each function is comprised of 4 bytes (13 bits implemented) that specify the base I/O address from which to begin decoding for chip selection of a particular function.

#### Base A Register

| D7-D0 |  |

|-------|--|

| 07-00 |  |

|       |  |

Byte 0 (Base Address bits 7-0) of 13-bit Address

This register comprises the low 8 bits of the base address for the Function I/O decode selection.

#### **Base B Register**

D7-D0

Byte 1 (Base Address bits 12-8) of 13-bit Address

This register comprises the next 5 bits of the base address for the Function I/O decode selection. Note that PCM16C02 has a maximum I/O address decode space of 8k (13 address lines decoded).

#### **Base C Register**

| D7-D0  |

|--------|

| Byte 2 |

This register is unused in the PCM16C02.

#### **Base D Register**

| D7-D0  |

|--------|

| Byte 3 |

This register is unused in the PCM16C02.

Using Base A and Base B Registers for each function supported by the PCM16C02 allows a 13-bit base address to be specified for I/O decoding and selection of function 0 and function 1 separately.

#### Function Limit Address Registers 0,1 [0x1032,0x1052]

The value placed in this register is a bit mask used to indicate which address bits the PCM16C02 will not decode. A value of one (1), indicates that the PCM16C02 will not decode the corresponding address line. A value of zero (0) indicates the PCM16C02 shall decode the corresponding address line. For proper operation, only contiguous sequences of ones (1) starting at bit 0 and moving leftward are allowed. For example, 00001001 is illegal whereas 00000111 is legal. This implies that the window size must be equal to a value of 2 raised to a integer power.

## D7-D0

#### Limit Address Size

The following Limit Address Size values are legal and correspond to a particular I/O address decoding window size.

| Limit Address<br>Size Value | Window Size                                                                                                                |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 0000 0000                   | NULL. Do not pass any I/O transactions to function<br>unless base and limit checking is disabled in the<br>function's COR. |

| 0000 0001                   | 2 bytes                                                                                                                    |

| 0000 0011                   | 4 bytes                                                                                                                    |

| 0000 0111                   | 8 bytes                                                                                                                    |

| 0000 1111                   | 16 bytes                                                                                                                   |

| 0001 1111                   | 32 bytes                                                                                                                   |

| 0011 1111                   | 64 bytes                                                                                                                   |

| 0111 1111                   | 128 bytes                                                                                                                  |

| 1111 1111                   | 256 bytes                                                                                                                  |

Note: The window created using the Base Register in conjuction with the Limit Register is naturally aligned to the size of the window (as specified by the Limit Register) and not to the value programmed in the Base Register. For example:

| Base Register | Limit Register | Window Range | Aligned to Base |

|---------------|----------------|--------------|-----------------|

| 0374h         | 07h            | 0370h-0377h  | No              |

| 03F8h         | 07h            | 03F8h-03FFh  | Yes             |

#### 5.4 LOGIC DESCRIPTIONS

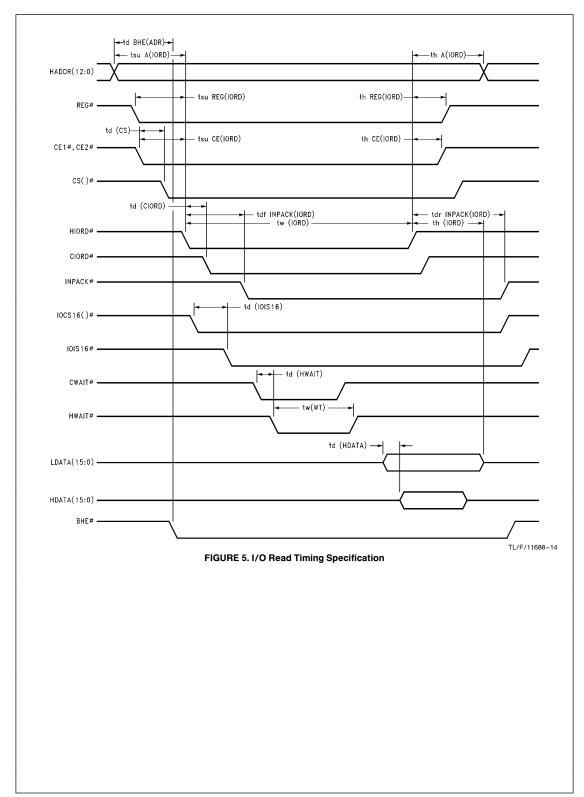

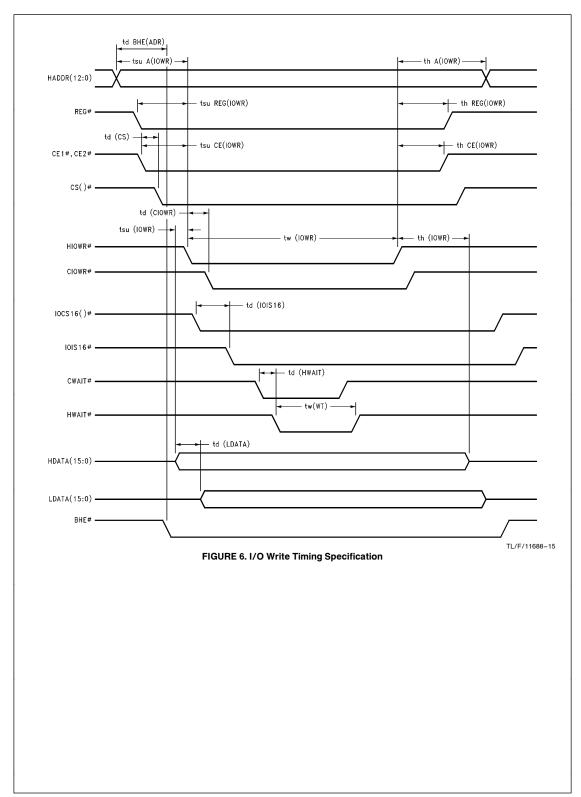

#### 5.4.1 I/O Card Interface Logic for PC Card Host I/O Accesses

This block of logic generates card-side bus control and the appropriate chip-select signals based on the inputs from the PC Card host bus. The block's main function is I/O address decoding and operates with the PC Card Standard. The Function's Base Registers 0,1 and Function Limit Registers 0,1 determine the location and size of the I/O window. Once set up, only PC Card accesses to the given function's I/O window will be passed to the device. All control signals are generated for the device for both read and write transactions. The selection of which function receives the PC Card transaction is implicit in the PC Card address and the particular I/O window the address falls within.

When a function is not selected, CIORD# and CIOWR# are forced to the de-asserted state. The chip selects CS(0)# and CS(1)# are held de-asserted for that port as well. Once a valid PC Card access (read or write) occurs, the control and chip select signals become active.

The condition for an I/O read when a valid address is decoded is:

CIORD # = HIORD # + REG # + (CE1 # \* CE2 #)

The condition for an I/O write when a valid address is decoded is:

CIOWR # = HIOWR # + REG # + (CE1 # \* CE2 #)

#### 5.4.2 EEPROM INTERFACE

The PCM16C02 Attribute memory is stored in an external serial CMOS EEPROM that uses the MICROWIRE protocol. Connection to the EEPROM is accomplished using standard serial EEPROM interface. The PCM16C02 is compatible with 16-bit EEPROM data organizations. Data transfer is synchronized using the EESK signal whose frequency is equal to MCLK(0)/32. (This allows  $f_{\mbox{EESK}}=\,937.5\mbox{ kHz}$  using f<sub>MCLK(0)</sub> of 30 MHz. Most industry standard EEPROMs specify a maximum clock frequency of 1 MHz.) Data on EEDI/EEDO is latched on the rising edge of EESK. EESK is only generated when the EEPROM is accessed, otherwise it is low. Muxing EEDI with EEDO on the PCM16C02 allows the DI and DO pins on the National NM93C86 EEPROM to be tied together, however, it is recommended that a resistor be placed between pins DI and DO on the serial EEPROM to reduce noise (refer to NSC Memory Databook Apps. Note AN-758. Figure 6).

Read access to the EEPROM is accomplished after a reset or power-up sequence. The PCM16C02 will not allow any accesses to the attribute memory (by asserting IREQ# to act as a PC Card busy signal) until the EEPROM has been read and placed in the shadow RAM attribute space on the PCM16C02 IC. Once the read sequences are completed, IREQ# will be de-asserted and the host will be allowed to access the attribute memory space.

Note: Until the PCM16C02 is configured, which requires the EEPROM be read, it is in a memory only interface. During this time, IREQ# is defined as RDY/BSY#.

In order to avoid accidental EEPROM overwrite, the PCM16C02 utilizes two registers that must be written with the proper byte sequence in order to enable EEPROM writes. In order to initiate an EEPROM write, the following register write sequence must be executed:

| Register        | Attribute Register Address | Hex Data |

|-----------------|----------------------------|----------|

| EE Control Reg  | 1002                       | 2E       |

| EE Security Reg | 1004                       | B7       |

| EE Control Reg  | 1002                       | 91       |

The PCM16C02 will then write the contents of the Shadow RAM into the EEPROM. Older data in the EEPROM is lost. During the write back, no accesses to attribute memory are allowed. The EEPROM write back cycle consists of three sequential operations: write enable, write, write disable. The PCM16C02 will not initiate write back from the Shadow RAM to the EEPROM during a power down condition. Any modification to the CIS to be saved requires the system to initiate a write back.

All EEPROM read/write operations follow a similar sequence: a start bit, some op code, address and data bits. Prior to any operation, EECS is set high. If the RESET signal is pulsed, EEPROM writes are immediately disabled.

EEPROM reads can be initiated by simply setting the ReadEEPROM bit (D6), regardless of the state of any other bits in the EEPROM Control Register (0x1002). In order to initiate EEPROM writes, however, the Write Enable sequence listed above must be executed. Simply setting the WriteEEPROM and EEWriteEnable bits in EEPROM Control Register won't initiate a write.

#### 5.4.3 Power Management

The PCM16C02 supports a hardware power management strategy. This allows the device to switch power on and off based on the activity of each individual function. Each function has a time-out counter set using the CTERM 0,1 Registers. If there has been no PC Card Host activity to the given functions I/O window and no ring indicate occurs, the function will be powered down. This is done by de-asserting the PCNTL() bit (based on its programmed polarity) in the PMGR and Clock Register. Any activity from the function will cause the PCM16C02 to assert these bits to provide full power to the function and start the clocks. If this activity was a host transaction, the PCM16C02 will assert HWAIT # for the target function until the PCM16C02 asserts the PCNTL() signal to power on the function and for 8 FCLK()'s. This gives the function 8 FCLK()s to either power on and respond or at least begin asserting its CWAIT() line. Wake-up activity could be defined as a PC Card transaction to the device, a RI\_IN()# if enabled, or a CINT() if enabled.

The PCM16C02 can operate in a V<sub>CC</sub> range of 5.0V to 3.0V which allows the overall power consumption of the PCM16C02 to be reduced by operating the PCM16C02 in a 3.0V environment.

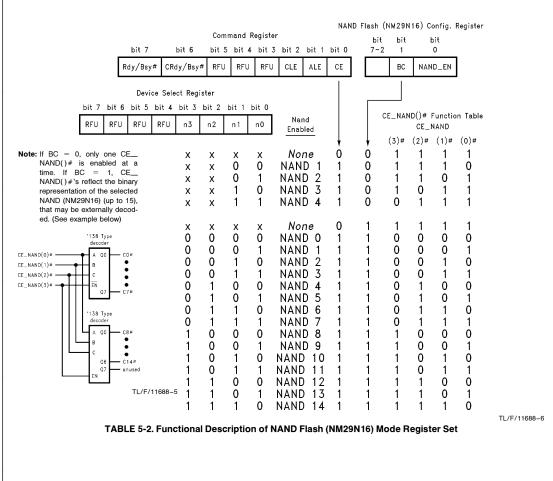

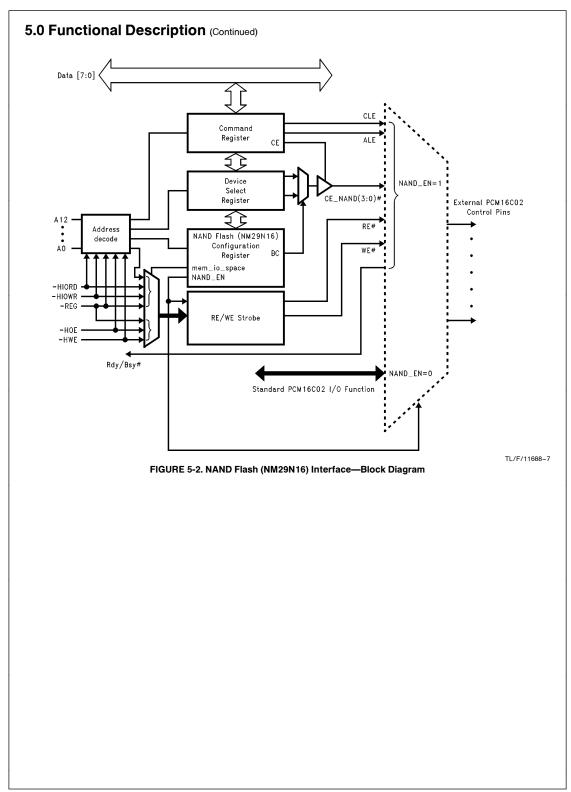

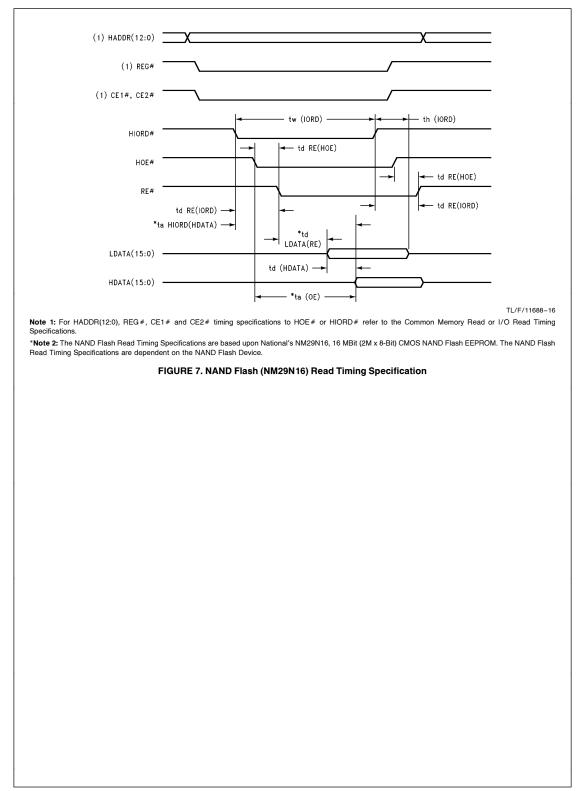

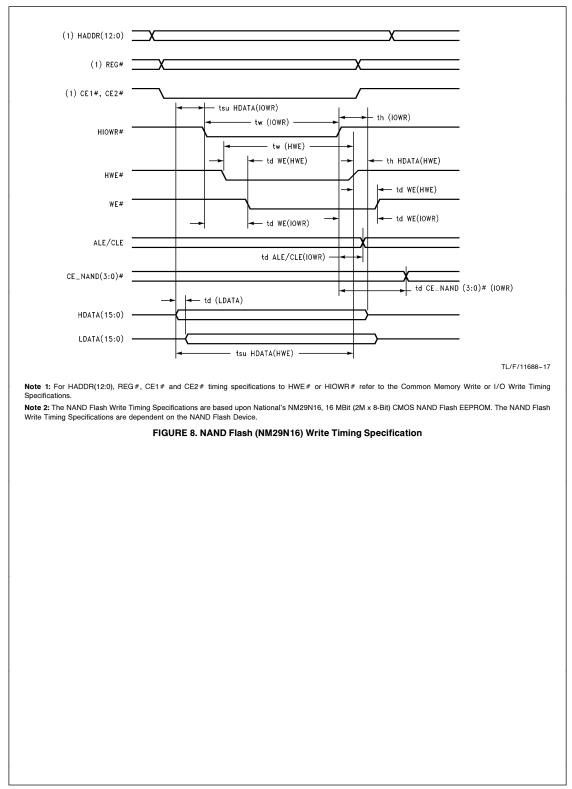

## 5.4.4 NAND Flash (NM29N16) Interface

The PCM16C02 supports NAND Flash (NM29N16) memory devices by allowing function 0 to be configured as a NAND Flash (NM29N16) interface. Function 0 can be configured as a NAND Flash (NM29N16) interface by setting bit D0 in the NAND Flash (NM29N16) Configuration Register to a one (1). Accesses to NAND Flash (NM29N16) devices are controlled through two (2) I/O addresses (base address and base address + 2) for the Command and Select registers. Read/Write strobes are accessed through either common memory space or I/O space based on the value placed in the NAND Flash (NM29N16) Configuration Reg bit D3 (mem\_io\_space). In order to support the I/O addresses, a minimum I/O window space of 8 bytes must be opened. Regardless of which address is chosen for the base address for function 0, the base address, base address + 2, and base address + 4 (if enabled) are dedicated for NAND Flash (NM29N16) control interface support. The detailed function of the I/O address ports and the common memory read/write port is listed below.

The following NAND (NM29N16) registers are active only when Function 0 is configured for NAND Flash (NM29N16) mode (bit D0 of the NAND Flash (NM29N16) Config. Register is set to one (1) ).

# NAND (NM29N16) Command Register

| [I/O window base address |           |       |     |     |    |

|--------------------------|-----------|-------|-----|-----|----|

| D7                       | D6        | D5-D3 | D2  | D1  | D0 |

| Rdy/Bsy#                 | CRdy/Bsy# | RFU   | CLE | ALE | CE |

**Rdy/Bsy**#—This bit reflects the real-time state of Function 0's Rdy/Bsy# pin when in NAND Flash (NM29N16) mode.

**CRdy/Bsy**—This bit is latched to a one (1) when Rdy/ Bsy# changes state. It can be cleared by writing the value of 02h to Function 0's Pin Replacement Register (address 0x1024).