# SIEMENS

# **ICs for Communications**

Joint Audio Decoder-Encoder - Multimode

PSB 7238 Version 2.1

Data Sheet 1998-07-01

| PSB 7238 1998-07-01<br>Revision History: |                                 | Current Version: 1998-07-01                  |

|------------------------------------------|---------------------------------|----------------------------------------------|

| Previous Version:                        |                                 | Preliminary Data Sheet 06.98 (V1.2)          |

| Page<br>(in previous<br>Version)         | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |

|                                          |                                 |                                              |

|                                          |                                 |                                              |

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide: see our webpage at http://www.siemens.de/semiconductor/communication

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4μC, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC<sup>™</sup>-A, FALC<sup>™</sup>54, IWE<sup>™</sup>, SARE<sup>™</sup>, UTPT<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, DigiTape<sup>™</sup> are trademarks of Siemens AG.

Edition 1998-07-01 Published by Siemens AG, HL SP, Balanstraße 73, 81541 München

© Siemens AG 1998. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# **Table of Contents**

# Page

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                                                                                | Introduction.5Overview.5Feature List.7Logic Symbol.9Pin Configuration (top view).10Pin Description.11Functional Block Diagram.17System Integration.18                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2                                                                                                 | General Architecture and Functions.21Architecture.21Functions.22Summary of the Functions.22Audio Functions and Supplementary Features.23                                                                                                                                                                                                                                                                                             |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.2.1<br>3.3.2.1<br>3.3.2.2<br>3.3.3.3 | Interfaces and Memory Organization.24Interfaces.24IOM®-2 Interface.24Serial Audio Interface.24Serial Audio Interface.26Parallel Host Interface.28External Memory Interface.28Clock Interface.29Shared Memories.29Directly Accessible Register Bank.31Input/Output Registers.31DSP/Host Com Area with a Multiplexed Host Interface.34Access to DSP/Host Com Area.34Mailbox.40DSP/Host Com Area with a Demultiplexed Host interface.42 |

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br>4.5<br>4.5.1                                                                   | Functional Blocks.45PLL and Baud Rate Generator.45Audio and Data Reception/Transmission.48HDLC Controller.60IOM®-2 Functions.69Monitor Channel Protocol.70C/I Channel.76Programming Indirectly Accessible Registers.79Programming via Parallel Host Interface.79                                                                                                                                                                     |

| 5<br>5.1<br>5.2<br>5.3                                                                                                            | Register Description.80Interrupt Structure.80Interrupt Status Registers.81Indirectly Accessible Configuration and Control Registers.85                                                                                                                                                                                                                                                                                               |

# SIEMENS

| Table of                                                                                        | Contents Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4                                                                                             | HDLC Controller Registers111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                 | Firmware Features       128         Basic Functions       128         Firmware Version Number       128         Software Reset       129         Power Down Command       130         Audio Interfaces       131         Compressed Audio Protocols and Control of JADE       131         Outband Control of JADE       131         Compressed Audio Protocol with Outband Control       143         Compressed Audio Protocol with Inband Control       145         Control Pipeline       153         Uncompressed Data Protocol       159         Audio Interface Timings       159         Uncompressed Data: Host IF, Compressed Data: Host IF       159         Uncompressed Data: IOM IF, Compressed Data: Host IF       167         Uncompressed Data: IOM IF, Compressed Data: Serial Audio       167 |

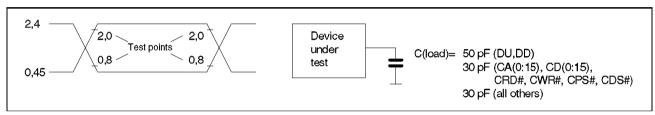

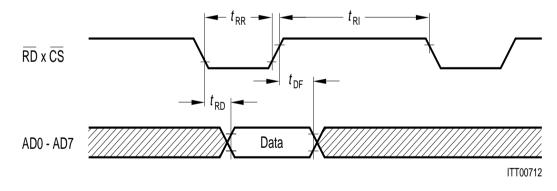

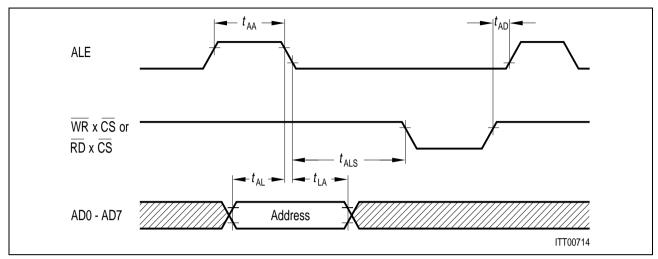

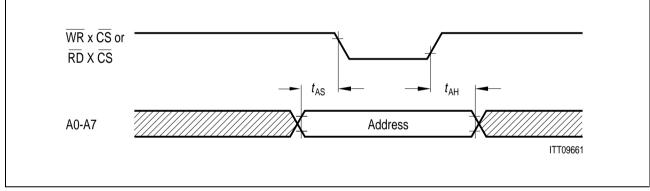

| 7<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.7.1<br>7.7.2<br>7.7.3<br>7.7.4<br>7.7.5 | Interface (SAI).176Electrical Specification.178Absolute Maximum Ratings.178Operating Conditions.178DC Characteristics.179Capacitances.180Oscillator Circuit.180XTAL 1,2 Recommended Typical Crystal Parameters.180AC Characteristics.181Testing Waveform.181Parallel Host Interface Timing.181IOM®-2 Interface Timing.185Serial Audio Interface Timing.187External Memory Interface.189Package Outlings.100                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8                                                                                               | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# 1 Introduction

# 1.1 Overview

The PSB 7238 Joint Audio Decoder Encoder Multimode (JADE MM) is a device which implements voice compression algorithms using the Low-Delay Code Excited Linear Prediction (LD-CELP) standard as defined in the ITU-T G.728 Recommendation, the Algebraic Code Excited Linear Prediction (ACELP) and the Multi-Pulse Maximum Likelihood Quantization (MP-MLQ) standard as defined in the ITU-T G.723 Recommendation, and for 7-kHz voice using the Sub-Band Coded Adaptive Differential PCM (SBC-ADPCM) coding according to the G.722 Recommendation. In addition G.711 PCM audio coding is also supported.

Thus in the G.728 mode it compresses a digitized PCM (64 Kbit/s) or linear (128 Kbit/s) voice signal into a 16 Kbit/s bit stream, and vice versa. The algorithm is implemented in 16-bit fixed point arithmetic and complies with the newest fixed point specification set forth by the ITU.

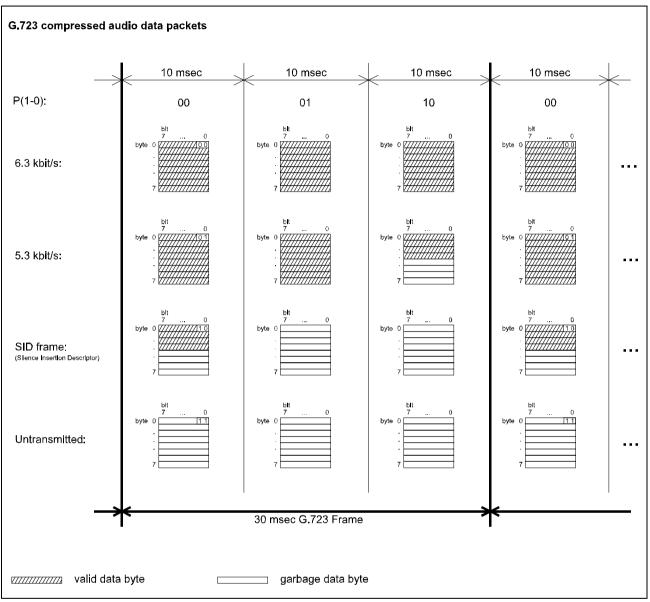

In G.723 mode it compresses the PCM or linear voice signal into 5.3 Kbit/s (ACELP) or 6.3 Kbit/s (MP-MLQ) bit stream, and vice versa. The implementation complies with the newest ITU-T C-code V5.1 and includes the G.723 Annex A (Voice Activity Detection and Comfort Noise Generation).

In the G.722 mode it compresses the PCM compressed (128 Kbit/s) or the linear uncompressed (256 Kbit/s) 7-kHz audio samples into a rate of 48/56/64 Kbit/s, and vice versa.

The JADE finds applications in

- ISDN Videophones (H.320)

- Analog Videophones (H.324)

- Video Conference Systems

- Corporate Network voice concentrators, multiplexers and gateways

- Data-over-voice and Voice-over-data terminals.

Other potential application areas are:

- Networks (e.g. LANs) for packetized voice

- Digital Added Main-Line (DAML) & Digital Circuit Multiplication Equipment (DCME)

- Voice storage e.g. in PC based applications

- Message recording and distribution.

The interfaces of the JADE allow a seamless integration into IOM-2 based systems. After the circuit is set up in the proper mode of operation and parameter settings are programmed by a controlling software, the circuit runs independent of the rest of the system. Status and control information to/from the JADE can be transferred either inband the compressed audio data via the corresponding selected interface or outband using an 8-bit parallel host interface.

In a Videophone system using the  $8\times8$  (formerly IIT) VCP (Video Codec and Multimedia Communications Processor) the Siemens PSB 7238 can work standalone without the need of external initialization. The default configuration of the JADE is such, that no host is needed in this case and the full communication is done between the VCP and the Siemens PSB 7238.

The voice compression algorithms are implemented by an embedded 16-bit fixed point Digital Signal Processor with all memories internal and no external memory needed.

Integration of these and other features, as well as perfectly matched interfaces with other ICs allows for the implementation of highly optimized, low cost system solutions e.g. for Videophones, Data-over-voice and Channel Multiplexing equipment.

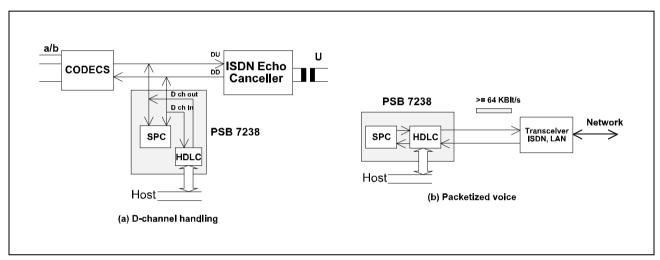

For system integration, two serial HDLC/transparent data channels are implemented which can be serviced by an attached host (or the on-chip DSP). System functions and communication between the chip and an external controller is supported by a full-duplex 256-byte on-chip mailbox communication memory.

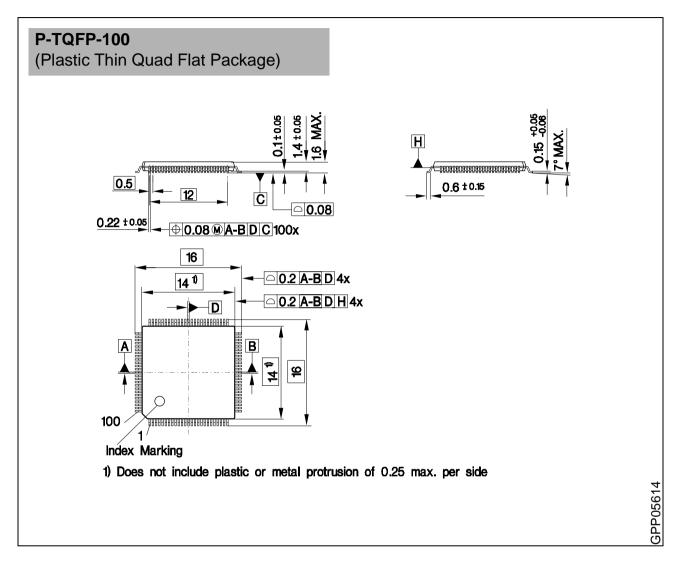

The circuit is offered in a Quad Flat Pack package with 100 pins (P-TQFP-100: size  $14 \times 14$  mm, pitch 0.5 mm, height 1.4 mm).

Note: This Data Sheet gives a thorough description of the functions and hardware that forms the base of PSB 7238. It includes information (e.g. External Memory Interface) that is not needed for the PSB 7238 as a "ready to use plug and play" *G*.728/G.723/G.722/G.711 audio compression device.

# SIEMENS

# Joint Audio Decoder-Encoder - Multimode

# Version 2.1

# 1.2 Feature List

# **Functions**

- G.728 compression/decompression (16 Kbit/s)

- G.723 compression/decompression (6.3, 5.3 Kbit/s)

- G.722 compression/decompression for 7-kHz audio (64, 56, 48 Kbit/s)

- G.711 compression/decompression (64 Kbit/s)

- Outband controlled audio protocol with optimized data rate

- Digital sampling rate conversion (16 kHz 8 kHz) for G.722 audio with 8-kHz Codec (bandwidth reduced to 3.4 kHz)

- Accepts/outputs uncompressed audio in 8-bit PCM A/µ law or 16-bit linear format

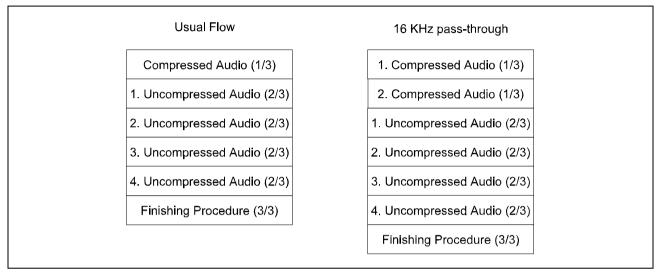

- Uncompressed/compressed audio switchable between different interface combinations (IOM/Serial Audio Interface, IOM/Host, Host/Host)

- Inband controlled H.221/H.223 oriented audio protocol, e.g. for direct serial connection to videocodec (VCP of 8×8 Inc., formerly IIT Inc.) as well as host based solutions

- Stable reaction on interrupt handshake timing violations of e.g. a slow host (Windows<sup>®</sup> PC)

# **System On-chip Functions**

- Two universal serial HDLC/transparent data controllers

- IOM-2 monitor and C/I channels

- Generation of programmable system clock output

- Three programmable timers

- Programmable on-chip PLL for internal clock generation from ISDN low frequency (7.68 MHz) clock

| Туре     | Ordering Code | Package    |

|----------|---------------|------------|

| PSB 7238 | Q67101-H6773  | P-TQFP-100 |

### Interfaces

- 4-line IOM-2/PCM interface

- 5-line serial audio interface, e.g. for connection to videocodec/H.221/223 processor

- Parallel 8-bit Host interface

- 4-line general purpose interface

- External memory interface to external SRAM with programmable waitstates (0 to 15), for development purposes only.

# Control

- Programmable via parallel host interface

- Operating parameters and mode settings via a register bank

- Access to audio channels and HDLC/serial transparent data controllers from DSP or an external host

- Interface to external software via a full-duplex 256-byte on-chip mailbox

- H.221/H.223 oriented inband configuration/mode switching

# General

- Supply voltage: 3.0 3.6 V

- Additional 4.5 to 5.5 V supply for connection to 5-V systems without external components

- Ambient temperature range 0 °C to + 70 °C

- P-TQFP-100 package

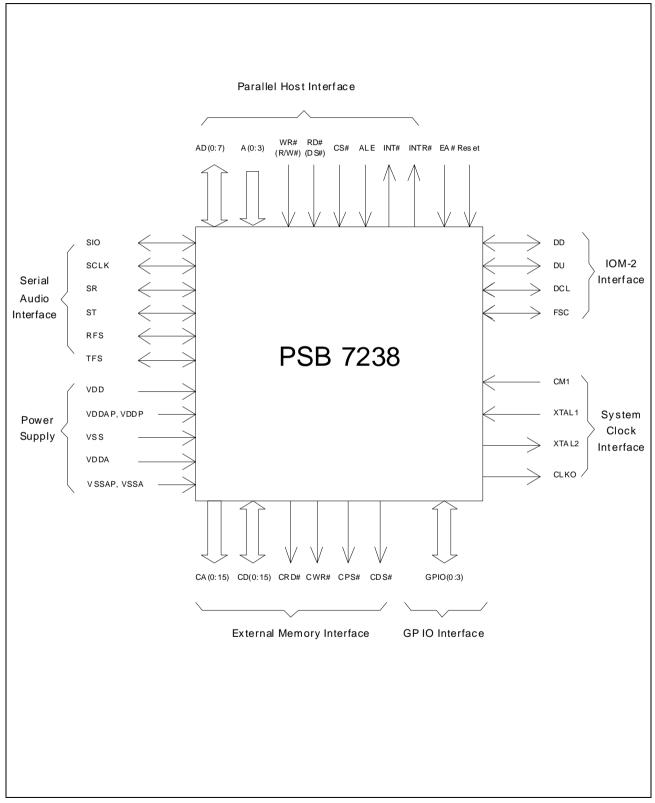

# 1.3 Logic Symbol

# Figure 1

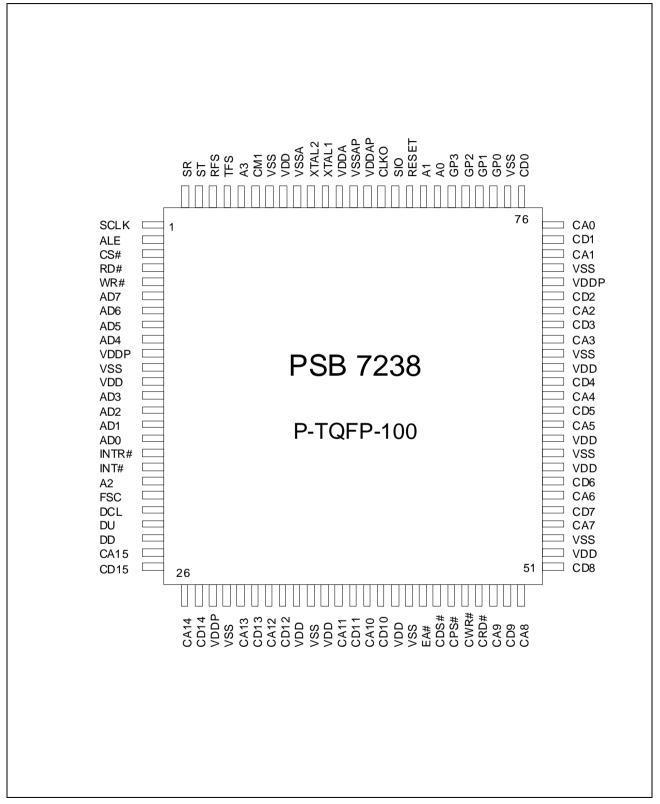

# **1.4 Pin Configuration** (top view)

# Figure 2

# 1.5 Pin Description

| Table 1 | Parallel Host Interface |          |                                                                                                                                                                   |

|---------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol                  | Function | Descriptions                                                                                                                                                      |

| 16      | AD0                     | I/O      | Multiplexed Bus Mode: Address/Data Bus. Transfers                                                                                                                 |

| 15      | AD1                     | I/O      | addresses from the host to JADE and data between the host and the JADE                                                                                            |

| 14      | AD2                     | I/O      | <b>Demultiplexed Bus Mode:</b> Data bus. Transfers data                                                                                                           |

| 13      | AD3                     | I/O      | between the host and the JADE                                                                                                                                     |

| 9       | AD4                     | I/O      |                                                                                                                                                                   |

| 8       | AD5                     | I/O      |                                                                                                                                                                   |

| 7       | AD6                     | I/O      |                                                                                                                                                                   |

| 6       | AD7                     | I/O      |                                                                                                                                                                   |

| 4       | DS                      | 1        | Data Strobe.<br>The rising edge marks the end of a valid read or write<br>operation (Motorola bus mode).                                                          |

|         | RD                      | 1        | Read.<br>This signal indicates a read operation (Siemens/Intel<br>bus mode).                                                                                      |

| 5       | R/W                     | 1        | Read/Write.<br>A 1 ("high") identifies a valid host access as a read<br>operation. A 0 identifies a valid host access as a write<br>operation (Motorola bus mode) |

|         | WR                      | 1        | Write.<br>This signal indicates a write operation (Siemens/Intel<br>bus mode).                                                                                    |

| 3       | CS                      | 1        | Chip Select.                                                                                                                                                      |

| 2       | ALE                     | 1        | Address Latch Enable.<br>A "high" on this line indicates an address on AD(0:7)<br>(multipexed bus mode only). ALE also selects the<br>interface mode              |

| 82      | A0                      | 1        | Address Bits A(0:3) (demultiplexed bus type)                                                                                                                      |

| 83      | A1                      | 1        |                                                                                                                                                                   |

| 19      | A2                      | 1        |                                                                                                                                                                   |

| 96      | A3                      | I        |                                                                                                                                                                   |

| Table 1 | Parallel Host Interface | (cont'd) |

|---------|-------------------------|----------|

|---------|-------------------------|----------|

| Pin No. | Symbol | Function | Descriptions                                                                                                                                                            |

|---------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | INTR   | O (OD)   | Interrupt Real-time.<br>Interrupt output line for high priority interrupt status<br>(serial audio receive/transmit, serial HDLC data<br>receive/transmit data) to host. |

| 18      | INT    | O (OD)   | Interrupt Request.<br>Interrupt output line for all other interrupt states.                                                                                             |

# Table 2IOM<sup>®</sup>-2 Interface

| Pin No. | Symbol | Function | Descriptions                                                                         |

|---------|--------|----------|--------------------------------------------------------------------------------------|

| 23      | DD     | I/O(OD)  | Data Downstream on IOM-2/PCM interface.                                              |

| 22      | DU     | I/O(OD)  | Data Upstream on IOM-2/PCM interface.                                                |

| 21      | DCL    | I/O(OD)  | Data Clock.<br>Clock frequency is twice the data rate, or equal to the<br>data rate. |

| 20      | FSC    | I/O(OD)  | Frame Sync.<br>Marks the beginning of a physical IOM-2 or PCM frame.                 |

# Table 3 Serial Audio Interface

| Pin No. | Symbol | Function | Descriptions                                                                                  |

|---------|--------|----------|-----------------------------------------------------------------------------------------------|

| 1       | SCLK   | I/O      | Serial Clock.<br>Serial clock for SR and ST.                                                  |

| 100     | SR     | I/O(OD)  | Serial Data Receive. Should be connected to $V_{\rm SS}$ via a pulldown resistor if not used. |

| 99      | ST     | I/O(OD)  | Serial Data Transmit.                                                                         |

| 98      | RFS    | I/O      | Audio Receive Frame Sync.                                                                     |

| 97      | TFS    | I/O      | Audio Transmit Frame Sync.                                                                    |

| Pin No. | Symbol | Function | Descriptions                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90      | XTAL1  | 1        | Crystal In or Clock In.<br>If a crystal is used, it is connected between XTAL1 and XTAL2. If a clock signal is provided (via an external oscillator), this signal is input via XTAL1. In this case the XTAL2 output is to be left non-connected. The XTAL1 input has to be 50% duty cycle and must not exceed the voltage range between $V_{\rm SSA}$ and $V_{\rm DDA}$ . |

| 91      | XTAL2  | 0        | Crystal Out.<br>Left unconnected if a crystal is not used.                                                                                                                                                                                                                                                                                                                |

| 86      | CLKO   | 0        | Clock Out.<br>Output clock of frequency equal to the internal frequency<br>divided by a programmable factor.                                                                                                                                                                                                                                                              |

#### Table 4System Clocks

#### External Memory Interface (for Development Purposes only) Table 5 Function Symbol Descriptions Pin No. 75 CA0 0 C-Bus Address. 73 CA1 Ο Used for addressing ROM or RAM external to the chip. CA2 69 Ο Is to be left NC if not used. 67 CA3 Ο 63 CA4 Ο 61 CA5 0 0 56 CA6 54 CA7 0 50 CA8 0 CA9 0 48 39 CA10 Ο 37 CA11 0 Ο 32 CA12 CA13 30 Ο 26 CA14 0 Ο 24 CA15

| Table 5 | External Memory Interface (for Development Purposes only) (cont'd) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------|--------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No. | Symbol                                                             | Function | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 76      | CD0                                                                | I/O      | C-Bus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 74      | CD1                                                                | I/O      | Data bus for external ROM or RAM. Is to be left NC if not                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 70      | CD2                                                                | I/O      | used.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 68      | CD3                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 64      | CD4                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 62      | CD5                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 57      | CD6                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 55      | CD7                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 51      | CD8                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 49      | CD9                                                                | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 40      | CD10                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 38      | CD11                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 33      | CD12                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 31      | CD13                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 27      | CD14                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 25      | CD15                                                               | I/O      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 43      | EA                                                                 | 1        | External program Access enable<br>When "high", an access to program address range<br>$(0000_{H} - 7FFF_{H})$ fetches an instruction from on-chip<br>ROM. Access to $8000_{H} - FFFF_{H}$ addresses external<br>memory via the External Memory Interface.<br>When "low", an access to $0000_{H} - FFFF_{H}$ (including<br>$0000_{H} - 7FFF_{H}$ , normally reserved for on-chip software)<br>accesses external program memory via the External<br>Memory Interface. |  |

| 47      | CRD                                                                | 0        | C-Bus Read to external memories.<br>Left NC if not used.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 46      | CWR                                                                | 0        | C-Bus Write to external memories.<br>Left NC if not used.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 45      | CPS                                                                | 0        | C-Bus Select line for external program memory.<br>Left NC if not used.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 44      | CDS                                                                | 0        | C-Bus Select line for external data memory.<br>Left NC if not used.                                                                                                                                                                                                                                                                                                                                                                                                |  |

# Table 5 External Memory Interface (for Development Purposes only) (cont'd)

| Table 6 | 6 General Control |          |                                                                                                                                                                                                                                                              |  |

|---------|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No. | Symbol            | Function | Description                                                                                                                                                                                                                                                  |  |

| 95      | CM1               | I        | Clock Mode<br>Selects the option for the generation of the DSP internal<br>working clock.                                                                                                                                                                    |  |

| 85      | SIO               | I/O      | Serial I/O line.<br>When programmed as input, a rising or falling<br>(selectable) edge on this line may generate a maskable<br>interrupt INT (host) or INT1 (DSP).<br>When programmed as output, its state is directly<br>controlled by the DSP or the host. |  |

| 84      | RESET             | I        | Reset input. Reset time: > 1 ms.                                                                                                                                                                                                                             |  |

# Table 7General Purpose I/O Interface

| Pin No. | Symbol | Function | Description              |

|---------|--------|----------|--------------------------|

| 81      | GP0    | I/O (OD) | General purpose I/O pins |

| 80      | GP1    | I/O (OD) |                          |

| 79      | GP2    | I/O (OD) |                          |

| 78      | GP3    | I/O (OD) |                          |

# Table 8Power Supply

| Pin No. | Symbol          | Function | Descriptions                                              |

|---------|-----------------|----------|-----------------------------------------------------------|

| 11      | V <sub>SS</sub> | 1        | Ground (common to $V_{\text{DD}}$ and $V_{\text{DDP}}$ ). |

| 29      | $V_{\rm SS}$    | I        |                                                           |

| 35      | $V_{\rm SS}$    | I        |                                                           |

| 42      | $V_{\rm SS}$    | I        |                                                           |

| 53      | $V_{\rm SS}$    | I        |                                                           |

| 59      | $V_{\rm SS}$    | I        |                                                           |

| 66      | $V_{\rm SS}$    | I        |                                                           |

| 72      | $V_{\rm SS}$    | I        |                                                           |

| 77      | $V_{\rm SS}$    | 1        |                                                           |

| 94      | $V_{\rm SS}$    | 1        |                                                           |

| Pin No. | Symbol            | Function | Descriptions                                                                                                                        |

|---------|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| 12      | $V_{DD}$          | 1        | Positive power supply voltage (3.0 - 3.6 V).                                                                                        |

| 36      | $V_{DD}$          | 1        |                                                                                                                                     |

| 60      | $V_{DD}$          | 1        |                                                                                                                                     |

| 93      | $V_{DD}$          | 1        |                                                                                                                                     |

| 34      | $V_{DD}$          | 1        | Note: In former versions, pins 34, 41, 52, 58 and 65                                                                                |

| 41      | $V_{DD}$          | 1        | could be connected to either $V_{DD}$ (for special version with external memory) or to V (for                                       |

| 52      | $V_{DD}$          | 1        | version with external memory) or to $V_{DDP}$ (for compatibility with other JADE versions). This                                    |

| 58      | $V_{DD}$          | 1        | version requires them to be connected to $V_{DD}$ .                                                                                 |

| 65      | $V_{DD}$          | 1        |                                                                                                                                     |

| 10      | $V_{DDP}$         | I        | Positive power supply voltage (4.5 - 5.5 V) for external                                                                            |

| 28      | $V_{DDP}$         | 1        | interfaces.                                                                                                                         |

| 71      | $V_{DDP}$         | 1        |                                                                                                                                     |

| 89      | V <sub>DDA</sub>  | I        | Separate positive power supply voltage (3.0 - 3.6 V) for Clock Generation Unit (Oscillator).                                        |

| 92      | V <sub>SSA</sub>  | 1        | Separate Ground (0 V) for Clock Generation Unit (Oscillator).                                                                       |

| 87      | V <sub>DDAP</sub> | 1        | Separate positive power supply voltage (3.0 - 3.6 V) for Clock Generation Unit (PLL).                                               |

|         |                   |          | Note: The power supply for the PLL requires pin 87 connected to $V_{DDAP}$ . In former versions pin 87 was connected to $V_{DDP}$ . |

| 88      | V <sub>SSAP</sub> | 1        | Separate Ground (0 V) for Clock Generation Unit (PLL)                                                                               |

# Table 8Power Supply (cont'd)

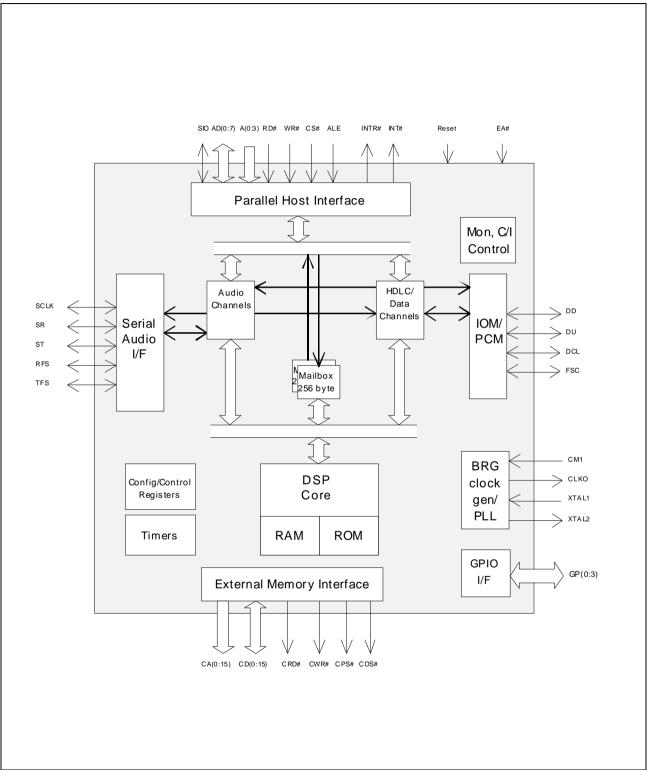

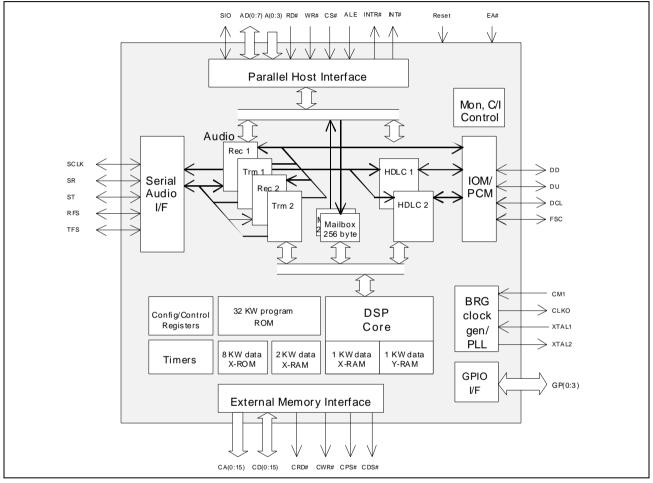

# 1.6 Functional Block Diagram

# Figure 3

Detailed description see Chapter 2.

# 1.7 System Integration

Example of integration in ISDN/analog videophone:

The first example represents a low-cost solution for a desk-top standalone videophone that connects to an ISDN S0 bus (ISDN basic access) or an analog telephone line.

The ISDN basic access consists of two 64 Kbit/s so-called B-channels to carry user information (voice, data, ...), and a separate 16 Kbit/s D-channel primarily used for signaling. The video and audio are both compressed so that they are carried, along with additional control information, in the two B-channels, or 128 Kbit/s.

The analog telephone line can carry up to 33.6 Kbit/s using a V.34+ modem.

The general aspects of videotelephony are covered by ITU-T H.320/H.324 recommendations. The video is compressed according to the H.261 (sometimes called " $p \times 64$ ") or the H.263 recommendation.

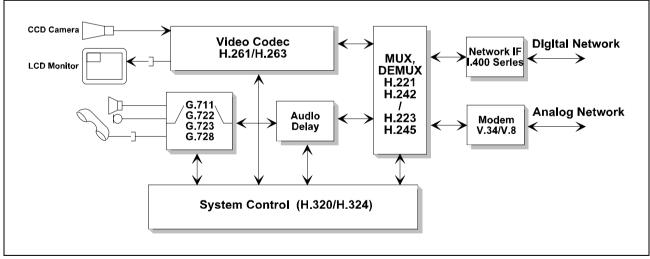

For the ISDN videophone (H.320) the compressed video and audio signals are multiplexed together with additional synchronization and control information into two B-channels, which are separately switched via the network and thus have to be resynchronized at the other end. The multiplexing and resynchronization of the B-channels is specified by the H.221 recommendation (see **Figure 4**).

For the analog videophone (H.324) the compressed video and audio signals are multiplexed together with additional control information into a single communication link. The multiplexing is specified by the H.223 recommendation (see **Figure 4**).

# Figure 4

Using non-parametric compression techniques, audio can be compressed to 64 Kbit/s PCM (logarithmical A- or  $\mu$ -law approximation for 3.1-kHz voice acc. to G.711) or 48/56/64 Kbit/s sub-band coded adaptive PCM (for 7-kHz audio acc. to G.722). This leaves, however, only approximately 64 Kbit/s for video on the ISDN which, at this rate, yields only a marginally good picture quality. For the analog videophone it's not even possible to transfer only audio at this data rate.

In order to make the best possible use of the total bandwidth and obtain the best possible video quality, the audio should require only a small fraction of the total data rate. This is made possible by using parametric compression techniques such as LD-CELP (16 Kbit/s), ACELP (5.3 Kbit/s) or MP-MLQ (6.3 Kbit/s). Above all, the corresponding norms (G.728 and G.723) are internationally adopted standards, so that compatibility between equipment from different manufacturers is ensured.

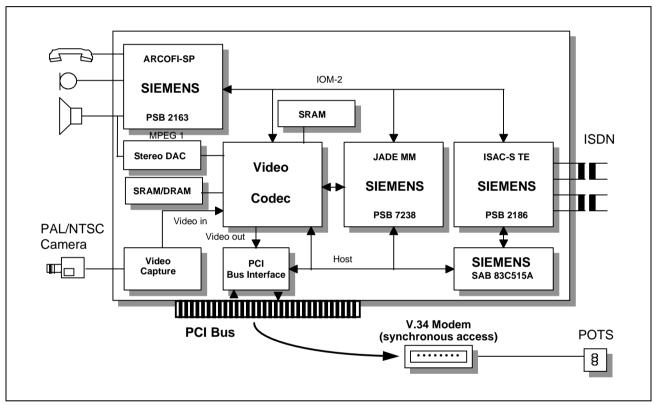

A low-cost H.320/324 videophone solution for both ISDN and POTS line as a PCI card for commercial PC's is shown in **Figure 5**.

# Figure 5

This "multimode" board is capable to work with whatever telephone line is available, digital ISDN or analog POTS.

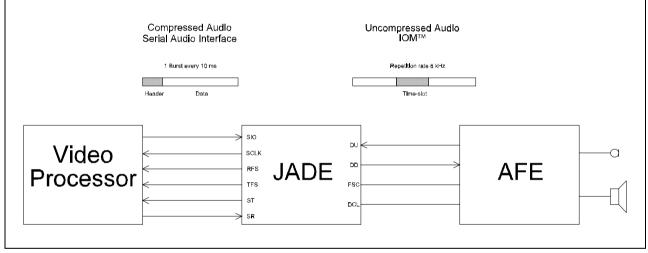

The JADE MM and the video codec chip (e.g. the Video Communication Processor "VCP" from 8×8 Inc.) constitute the heart of the videophone.

Both (together with the microcontroller 83C515) are connected to the PC via the PCI bus using PCI bus interface (e.g. the "VPIC" of  $8 \times 8$  Inc.).

The JADE MM compresses/decompresses audio according to the ITU-T standards G.728, G.723, G.722 and G.711 and runs a fully inband controlled protocol on the interface to the video codec. It receives/transmits uncompressed audio via the IOM-2 interface from/to the ARCOFI-SP. The setup for this application is done automatically after a hardware reset, so no additional initialization by a host is required. Since the JADE MM has all its memories on chip, no external SRAM needs to be connected.

The ARCOFI-SP (Audio Ringing Codec Filter) is a hands-free codec for 3.1-kHz voice which performs detection and elaborate balancing of the received and transmitted audio to suppress undesirable effects due to acoustical feedback of the signal from the remote subscriber. The quality obtained is very close to that of echo-free full duplex conferencing.

The video is captured by a PAL/NTSC camera and digitized and demodulated e.g. by a standard SAA 7110 which is directly connected to the video processor. Alternatively, a digital camera may be used, which can be connected directly to the video processor.

The video processor compresses and decompresses video according to the ITU-T standards H.261/263 and multiplexes/demultiplexes video, audio and data according to H.221/223. The video processor uses DRAMs and SRAMs to store data and program code.

When operating in the ISDN mode, the H.221 multiplexed data stream is sent via the two B-channels of the IOM-2 interface to the ISAC-S-TE (ISDN Subscriber Access Controller for S-interface) which transmits them to the ISDN according to I.430 S0 interface recommendation. The ISAC-S-TE also handles, together with the attached microcontroller (e.g. SAB 83C515), D-channel layer-2 and layer-3 call control signaling.

The reverse functions are performed on the B-channels received from the network.

Instead of an S0, it is conceivable to implement any other layer-1 interface just by replacing the ISAC-S TE by an appropriate transceiver, e.g. by a transceiver for **2-wire** digital transmission ISAC-P PSB 2196 or ISDN echo canceller for 2B1Q.

When operating in the POTS mode, the H.223 multiplexed data stream is sent via the PCI interface to a V.34 modem. The modem must be able to work in synchronous mode, i.e. the H.223 multiplexed data shall be applied directly to the V.34 synchronous data pump. When an external, non-integrated V.34 modem is utilized, control between the modem and the terminal shall be via ITU-T V.25ter and V.80. In such cases the physical interface is implementation specific.

To achieve "lip synchronization", the audio may be delayed with respect to the video. This is necessary because of the higher transmission delay suffered by the video signal, due to the elaborate H.261/263 video compression. A delay of approximately 0.5 seconds is enough in most practical cases. To make maximum use of the existing memory in the system, the delay is performed by the video processor with its external RAMs.

In videophone applications calling for high quality, 7-kHz wide-band audio, the PSB 7238 can be switched to G.722 mode. In this case the rate of the compressed audio is 48, 56 or 64 Kbit/s.

When decoding MPEG bitstreams, the audio D/A conversion is provided by a stereo audio DAC.

Demonstration board designs for H.320 PC based videophones containing the chip set from Siemens AG and 8×8 Inc. are available and can be ordered from Siemens/8×8.

# **General Architecture and Functions**

# 2 General Architecture and Functions

# 2.1 Architecture

Figure 6 shows a sketch of the PSB 7238 architecture with its most important functional modules.

# Figure 6

The audio processing of the PSB 7238 is based on a 16-bit fixed point DSP core, **SPCF** (Signal Processor Core Fast).

The **Clock Generator** is responsible for generating the internal clocks for the SPCF. A **Baud Rate Generator** provides an output clock of programmable rate.

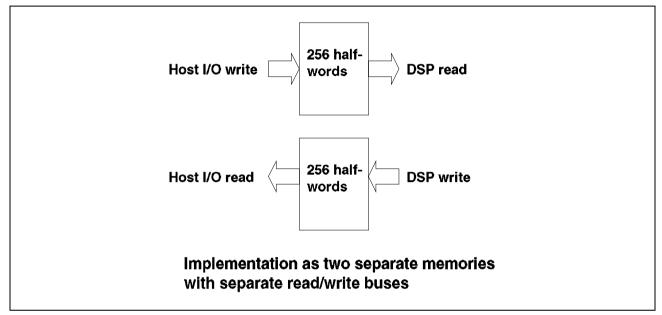

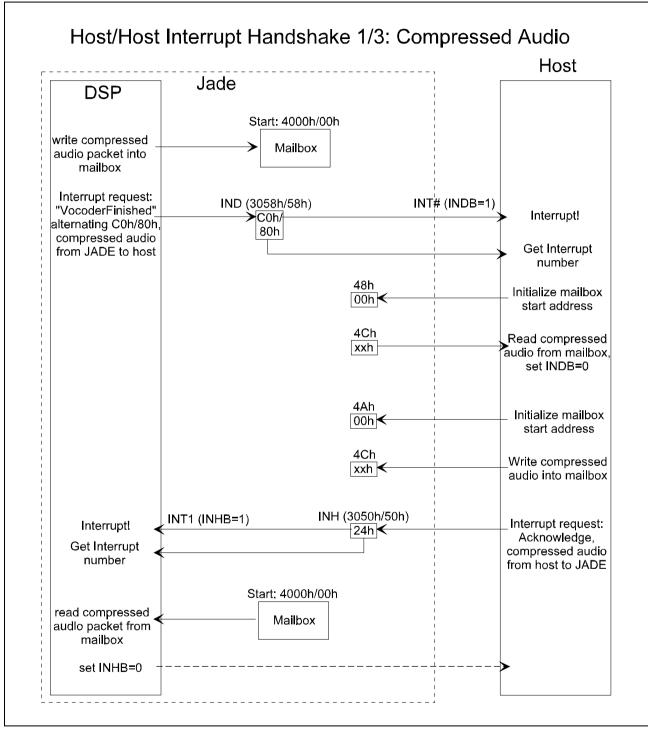

The **Parallel Host Interface** is used to control the circuit through an associated host via interrupt handshake procedures. Alternatively, the circuit can be controlled via the serial audio interface, thus enabling standalone applications to be implemented. Communication between the host, if used, and the DSP is interrupt supported, via a full-duplex 256-byte on-chip **Communication Memory Mailbox**.

### **General Architecture and Functions**

Two receive and two transmit audio channels are provided. They are input/output on the **ISDN Oriented Modular** (IOM-2) or the **Serial Audio Interface** (SAI) interfaces in individually programmable time-slots. These channels are accessed from the DSP and/or the parallel host interface.

The two **HDLC Controller** channels can be serviced by the DSP or the parallel host interface. The serial data for the HDLC controllers are located in programmable time-slots on IOM-2 and/or SAI.

For development purposes, the **External Memory Interface** allows programs to be executed from an external memory and external data memory to be used.

# 2.2 Functions

# 2.2.1 Summary of the Functions

The main functions implemented by the PSB 7238 are:

- G.728 compression/decompression (16 Kbit/s)

- G.723 compression/decompression (6.3, 5.3 Kbit/s)

- G.722 compression/decompression for 7-kHz audio (64, 56, 48 Kbit/s)

- G.711 compression/decompression (64 Kbit/s)

- Digital sampling rate conversion (16 kHz 8 kHz) for G.722 audio with 8-kHz codec (bandwidth reduced to 3.4 kHz)

- Accepts/outputs uncompressed audio 8-bit PCM A/µ law or 16-bit linear format

- Uncompressed/compressed audio switchable between different interface combinations (IOM/Serial Audio Interface, IOM/Host, Host/Host)

- Inband controlled H.221/H.223 oriented audio protocol, e.g. for direct serial connection to videocodec (VCP of 8×8 Inc., formerly IIT Inc.)

- Outband controlled audio protocol with optimized data rate

- Stable reaction on interrupt handshake timing violations of e.g. a slow host (Windows<sup>®</sup> PC)

For more details on the hardware (necessary for a better understanding of some of the topics described in the present chapter), please refer to the other chapters of this data sheet.

# **General Architecture and Functions**

# 2.2.2 Audio Functions and Supplementary Features

### General

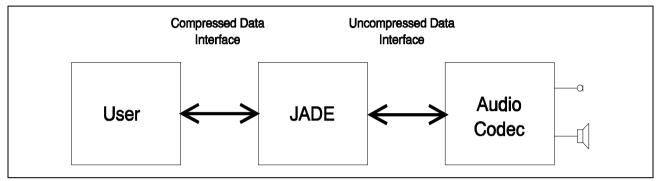

The uncompressed/compressed audio is applied to the interfaces as follows:

| Uncompressed Audio                     | Compressed Audio                                                                  |

|----------------------------------------|-----------------------------------------------------------------------------------|

| IOM-2 (transparent)                    | SAI (H.221/223 oriented audio protocol or transparent)                            |

| IOM-2 (transparent)                    | Host IF (interrupt handshake protocol with minimized interrupt load for the host) |

| Host IF (interrupt handshake protocol) | Host IF (interrupt handshake protocol)                                            |

"Transparent" means that data is received/transmitted in a time-slot without protocol.

# 1. Full Duplex G.728 Encoding/Decoding of One Audio Channel

Audio coding according to ITU-T G.728 fixed point recommendation using Low Delay Code Excited Prediction (LD-CELP, 16 Kbit/s), offering toll quality audio. The postfilter of the G.728 may be switched on (offering a higher quality impression) or off (providing objective better S/N values).

# 2. Full Duplex G.723 Encoding/Decoding of One Audio Channel

Audio coding according to ITU-T G.723 recommendation using Multipulse Maximum Likelihood Quantization (MP-MLQ, 6.3 Kbit/s) or Algebraic Code Excited Linear Prediction (ACELP, 5.3 Kbit/s). The high pass filter, the postfilter and the Voice Activity Detection of the G.723 may be independently switched on or off.

# 3. Full Duplex G.722 Encoding/Decoding of One Audio Channel

Audio coding for 7-kHz voice using the Sub-Band Coded Adaptive Differential PCM (SB-ADPCM) algorithm according to the G.722 Recommendation.

# 4. Serial H.221/223 Oriented Audio Protocol

The PSB 7238 supports a serial H.221/223 oriented audio protocol for direct connection to a Videocodec (VCP of 8×8 Inc.). This protocol provides an outband synchronization of the audio bit streams by using block structures for the compressed audio data.

# 3 Interfaces and Memory Organization

3.1 Interfaces

# 3.1.1 IOM<sup>®</sup>-2 Interface

#### **Electrical Interface**

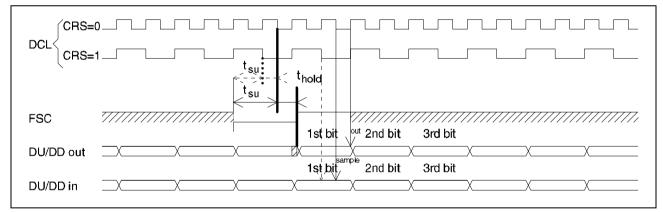

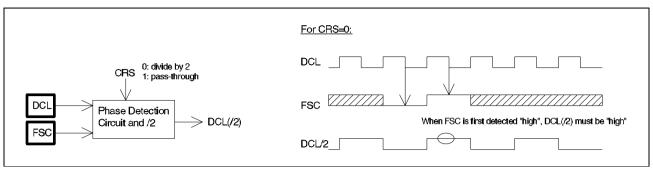

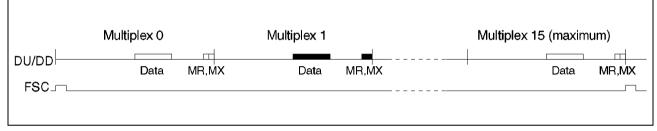

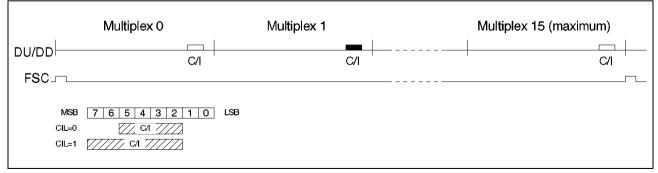

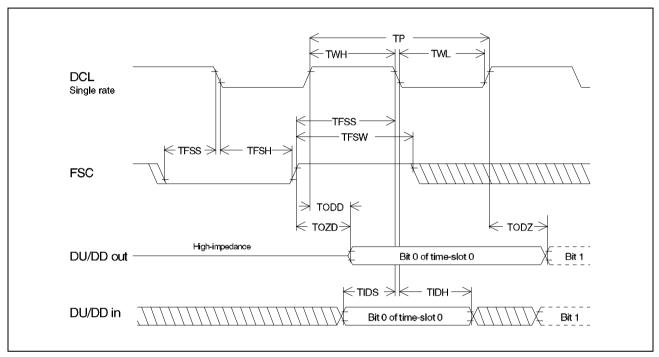

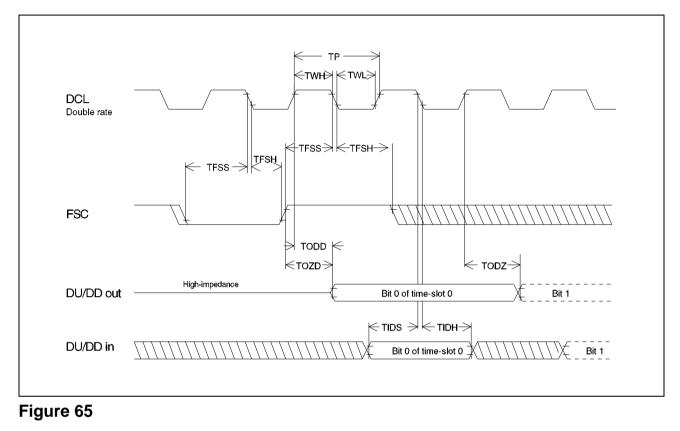

The IOM-2 interface is a 4-wire interface with two data lines (DD and DU, programmable open drain or push-pull), a data clock line (DCL input/output) and a frame sync signal (FSC input/output). The data clock is by default equal to twice the data rate ("Double Rate"). However, DCL may be set equal to the data rate ("Single Rate") by programming. In standalone configuration the clock signal is always "Double Rate".

In terminal applications, the bit rate on the interface is normally 768 Kbit/s, in line card applications it is 2048 Kbit/s (for details, see IOM-2 Interface Reference Guide). However, the data rate may be different (between 16 Kbit/s and 4.096 Mbit/s and the DCL rate correspondingly between 16 kHz and 4.096 MHz), since the interface can be considered as a general purpose TDM (Time-Division Multiplex) highway.

The total number of time-slots on the interface is not explicitly programmed: instead, the FSC signal (at repetition rate 8 kHz) always marks the TDM physical frame beginning. See **Figure 7**.

# Figure 7

- DCL Bits on DU/DD are clocked out with the rising edge of DCL and latched in with the falling edge of DCL. Frequency 16 kHz to 4.096 MHz.

- FSC (8 kHz) Marks the beginning of the physical frame on DU and DD. The first bit in the frame is output after the rising edge of FSC. The first bit in the frame is latched in with the first falling edge after FSC has gone "high" if CRS = 1, or after the second edge (at 3/4) if CRS = 0.

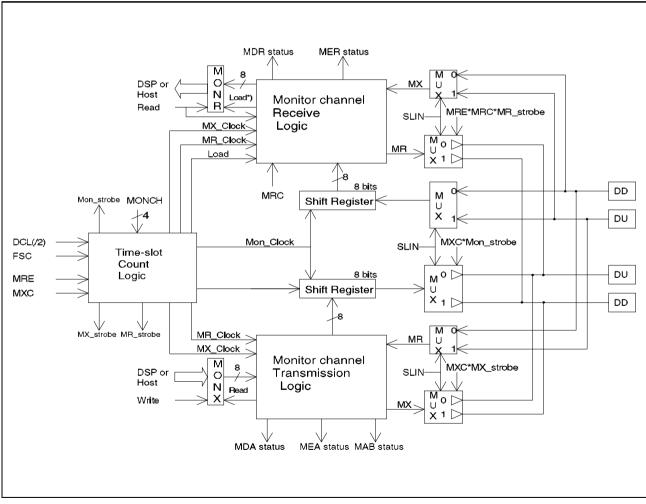

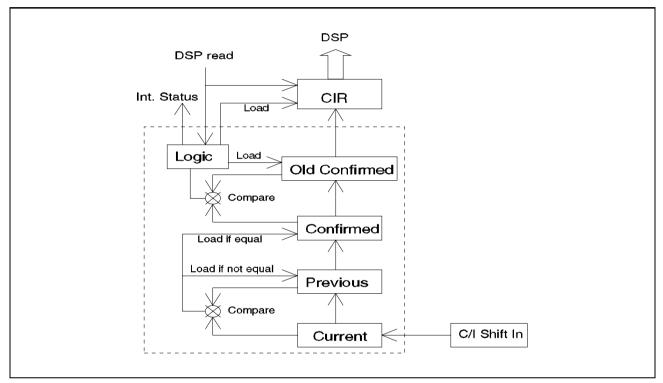

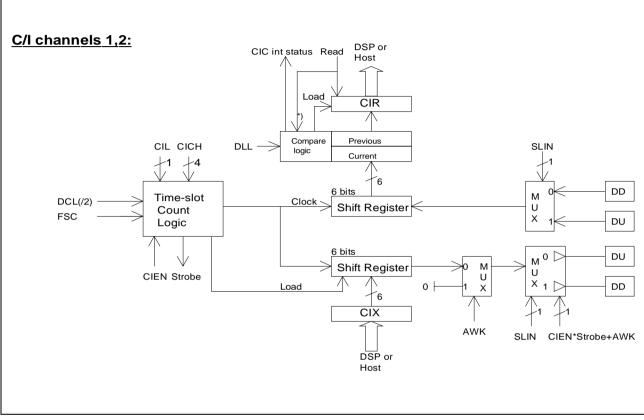

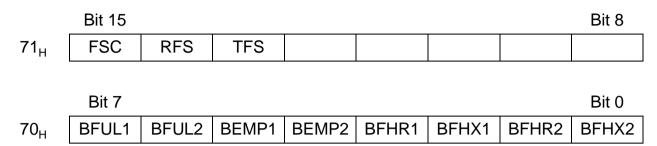

### Channels

The following channels may be programmed on the IOM-2 interface: two receive audio channels, two transmit audio channels, one monitor channel, two C/I channels, two receive and two transmit HDLC channels:

| Audio receive 1 and receive 2 channels<br>Audio transmit 1 and transmit 2 channels | Independently programmable on DD or DU, with programmable locations (start at bit 1 512) and lengths (1 32 bits) w.r.t. FSC                             |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Monitor channel                                                                    | Programmable on DD(in)/DU(out) or<br>DD(out)/DU(in), with programmable<br>time-slot (3rd byte in multiplex 0,, 15)<br>after FSC                         |  |  |

| Two C/I channels                                                                   | Programmable on DD(in)/DU(out) or<br>DD(out)/DU(in), with programmable<br>length (4 or 6 bits) and position (4th byte<br>in multiplex 0,, 15) after FSC |  |  |

| Two HDLC receive and transmit channels                                             | Independently programmable on DD or DU, with programmable locations (start at bit 1 512) and lengths (1 256 bits) w.r.t. FSC                            |  |  |

The transfer of voice samples is performed with the help of an interrupt with repetition rate 8 kHz derived from the FSC signal. A double-buffered register is provided for each channel, accessible from the DSP and from the parallel host interface. The double buffered register ensures that enough time is always provided for reading and writing data before an overflow/underflow occurs, independent of the location of the time-slots. Alternatively, the audio samples can be transferred between the DSP or Host and IOM-2 by using an interrupt generated when a programmable number (1 ... 32) of bits are shifted out (number independent of the time-slot length on the line).

Outside the time-slots where transmission takes place the DU and DD lines are in high impedance.

# 3.1.2 Serial Audio Interface

The Serial Audio Interface is a generic 5-line serial interface with the following lines:

| SCLK | Serial Bit Clock    | Input or output. |

|------|---------------------|------------------|

| SR   | Serial Receive      | Input/output.    |

| ST   | Serial Transmit     | Input/output.    |

| RFS  | Receive Frame Sync  | Input or output. |

| TFS  | Transmit Frame Sync | Input or output. |

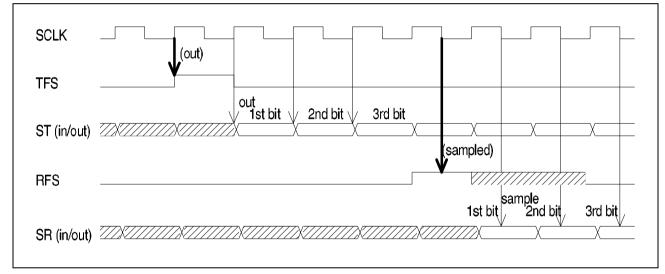

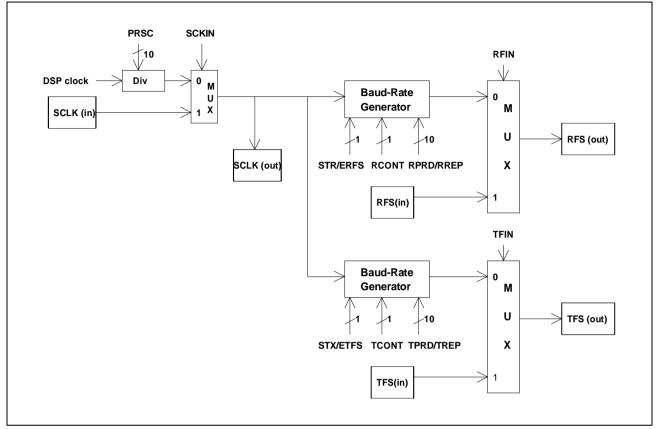

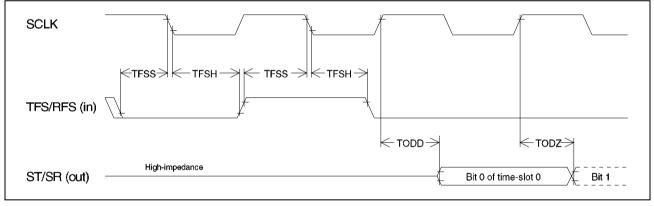

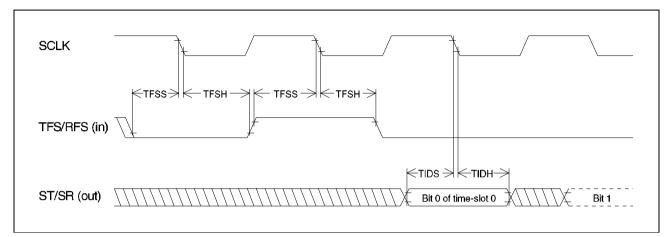

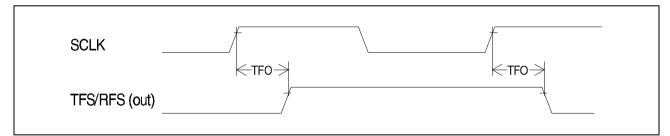

Figure 8 shows an example where RFS is input and TFS is output.

#### Figure 8

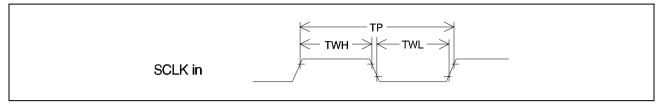

SCLK Input or output

Bits on SR/ST are clocked out with the rising edge of SCLK and latched in with the falling edge of SCLK. Alternatively, bits can be clocked out with the falling edge of SCLK and latched in with the rising edge. When SCLK is programmed as output, it is derived from a programmable baud rate generator. Additionaly, SLCK can be set to strobed operation.

RFS Input or output

Marks the beginning of the physical frame on SR.

When input Sampled with a falling edge of SCLK.

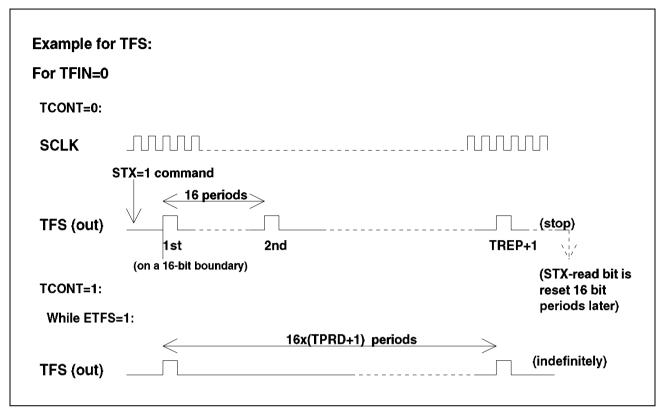

When outputClocked out with the rising or falling edge of SCLK<br/>(duration = 1 SCLK period).<br/>Repetition rate (continuous mode) or number of<br/>pulses (burst mode) is programmable

TFS Input or output

Marks the beginning of the physical frame on ST.

When input Sampled with a falling edge of SCLK.

When outputClocked out with the rising or falling edge of SCLK

(duration = 1 SCLK period).

Repetition rate (continuous mode) or number of pulses (burst mode) is programmable.

SCLK is derived from the chip-internal DSP clock via a programmable baud rate generator (division factor 1, 2, 3, ..., 1024).

The Receive Frame Sync (RFS), when programmed as output, has two selectable modes of operation:

In the continuous mode (CONT = 1), pulses are continuously generated, separated by a distance

$16 \times (PRD + 1)$  bits from each other, where PRD = 0, ..., 255.

In the **burst mode** (CONT = 0), pulses are generated upon command a programmable number of times (REP + 1: 1, ..., 1024), spaced 16 bits apart from each other.

The same applies to TFS when it is an output.

# Channels

| Two Audio receive and transmit channels | Independently programmable on SR, ST,<br>DU or DD with programmable locations<br>(start at bit 1 512) and lengths<br>(1 32 bits) with respect to RFS/TFS.  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Two HDLC receive and transmit channels  | Independently programmable on SR, ST,<br>DU or DD with programmable locations<br>(start at bit 1 512) and lengths<br>(1 256 bits) with respect to RFS/TFS. |

# 3.1.3 Parallel Host Interface

The parallel host interface can be selected to be either of the

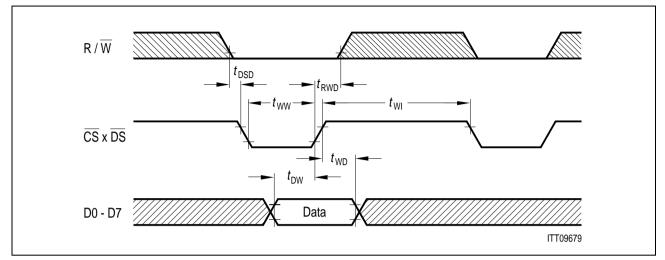

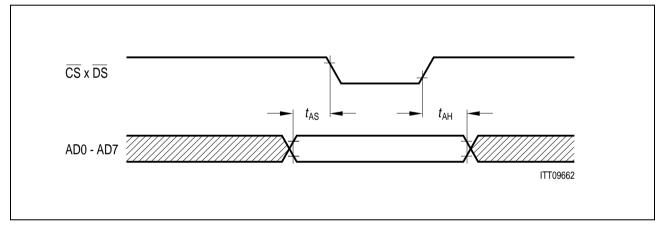

- 1. Motorola type with control signals  $\overline{CS}$ , R/W,  $\overline{DS}$

- 2. Siemens/Intel demultiplexed bus type with control signals CS, WR, RD

- 3. or of the Siemens/Intel multiplexed address/data bus type with control signals <del>CS</del>, <del>WR</del>, <del>RD</del>, ALE

The selection is performed via pin ALE as follows:

ALE tied to  $V_{\text{DD}} \rightarrow (1)$

ALE tied to  $V_{SS} \rightarrow (2)$

Edge on ALE  $\rightarrow$  (3)

The occurrence of an edge on ALE, either positive or negative, at any time during the operation immediately selects the multiplexed bus type. A return to one of the other is possible only if a hardware reset is issued.

# 3.1.4 External Memory Interface

The external memory interface allows the connection of both program and data memories to the PSB 7238. The access to either type of memory is determined by the signals  $\overline{CPS}$  and  $\overline{CDS}$ , respectively. In standard applications, the external memory interface used as a program memory interface is normally not needed, but is reserved for development purposes.

The upper 32k half ( $8000_{H}$  - FFFF<sub>H</sub>) of the address space is reserved for execution of software from external memory.

For executing software in the lower address range  $0000_{H} - 7FFF_{H}$ , a control line EA (External Access) determines whether program is fetched from internal or external memory. Thus, in standard applications, the EA line should always be "high".

The DSP program execution can be controlled from the outside by loading the PC-counter of the DSP via the parallel host interface.

The external memory interface implements:

- protection against reading the internal ROM.

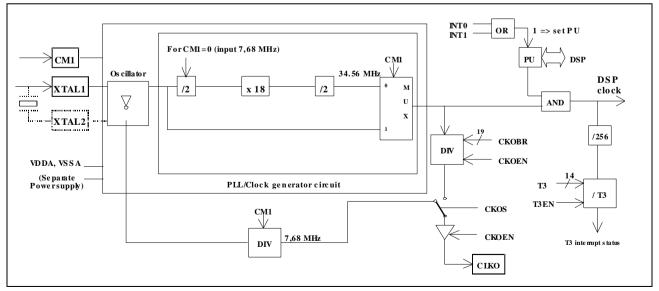

# 3.1.5 Clock Interface

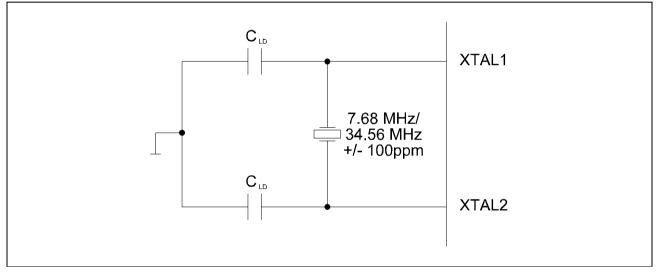

The chip internal clock is derived from a crystal connected across XTAL1,2 or from an external clock input via pin XTAL1. Two different clock options are provided, controlled by the clock mode pin CM1.

These clock modes are:

- CM1 = 0 The internal clock circuitry generates a frequency 4.5 times the input on XTAL1(,2). The internal frequency required is 34.56 MHz and is obtained by providing a frequency of 7.68 MHz on XTAL1 input.

- CM1 = 1 The internal frequency is directly input via XTAL1(,2). When using a crystal, a 34.56 MHz crystal swinging at its basic harmonic has to be connected to XTAL1,2.

After reset the pin CLKO outputs a frequency of 7.68 MHz, independent of the selection of CM1 bit. Alternatively, CLKO can be programmed to output the frequency of a programmable divider (CKOS bit in register  $2002_{\rm H}$ ). Thus, a clock of frequency equal to the internal clock divided by a programmable baud rate factor (1, 2, 3, ..., 2<sup>19</sup>) can be generated.

When using the PLL (CM1 = 0), it is made sure that during reset phase CLKO delivers a continuous 7.68 MHz clock. When using the non-PLL mode (CM1 = 1) CLKO goes low while reset phase.

# 3.2 Shared Memories

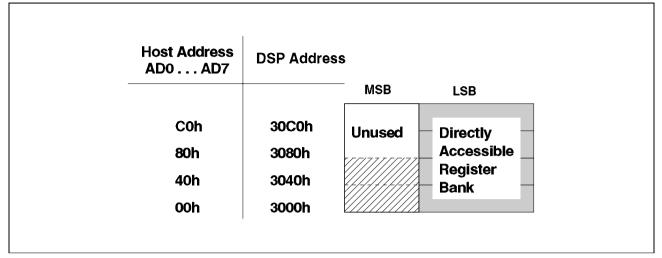

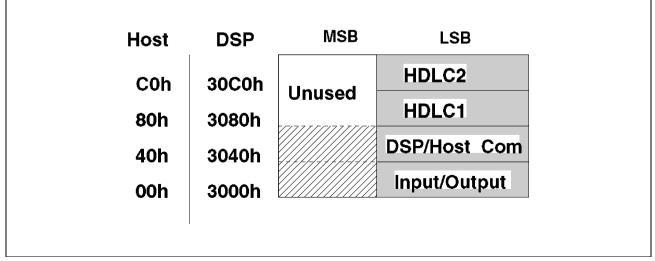

Note: The absolute addresses for the different internal register banks and memories are given here and in the rest of this Data Sheet both as seen from the host **and** from the embedded DSP, the latter information being included for the sake of completeness only.

# Directly Accessible Register Bank (DARB)

The host accesses directly via its 8-bit address bus the so-called **Directly Accessible Register Bank (DARB)** located between DSP addresses  $3000_{H}$  and  $30FF_{H}$ .

#### Figure 9

This area is in turn divided into four blocks of 64 bytes each according to their functions. Not all the addresses in each of these 64-byte areas are used. An overview of the functions of these 64-byte areas is given in **Figure 10**, please refer also to the appropriate chapters for a detailed description.

- 1. Locations for reading and writing samples "in real time" from/to the serial interfaces (IOM-2 and serial audio interface) **Input/Output area** (see **Chapter 3.3.1**)

- 2. Area for communication between the host and the embedded DSP, for programming parameters and reporting status conditions **DSP/Host Com area** (see **Chapter 3.3.2** and **Chapter 3.3.3**)

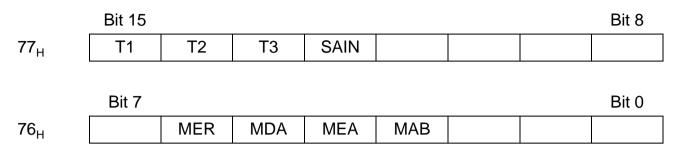

- 3. Register bank for HDLC Controller 1 accessed by host if HHA1 (configuration bit) is '1' - HDLC1

- 4. Register bank for HDLC Controller 2 accessed by host if HHA2 (configuration bit) is '1' - HDLC2

# Figure 10

# **3.3 Directly Accessible Register Bank**

# 3.3.1 Input/Output Registers

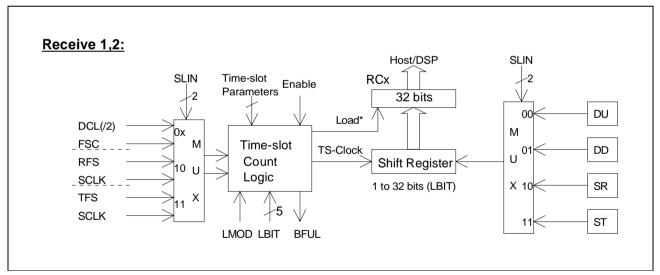

This area contains the locations for receiving/transmitting real-time audio and data between the serial interfaces (IOM-2 and serial audio interface) and the host (or embedded DSP).

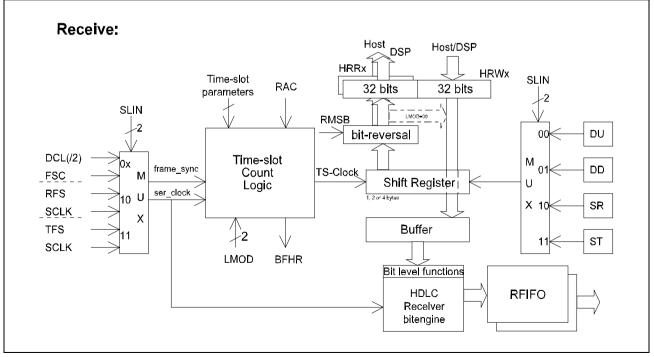

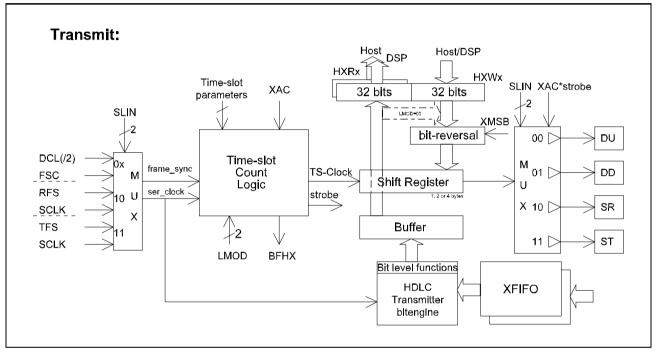

The PSB 7238 implements two receive and two transmit audio channels, denoted RC1,2 and XC1,2 respectively. Further, two receive and two transmit channels are provided to access the HDLC1,2 receiver input data and the HDLC1,2 transmitter output, respectively, called HR1,2 and HX1,2.

Transfer of audio samples is interrupt supported, whereby two possibilities are provided:

- interrupt status generated after a programmable number of bits (1, ..., 32) have been shifted in/out;

- interrupt indicating the start of a physical frame (normally at 8 kHz, either from FSC, RFS or TFS frame sync pulses): in this case the number of significant bits depends on the time-slot length programmed for that channel on the line (DU/DD/SR/ST).

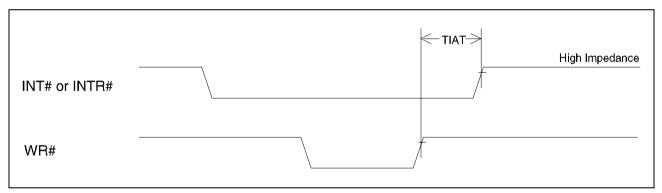

The interrupt statuses may generate a maskable interrupt on the high priority interrupt lines INTR (Host) and/or INTO (embedded DSP), respectively.

RC1, RC2, XC1, XC2, HR1, HR2, HX1, HX2 channel registers are located in the address range  $00_H - 3F_H$  for the host, and in the memory mapped area  $3000_H - 303F_H$  for the DSP. The register banks for the host and the DSP are physically separate from each other. The read registers and write registers are physically separate.

The addresses for these registers are such that a 32-bit sample can be accessed from the DSP via only two 16-bit read/write operations (16-bit data bus). From the host, the access is byte-by-byte (8-bit data bus).

# List of Registers

- RC1: 32-bit register for audio receive channel 1 (read)

- RC2: 32-bit register for audio receive channel 2 (read)

- XC1: 32-bit register for audio transmit channel 1 (write)

- XC2: 32-bit register for audio transmit channel 2 (write)

- HRR1: 32-bit register for reading data from HDLC receiver 1 input shift register

- HRW1: 32-bit register for writing data to be loaded into HDLC receiver 1 input

- HXR1: 32-bit register for reading data from HDLC transmitter 1 output

- HXW1: 32-bit register for writing data to HDLC transmitter 1 output shift register

- HRR2: 32-bit register for reading data from HDLC receiver 2 input shift register

- HRW2: 32-bit register for writing data to be loaded into HDLC receiver 2 input

- HXR2: 32-bit register for reading data from HDLC transmitter 2 output

- HXW2: 32-bit register for writing data to HDLC transmitter 2 output shift register

# **Memory Map**

|                         | Access from the           | Host                      |

|-------------------------|---------------------------|---------------------------|

| COF                     | <br>۱                     | HDLC2                     |

| 80h                     | ;<br>                     | HDLC1                     |

| 40h                     |                           | DSP/Host Com              |

| -00h                    |                           | Input/Output              |

| Host Address<br>A0 - A7 | Host Write                | Host Read                 |

| 1Fh                     | HXW2 (31:24)              | HXR2 (31:24)              |

| 1Eh                     | HXW2 (23:16)              | HXR2 (23:16)              |

| 1Dh                     | HXW2 (15:8)               | HXR2 (15:8)               |

| 1Ch                     | HXW2 (7:0)                | HXR2 (7:0)                |

| 1Bh                     | HRW2 (31:24)              | HRR2 (31:24)              |

| 1Ah                     | HRW2 (23:16)              | HRR2 (23:16)              |

| 19h                     | HRW2 (15:8)               | HRR2 (15:8)               |

| 18h                     | HRW2 (7:0)                | HRR2 (7:0)                |

| 17h                     | HXW1 (31:24)              | HXR1 (31:24)              |

| 16h                     | HXW1 (23:16)              | HXR1 (23:16)              |

| 15h                     | HXW1 (15:8)               | HXR1 (15:8)               |

| 14h                     | HXW1 (7:0)                | HXR1 (7:0)                |

| 13h                     | HRW1 (31:24)              | HRR1 (31:24)              |

| 12h                     | HRW1 (23:16)              | HRR1 (23:16)              |

| 11h<br>10h              | HRW1 (15:8)<br>HRW1 (7:0) | HRR1 (15:8)<br>HRR1 (7:0) |

| 10n                     |                           |                           |

| 07h                     | XC2 (31:24)               | RC2 (31:24)               |

| 06h                     | XC2 (23:16)               | RC2 (23:16)               |

| 05h                     | XC2 (15:8)                | RC2 (15:8)                |

| 04h                     | XC2 (7:0)                 | RC2 (7:0)                 |

| 03h                     | XC1 (31:24)               | RC1 (31:24)               |

| 02h                     | XC1 (23:16)               | RC1 (23:16)               |

| 01h                     | XC1 (15:8)                | RC1 (15:8)                |

| 00h                     | XC1 (7:0)                 | RC1 (7:0)                 |

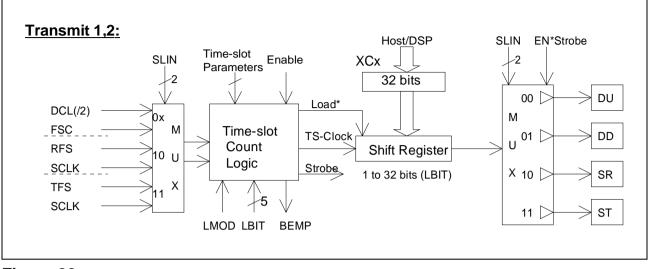

Figure 11

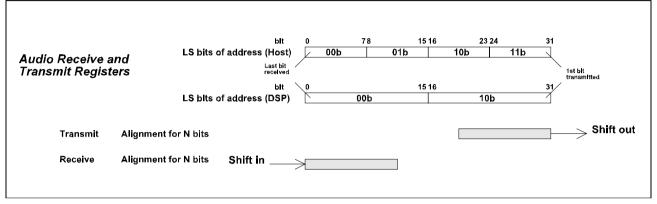

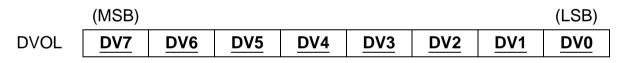

#### Alignment of Data for Audio Channels

The most significant bit is always the first bit received/transmitted. Therefore, if audio is processed in units of N bits (N programmable between 1 and 32), the alignment of the data for receive and transmit audio channels in the registers is as shown in the **Figure 12**.

#### Figure 12

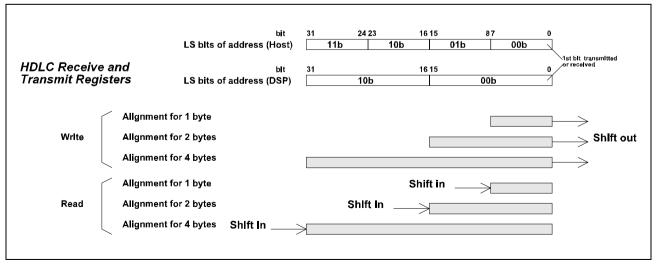

# Alignment of Data for HDLC/Transparent Serial Data Receiver and Transmitter Registers

In the HDLC controllers the reception/transmission of most significant or least significant bit can be selected by control switches (RMSB, XMSB). Nevertheless, for serial data communication, the convention is that the least significant bit of user data is received/transmitted first. In order to have an identical format for the data in the serial controller input/output registers as in the FIFOs, the data is aligned in the registers as shown below (the available options for data unit sizes when pre/postprocessing HDLC/transparent data are: 1, 2 or 4 bytes).

#### Figure 13

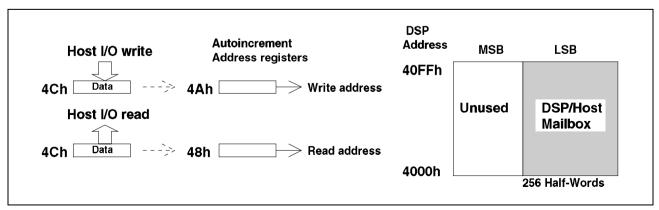

# 3.3.2 DSP/Host Com Area with a Multiplexed Host Interface

The DSP/host communication area contains the registers to support hardware and software interrupts and special purpose registers that support communication between the embedded DSP and the host. In multiplexed mode, address and data are multiplexed on pins AD(0-7). It is necessary e.g for indirect programming of the configuration and control registers from the host and for a complete access to all host addresses.

# 3.3.2.1 Access to DSP/Host Com Area

The address mapping in multiplexed mode is given in Table 9.

| DSP               | DSP Write               | DSP Read                 | Host                              | Host Write                    | Host Read                       |

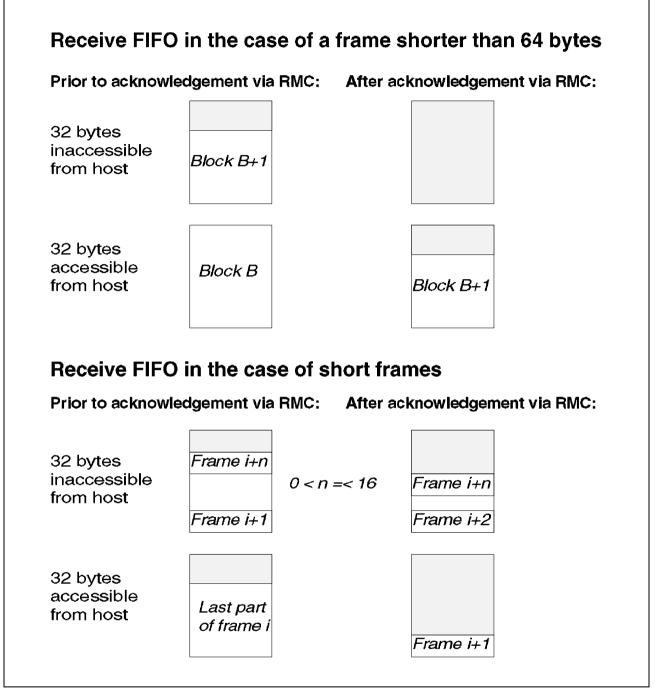

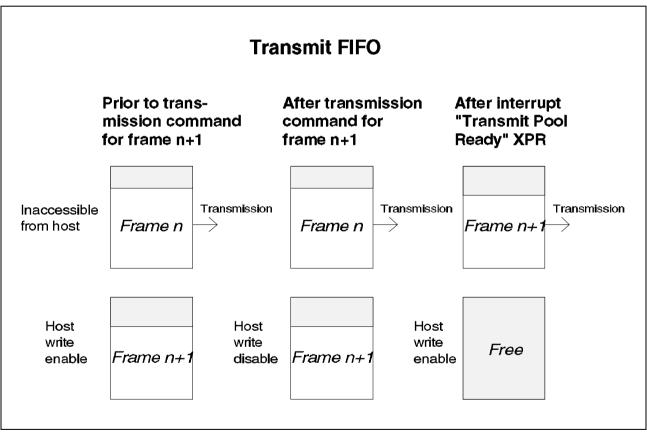

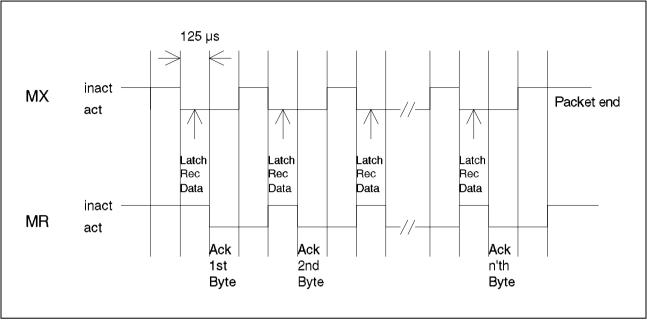

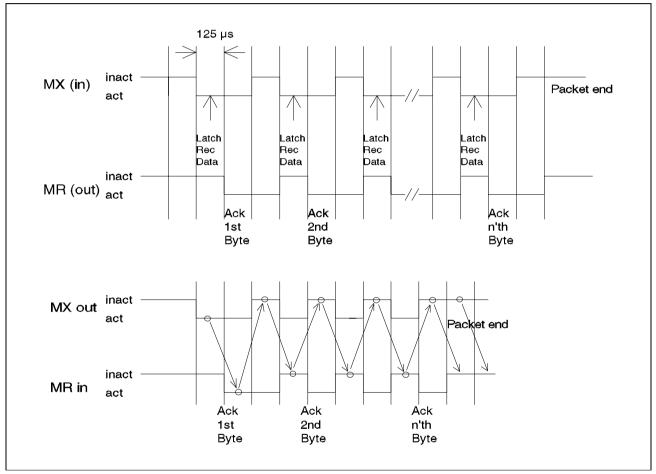

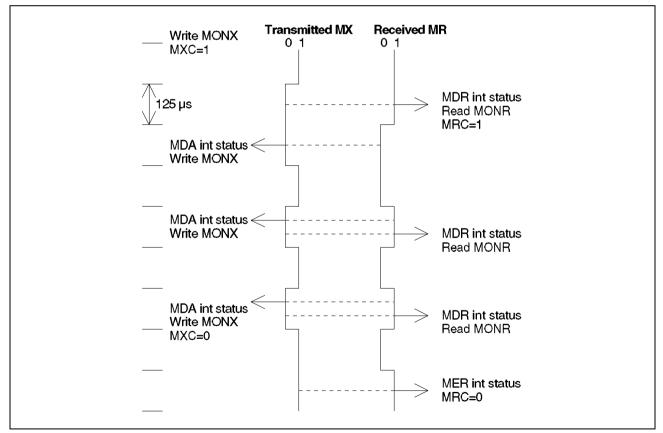

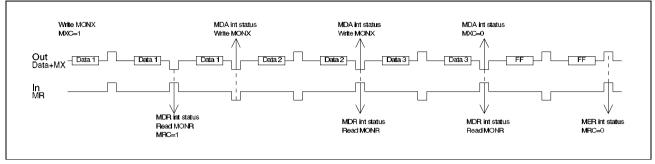

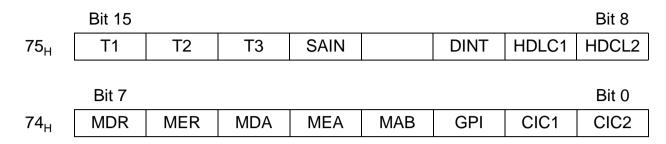

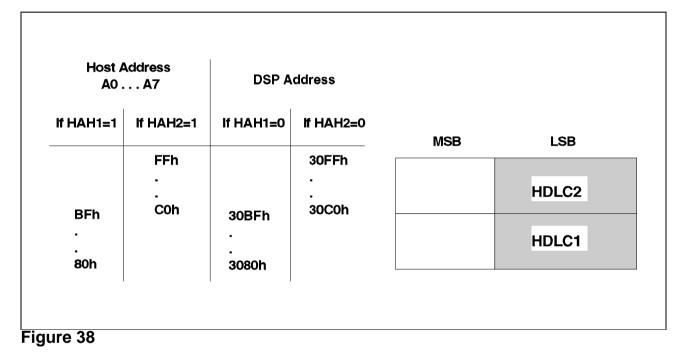

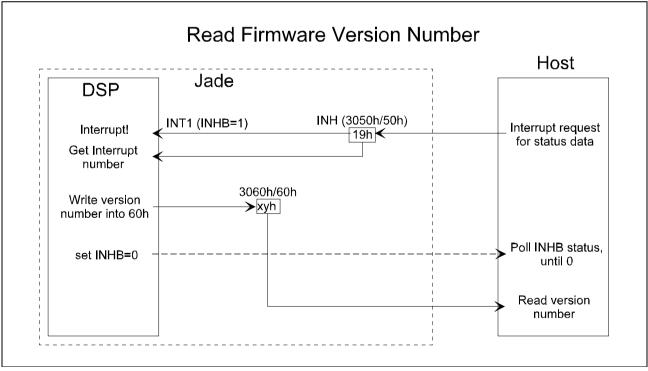

|-------------------|-------------------------|--------------------------|-----------------------------------|-------------------------------|---------------------------------|