Wired Communications

Edition 2001-12-17

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# ABM 3G ATM Buffer Manager PXF 4333 Version 1.1

Wired Communications

| ΔR | M-3 | C | Da | ta | SI | neet |

|----|-----|---|----|----|----|------|

|    |     |   |    |    |    |      |

| Revision H  | istory:      | 2001-12-17                               | DS 1 |

|-------------|--------------|------------------------------------------|------|

| Previous Ve | ersion:      | none                                     |      |

| Page        | Subjects (ma | ajor changes since last revision)        |      |

|             | Reworked fr  | om preliminary to first finalized status |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

|             |              |                                          |      |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

#### Disclaimer:

This data sheet describes a product under development by Infineon Technologies AG ('Infineon'). Infineon reserves the right to change features and characteristics of the product or to discontinue this product without notice. None of the information contained in this document constitutes an express or implied assurance of availability or functionality. Please contact Infineon for the latest information on the product.

| Table of | Contents                                                      | Page |

|----------|---------------------------------------------------------------|------|

| 1        | Overview                                                      | 19   |

| 1.1      | Features                                                      | 20   |

| 1.1.1    | Queueing Functions                                            | 20   |

| 1.1.2    | Scheduling Functions                                          | 21   |

| 1.1.3    | Interfaces                                                    | 21   |

| 1.1.4    | Supervision Functions                                         | 22   |

| 1.1.5    | Technology                                                    | 22   |

| 1.2      | Logic Symbol                                                  | 23   |

| 1.3      | Typical Applications                                          | 24   |

| 2        | Pin Descriptions                                              | 25   |

| 2.1      | Pin Diagram                                                   | 25   |

| 2.2      | Pin Diagram with Functional Groupings                         | 26   |

| 2.3      | Pin Definitions and Functions                                 | 27   |

| 2.3.1    | Common System Clock Supply (3 pins)                           | 27   |

| 2.3.2    | UTOPIA Receive Interface Upstream (Master/Slave) (32 pins)    | 28   |

| 2.3.3    | UTOPIA Transmit Interface Downstream (Master/Slave) (32 pins) | 29   |

| 2.3.4    | UTOPIA Receive Interface Downstream (Master/Slave) (32 pins)  | 31   |

| 2.3.5    | UTOPIA Transmit Interface Upstream (Master/Slave) (32 pins)   | 32   |

| 2.3.6    | Microprocessor Interface (32 pins)                            | 33   |

| 2.3.7    | Cell Storage RAM Upstream (50 pins)                           |      |

| 2.3.8    | Cell Storage RAM Downstream (50 pins)                         | 37   |

| 2.3.9    | Common Up- and Downstream Cell Pointer RAM (42 pins)          |      |

| 2.3.10   | JTAG Boundary Scan (5 pins)                                   |      |

| 2.3.11   | Production Test (2 pin)                                       |      |

| 2.3.12   | Supply (74 VSS, 32 VDD33 and 14 VDD18 pins)                   |      |

| 2.3.13   | Unconnected (13 pins)                                         | 42   |

| 3        | Functional Description                                        |      |

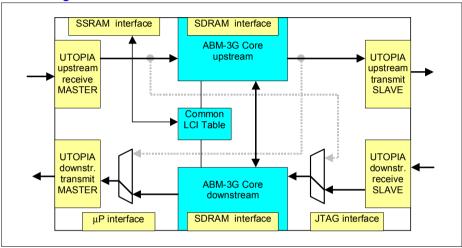

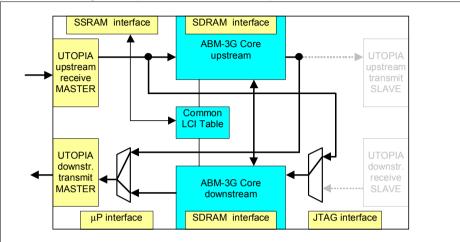

| 3.1      | Block Diagrams                                                |      |

| 3.1.1    | Throughput and Speedup                                        |      |

| 3.2      | Functional Block Description                                  |      |

| 3.2.1    | Cell Handler (Upstream/Downstream)                            |      |

| 3.2.2    | Buffer Manager and Queue Scheduler (Overview)                 |      |

| 3.2.3    | AAL5 Assistant                                                |      |

| 3.2.4    | Internal Address Reduction Unit                               |      |

| 3.2.5    | Clocking System                                               |      |

| 3.2.5.1  | Clocking System Overview                                      |      |

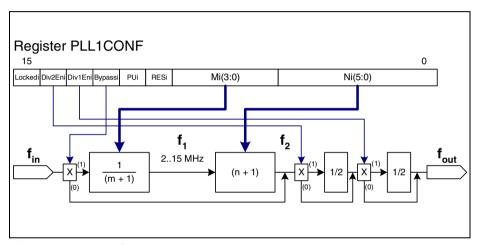

| 3.2.5.2  | DPLL Programming                                              |      |

| 3.2.5.3  | Programming Example                                           |      |

| 3.2.5.4  | Initialization Phase                                          |      |

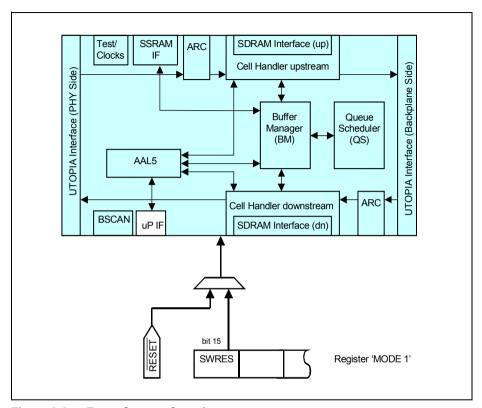

| 3.2.6    | Reset System                                                  |      |

| 3.3      | System Integration                                            | 55   |

| Table of | Contents                                            | Page |

|----------|-----------------------------------------------------|------|

| 3.3.1    | LCI Translation in Mini-Switch Configurations       | 58   |

| 3.4      | Buffer Manager and Queue Scheduler Details          |      |

| 3.4.1    | Buffer Manager                                      | 61   |

| 3.4.1.1  | Functional Overview                                 |      |

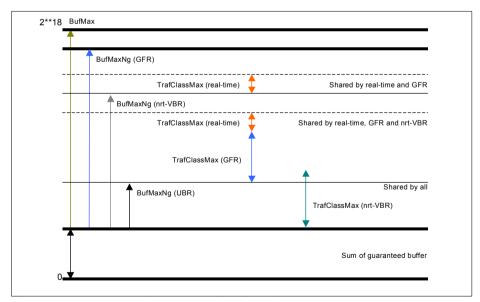

| 3.4.1.2  | Logical Buffer Views                                | 62   |

| 3.4.1.3  | Threshold Classification                            | 64   |

| 3.4.1.4  | Counter Classification                              | 65   |

| 3.4.1.5  | Threshold and Occupancy Counter Overview            | 65   |

| 3.4.1.6  | Discard Mechanisms and Buffer Reservation           |      |

| 3.4.1.7  | Cell Acceptance Algorithm                           | 71   |

| 3.4.1.8  | Statistical Counters                                |      |

| 3.4.2    | Queue Scheduler                                     |      |

| 3.4.2.1  | Functional Overview                                 |      |

| 3.4.2.2  | Scheduler Block                                     |      |

| 3.4.2.3  | Quality of Service Support                          |      |

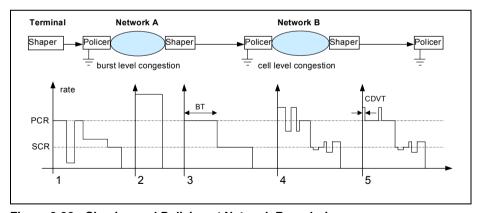

| 3.4.2.4  | Traffic Shaping                                     |      |

| 3.4.2.5  | VC-Merge and Dummy Queue                            |      |

| 3.4.3    | Scheduler Block Usage                               |      |

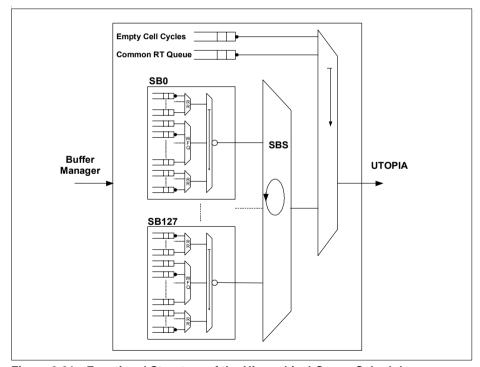

| 3.4.4    | Scheduler Block Scheduler (SBS)                     |      |

| 3.4.5    | Supervision Functions                               |      |

| 3.4.5.1  | Cell Header Protection                              |      |

| 3.4.5.2  | Cell Queue Supervision                              |      |

| 3.4.5.3  | Scan Unit                                           |      |

| 3.5      | Internal Tables                                     |      |

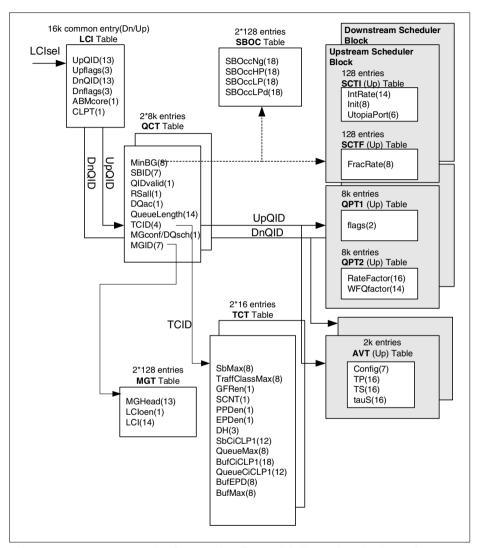

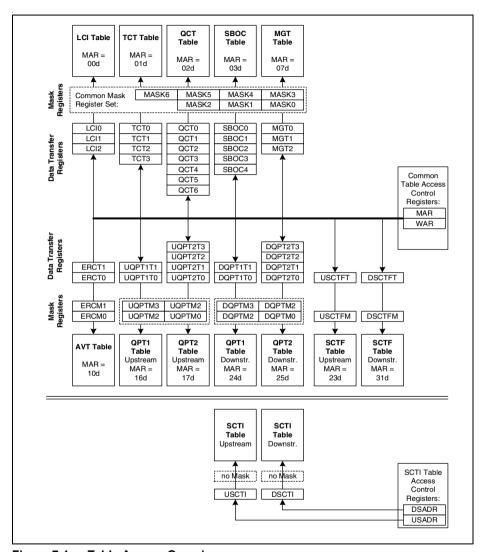

| 3.5.1    | Table Overview                                      |      |

| 3.5.2    | LCI: Local Connection Identifier Table              |      |

| 3.5.3    | QCT: Queue Configuration Table                      |      |

| 3.5.4    | QPT: Queue Parameter Table                          |      |

| 3.5.5    | TCT: Traffic Class Table                            |      |

| 3.5.6    | SBOC: Scheduler Block Occupancy Table               |      |

| 3.5.7    | SCT: Scheduler Configuration Table                  |      |

| 3.5.8    | MGT: Merge Group Table                              |      |

| 3.5.9    | AVT: VBR Configuration Table                        |      |

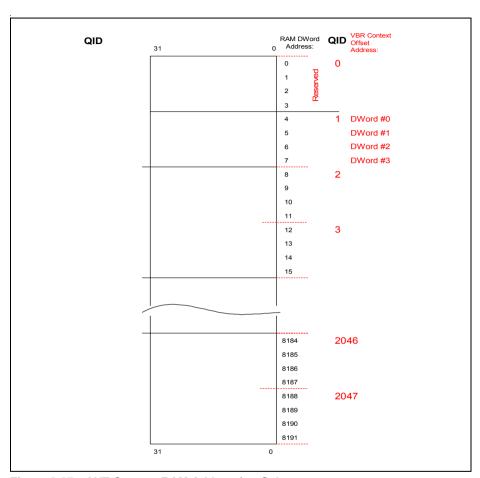

| 3.5.9.1  | AVT Context RAM Organization and Addressing         |      |

| 3.5.9.2  | AVT Context RAM Section for VBR Shaping Support     |      |

| 3.5.9.3  | Common AVT CONFIG Field                             |      |

| 4        | Operational Description                             |      |

| 4.1      | Basic Device Initialization                         |      |

| 4.2      | Basic Traffic Management Initialization             |      |

| 4.2.1    | Setup of Queues                                     |      |

| 4.2.2    | Programming Queue Scheduler Rates and Granularities |      |

| 4.2.2.1  | Scheduler Block Scheduler                           | 106  |

| Table of | Contents                                         | Page  |

|----------|--------------------------------------------------|-------|

| 4.2.2.2  | Programming the Scheduler Block Rates            | . 106 |

| 4.2.2.3  | Programming the Common Real-Time Bypass          |       |

| 4.2.2.4  | Programming the SDRAM Refresh Empty Cell Cycles  |       |

| 4.2.2.5  | Programming the PCR Limiter                      |       |

| 4.2.2.6  | Programming the Leaky Bucket Shaper              |       |

| 4.2.2.7  | Guaranteed Cell Rates and WFQ Weight Factors     |       |

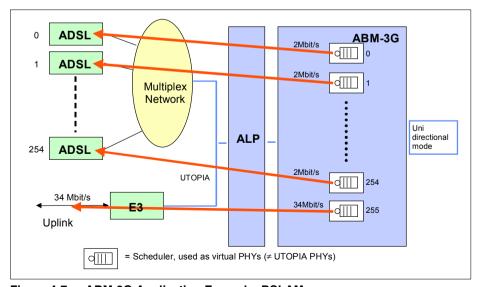

| 4.2.3    | ABM-3G Configuration Example                     |       |

| 4.2.4    | Normal Operation                                 | . 116 |

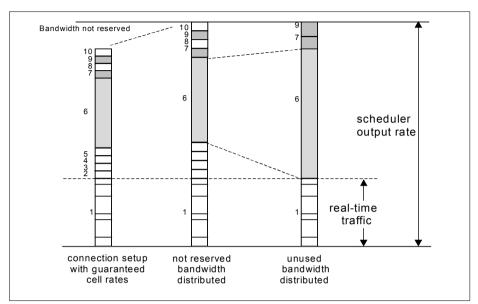

| 4.2.5    | Bandwidth Reservation                            | . 116 |

| 4.2.5.1  | Bandwidth Reservation Example                    | . 117 |

| 4.2.6    | Buffer Reservation                               | . 118 |

| 4.2.7    | Support of Standard ATM Service Categories       | . 119 |

| 4.2.7.1  | CBR Connections                                  | . 119 |

| 4.2.7.2  | rt-VBR Connections                               | . 119 |

| 4.2.7.3  | nrt-VBR Connections                              | . 119 |

| 4.2.7.4  | UBR+ Connections                                 | . 119 |

| 4.2.7.5  | GFR Connections                                  | . 120 |

| 4.2.7.6  | UBR Connections                                  | . 120 |

| 4.2.7.7  | Generic Service Classes                          | . 120 |

| 4.3      | Connection Teardown Example                      | . 121 |

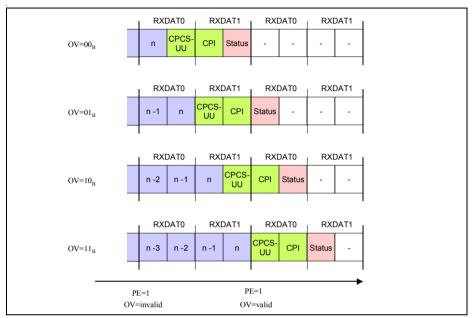

| 4.4      | AAL5 Packet Insertion/Extraction                 | . 121 |

| 4.4.1    | AAL5 Packet Insertion                            | . 121 |

| 4.4.2    | AAL5 Packet Extraction                           | . 121 |

| 4.5      | Exception Handling                               | . 123 |

| 5        | Interface Description                            | . 124 |

| 5.1      | UTOPIA L2 Interfaces (PHY side)                  |       |

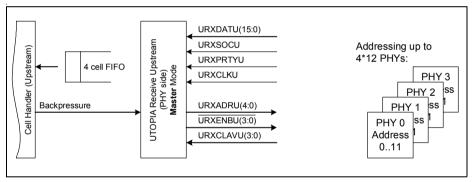

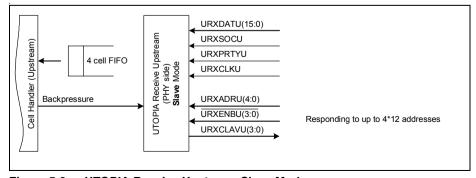

| 5.1.1    | URXU: UTOPIA Receive Upstream (PHY side)         |       |

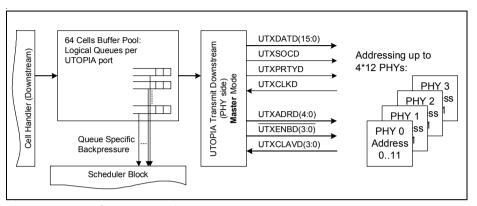

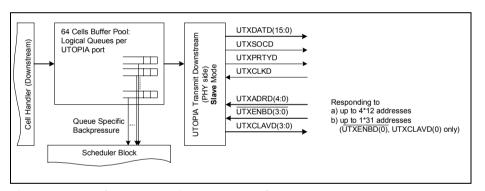

| 5.1.2    | UTXD: UTOPIA Transmit Downstream (PHY side)      |       |

| 5.1.3    | UTOPIA Port/Address Mapping (PHY side)           | . 127 |

| 5.1.4    | Functional UTOPIA Timing (PHY side)              | . 128 |

| 5.1.5    | UTOPIA Master Mode Polling Scheme (PHY side)     | . 129 |

| 5.1.6    | UTOPIA Cell Format (PHY side)                    | . 130 |

| 5.1.6.1  | UTOPIA Level 2 Standard Cell Formats             | . 130 |

| 5.1.6.2  | LCI Mapping Mode: VPI Mode                       | . 131 |

| 5.1.6.3  | LCI Mapping Mode: VCI Mode                       | . 131 |

| 5.1.6.4  | LCI Mapping Mode: Infineon Mode                  |       |

| 5.1.6.5  | LCI Mapping Mode: Address Reduction Mode         | . 132 |

| 5.2      | UTOPIA L2 Interface (Backplane side)             |       |

| 5.2.1    | URXD: UTOPIA Receive Downstream (Backplane side) |       |

| 5.2.2    | UTXU: UTOPIA Transmit Upstream (Backplane side)  |       |

| 5.2.3    | UTOPIA Port/Address Mapping (Backplane side)     | . 134 |

| 5.2.4    | Functional UTOPIA Timing (Backplane side)        |       |

| Table of                                                                                                                | Contents P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | age                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 5.2.5<br>5.2.6<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.4<br>5.4.1<br>5.5<br>5.6<br>5.6.1<br>5.6.2      | UTOPIA Master Mode Polling Scheme (Backplane side) UTOPIA Cell Format (Backplane side) MPI: Microprocessor Interface Intel Style Write Access Intel Style Read Access Motorola Style Write Access Motorola Style Read Access Interrupt Signals External RAM Interfaces RAM Configurations Test Interface Clock and Reset Interface Clocking Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 134<br>135<br>135<br>135<br>136<br>137<br>137<br>138<br>141<br>141<br>141        |

| 6                                                                                                                       | Memory Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 142                                                                              |

| 7 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.2.5 7.2.6 7.2.7 7.2.8 7.2.9 7.2.10 7.2.11 7.2.12 7.2.13 7.2.14 7.2.15 7.2.16 7.2.17 | Register Description Overview of the ABM-3G Register Set Detailed Register Descriptions Cell Flow Test Registers SDRAM Configuration Registers Cell Insertion/Extraction and AAL5 Control Registers Buffer Occupation Counter Registers Buffer Threshold and Occupation Capture Registers Configuration Register Backpressure Control Registers LCI Table Transfer Registers LCI Table Transfer Registers Traffic Class Table Transfer Registers Queue Configuration Table Transfer Registers Scheduler Block Occupancy Table Transfer Registers Merge Group Table Transfer Registers Mask Registers Rate Shaper CDV Registers Queue Parameter Table Mask Registers Scheduler Configuration Register Queue Parameter Table Transfer Registers Scheduler Block Configuration Table Transfer/Mask Registers | 158<br>174<br>176<br>181<br>181<br>195<br>211<br>223<br>230<br>235<br>240<br>246 |

| 7.2.19<br>7.2.20<br>7.2.21                                                                                              | SDRAM Refresh Registers UTOPIA Port Select of Common Real Time Queue Registers 257 Scheduler Block Enable Registers Common Real Time Queue Rate Registers AVT Table Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 278                                                                              |

| Table of                                                                     | Contents                                                                                                                                                                                                                                          | Page                                               |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 7.2.22<br>7.2.23<br>7.2.24<br>7.2.25<br>7.2.26<br>7.2.27<br>7.2.28<br>7.2.29 | PLL Control Registers External RAM Test Registers ABM-3G Version Code Registers Interrupt Status/Mask Registers RAM Select Registers Global ABM-3G Status and Mode Registers UTOPIA Configuration Registers Test Registers/Special Mode Registers | . 290<br>. 295<br>. 297<br>. 307<br>. 311<br>. 317 |

| 8                                                                            | Electrical Characteristics                                                                                                                                                                                                                        |                                                    |

| 8.1                                                                          | Absolute Maximum Ratings                                                                                                                                                                                                                          |                                                    |

| 8.2                                                                          | Operating Range                                                                                                                                                                                                                                   |                                                    |

| 8.3                                                                          | DC Characteristics                                                                                                                                                                                                                                |                                                    |

| 8.4                                                                          | AC Characteristics                                                                                                                                                                                                                                |                                                    |

| 8.4.1                                                                        | Microprocessor Interface Timing Intel Mode                                                                                                                                                                                                        |                                                    |

| 8.4.1.1                                                                      | Microprocessor Write Cycle Timing (Intel)                                                                                                                                                                                                         |                                                    |

| 8.4.1.2                                                                      | Microprocessor Read Cycle Timing (Intel)                                                                                                                                                                                                          |                                                    |

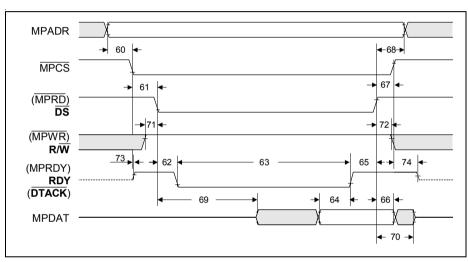

| 8.4.2.1                                                                      | Microprocessor Interface Timing Motorola Mode                                                                                                                                                                                                     |                                                    |

| 8.4.2.1                                                                      | Microprocessor Write Cycle Timing (Motorola)                                                                                                                                                                                                      |                                                    |

| 8.4.3                                                                        | UTOPIA Interface                                                                                                                                                                                                                                  |                                                    |

| 8.4.4                                                                        | CPR SSRAM Interface                                                                                                                                                                                                                               |                                                    |

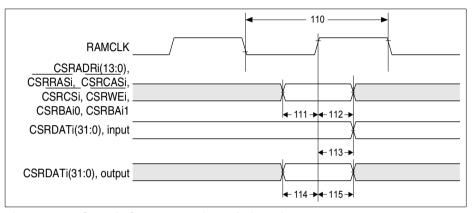

| 8.4.5                                                                        | CSR SDRAM Interface(s)                                                                                                                                                                                                                            |                                                    |

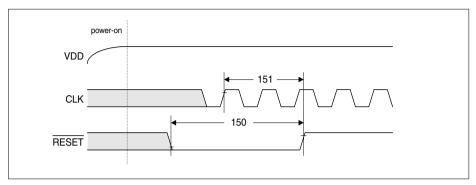

| 8.4.6                                                                        | Reset Timing                                                                                                                                                                                                                                      |                                                    |

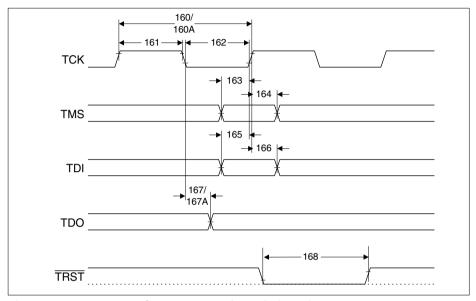

| 8.4.7                                                                        | Boundary-Scan Test Interface                                                                                                                                                                                                                      |                                                    |

| 8.5                                                                          | Capacitances                                                                                                                                                                                                                                      |                                                    |

| 8.6                                                                          | Package Characteristics                                                                                                                                                                                                                           |                                                    |

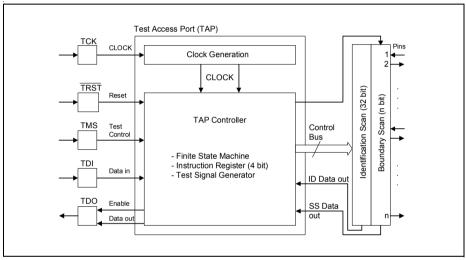

| 9                                                                            | Test Mode                                                                                                                                                                                                                                         | . 356                                              |

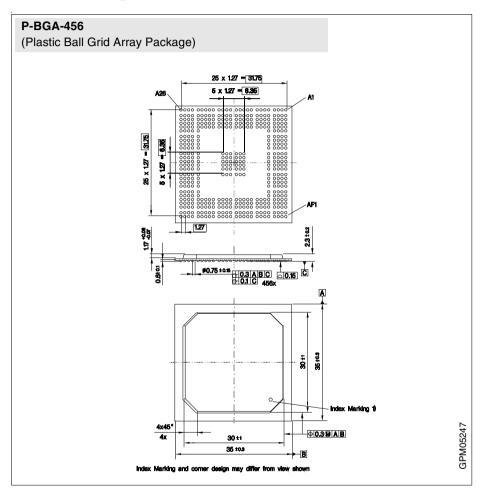

| 10                                                                           | Package Outlines                                                                                                                                                                                                                                  | . 358                                              |

| 11                                                                           | Glossary                                                                                                                                                                                                                                          | . 359                                              |

| List of Figui | res                                                                   | Page  |

|---------------|-----------------------------------------------------------------------|-------|

| Figure 1-1    | Logic Symbol                                                          | 23    |

| Figure 1-2    | General System Integration                                            |       |

| Figure 2-1    | Pin Configuration (Bottom View)                                       |       |

| Figure 2-2    | Pin Configuration (Bottom View)                                       |       |

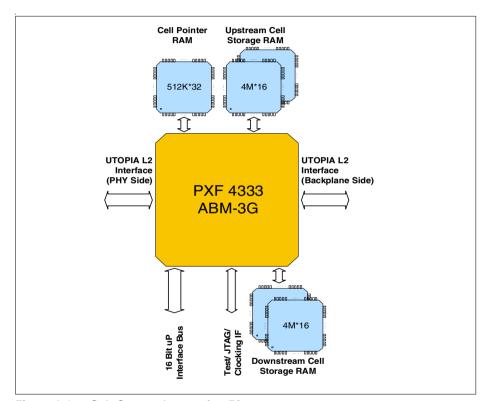

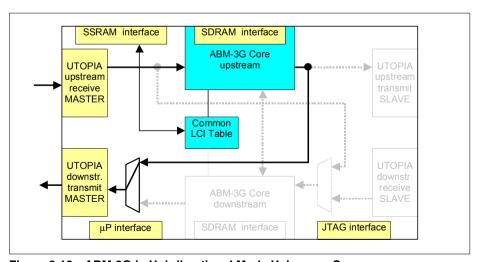

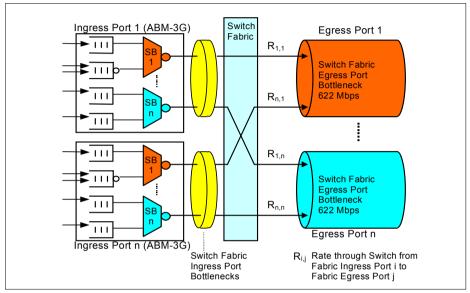

| Figure 3-1    | Sub-System Integration Diagram                                        |       |

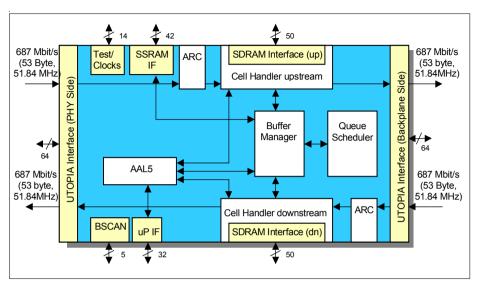

| Figure 3-2    | Functional Block Diagram                                              |       |

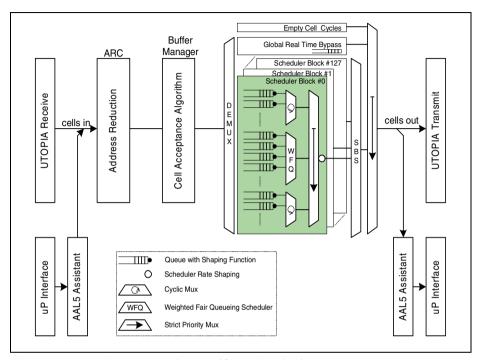

| Figure 3-3    | Logical Block Diagram (One Direction)                                 |       |

| Figure 3-5    | LCI Building Patterns                                                 | 49    |

| Figure 3-6    | LCI Building Patterns (VPI only)                                      | 51    |

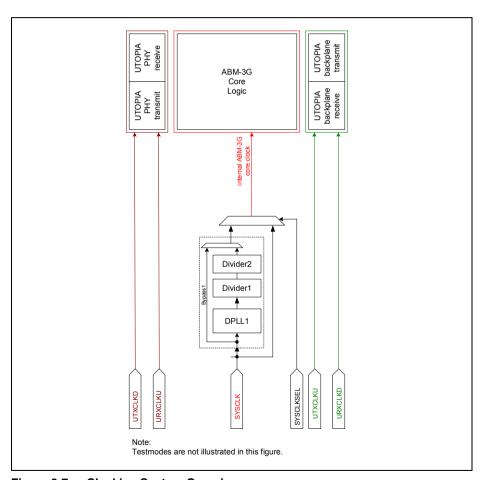

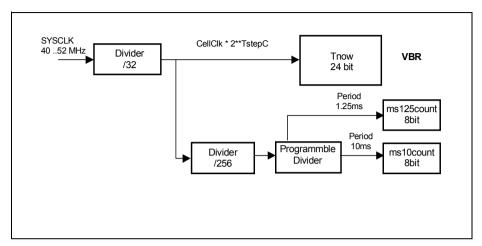

| Figure 3-7    | Clocking System Overview                                              | 52    |

| Figure 3-8    | DPLL Structure                                                        | 53    |

| Figure 3-9    | Reset System Overview                                                 | 55    |

| Figure 3-10   | ABM-3G in Bi-directional Mode                                         |       |

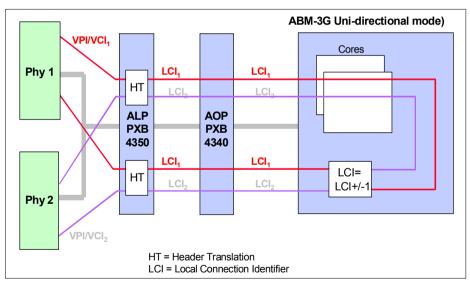

| Figure 3-11   | ABM-3G in Uni-directional Mode Using both Cores                       | 57    |

| Figure 3-12   | ABM-3G in Uni-directional Mode Using one Core                         |       |

| Figure 3-13   | Connection Identifiers in Mini-Switch Configuration                   |       |

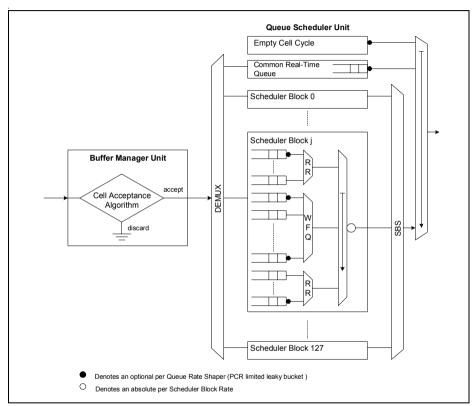

| Figure 3-14   | Cell Acceptance and Scheduling                                        |       |

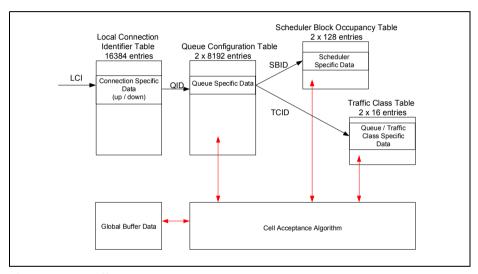

| Figure 3-15   | Buffer Manager Tables                                                 |       |

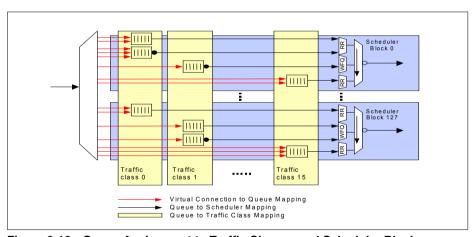

| Figure 3-16   | Queue Assignment to Traffic Classes and Scheduler Blocks              |       |

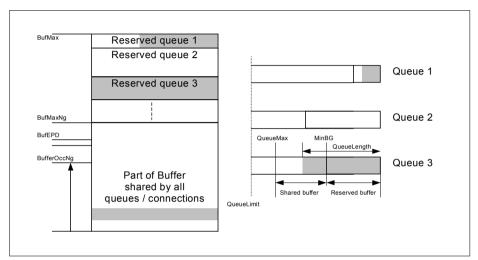

| Figure 3-18   | Buffer Management with per Queue Minimum Buffer Reservation .         |       |

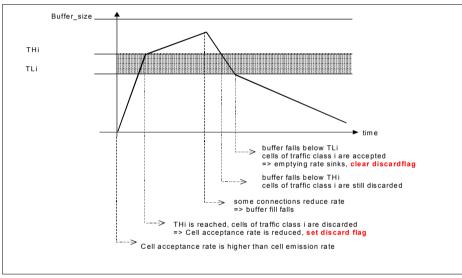

| Figure 3-19   | Buffer Threshold with Hysteresis                                      |       |

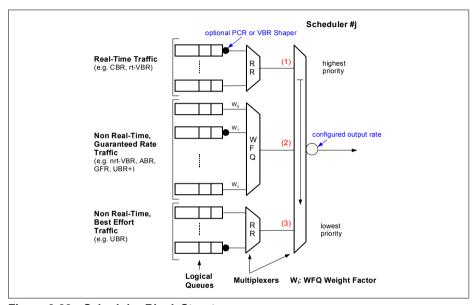

| Figure 3-21   | Functional Structure of the Hierarchical Queue Scheduler              |       |

| Figure 3-22   | Scheduler Block Structure                                             |       |

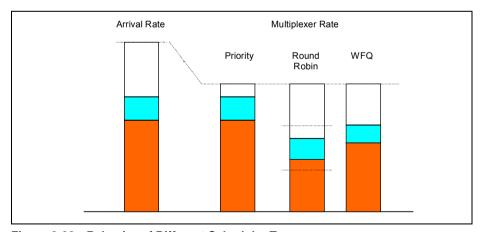

| Figure 3-23   | Behavior of Different Scheduler Types                                 |       |

| Figure 3-25   | Scheduler Behavior Example                                            |       |

| Figure 3-26   | Shaping and Policing at Network Boundaries                            |       |

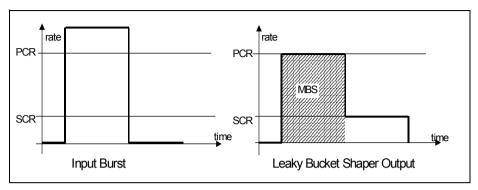

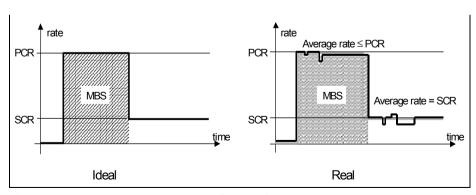

| Figure 3-27   | Ideal ABM-3G Shaper Output                                            |       |

| Figure 3-28   | Ideal and Real ABM-3G Shaper Output.                                  |       |

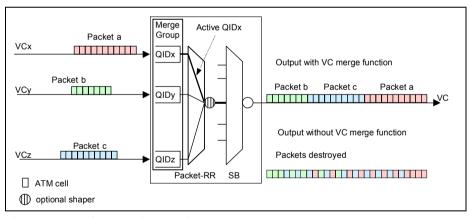

| Figure 3-31   | VC Merge Scheduling                                                   |       |

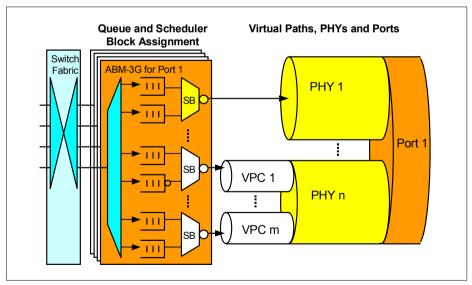

| Figure 3-32   | Scheduler Block Usage at Switch Output                                |       |

| Figure 3-33   | Scheduler Block Usage at Switch Input                                 |       |

| Figure 3-34   | SCAN Timer Generation                                                 |       |

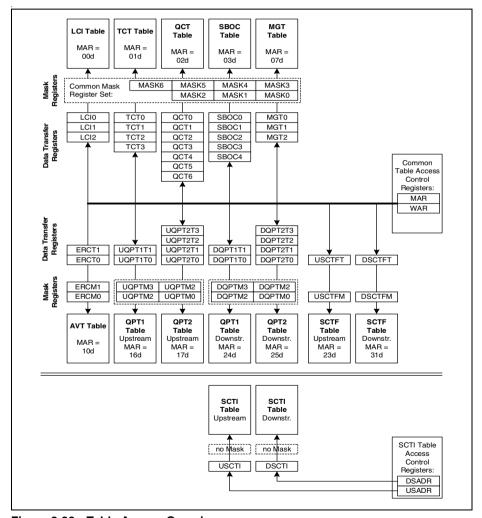

| Figure 3-36   | Table Access Overview                                                 |       |

| Figure 3-37   | AVT Context RAM Addressing Scheme                                     |       |

| Figure 4-1    | Parameters for Connection Setup (bit field width indicated)           |       |

| Figure 4-7    | ABM-3G Application Example: DSLAM                                     |       |

| Figure 4-9    | Example of Threshold Configuration                                    |       |

| Figure 4-10   | AAL5 Extraction: End of packet, Trailer and Status Byte               |       |

| Figure 5-1    | UTOPIA Receive Upstream Master ModeUTOPIA Receive Upstream Slave Mode |       |

| Figure 5-2    | ·                                                                     |       |

| Figure 5-3    | UTOPIA Transmit Downstream Master Mode                                |       |

| Figure 5-4    | UTOPIA Transmit Downstream Slave Mode                                 | . 120 |

| List of Figur | es                                                       | Page |

|---------------|----------------------------------------------------------|------|

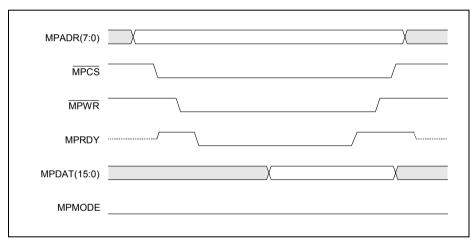

| Figure 5-5    | Intel Style Write Access                                 | 135  |

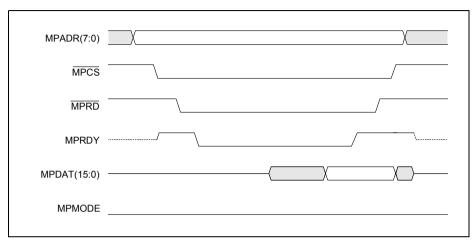

| Figure 5-6    | Intel Style Read Access                                  | 136  |

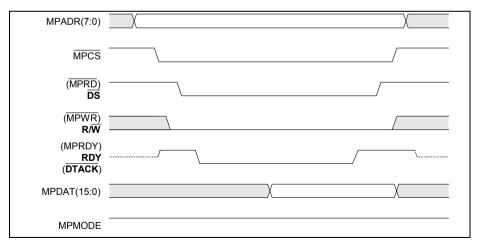

| Figure 5-7    | Motorola Style Write Access                              | 136  |

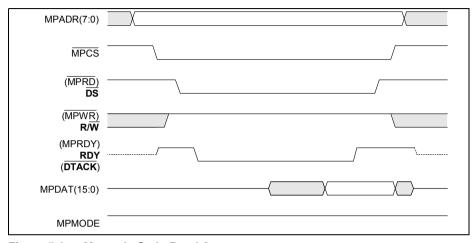

| Figure 5-8    | Motorola Style Read Access                               | 137  |

| Figure 7-1    | Table Access Overview                                    |      |

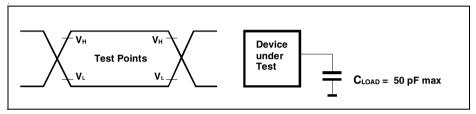

| Figure 8-1    | Input/Output Waveform for AC Measurements                | 339  |

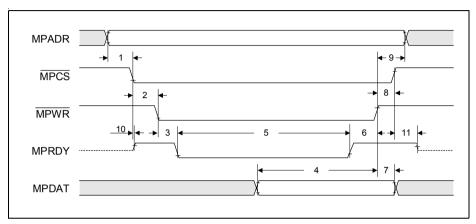

| Figure 8-2    | Microprocessor Interface Write Cycle Timing (Intel)      | 340  |

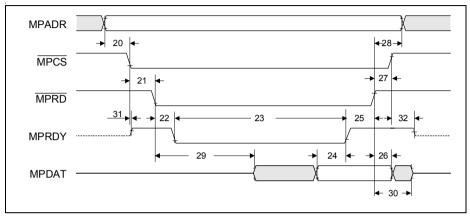

| Figure 8-3    | Microprocessor Interface Read Cycle Timing (Intel)       | 341  |

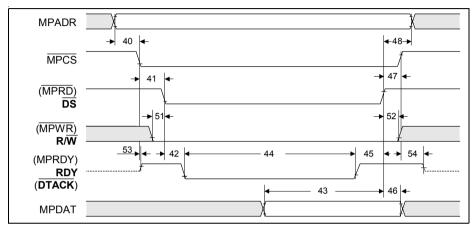

| Figure 8-4    | Microprocessor Interface Write Cycle Timing (Motorola)   | 342  |

| Figure 8-5    | Microprocessor Interface Read Cycle Timing (Motorola)    | 343  |

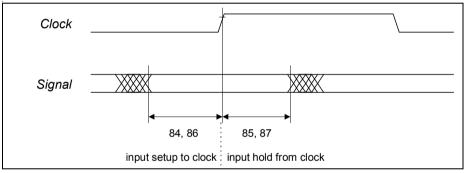

| Figure 8-6    | Setup and Hold Time Definition (Single- and Multi-PHY)   | 345  |

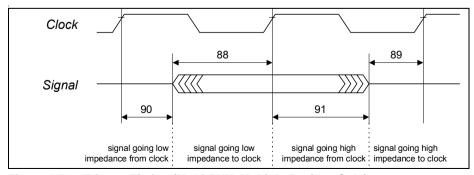

| Figure 8-7    | Tristate Timing (Multi-PHY, Multiple Devices Only)       | 345  |

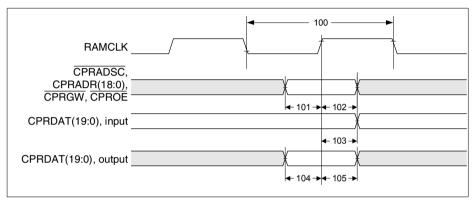

| Figure 8-8    | SSRAM Interface Generic Timing Diagram                   | 350  |

| Figure 8-9    | Generic SDRAM Interface Timing Diagram                   | 351  |

| Figure 8-10   | Reset Timing                                             | 353  |

| Figure 8-11   | Boundary-Scan Test Interface Timing Diagram              |      |

| Figure 9-1    | Block Diagram of Test Access Port and Boundary Scan Unit | 356  |

| List of Table | es                                                          | Page |

|---------------|-------------------------------------------------------------|------|

| Table 2-1     | Ball Definitions and Functions                              | 27   |

| Table 3-4     | Maximum ABM-3G Throughput and Speedup                       |      |

| Table 3-17    | Threshold and Counter Table                                 | 66   |

| Table 3-20    | Statistical Counters                                        |      |

| Table 3-24    | Guaranteed Rates for each ATM Service Category              | 79   |

| Table 3-29    | Summary of VBR Shaping Parameters                           |      |

| Table 3-30    | VBR Conformance Definitions                                 |      |

| Table 3-35    | Timer Values for Clock Generation                           | 91   |

| Table 3-38    | AVT Context Table: VBR Shaping (Table Layout)               | 97   |

| Table 3-39    | AVT Context Table: VBR Shaping Parameter Description        |      |

| Table 3-40    | Config(6:0) Bit Map                                         |      |

| Table 4-2     | Scheduler Block Rate Limits                                 |      |

| Table 4-3     | SB Rate Calculation Examples for SYSCLK = 51.84 MHz         |      |

| Table 4-4     | Minimum Shaper Rates as a Function of TstepC and SYSCLK     | 111  |

| Table 4-5     | Shaper Accuracy as a Function of desired PCR and TstepC     |      |

| Table 4-6     | Maximum BT as a Function of TstepC and SYSCLK               |      |

| Table 4-8     | Number of Possible Connections per PHY                      |      |

| Table 4-11    | AAL5 Status Byte                                            |      |

| Table 5-1     | Port/Address Mapping                                        | 127  |

| Table 5-2     | Port Polling Sequence                                       | 129  |

| Table 5-3     | Standardized UTOPIA Level 2 Cell Format (16-bit)            | 130  |

| Table 5-4     | Standardized UTOPIA Level 2 Cell Format (16-bit): OAM Cells | 130  |

| Table 5-5     | Standardized UTOPIA Level 2 Cell Format (16-bit)            | 131  |

| Table 5-6     | Standardized UTOPIA Level 2 Cell Format (16-bit)            | 131  |

| Table 5-7     | Standardized UTOPIA Level 2 Cell Format (16-bit)            | 132  |

| Table 5-8     | Standardized UTOPIA Level 2 Cell Format (16-bit)            | 132  |

| Table 5-9     | External RAM Sizes                                          | 138  |

| Table 5-10    | SSRAM Configuration Examples                                | 139  |

| Table 5-11    | SDRAM Configuration Examples                                | 140  |

| Table 5-12    | SSRAM and SDRAM Type Examples                               | 141  |

| Table 7-1     | Color Convention for Internal Table Field Illustration      | 145  |

| Table 7-2     | ABM-3G Registers Overview                                   | 145  |

| Table 7-3     | External RAM Sizes                                          |      |

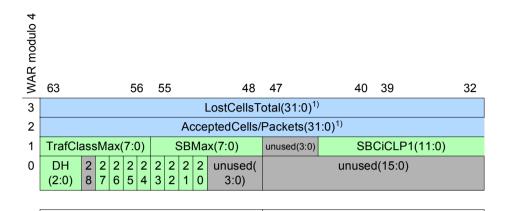

| Table 7-5     | WAR Register Mapping for LCI Table Access                   | 191  |

| Table 7-4     | Registers for LCI Table Access                              | 191  |

| Table 7-6     | Registers for TCT Table Access                              | 195  |

| Table 7-7     | WAR Register Mapping for TCT Table Access                   | 196  |

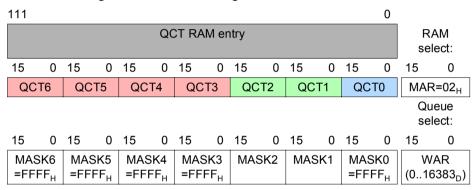

| Table 7-8     | Registers for Queue Configuration Table Access              | 211  |

| Table 7-9     | WAR Register Mapping for LCI Table Access                   |      |

| Table 7-10    | Registers for SBOC Table Access                             | 223  |

| Table 7-11    | WAR Register Mapping for SBOC Table Access                  | 224  |

| Table 7-12    | Registers for MGT Table Access                              | 230  |

| List of Table | es I                                                             | Page |

|---------------|------------------------------------------------------------------|------|

| Table 7-13    | WAR Register Mapping for MGT Table Access                        | 231  |

| Table 7-14    | Registers for QPT1 Upstream Table Access                         |      |

| Table 7-15    | Registers for QPT1 Downstream Table Access                       | 247  |

| Table 7-16    | WAR Register Mapping for QPT Table Access                        | 248  |

| Table 7-17    | Registers for QPT2 Upstream Table Access                         | 251  |

| Table 7-18    | Registers for QPT2 Downstream Table Access                       | 251  |

| Table 7-19    | WAR Register Mapping for QPT Table Access                        | 252  |

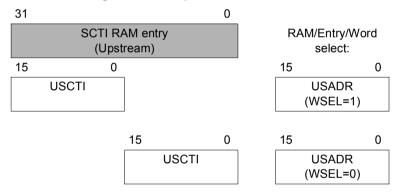

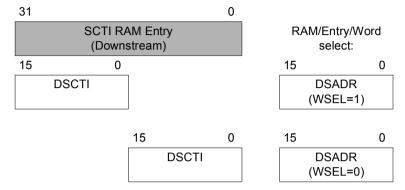

| Table 7-20    | Registers SCTI Upstream Table Access                             | 257  |

| Table 7-21    | Registers SCTI Downstream Table Access                           | 258  |

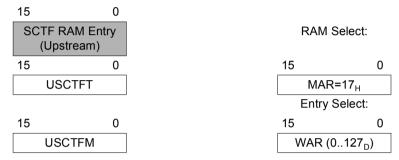

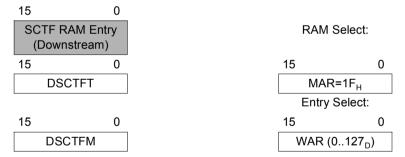

| Table 7-22    | Registers SCTF Upstream Table Access                             | 267  |

| Table 7-23    | Registers SCTF Downstream Table Access                           | 267  |

| Table 7-24    | WAR Register Mapping for SCTFU/SCTFD Table access                | 268  |

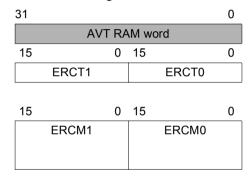

| Table 7-25    | Registers for AVT Table Access                                   | 280  |

| Table 7-26    | WAR Register Mapping for AVT Table Access                        | 281  |

| Table 7-27    | Extended RAM Address Range for Test Access                       | 292  |

| Table 8-1     | Absolute Maximum Ratings                                         | 336  |

| Table 8-2     | Operating Range                                                  | 336  |

| Table 8-3     | DC Characteristics                                               | 337  |

| Table 8-4     | Clock Frequencies                                                |      |

| Table 8-5     | Microprocessor Interface Write Cycle Timing (Intel)              | 340  |

| Table 8-6     | Microprocessor Interface Read Cycle Timing (Intel)               | 341  |

| Table 8-7     | Microprocessor Interface Write Cycle Timing (Motorola)           | 342  |

| Table 8-8     | Microprocessor Interface Read Cycle Timing (Motorola)            |      |

| Table 8-9     | Transmit Timing (16-Bit Data Bus, 50 MHz Cell Mode, Single PHY). |      |

| Table 8-10    | Receive Timing (16-Bit Data Bus, 50 MHz Cell Mode, Single PHY) . | 346  |

| Table 8-11    | Transmit Timing (16-Bit Data Bus, 50 MHz Cell Mode, Multi-PHY)   | 347  |

| Table 8-12    | Receive Timing (16-Bit Data Bus, 50 MHz Cell Mode, Multi-PHY)    | 348  |

| Table 8-13    | SSRAM Interface AC Timing Characteristics                        |      |

| Table 8-14    | SDRAM Interface AC Timing Characteristics                        | 351  |

| Table 8-15    | Reset Timing                                                     |      |

| Table 8-16    | Boundary-Scan Test Interface AC Timing Characteristics           | 354  |

| Table 8-18    | Thermal Package Characteristics                                  | 355  |

| Table 8-17    | Canacitances                                                     | 355  |

| List of Regis              | ters                      | Page |

|----------------------------|---------------------------|------|

| Register 1                 | UCFTST/DCFTST             | 156  |

| Register 2                 | URCFG/DRCFG               |      |

| Register 3                 | UA5TXHD0/DA5TXHD0         |      |

| Register 4                 | UA5TXHD1/DA5TXHD1         |      |

| Register 5                 | UA5TXDAT0/DA5TXDAT0       |      |

| Register 6                 | UA5TXDAT1/DA5TXDAT1       | 163  |

| Register 7                 | UA5TXTR/DA5TXTR           |      |

| Register 8                 | UA5TXCMD/DA5TXCMD         | 165  |

| Register 9                 | UA5RXHD0/DA5RXHD0         |      |

| Register 10                | UA5RXHD1/DA5RXHD1         | 168  |

| Register 11                | UA5RXDAT0/DA5RXDAT0       | 170  |

| Register 12                | UA5RXDAT1/DA5RXDAT1       |      |

| Register 13                | UA5SARS/DA5SARS           |      |

| Register 14                | UBufferOcc/DBufferOcc     | 174  |

| Register 15                | UBufferOccNg/DBufferOccNg | 175  |

| Register 16                | UBufMax/DBufMax           | 176  |

| Register 17                | UMAC/DMAC                 | 178  |

| Register 18                | UMIC/DMIC                 |      |

| Register 19                | CLP1DIS                   |      |

| Register 20                | CONFIG                    |      |

| Register 21                | UUBPTH0                   |      |

| Register 22                | UUBPTH1                   | 183  |

| Register 23                | UUBPTH2                   | 19/  |

| Register 24                | UUBPTH3                   |      |

| Register 25                | UBPEL                     |      |

| Register 26                | DUBPTH0                   |      |

| Register 27                | DUBPTH1                   |      |

| Register 28                | DUBPTH2                   |      |

| Register 29                | DUBPTH3                   |      |

| Register 30                | LCI0                      |      |

| Register 31                | LCI1                      |      |

| Register 32                | LCI2                      | 10/  |

| Register 33                | TCT0                      |      |

| Register 34                | TCT1                      |      |

| Register 35                | TCT2                      |      |

| Register 36                | TCT3                      |      |

| Register 37                | QCT0                      |      |

| Register 38                | QCT1                      | 21/  |

| Register 39                | QCT2                      |      |

| Register 40                | QCT3                      |      |

| Register 41                | QCT4                      | 220  |

| Register 42                | QCT5                      |      |

| Register 43                | QCT6                      |      |

| Register 44                | SBOC0                     |      |

| Register 45                | SBOC1                     | 226  |

| Register 45                | SBOC2                     | ZZC  |

| Register 46<br>Register 47 | SBOC3                     |      |

|                            | SBOC4                     |      |

| Register 48                | MGT0                      |      |

| Register 49<br>Register 50 | MGT1                      |      |

| Degister 50                | MGT2                      |      |

| List of Regis | ters            | Page  |

|---------------|-----------------|-------|

| Register 52   | MASK0/MASK1     | 235   |

| Register 53   | MASK2/MASK3     |       |

| Register 54   | MASK4/MASK5     | 237   |

| Register 55   | MASK6           |       |

| Register 56   | UCDV/DCDV       | 239   |

| Register 57   | UQPTM0/DQPTM0   | . 240 |

| Register 58   | UQPTM1/DQPTM1   |       |

| Register 59   | UQPTM2/DQPTM2   | . 242 |

| Register 60   | UQPTM3/DQPTM3   | . 243 |

| Register 61   | UQPTM4/DQPTM4   |       |

| Register 62   | UQPTM5/DQPTM5   |       |

| Register 63   | USCONF/DSCONF   |       |

| Register 64   | UQPT1T0/DQPT1T0 |       |

| Register 65   | UQPT1T1/DQPT1T1 |       |

| Register 66   | UQPT2T0/DQPT2T0 |       |

| Register 67   | UQPT2T1/DQPT2T1 |       |

| Register 68   | UQPT2T2/DQPT2T2 |       |

| Register 69   | UQPT2T3/DQPT2T3 | . 256 |

| Register 70   | USADR/DSADR     |       |

| Register 71   | USCTI/DSCTI     |       |

| Register 72   | UECRI/DECRI     |       |

| Register 73   | UECRF/DECRF     |       |

| Register 74   | UCRTQ/DCRTQ     |       |

| Register 75   | USCTFM/DSCTFM   |       |

| Register 76   | USCTFT/DSCTFT   |       |

| Register 77   | USCENO/DSCENO   |       |

| Register 78   | USCEN1/DSCEN1   |       |

| Register 79   | USCEN2/DSCEN2   |       |

| Register 80   | USCEN3/DSCEN3   |       |

| Register 81   | USCEN4/DSCEN4   |       |

| Register 82   | USCEN5/DSCEN5   |       |

| Register 83   | USCEN6/DSCEN6   |       |

| Register 84   | USCEN7/DSCEN7   |       |

| Register 85   | UCRTRI/DCRTRI   | . 278 |

| Register 86   | UCRTRF/DCRTRF   | 279   |

| Register 87   | ERCT0           |       |

| Register 88   | ERCT1           | _     |

| Register 89   | ERCM0           |       |

| Register 90   | ERCM1           |       |

| Register 91   | ERCCONF0        |       |

| Register 92   | PLL1CONF        |       |

| Register 93   | PLLTST          |       |

| Register 94   | EXTRAMD0        |       |

| Register 95   | EXTRAMD1        |       |

| Register 96   | EXTRAMA0        |       |

| Register 97   | EXTRAMA1        |       |

| Register 98   | EXTRAMC         |       |

| Register 99   | VERL            | _     |

| Register 100  | VERH            |       |

| Register 101  | ISRU            |       |

|               | ICDU            |       |

| List of Regis | ters P   | age |

|---------------|----------|-----|

| Register 103  | ISRC     | 303 |

| Register 104  | IMRU     | 304 |

|               | IMRD     |     |

| Register 106  | IMRC     | 306 |

|               | MAR      |     |

|               | WAR      |     |

| Register 109  | USTATUS  | 311 |

|               | MODE1    |     |

| Register 111  | MODE2    | 315 |

| Register 112  | UTRXCFG  | 317 |

|               | UUTRXP0  |     |

|               | UUTRXP1  |     |

|               | UUTRXP2  |     |

|               | DUTRXP0  |     |

| Register 117  | DUTRXP1  | 323 |

| Register 118  | DUTRXP2  | 324 |

|               | UUTTXCFG |     |

| Register 120  | DUTTXCFG | 327 |

| Register 121  | UUTTXP0  | 329 |

|               | UUTTXP1  |     |

|               | UUTTXP2  |     |

| Register 124  | DUTTXP0  | 332 |

|               | DUTTXP1  |     |

|               | DUTTXP2  |     |

| Register 127  | TEST     | 335 |

|               |          |     |

#### **Preface**

The purpose of this Data Sheet is to provide comprehensive information about the ABM-3G device regarding system-level integration, hardware/board design, and software driver aspects.

#### Organization of this Document

This Data Sheet is divided into 13 chapters and two appendices. It is organized as follows:

#### · Chapter 1, Overview

Gives a general description of the product and its family, lists the key features, and presents some typical applications.

#### · Chapter 2, Pin Descriptions

Lists pin locations with associated signals, categorizes signals according to function, and describes the signals.

#### Chapter 3, Functional Description

Gives descriptions of major functional blocks, configuration tables, and global device functions.

#### • Chapter 4, Operational Description

Describes basic initialization and operation procedures.

#### Chapter 5, Interface Description

Gives a functional description of all interfaces.

#### Chapter 6, Memory Structure

#### Chapter 7, Register Description

Lists all registers and tables with functional description.

#### Chapter 8, Electrical Characteristics

Provides detailed information about electrical characteristics and interface timings.

- · Chapter 9, Test Mode

- Chapter 10, Package Outlines

- Chapter 11, Glossary

#### **Related Documentation**

- ITU-T Recommendation I.371, Traffic Control and Congestion Control in B-ISDN, 2nd Release, March 1996.

- [2] ATMF, Traffic Management Specification 4.1, March 1999.

- [3] ATMF, UTOPIA Level 1 Specification Version 2.01, March 1994.

- [4] ATMF, UTOPIA Level 2 Specification Version 1, June 1995.

#### **Your Comments**

We welcome your comments on this document. We are continuously trying improving our documentation. Please send your remarks and suggestions by e-mail to

sc.docu\_comments@infineon.com

Please provide in the subject of your e-mail:

device name (ABM-3G), device part number (PXF 4333), device version (Version 1.1), and in the body of your e-mail:

document type (Data Sheet), issue date (2001-12-17) and document revision number (DS 1).

#### 1 Overview

The ABM-3G PXF 4333 Version 1.1 is Infineon's new generation ATM Buffer Manager device. It addresses the performance needs of new multi-service platforms with combined ATM cell and packet-handling applications. The ABM-3G manages ATM traffic flowing through multi-service platforms in which voice, video, and data traffic converge. The optimizes the interworking of ATM and higher-layer traffic-management and flow-control schemes. Optional "leaky bucket" shaping per queue provides full VBR support. The ABM-3G is useful in applications where extensive ATM traffic management capabilities are required. This includes either distributed or centralized system architectures that cover enterprise and Central Office switches, DSLAMs, and ATM line cards for routers and switches.

# ATM Buffer Manager ABM-3G

ABM-3G PXF 4333 V1.1

#### 1.1 Features

- ATM Traffic Management processing support up to STM-4/OC-12 equivalent bandwidth

- Throughput at UTOPIA Interface up to 687 Mbit/s transmit, 795 Mbit/s receive

- Speed-up factor relative to STM-4/OC12: 1.32

- Uni-directional mode with combined resources of both directions (optional)

- 256K cells buffer per direction (configurable in guaranteed and shared buffer)

- Up to 16384 connections arbitrarily assignable to queues for sharing connections and saving resources

- Up to 8192 queues per direction, individually assignable to schedulers and to traffic classes

- Up to 128 Scheduler Blocks (SB) per direction with programmable service rates, individually assignable to UTOPIA ports

- The ABM-3G is cascadable to provide up to 512 schedulers, 32K queues, and 1M cell memories per direction

- Up to 16 traffic classes with individually-selectable thresholds for highest service differentiation

- Up to 48 ports per UTOPIA Interface

- Standards-compliant support for the following ATM Forum service categories: CBR, rt-VBR, nrt-VBR, GFR, UBR, UBR+

- Generic PHB (Per Hop Behavior) characteristics are configurable (PHB traffic class is not standardized)

- · Configurable cell-address translation modes

### 1.1.1 Queueing Functions

Per-VC queueing for up to 8192 connections per direction for optimal connection isolation

| Туре                 | Package |

|----------------------|---------|

| ABM-3G PXF 4333 V1.1 | BGA-456 |

# ABM-3G PXF 4333 V1.1

Overview

- Optional queue sharing

- · Guaranteed per-queue minimum buffer reservation

- Cell acceptance based on programmable threshold sets with hysteresis evaluation

- Threshold sets for individual queues, traffic classes, schedulers, and global buffer for optimized buffer sharing

- Per VC Packet Discard, including Early Packet Discard (EPD) & Partial Packet Discard (PPD) thresholds for Guaranteed Frame Rate (GFR) support

- · Cell Loss Priority (CLP) aware selective discard thresholds

- · UTOPIA input port backpressure thresholds without head-of-line-blocking

#### 1.1.2 Scheduling Functions

- Multistage scheduling units with

- Work conservative Weighted Round Robin (WRR) scheduling stage for 128

Scheduler Blocks

- Each Scheduler Block comprising of

- a Weighted Fair Queueing (WFQ) scheduler with 16320 programmable weight factors for each queue, providing rate guarantees and fairness in bandwidth allocation

- a high priority Round Robin (RR) scheduler for real-time traffic

- a low priority RR scheduler for best effort traffic

- Additional common real-time bypass queue for each direction, for cascading multiple ABM-3Gs

- Selectable Peak Cell Rate (PCR) shaping for each queue with minimum 2.62 Kbps and maximum 343 Mbit/s at 52 MHz clock (65472 programmable rates)

- Selectable Variable Bit Rate (VBR.1.2.3) leaky bucket shaping for up to 2046 queues

- VC merge function for up to 128 merge groups (arbitrary queues per merge group) for Multi Protocol Label Switching (MPLS) applications

- · SB scheduler overbooking possibility

#### 1.1.3 Interfaces

- Two external SDRAM Interfaces for cell storage, one for upstream and one for downstream direction (up to 256 K cell buffer per direction)

- · One common cell pointer SSRAM Interface

- Multiport UTOPIA Level 2 Interface in up- and downstream direction conforming to the specifications of the ATM Forum [4]

- 4-cell FIFO buffer at UTOPIA receive interfaces for clock synchronization (head-of-line blocking-free)

- 64-cell buffer logical queueing for up to 48 PHYs at UTOPIA transmit interfaces (head-of-line blocking-free)

- 16-bit Microprocessor Interface, configurable as Intel or Motorola type (with AAL5 packet insertion/extraction support)

- · Queue Congestion Indication Interface

- · JTAG Boundary Scan Interface

# 1.1.4 Supervision Functions

- · Internal pointer supervision

- Cell-header protection function

## 1.1.5 Technology

- Supply voltages 1.8 V (core) and 3.3 V (I/Os)

- Ball Grid Array BGA-456 package (Plastic BGA (35 mm)<sup>2</sup>)

- Temperature range -40°C to 85°C

- Power dissipation 2.0 W (typical)

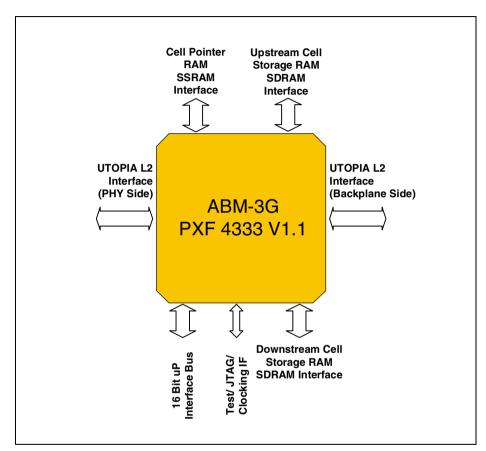

# 1.2 Logic Symbol

Figure 1-1 Logic Symbol

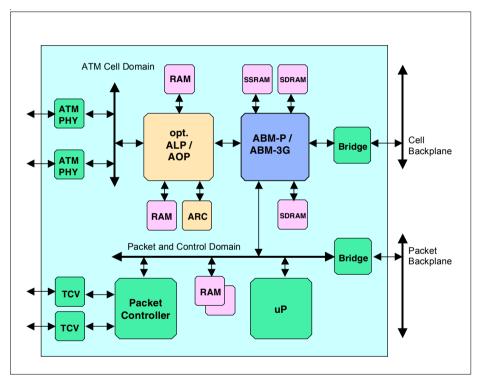

# 1.3 Typical Applications

The ABM-3G device is designed for traffic management on line cards and trunk cards such as are used in:

- ATM Switches

- DSLAMs, DLCs

- · Multi-Service Access Switches

- 3G Wireless Infrastructure

Figure 1-2 General System Integration

# 2 Pin Descriptions

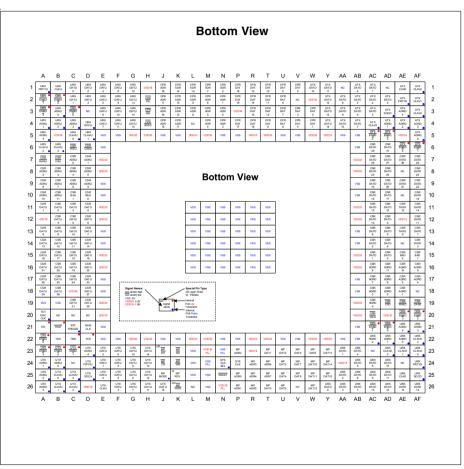

## 2.1 Pin Diagram

Figure 2-1 Pin Configuration (Bottom View)

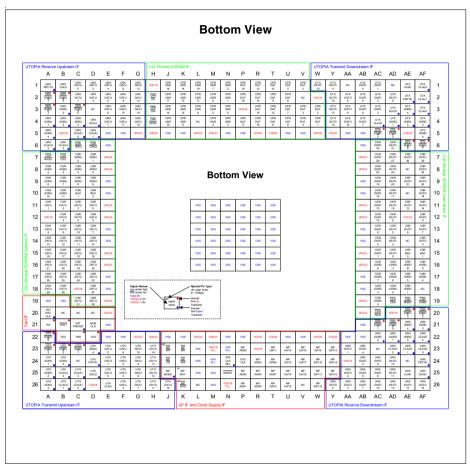

#### 2.2 Pin Diagram with Functional Groupings

Figure 2-2 Pin Configuration (Bottom View)

#### 2.3 Pin Definitions and Functions

Table 2-1 lists and explains all pins/balls organized into functional groups. Table 2-1 uses the following naming conventions:

Ball No. Ball Number with respect to package outline (see Figure 2-1)

Symbol Signal Name Type Type of pin/ball:

Input pin

Input pin (Internal Pull-Down Transistor)  $I_{PD}$ **I**PU

Input pin (Internal Pull-Up Transistor)

0 Output pin (Push/Pull) O (oD) Output pin (Open Drain)

O (tri) Output pin (TriState)

**Function** Functional pin/ball description

Note: The ABM-3G signal pins are not 5 V I/O tolerant. For further details refer to "DC Characteristics" on Page 337.

Table 2-1 **Ball Definitions and Functions**

| Ball | Symbol | Туре | Function |

|------|--------|------|----------|

| No.  |        |      |          |

#### 2.3.1 Common System Clock Supply (3 pins)

| P24 | SYSCLK    | I               | System Clock This clock signal feeds DPLL1 and DPLL2 and the internal ABM-3G Core Clock, depending on signal SYSCLKSEL.                       |

|-----|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| N24 | SYSCLKSEL | I <sub>PD</sub> | Internal ABM-3G Core Clock Source Select: 'H': Internal Core Clock is supplied by signal SYSCLK 'L': Internal Core Clock is supplied by DPLL1 |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No. | Symbol | Туре | Function                                              |

|-------------|--------|------|-------------------------------------------------------|

| D21         | RAMCLK | 0    | Reference clock for external RAM (CSRU, CSRD and CPR) |

# 2.3.2 UTOPIA Receive Interface Upstream (Master/Slave) (32 pins)

| G4,<br>G3,<br>G2,<br>G1,<br>F4,<br>F3,<br>F2,<br>F1,<br>E4,<br>E3,<br>E2,<br>E1,<br>D2,<br>D1,<br>C2,<br>C1 | 15,<br>14,<br>13,<br>12,<br>11,<br>10,<br>9,<br>8,<br>7,<br>6,<br>5,<br>4,<br>3,<br>2,<br>1,<br>0 | URXDATU(15:0) |                   | UTOPIA Receive Data Bus Upstream (from PHY)                                 |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------------------------------------------------------------------|

| A1                                                                                                          | URXF                                                                                              | PRTYU         | I <sub>PD</sub>   | UTOPIA Receive Odd Parity of URXDATU(15:0) (PHY side)                       |

| A5,<br>C4,<br>B4,<br>A4,<br>B3                                                                              | 4,<br>3,<br>2,<br>1,                                                                              | URXADRU(4:0)  | I/O <sub>PD</sub> | UTOPIA Receive Address Bus (PHY side) Master Mode: output Slave Mode: input |

| A3,<br>B2,<br>A2,<br>C3                                                                                     | 3,<br>2,<br>1,<br>0                                                                               | URXENBU(3:0)  | I/O <sup>PU</sup> | UTOPIA Receive Enable Bus (PHY side) Master Mode: output Slave Mode: input  |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No.             | Symb                | ool           | Туре              | Function                                                                 |

|-------------------------|---------------------|---------------|-------------------|--------------------------------------------------------------------------|

| B6,<br>A6,<br>D5,<br>C5 | 3,<br>2,<br>1,<br>0 | URXCLAVU(3:0) | I/O <sub>PD</sub> | UTOPIA Receive CLAV Bus (PHY side) Master Mode: input Slave Mode: output |

| D4                      | URXSOCU             |               | I <sub>PD</sub>   | UTOPIA Receive Start of Cell signal (PHY side)                           |

| B1                      | URXCLKU             |               | I                 | UTOPIA Receive Clock signal (PHY side)                                   |

# 2.3.3 UTOPIA Transmit Interface Downstream (Master/Slave) (32 pins)

| W1,<br>Y4,<br>Y3,<br>Y2,<br>Y1,<br>AA4,<br>AA3,<br>AA2,<br>AB4,<br>AB3,<br>AB2,<br>AB1,<br>AC3,<br>AC2,<br>AC1,<br>AD2 | 15,<br>14,<br>13,<br>12,<br>11,<br>10,<br>9,<br>8,<br>7,<br>6,<br>5,<br>4,<br>3,<br>2,<br>1,<br>0 | UTXDATD(15:0) | 0               | UTOPIA Transmit Data Bus Downstream (to PHY)           |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------|-----------------|--------------------------------------------------------|

| AE2                                                                                                                    | UTXP                                                                                              | PRTYD         | O <sub>PD</sub> | UTOPIA Transmit Odd Parity of UTXDATD(15:0) (PHY side) |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No.                         | Symb                      | ool           | Туре              | Function                                                                          |

|-------------------------------------|---------------------------|---------------|-------------------|-----------------------------------------------------------------------------------|

| AE3,<br>AF4,<br>AE4,<br>AD4,<br>AF5 | 4,<br>3,<br>2,<br>1,<br>0 | UTXADRD(4:0)  | I/O <sub>PD</sub> | UTOPIA Transmit Address Bus (PHY side) Master Mode: output Slave Mode: input      |

| AD5,<br>AC5,<br>AF6,<br>AE6         | 3,<br>2,<br>1,<br>0       | UTXENBD(3:0)  | I/O <sup>PU</sup> | UTOPIA Transmit Enable Bus (PHY side)<br>Master Mode: output<br>Slave Mode: input |

| AC4,<br>AF1,<br>AF2,<br>AF3         | 3,<br>2,<br>1,<br>0       | UTXCLAVD(3:0) | I/O <sub>PD</sub> | UTOPIA Transmit CLAV Bus (PHY side) Master Mode: input Slave Mode: output         |

| AD3                                 | UTXSOCD                   |               | O <sub>PD</sub>   | UTOPIA Transmit Start of Cell signal (PHY side)                                   |

| AE1                                 | UTXCLKD                   |               | I                 | UTOPIA Transmit Clock signal (PHY side)                                           |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball | Symbol | Туре | Function |

|------|--------|------|----------|

| No.  |        |      |          |

# 2.3.4 UTOPIA Receive Interface Downstream (Master/Slave) (32 pins)

|       |      | ,             |                   |                                                             |

|-------|------|---------------|-------------------|-------------------------------------------------------------|

| AD24, | 15,  |               | I                 | UTOPIA Receive Data Bus Downstream                          |

| AF26, | 14,  |               |                   | (from Backplane)                                            |

| AE26, | 13,  |               |                   |                                                             |

| AD26, | 12,  |               |                   |                                                             |

| AD25, | 11,  | _             |                   |                                                             |

| AC26, | 10,  | (0:           |                   |                                                             |

| AC25, | 9,   | 15            |                   |                                                             |

| AC24, | 8,   | <u>P</u>      |                   |                                                             |

| AB26, | 7,   | A             |                   |                                                             |

| AB25, | 6,   | JRXDATD(15:0) |                   |                                                             |

| AB24, | 5,   | <u>"</u>      |                   |                                                             |

| AB23, | 4,   |               |                   |                                                             |

| AA26, | 3,   |               |                   |                                                             |

| AA25, | 2,   |               |                   |                                                             |

| AA23, | 1,   |               |                   |                                                             |

| Y26   | 0    |               |                   |                                                             |

| AF24  | URXF | PRTYD         | I <sub>PD</sub>   | UTOPIA Receive Odd Parity of URXDATD(15:0) (Backplane side) |

| AE21, | 4,   | 6             | I/O <sub>PD</sub> | UTOPIA Receive Address Bus (Backplane side)                 |

| AF21, | 3,   | URXADRD(4:0)  | ''                | Master Mode: output                                         |

| AC22, | 2,   | R 2           |                   | Slave Mode: input                                           |

| AD22, | 1,   | Q .           |                   | ·                                                           |

| AE22  | 0    | 📡             |                   |                                                             |

|       |      | <u>"</u>      |                   |                                                             |

| AE20, | 3,   | <u>(</u> 0    | I/O <sup>PU</sup> | UTOPIA Receive Enable Bus (Backplane side)                  |

| AF20, | 2,   | (33)          |                   | Master Mode: output                                         |

| AC21, | 1,   | BD            |                   | Slave Mode: input                                           |

| AD21  | 0    |               |                   |                                                             |

|       |      | URXENBD(3:0)  |                   |                                                             |

|       |      |               |                   |                                                             |

|       |      |               |                   |                                                             |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No.                     | Symb                | ol            | Туре              | Function                                                                       |

|---------------------------------|---------------------|---------------|-------------------|--------------------------------------------------------------------------------|

| AF22,<br>AD23,<br>AE23,<br>AF23 | 3,<br>2,<br>1,<br>0 | URXCLAVD(3:0) | I/O <sub>PD</sub> | UTOPIA Receive CLAV Bus (Backplane side) Master Mode: input Slave Mode: output |

| AF25                            | URXSOCD             |               | I <sub>PD</sub>   | UTOPIA Receive Start of Cell signal (Backplane side)                           |

| AE25                            | URXCLKD             |               | I                 | UTOPIA Receive Clock signal (Backplane side)                                   |

# 2.3.5 UTOPIA Transmit Interface Upstream (Master/Slave) (32 pins)

| J26,<br>H23,<br>H24,<br>H25,<br>H26,<br>G23,<br>G24,<br>G25,<br>G26,<br>F23,<br>F24,<br>F25,<br>F26,<br>E23,<br>E24, | 15,<br>14,<br>13,<br>12,<br>11,<br>10,<br>9,<br>8,<br>7,<br>6,<br>5,<br>4,<br>3,<br>2, | UTXDATU(15:0) | O               | UTOPIA Transmit Data Bus Upstream (to Backplane)             |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------|-----------------|--------------------------------------------------------------|

| E24,<br>E25                                                                                                          | 1,<br>0                                                                                |               |                 |                                                              |

| D24                                                                                                                  | UTXPRTYU                                                                               |               | O <sub>PD</sub> | UTOPIA Transmit Odd Parity of UTXDATU(15:0) (Backplane side) |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No.                         |                           |               | Туре              | Function                                                                                 |

|-------------------------------------|---------------------------|---------------|-------------------|------------------------------------------------------------------------------------------|

| D23,<br>A26,<br>A25,<br>A24,<br>B24 | 4,<br>3,<br>2,<br>1,<br>0 | UTXADRU(4:0)  | I/O <sub>PD</sub> | UTOPIA Transmit Address Bus (Backplane side)<br>Master Mode: output<br>Slave Mode: input |

| A23,<br>B23,<br>C23,<br>A22         | 3,<br>2,<br>1,<br>0       | UTXENBU(3:0)  | I/O <sup>PU</sup> | UTOPIA Transmit Enable Bus (Backplane side)<br>Master Mode: output<br>Slave Mode: input  |

| C25,<br>C26,<br>B26,<br>B25         | 3,<br>2,<br>1,<br>0       | UTXCLAVU(3:0) | I/O <sub>PD</sub> | UTOPIA Transmit CLAV Bus (Backplane side) Master Mode: input Slave Mode: output          |

| D25                                 | UTXSOCU                   |               | O <sub>PD</sub>   | UTOPIA Transmit Start of Cell signal (Backplane side)                                    |

| E26                                 | UTXCLKU                   |               | I                 | UTOPIA Transmit Clock signal (Backplane side)                                            |

# 2.3.6 Microprocessor Interface (32 pins)

| N25 | RESET | I | ABM-3G Reset |

|-----|-------|---|--------------|

|     |       |   |              |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No.                                                                                                          | Symb                                                                                              | ol          | Туре   | Function                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Y25,<br>Y24,<br>Y23,<br>W26,<br>W25,<br>W24,<br>W23,<br>V25,<br>V24,<br>V23,<br>U26,<br>U25,<br>U24,<br>U23,<br>T23, | 15,<br>14,<br>13,<br>12,<br>11,<br>10,<br>9,<br>8,<br>7,<br>6,<br>5,<br>4,<br>3,<br>2,<br>1,<br>0 | MPDAT(15:0) | I/O    | Microprocessor Data Bus                                                                                                                        |

| T25,<br>T24,<br>R26,<br>R25,<br>R24,<br>P23,<br>P26,<br>P25                                                          | 7,<br>6,<br>5,<br>4,<br>3,<br>2,<br>1,                                                            | MPADR(7:0)  | I      | Microprocessor Address Bus                                                                                                                     |

| K24                                                                                                                  | MPWR                                                                                              |             | I      | WR when MPMOD=0 (Intel Mode) R/W when MPMOD=1 (Motorola Mode).                                                                                 |

| K23                                                                                                                  | MPRD                                                                                              |             | I      | RD when MPMOD=0 (Intel Mode) DS when MPMOD=1 (Motorola Mode).                                                                                  |

| J24                                                                                                                  | MPCS                                                                                              |             | I      | Chip Select from Microprocessor.                                                                                                               |

| J23                                                                                                                  | MPINT                                                                                             |             | O(oD)  | Interrupt Request to Microprocessor.  Open drain, needs external pull-up resistor. Interrupt pins of several devices can be wired-or together. |

| K25                                                                                                                  | MPRDY                                                                                             |             | O(tri) | Ready Output to Microprocessor for read and write accesses.                                                                                    |

Table 2-1 Ball Definitions and Functions (cont'd)

| Ball<br>No. | Symbol | Туре            | Function                                                                    |

|-------------|--------|-----------------|-----------------------------------------------------------------------------|

| J25         | MPMODE | I <sub>PD</sub> | Intel/Motorola select: 'L' Intel type processor 'H' Motorola type processor |

# 2.3.7 Cell Storage RAM Upstream (50 pins)

|      | •   | otorug        | • • | potroum (or pino)                     |

|------|-----|---------------|-----|---------------------------------------|

| C19, | 31, |               | I/O | Data Bus to Cell Storage RAM Upstream |

| D19, | 30, |               |     |                                       |

| A18, | 29, |               |     |                                       |

| B18, | 28, |               |     |                                       |

| D18, | 27, |               |     |                                       |

| A17, | 26, |               |     |                                       |

| B17, | 25, |               |     |                                       |

| C17, | 24, |               |     |                                       |

| D17, | 23, |               |     |                                       |

| D16, | 22, |               |     |                                       |

| A16, | 21, |               |     |                                       |

| B16, | 20, |               |     |                                       |

| C16, | 19, |               |     |                                       |

| A15, | 18, | CSRDATU(31:0) |     |                                       |

| B15, | 17, | (3            |     |                                       |

| D15, | 16, | 2             |     |                                       |

| C15, | 15, | ≦             |     |                                       |

| D14, | 14, | E.            |     |                                       |

| A14, | 13, | ပိ            |     |                                       |

| B14, | 12, |               |     |                                       |

| C14, | 11, |               |     |                                       |

| C13, | 10, |               |     |                                       |

| B13, | 9,  |               |     |                                       |

| A13, | 8,  |               |     |                                       |