GaAs MMIC CGY 353

Data Sheet

3-stage power amplifier for 3.5 GHz applications

- Linear Output power 31.0 dBm

- Gain of 21.0 dB typ.

- Operating voltage 7.0 V typ.

- Unconditionally stable

| Туре    | Marking | Ordering Code<br>(taped) | Package |

|---------|---------|--------------------------|---------|

| CGY 353 | CGY 353 | Q62702-G82               | MW-16   |

### **Maximum Ratings**

| Parameter                                                                                                     | Symbol        | Value              | Unit |

|---------------------------------------------------------------------------------------------------------------|---------------|--------------------|------|

| Positive supply voltage                                                                                       | $V_{D}$       | 8.0                | V    |

| Supply current                                                                                                | $I_{D}$       | 2.0                | А    |

| Maximum input power                                                                                           | $P_{IN\_max}$ | 17.0               | dBm  |

| Channel temperature                                                                                           | $T_{Ch}$      | 150                | °C   |

| Storage temperature                                                                                           | $T_{ m stg}$  | - 55 + <b>1</b> 50 | °C   |

| Total power dissipation ( $T_{\rm S} \le 81~{}^{\circ}{\rm C}$ ) $T_{\rm S}$ : Temperature at soldering point | $P_{tot}$     | 7.0                | W    |

| Pulse peak power dissipation duty cycle 30%, $t_{ON} = 0.5 \text{ ms}$                                        | $P_{Pulse}$   | 11.0               | W    |

#### **Thermal Resistance**

| Parameter               | Symbol      | Value  | Unit |

|-------------------------|-------------|--------|------|

| Channel-soldering point | $R_{thChS}$ | t.b.d. | K/W  |

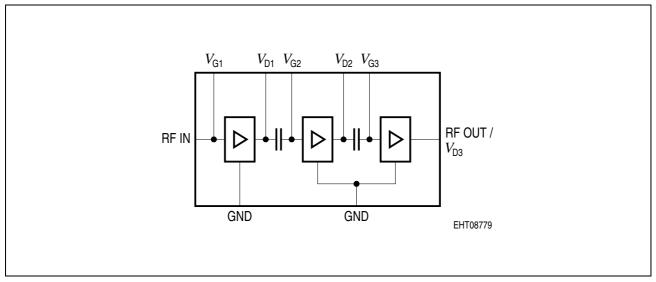

Figure 1 Functional Block Diagram

# **Pin Configuration**

| Pin No. | Name                 | Configuration                               | Bias Voltage               |  |

|---------|----------------------|---------------------------------------------|----------------------------|--|

| 1       | RF IN                | RF input <sup>1)</sup>                      | _                          |  |

| 2       | GND                  | GND                                         | 0 V                        |  |

| 3       | GND                  | GND                                         | 0 V                        |  |

| 4       | GND                  | GND                                         | 0 V                        |  |

| 5       | GND                  | GND                                         | 0 V                        |  |

| 6       | GND                  | GND                                         | 0 V                        |  |

| 7       | $V_{D1}$             | 1 <sup>st</sup> RF Amp Drain Bias           | pos. voltage <sup>2)</sup> |  |

| 8       | $V_{G2}$             | 2 <sup>nd</sup> RF Amp Gate Bias            | neg. voltage <sup>3)</sup> |  |

| 9       | $V_{G1}$             | 1 <sup>st</sup> RF Amp Gate Bias            | neg. voltage <sup>3)</sup> |  |

| 10      | GND                  | GND                                         | 0 V                        |  |

| 11      | GND                  | GND                                         | 0 V                        |  |

| 12      | RF OUT/ $V_{\rm D3}$ | RF output/3 <sup>rd</sup> RF Amp Drain Bias | pos. voltage <sup>2)</sup> |  |

| 13      | RF OUT/ $V_{\rm D3}$ | RF output/3 <sup>rd</sup> RF Amp Drain Bias | pos. voltage <sup>2)</sup> |  |

| 14      | RF OUT/ $V_{\rm D3}$ | RF output/3 <sup>rd</sup> RF Amp Drain Bias | pos. voltage <sup>2)</sup> |  |

| 15      | $V_{G3}$             | 3 <sup>rd</sup> RF Amp Gate Bias            | neg. voltage <sup>3)</sup> |  |

### Pin Configuration (cont'd)

| Pin No.                   | Name     | Configuration                     | Bias Voltage               |

|---------------------------|----------|-----------------------------------|----------------------------|

| 16                        | $V_{D2}$ | 2 <sup>nd</sup> RF Amp Drain Bias | pos. voltage <sup>2)</sup> |

| MW-16<br>Heatsink<br>Slug | GND      | OWP Ground                        | 0 V                        |

The gate voltage of the 1<sup>st</sup> RF Amp is not blocked internally (see also **Figure 1**). Therefore  $V_{\rm G1}$  must be blocked externally at RF IN.

The positive DC voltages of  $V_{\rm D1}$ ,  $V_{\rm D2}$  and  $V_{\rm D3}$  are typically equal. The voltage range is typically between + 5.0 V and + 7.0 V.

The negative DC voltages of  $V_{\rm G1}$ ,  $V_{\rm G2}$  and  $V_{\rm G3}$  are typically equal. The voltage range depends on the wanted drain current. A gate voltage of – 2.1 V will set  $I_{\rm D}$  typically to 1.2 A at  $V_{\rm D}$  = 7.0 V. In that case  $I_{\rm D1}$  will have about 70 mA,  $I_{\rm D2}$  about 270 mA and  $I_{\rm D3}$  about 900 mA.

#### **Electrical Characteristics**

Conditions:  $V_{\rm D}$  = 7.0 V,  $T_{\rm A}$  = 25 °C, f = 3425 - 3450 MHz,  $Z_{\rm S}$  =  $Z_{\rm L}$  = 50  $\Omega$ , pulsed operation mode, duty cycle = 30%, unless otherwise specified.

| Parameters                           | Symbol      | L    | Limit Values |      |     | Test                     |

|--------------------------------------|-------------|------|--------------|------|-----|--------------------------|

|                                      |             | min. | typ.         | max. |     | Conditions               |

| Supply current                       | $I_{DD}$    | _    | 1.2          | _    | Α   | _                        |

| Power down current                   | $I_{Pdown}$ | _    | 10           | _    | mA  | _                        |

| Supply current neg. voltage          | $I_{G}$     | _    | 1            | _    | mA  | -                        |

| Gain at nominal linear output power  | G           | _    | 21           | _    | dB  | -                        |

| Linear Output Power                  | $P_{OUT}$   | _    | 31           | _    | dBm | $P_{\rm IN}$ = 12 dBm    |

| Saturation Output<br>Power           | $P_{SAT}$   | _    | 33           | _    | dBm | $P_{IN}$ = 14 dBm        |

| Overall Power added Efficiency       | PAE         | _    | 15           | _    | %   | $P_{\rm IN}$ = 10 dBm    |

| Adjacent channel power <sup>1)</sup> | ACP         | _    | _            | - 30 | dBc | ± 156 kHz beside carrier |

| Input return loss <sup>2)</sup>      | S11         | 10   | _            | _    | dB  | $P_{\rm IN}$ = 10 dBm    |

| Output return loss                   | S22         | 8    | _            | _    | dB  | $P_{\rm IN}$ = 10 dBm    |

| Noise Figure                         | NF          | _    | 5            |      | dB  | _                        |

Modulation:  $\pi/4$  DQPSK with an alpha = 0.4 root raised cosine filtered Symbol rate: 256 ksymbols/s.

Duty cycle: 30%, 3 bursts per 5 ms frame with a minimum interval of 1 ms between bursts.

The modulation signal has a peak to mean envelope ratio of 3.1 dB.

Transmission burst: Each burst has a 500 s nominal duration with 20 dB of raised cosine shaping of 8 s duration at the beginning and the end of the burst. A maximum of three bursts occur in each 5 ms period, but consecutive bursts are separated by a minimum interval of 1 ms.

<sup>&</sup>lt;sup>2)</sup> Values of S11 and S22 with match as realized on application board.

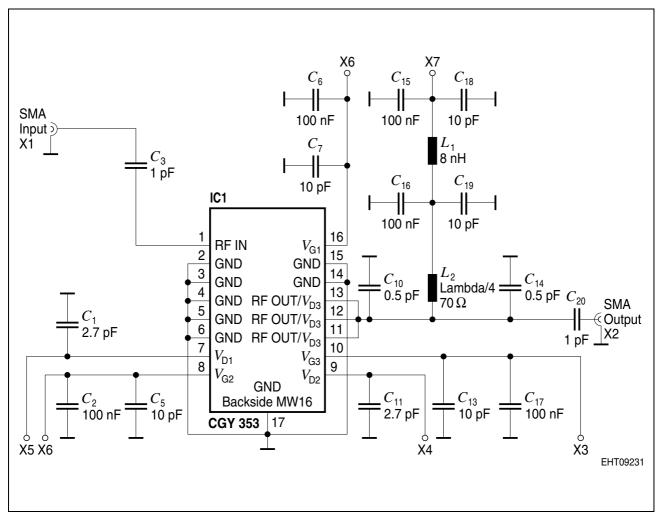

Figure 2 Application Circuit

#### Notes:

Input and output line:  $50 \Omega$

$C_{10}$  and  $C_{14}$ : 0402 capacitors

All other capacitors: 0603

$C_{20}$ : AVX 06035J1R0BBT

$L_1$ : Coilcraft Air Core Inductor A03T

Suggested Heat Sink: about 7 K/W

$V_{\rm D3}$  additionally blocked with 4.7  $\mu F/16$  V at connection X7

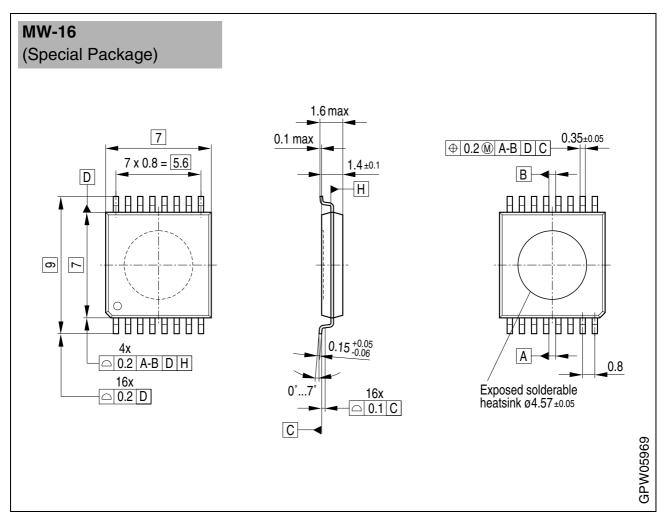

## **Package Outlines**

### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm