# 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

### FEATURES:

- 3.3V operation

- · JEDEC LVTTL compatible level

- Clock input is 5V tolerant

- Q outputs, Q/2 output

- <300ps output skew, Q0–Q4</li>

- Outputs 3-state and reset while OE/RST low

- · PLL disable feature for low frequency testing

- · Internal loop filter RC network

- Internal VCO/2 option

- · Balanced drive outputs ±24mA

- ESD >2000V

- 80MHz maximum frequency

- · Available in QSOP package

## **DESCRIPTION:**

The QS5LV931 Clock Driver uses an internal phase locked loop (PLL) to lock low skew outputs to a reference clock input. Six outputs are available: Q0–Q4, Q/2. Careful layout and design ensure <300ps skew between the Qo-Q4, and Q/2 outputs. The QS5LV931 includes an internal RC filter which provides excellent jitter characteristics and eliminates the need for external components. Various combinations of feedback and a divide-by-2 in the VCO path allow applications to be customized for linear VCO operation over a wide range of input SYNC frequencies. The PLL can also be disabled by the PLL\_EN signal to allow low frequency or DC testing. The QS5LV931 is designed for use in cost sensitive high-performance computing systems, workstations, multi-board computers, networking hardware, and mainframe systems. Several can be used in parallel or scattered throughout a system for guaranteed low skew, system-wide clock distribution networks. In the QSOP package, the QS5LV931 clock driver represents the best value in small form factor, high-performance clock management products.

For more information on PLL clock driver products, see Application Note AN-227.

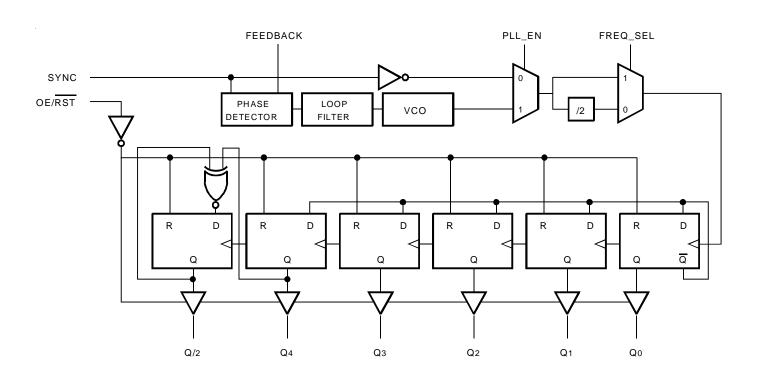

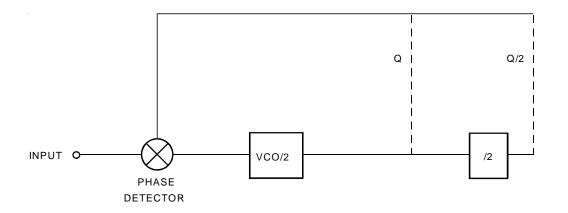

# FUNCTIONAL BLOCK DIAGRAM

1

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

### JANUARY 2002

## QS5LV931

### 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

#### **INDUSTRIAL TEMPERATURE RANGE**

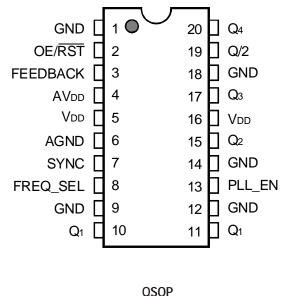

## **PINCONFIGURATION**

TOP VIEW

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol   | Description                           | Max         | Unit |

|----------|---------------------------------------|-------------|------|

| AVdd/Vdd | Supply Voltage to Ground              | –0.5 to +7  | V    |

|          | DC Input Voltage VIN                  |             | V    |

|          | Maximum Power Dissipation (TA = 85°C) | 0.5         | W    |

| Tstg     | Storage Temperature Range             | -65 to +150 | °C   |

NOTE:

Stresses beyond those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

### CAPACITANCE ( $TA = +25^{\circ}C$ , f = 1MHz, VIN = 0V)

| Pins | Тур. | Max. | Unit |

|------|------|------|------|

| Cin  | 3    | 4    | pF   |

| Соит | 4    | 5    | pF   |

### **PIN DESCRIPTION**

| Pin Name | I/O | Description                                                                                                                                |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC     |     | Reference clock input                                                                                                                      |

| FREQ_SEL | I   | VCO frequency select. For choosing optimal VCO operating frequency depending on input frequency. HIGH is for higher frequencies,           |

|          |     | LOW is for lower frequencies.                                                                                                              |

| FEEDBACK | I   | PLL feedback input which is connected to either a Q or a Q/2 output. External feedback provides flexibility for different output frequency |

|          |     | relationships. See the Frequency Selection Table for more information.                                                                     |

| Q0 -Q4   | 0   | Clock outputs                                                                                                                              |

| Q/2      | 0   | Clock output. Matched in phase, but frequency is half the Q frequency.                                                                     |

| OE/RST   | I   | Output enable/asynchronous reset. Resets all output registers. When 0, all outputs are held in a tri-stated condition. When 1, outputs are |

|          |     | enabled.                                                                                                                                   |

| PLL_EN   | I   | PLL enable. Enables and disables the PLL. Allows the SYNC input to be single-stepped for system debug.                                     |

| Vdd      | _   | Power supply for output buffers                                                                                                            |

| AVDD     | _   | Power supply for phase lock loop and other internal circuitries                                                                            |

| GND      | _   | Ground supply for output buffers                                                                                                           |

| AGND     | _   | Ground supply for phase lock loop and other internal circuitries                                                                           |

# OUTPUT FREQUENCY SPECIFICATIONS

Industrial: TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, AVDD/VDD = 3.3V  $\pm 0.3$ V

| Symbol   | Description             | - 50 | - 66 | - 80 | Units |

|----------|-------------------------|------|------|------|-------|

| Fmax_Q   | Max Frequency, Qo - Q4, | 50   | 66   | 80   | MHz   |

| Fmax_Q/2 | Max Frequency, Q/2      | 25   | 33   | 40   | MHz   |

| Fmin_q   | Min Frequency, Qo - Q4  | 10   | 10   | 10   | MHz   |

| Fmin_0/2 | Min Frequency, Q/2      | 5    | 5    | 5    | MHz   |

# FREQUENCY SELECTION TABLE

|          |                 | SYNC (MHz)                       |            |                 |                 |

|----------|-----------------|----------------------------------|------------|-----------------|-----------------|

|          | Output Used for | (allowable range) <sup>(1)</sup> |            | Output Frequenc | y Relationships |

| FREQ_SEL | Feedback        | Min. Max                         |            | Q/2             | Q0 - Q4         |

| HIGH     | Q/2             | Fmin_0/2                         | Fmax_Q/2   | SYNC            | SYNC X 2        |

| HIGH     | Q0 -Q4          | Fmin_q                           | Fmax_Q     | SYNC / 2        | SYNC            |

| LOW      | Q/2             | Fmin_0/2/2                       | Fmax_0/2/2 | SYNC            | SYNC X 2        |

| LOW      | Q0 -Q4          | Fmin_q/2                         | Fmax_0/2   | SYNC / 2        | SYNC            |

NOTE:

1. Operation in the specified SYNC frequency range guarantees that the VCO will operate in its optimal range of 20MHz to FMAX\_0 x2. Operation with Sync inputs outside specified frequency ranges may result in out-of-lock outputs. FREQ\_SEL only affects VCO frequency and does not affect output frequencies.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, AVDD/VDD = 3.3V  $\pm 0.3$ V

| Symbol | Parameter              | Conditions                     | Min.      | Тур. | Max. | Unit |

|--------|------------------------|--------------------------------|-----------|------|------|------|

| Vih    | Input HIGH Voltage     | Guaranteed Logic HIGH Level    | 2         | _    | _    | V    |

| VIL    | Input LOW Voltage      | Guaranteed Logic LOW Level     | —         | _    | 0.8  | V    |

| Vон    | Output HIGH Voltage    | Iон = —24mA                    | VDD — 0.6 | _    | _    | V    |

|        |                        | Іон = —100µА                   | Vdd — 0.2 | _    | _    |      |

| Vol    | Output LOW Voltage     | VDD = Min., IOL = 24mA         | —         | _    | 0.45 | V    |

|        |                        | $VDD = Min., IOL = 100\mu A$   | —         | _    | 0.2  |      |

| Vн     | Input Hysteresis       | —                              | —         | 100  | _    | mV   |

| loz    | Output Leakage Current | Vout = VDD or GND,             | —         | _    | 5    | μA   |

|        |                        | VDD = Max., Outputs Disabled   |           |      |      |      |

| lin    | Input Leakage Current  | AVDD = Max., VIN = AVDD or GND | —         | —    | 5    | μΑ   |

## **POWER SUPPLY CHARACTERISTICS**

| Symbol       | Parameter                               | Test Conditions                        | Тур. | Max. | Unit   |

|--------------|-----------------------------------------|----------------------------------------|------|------|--------|

| IDDQ         | Quiescent Power Supply Current          | $VDD = Max., OE/\overline{RST} = LOW,$ | _    | 1    | mA     |

|              |                                         | SYNC = LOW, All outputs unloaded       |      |      |        |

| $\Delta$ IDD | Power Supply Current per Input HIGH     | VDD = Max., VIN = 3V                   | 1    | 30   | μA     |

| IDDD         | Dynamic Power Supply Current per Output | VDD = Max., CL = 0pF                   | 0.2  | 0.3  | μA/MHz |

# INPUT TIMING REQUIREMENTS

| Symbol | Description <sup>(1)</sup>                    | Min. | Max.   | Unit |

|--------|-----------------------------------------------|------|--------|------|

| tr, tr | Maximum input rise and fall times, 0.8V to 2V | _    | 3      | ns   |

| Fi     | Input Clock Frequency, SYNC <sup>(1)</sup>    | 2.5  | Fmax_Q | MHz  |

| tPWC   | Input clock pulse, HIGH or LOW <sup>(2)</sup> | 2    | _      | ns   |

| Dн     | Duty Cycle, SYNC <sup>(2)</sup>               | 25   | 75     | %    |

NOTES:

1. See Output Frequency and Frequency Selection tables for more detail on allowable SYNC input frequencies for different speed grades with different FEEDBACK and FREQ\_SEL combinations.

<sup>2.</sup> Where pulse with implied by  $\mathsf{D}\mathsf{H}$  is less than twpc limit, twpc limit applies

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE

| Symbol        | Parameter (1)                                                   | Min.      | Max.        | Unit |

|---------------|-----------------------------------------------------------------|-----------|-------------|------|

| <b>t</b> SKR  | Output Skew Between Rising Edges, Qo-Q4 and Q/2 <sup>(2)</sup>  | —         | 300         | ps   |

| <b>t</b> SKF  | Output Skew Between Falling Edges, Qo-Q4 and Q/2 <sup>(2)</sup> | —         | 300         | ps   |

| tPW           | Pulse Width, Qo-Q4, Q/2 outputs, 80MHz                          | Tcy/2-0.4 | Tcy/2 + 0.4 | ns   |

| tı            | Cycle-to-Cycle Jitter (4)                                       | — 0.15    | 0.15        | ns   |

| tPD           | SYNC Input to Feedback Delay (5)                                | - 500     | 500         | ps   |

| <b>t</b> LOCK | SYNC to Phase Lock                                              | —         | 10          | ms   |

| tрzн          | Output Enable Time, OE/RST LOW to HIGH (3)                      | 0         | 14          | ns   |

| tPZL          |                                                                 |           |             |      |

| tPHZ          | Output Disable Time, OE/RST HIGH to LOW <sup>(3)</sup>          | 0         | 14          | ns   |

| tPLZ          |                                                                 |           |             |      |

| tR,tF         | Output Rise/Fall Times, 0.8V ~ 2V                               | 0.3       | 2           | ns   |

NOTES:

1. See Test Loads and Waveforms for test load and termination.

2. Skew specifications apply under identical environments (loading, temperature, VDD, device speed grade).

3. Measured in open loop mode  $PLL_EN = 0$ .

4. Jitter is characterized with Q output at 20MHz. See Frequency Selection Table for information on proper FREQ\_SEL level for specified input frequencies.

5. tPD measured at device inputs at 0.5VDD, Q output at 80MHz.

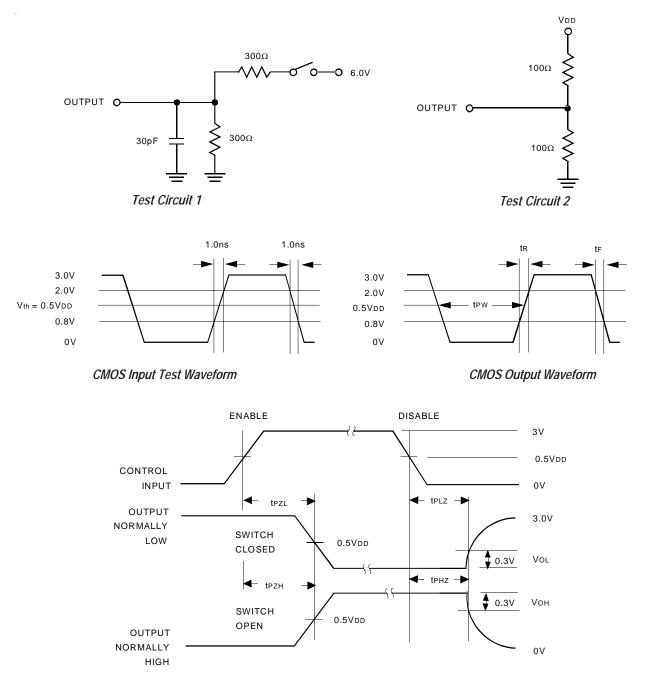

## AC TEST LOADS AND WAVEFORMS

#### Enable and Disable Times

TEST CIRCUIT 1 is used for output enable/disable parameters. TEST CIRCUIT 2 is used for all other timing parameters.

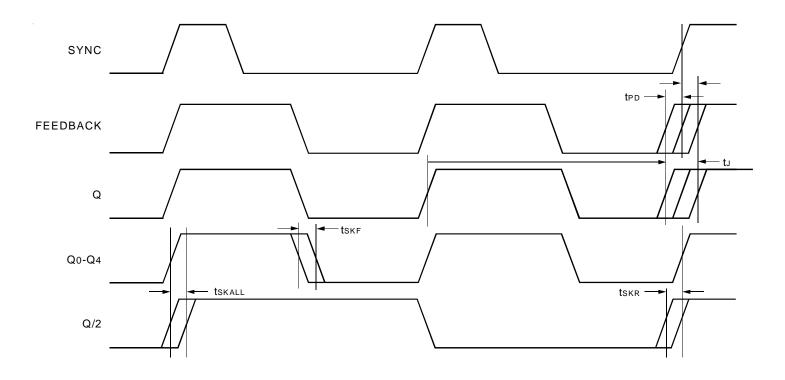

## AC TIMING DIAGRAM

#### NOTES:

1. AC Timing Diagram applies to  $\ensuremath{\mathsf{Q}}$  output connected to FEEDBACK .

2. All parameters are measured at 0.5Vpp.

#### QS5LV931 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

## PLLOPERATION

The Phase Locked Loop (PLL) circuit included in the QS5LV931 provides for replication of incoming SYNC clock signals. Any manipulation of that signal, such as frequency multiplying, is performed by digital logic following the PLL (see the block diagram). The key advantage of the PLL

circuit is to provide an effective zero propagation delay between the output and input signals. In fact, adding delay circuits in the feedback path, 'propagation delay' can even be negative! A simplified schematic of the QS5LV931 PLL circuit is shown below.

## SIMPLIFIED DIAGRAM OF QS5LV931 FEEDBACK

The phase difference between the output and the input frequencies feeds the VCO which drives the outputs. Whichever output is fed back, it will stabilize at the same frequency as the input. Hence, this is a true negative feedback closed loop system. In most applications, the output will optimally have zero phase shift with respect to the input. In fact, the internal loop filter on the QS5LV931 typically provides within 150ps of phase shift between input and output. If the user wishes to vary the phase difference (typically to compensate for backplane delays), this is most easily accomplished by adding delay circuits to the feedback path. The respective output used for feedback will be advanced by the amount of delay in the feedback path. All other outputs will retain their proper relationships to that output.

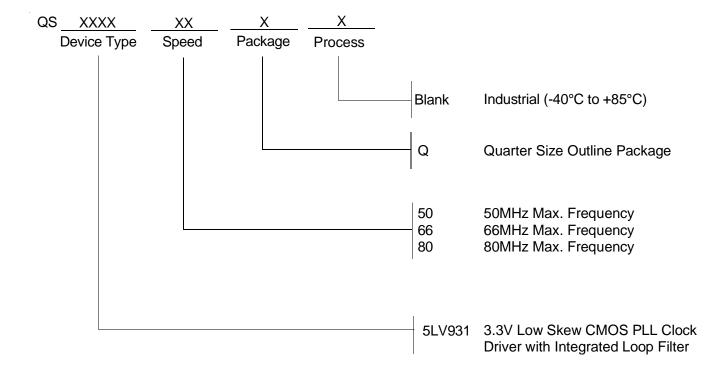

## ORDERING INFORMATION

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 *for SALES:* 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com *for Tech Support:* logichelp@idt.com (408) 654-6459