21-S3-CK215/FK215-092002

# **USER'S MANUAL**

S3CK215/FK215 CalmRISC 8-Bit CMOS Microcontroller Revision 1

# PRODUCT OVERVIEW

# OVERVIEW

The S3CK215/FK215 single-chip CMOS microcontroller is designed for high performance using Samsung's new 8-bit CPU core, CalmRISC.

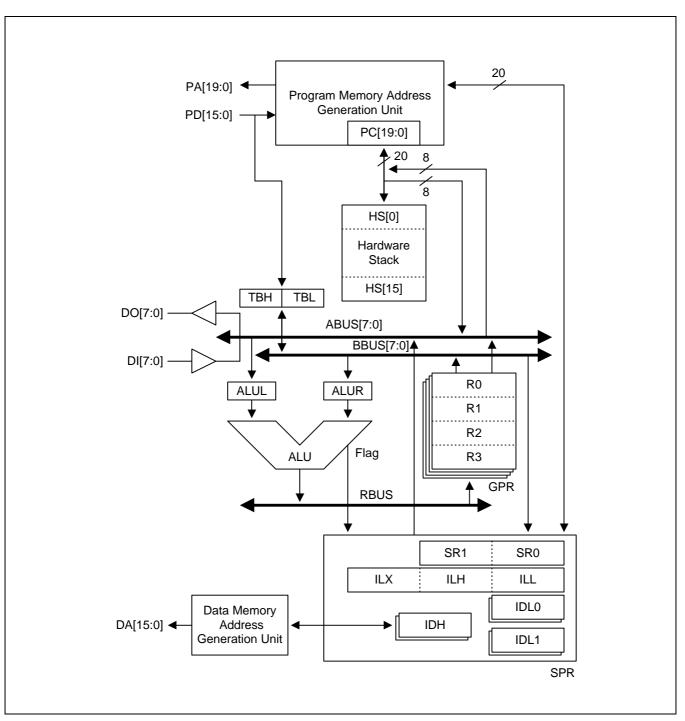

CalmRISC is an 8-bit low power RISC microcontroller. Its basic architecture follows Harvard style, that is, it has separate program memory and data memory. Both instruction and data can be fetched simultaneously without causing a stall, using separate paths for memory access. Represented below is the top block diagram of the CalmRISC microcontroller.

Figure 1-1. Top Block Diagram

The CalmRISC building blocks consist of:

- An 8-bit ALU

- 16 general purpose registers (GPR)

- 11 special purpose registers (SPR)

- 16-level hardware stack

- Program memory address generation unit

- Data memory address generation unit

Sixteen GPRs are grouped into four banks (Bank0 to Bank3), and each bank has four 8-bit registers (R0, R1, R2, and R3). SPRs, designed for special purposes, include status registers, link registers for branch-link instructions, and data memory index registers. The data memory address generation unit provides the data memory address (denoted as DA[15:0] in the top block diagram) for a data memory access instruction. Data memory contents are accessed through DI[7:0] for read operations and DO[7:0] for write operations. The program memory address generation unit contains a program counter, PC[19:0], and supplies the program memory address through PA[19:0] and fetches the corresponding instruction through PD[15:0] as the result of the program memory access. CalmRISC has a 16-level hardware stack for low power stack operations as well as a temporary storage area.

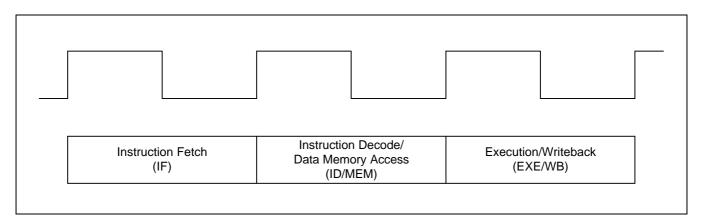

#### Figure 1-2. CalmRISC Pipeline Diagram

CalmRISC has a 3-stage pipeline as described below:

As can be seen in the pipeline scheme, CalmRISC adopts a register-memory instruction set. In other words, data memory where *R* is a GPR can be one operand of an ALU instruction as shown below:

The first stage (or cycle) is the Instruction fetch stage (IF for short), where the instruction pointed by the program counter, PC[19:0], is read into the Instruction Register (IR for short). The second stage is the Instruction Decode and Data Memory Access stage (ID/MEM for short), where the fetched instruction (stored in IR) is decoded and data memory access is performed, if necessary. The final stage is the Execute and Write-back stage (EXE/WB), where the required ALU operation is executed and the result is written back into the destination registers.

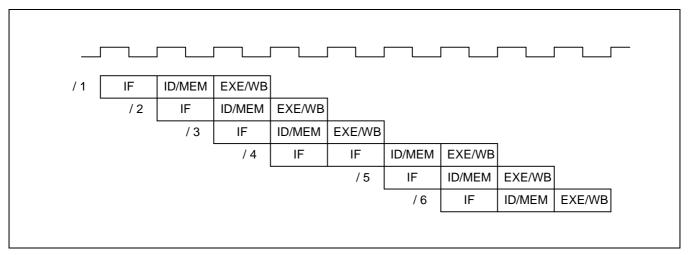

Since CalmRISC instructions are pipelined, the next instruction fetch is not postponed until the current instruction is completely finished but is performed immediately after completing the current instruction fetch. The pipeline stream of instructions is illustrated in the following diagram.

Figure 1-3. CalmRISC Pipeline Stream Diagram

Most CalmRISC instructions are 1-word instructions, while same branch instructions such as long "call" and "jp" instructions are 2-word instructions. In Figure 1-3, the instruction, *I4*, is a long branch instruction, and it takes two clock cycles to fetch the instruction. As indicated in the pipeline stream, the number of clocks per instruction (CPI) is 1 except for long branches, which take 2 clock cycles per instruction.

### FEATURES

#### CPU

CalmRISC core (8-bit RISC architecture)

#### Memory

- ROM: 8K-word (16K-byte)

- RAM: 1024-byte (excluding LCD data RAM)

#### Stack

• Size: maximum 16 word-level

#### 39 I/O Pins

• 39 configurable I/O pins

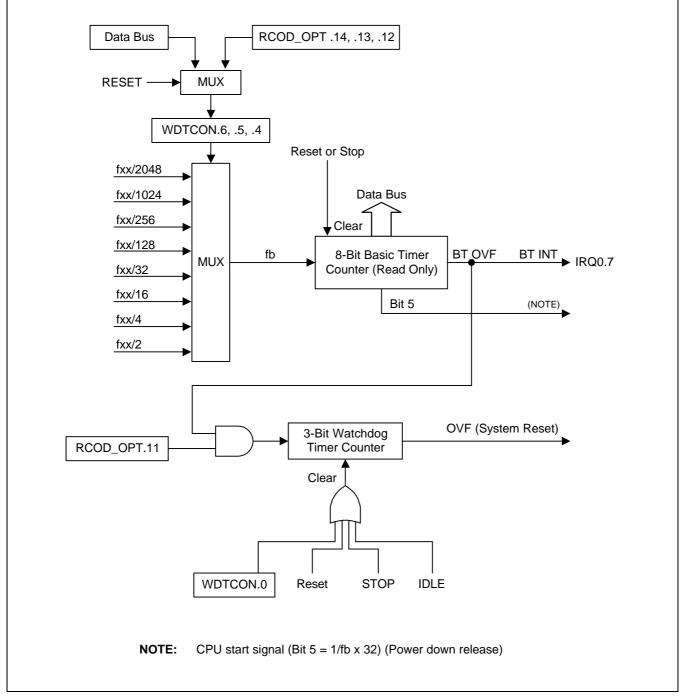

#### **Basic Timer**

- Overflow signal makes a system reset

- Watchdog function

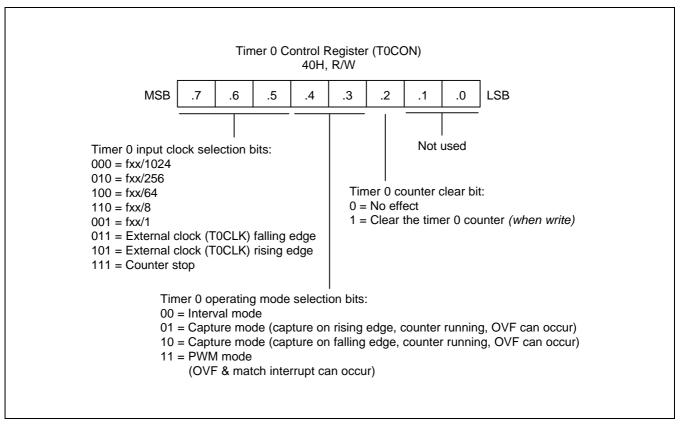

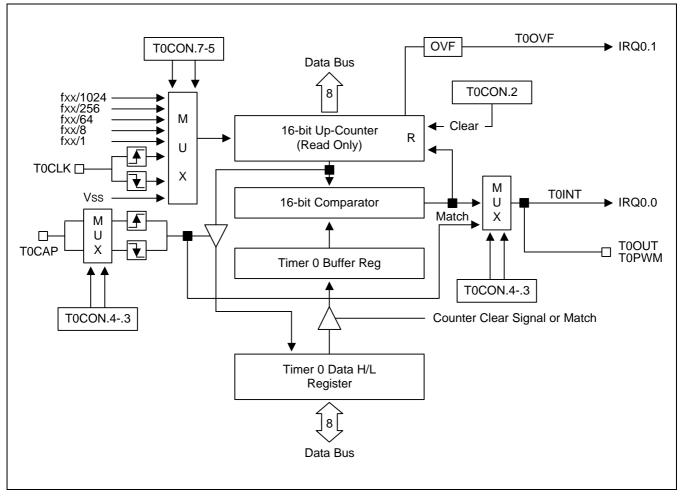

#### 16-bit Timer/Counter 0

- Programmable 16-bit timer

- Interval, capture, PWM mode

- Match/capture, overflow interrupt

#### 16-bit Timer/Counter 1

- Programmable 16-bit timer

- Match interrupt generator

#### 8-bit Timer/Counter 2

- Programmable 8-bit timer

- Interval, capture, PWM mode

- Match/capture, overflow interrupt

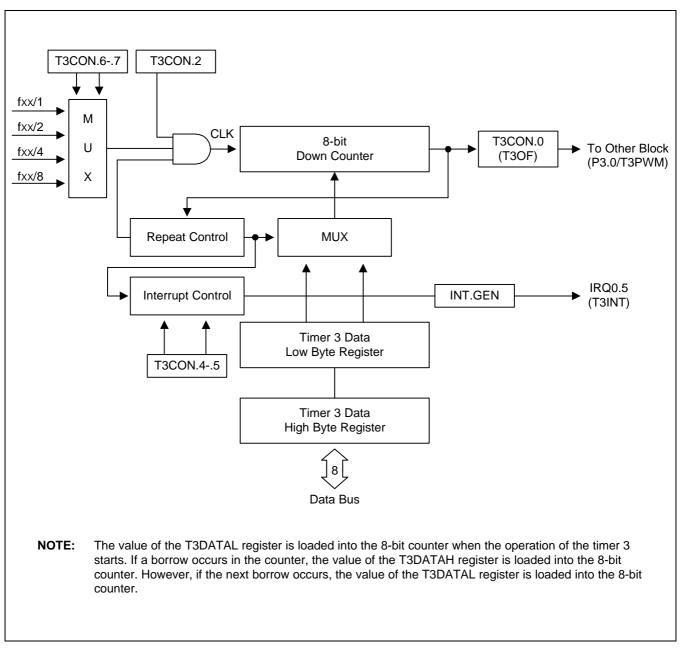

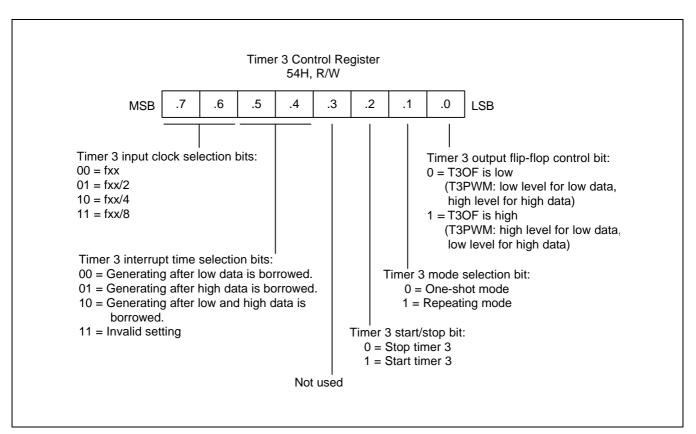

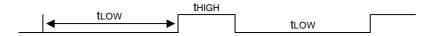

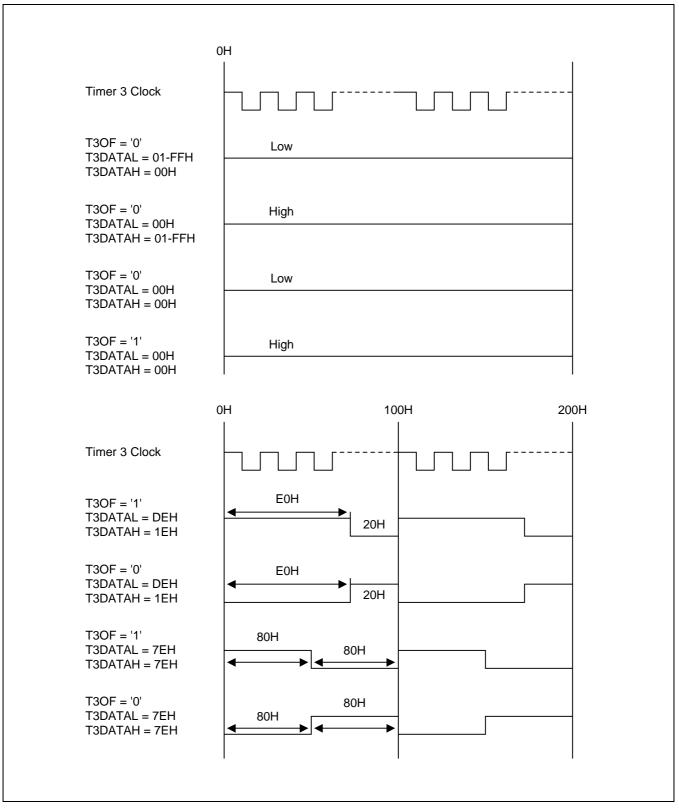

#### 8-bit Timer/Counter 3

- Programmable 8-bit timer

- Match interrupt/carrier frequency generator

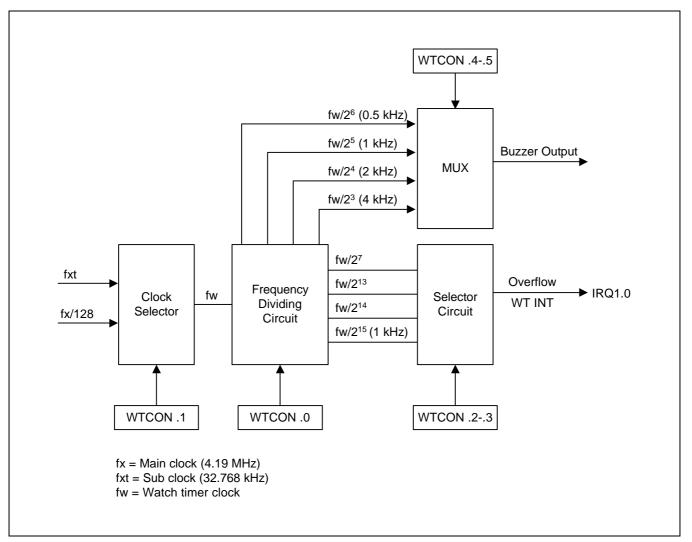

#### Watch Timer

- Real-time and interval time measurement

- Clock generation for LCD

- Four frequency outputs for buzzer sound (0.5/1/2/4 kHz at 32.768 kHz)

# SAMSUNG ELECTRONICS

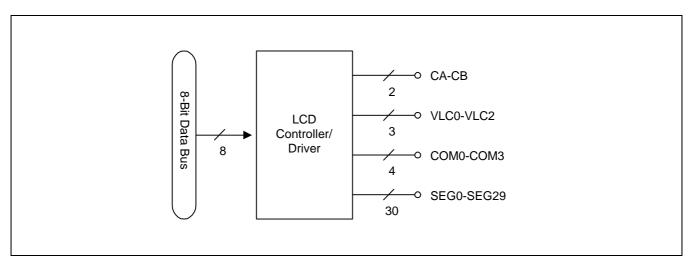

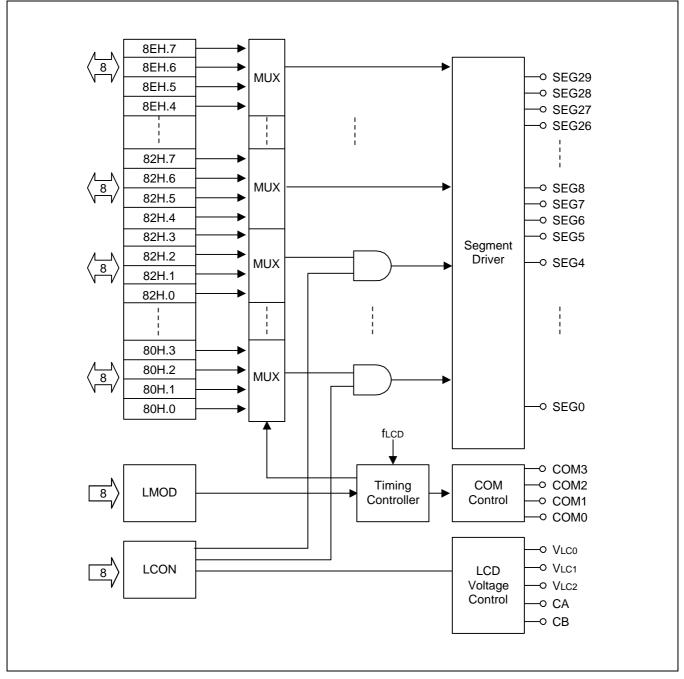

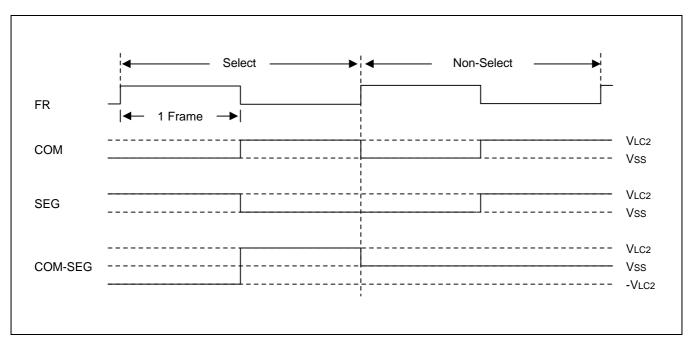

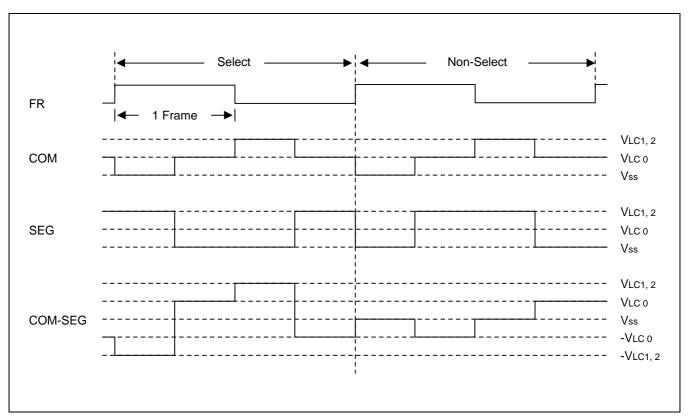

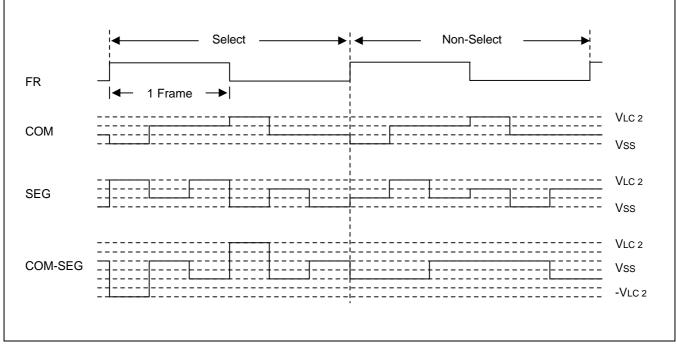

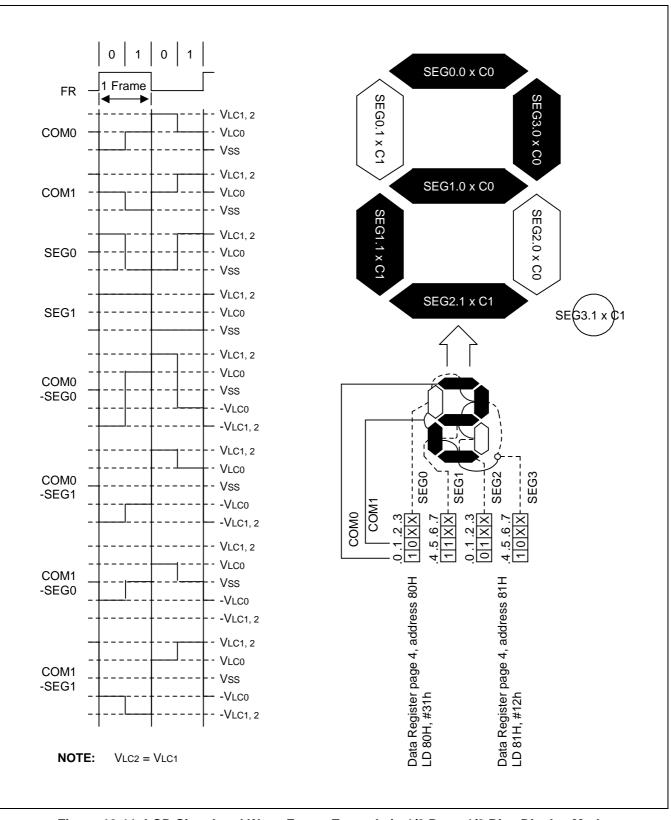

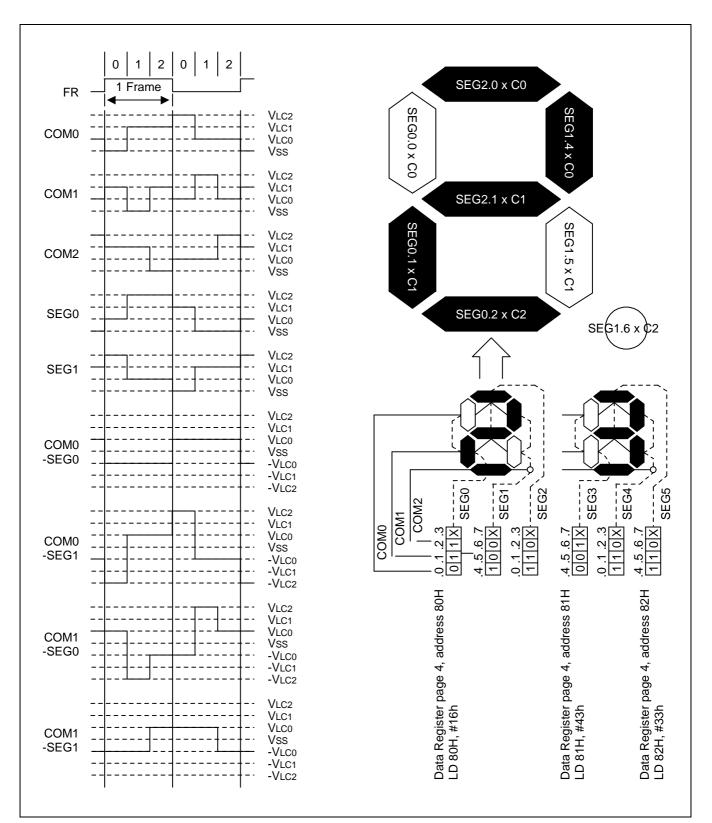

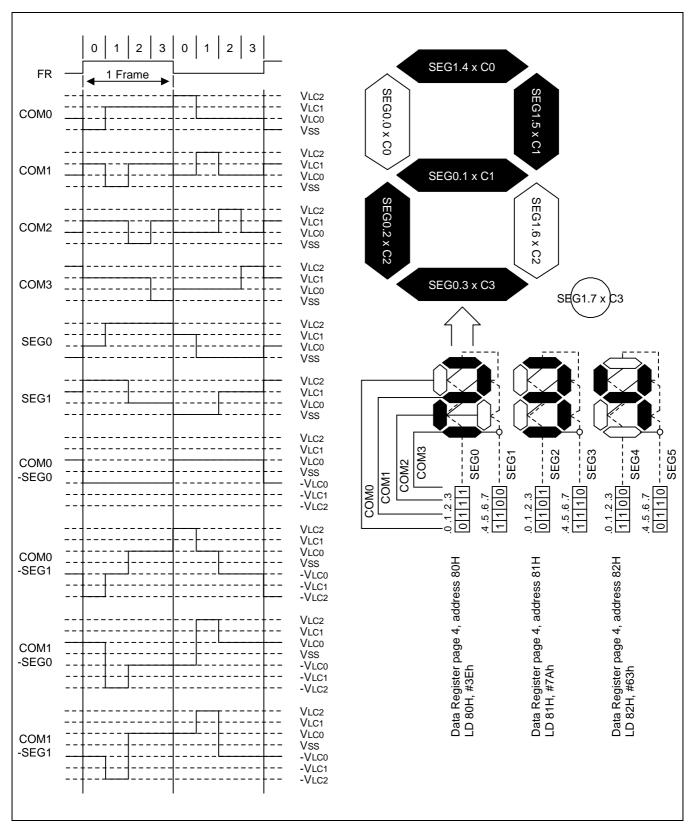

#### LCD Controller/Driver

- 30 segments and 4 common terminals

- Static, 1/2 duty, 1/3 duty, 1/4 duty

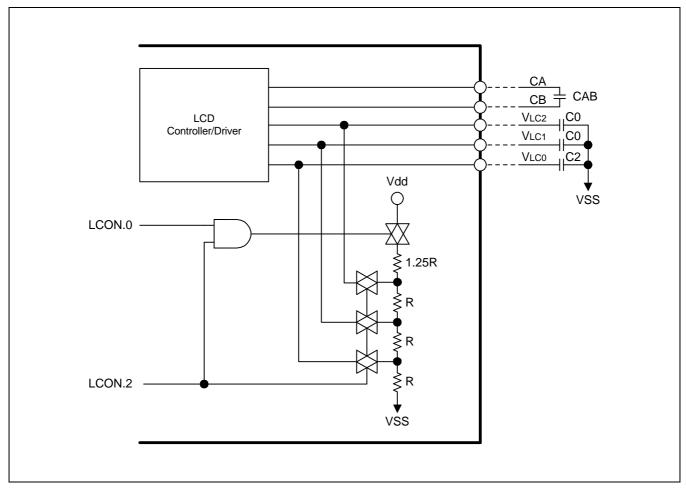

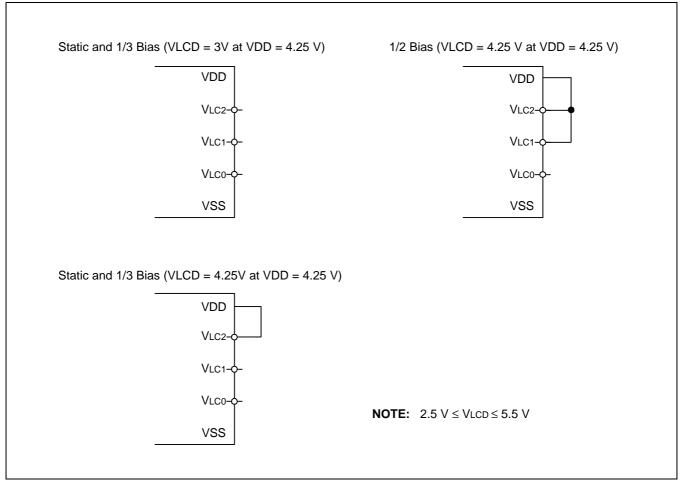

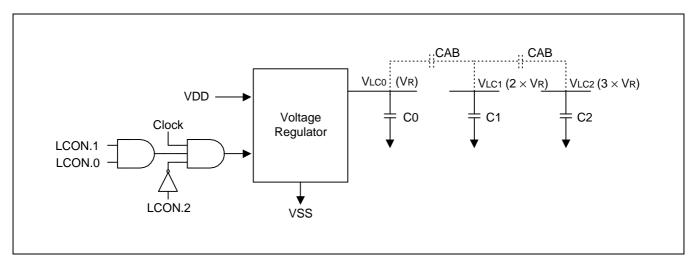

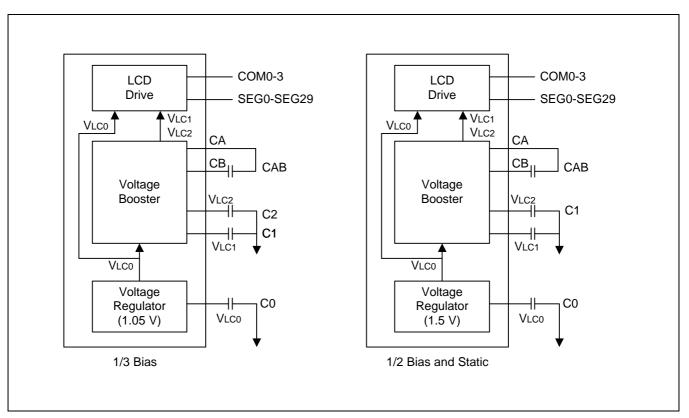

#### Voltage Regulator and Booster

- LCD display voltage supply

- Capacitor/Resistor bias selectable

- 3.0 V drive

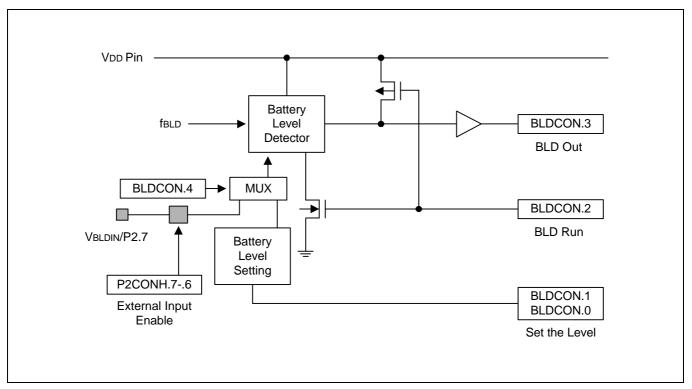

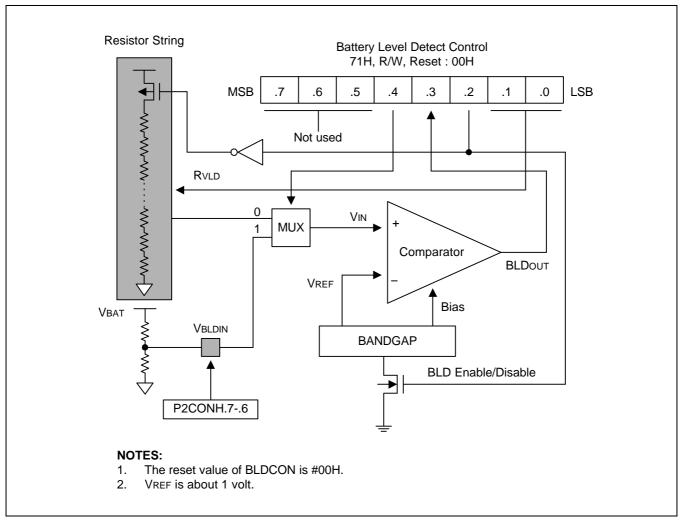

#### **Battery Level Detector**

Programmable detection voltage (2.4 V, 3.0 V, 4.0 V)

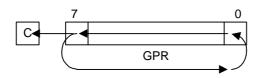

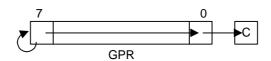

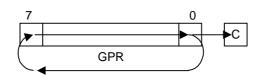

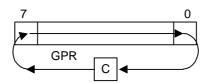

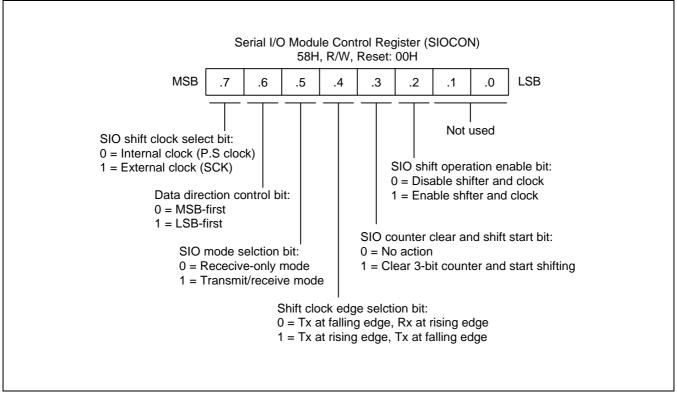

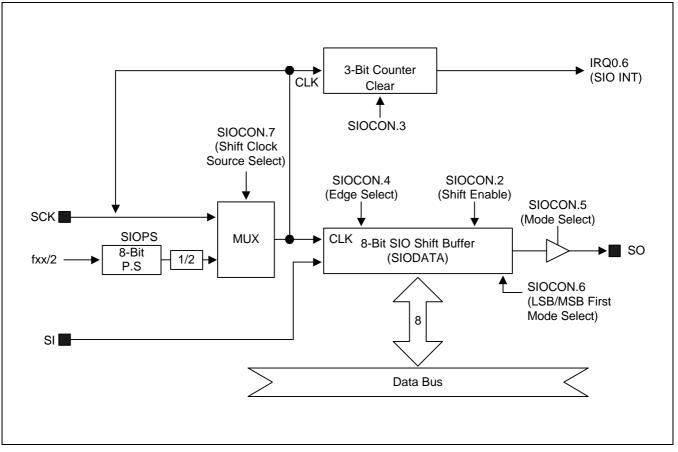

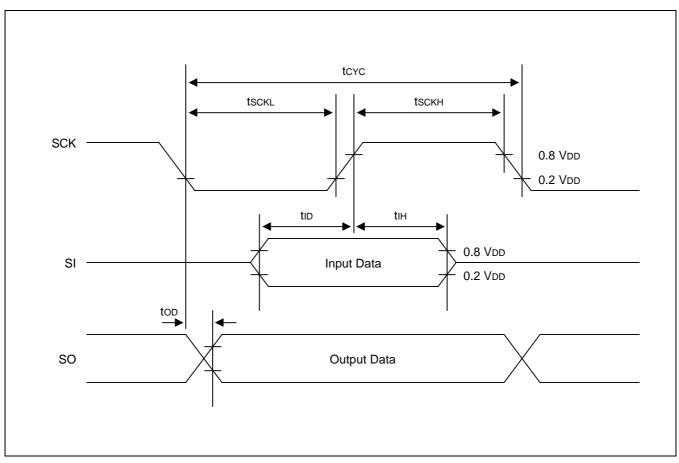

#### 8-Bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive mode

- LSB-first/MSB-first transmission selectable

- Internal/external clock source

#### A/D Converter

- Eight analog input channels

- 25 μs conversion speed at 8 MHz

- 10-bit conversion resolution

- Operating voltage: 2.7 V to 5.5 V

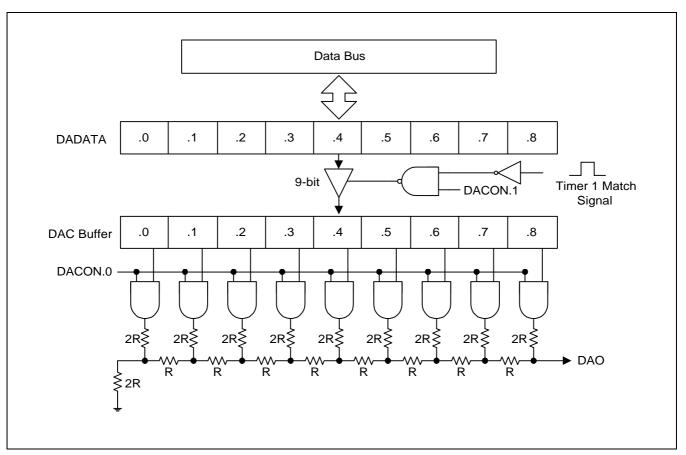

#### **D/A Converter**

- One analog output channel

- 9-bit conversion resolution (R-2R)

- Operating voltage: 2.7 V to 5.5 V

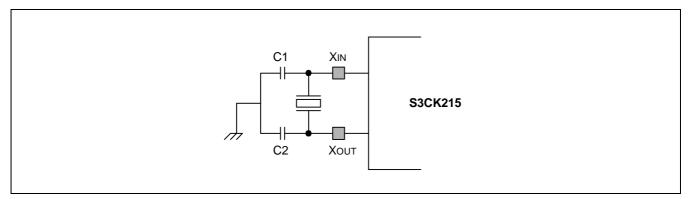

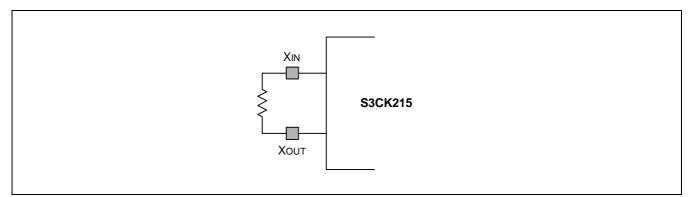

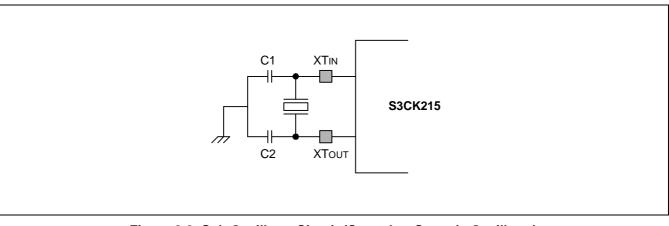

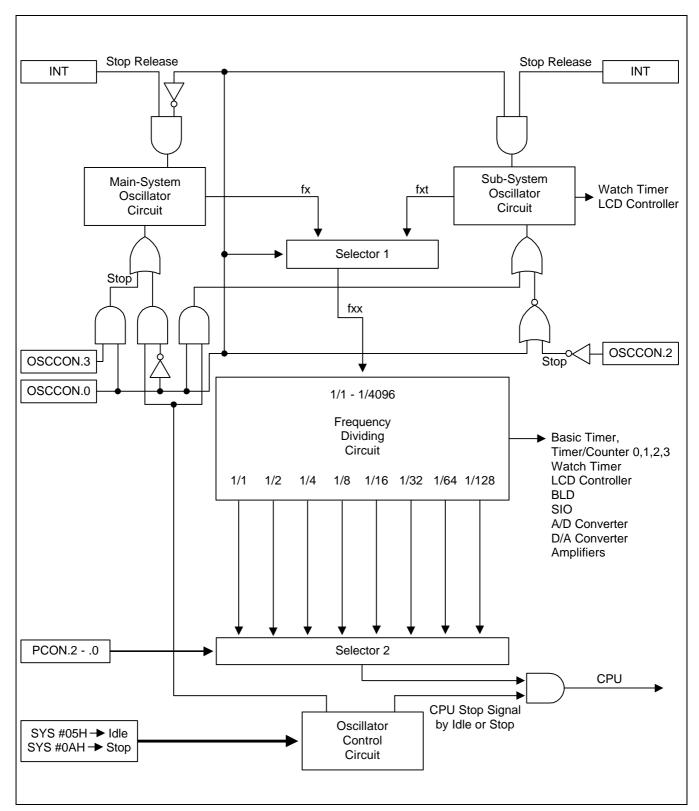

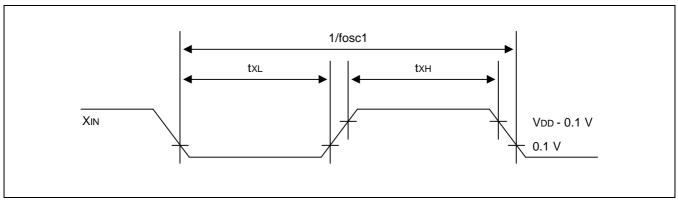

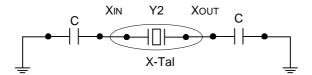

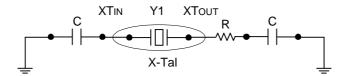

#### **Oscillation Sources**

- Crystal, ceramic, RC for main clock

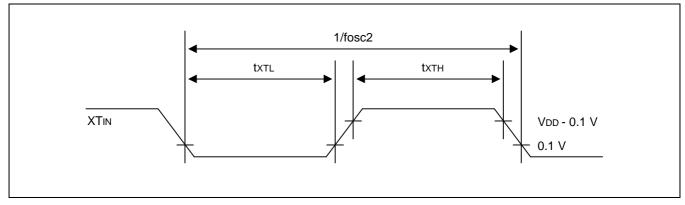

- Crystal for sub clock

- Main clock frequency 0.4–8 MHz

- Sub clock frequency: 32.768 kHz

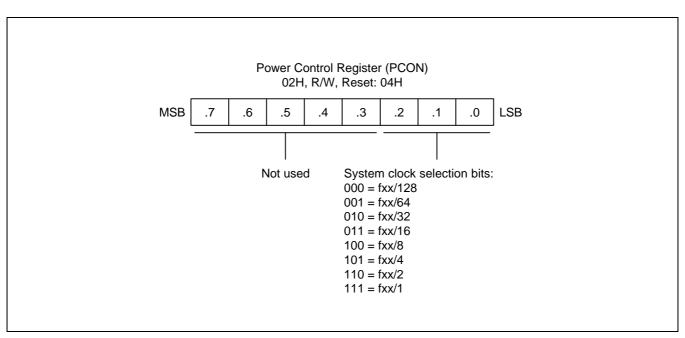

- CPU clock divider circuit (divided by 1, 2, 4, 8, 16, 32, 64 or 128)

#### **Two Power-Down Modes**

- Idle (only CPU clock stops)

- Stop (System clock stops)

#### Interrupts

• 2 Vectors, 13 interrupts

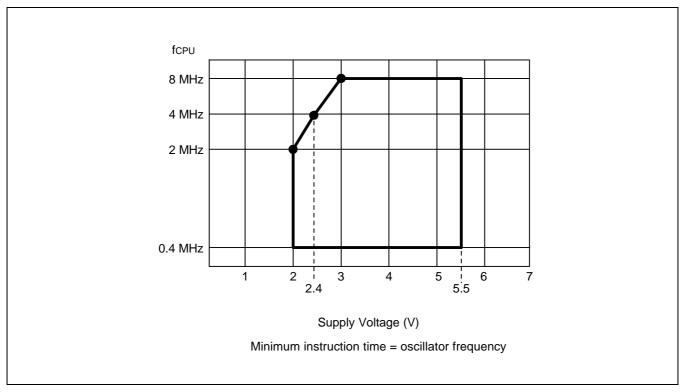

#### **Instruction Execution Times**

- 125 ns at 8 MHz (main clock)

- 30.5 µs at 32.768 kHz (sub clock)

#### **Operating Temperature Range**

- 25 °C to 85 °C

#### **Operating Voltage Range**

- 2.0 V to 5.5 V at 2 MHz (2MIPS)

- 2.4 V to 5.5 V at 4 MHz (4MIPS)

- 3.0 V to 5.5 V at 8 MHz (8MIPS)

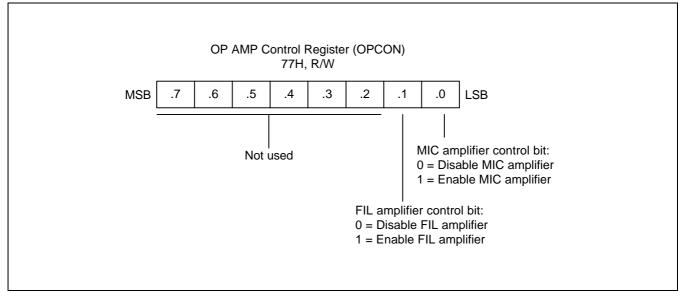

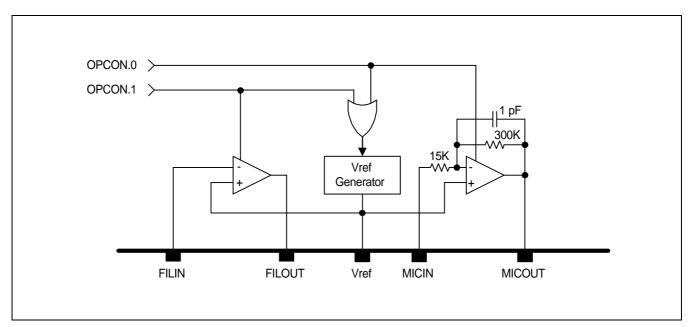

#### **Two Amplifiers**

• Microphone and filter

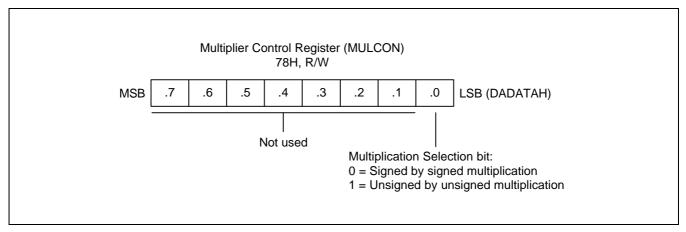

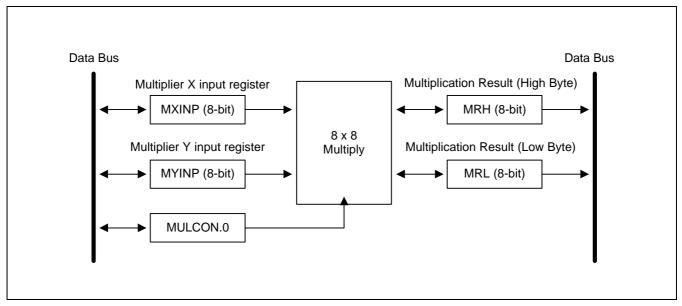

#### 8 × 8 Multiplication

• Signed by signed, unsigned by unsigned

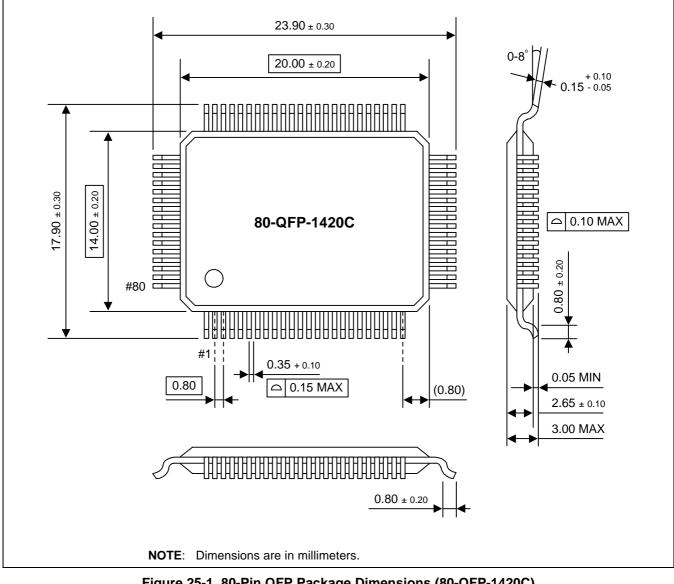

#### Package Type

• 80-pin QFP-1420

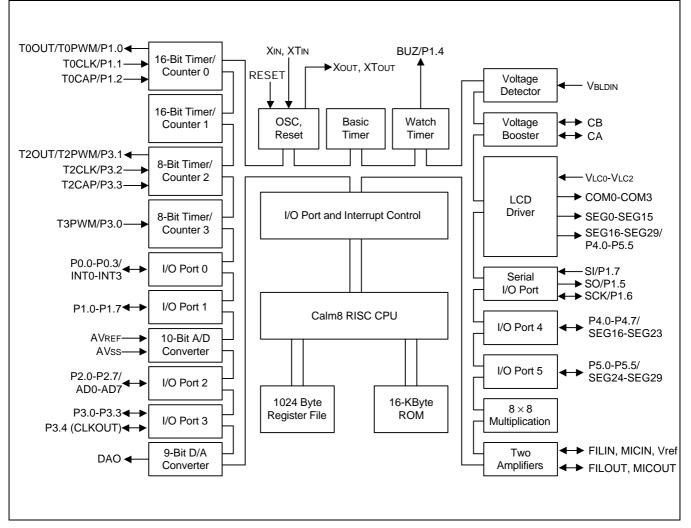

### **BLOCK DIAGRAM**

Figure 1-4. Block Diagram

# **PIN ASSIGNMENT**

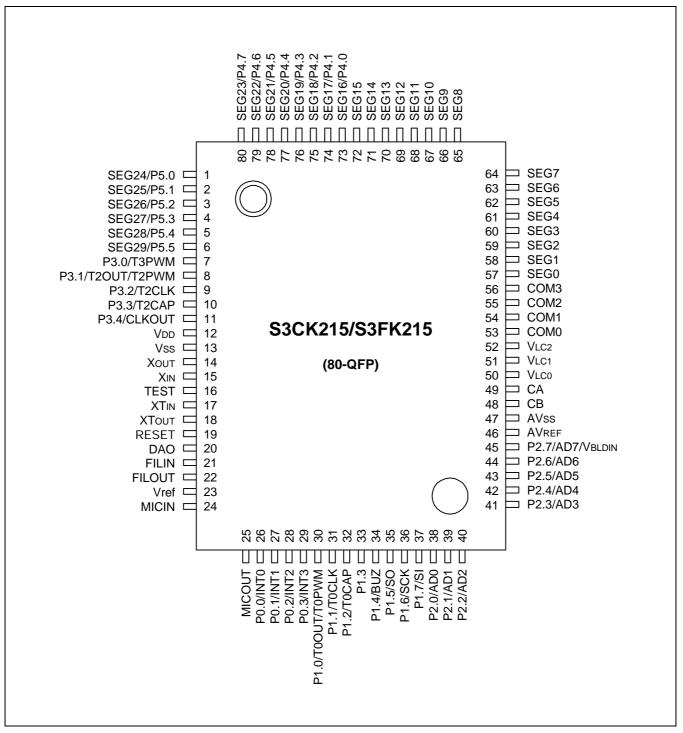

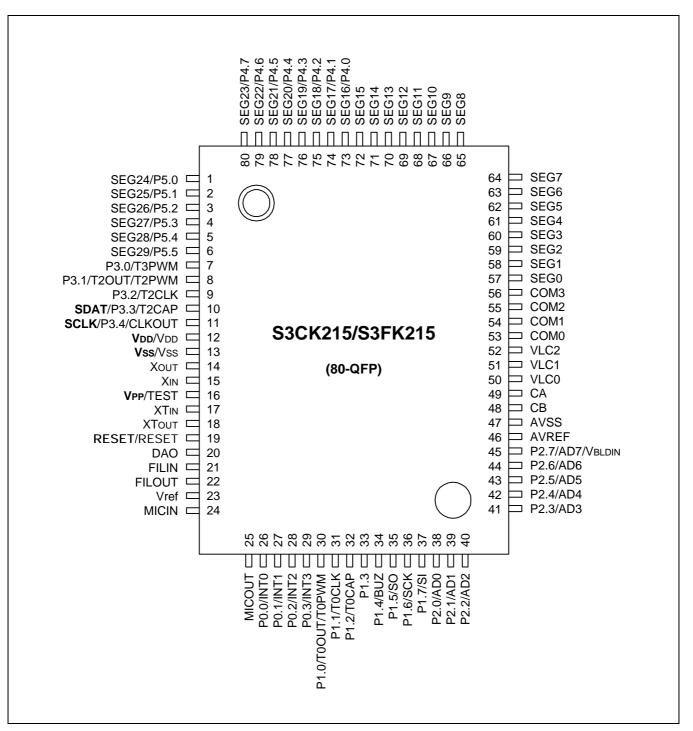

Figure 1-5. Pin Assignment (80-QFP)

# **PIN DESCRIPTIONS**

| Pin<br>Names                                                 | Pin<br>Type | Pin<br>Description                                                                                                                                                                                     | Circuit<br>Type | Pin<br>Numbers                               | Share<br>Pins                                                |

|--------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------|--------------------------------------------------------------|

| P0.0<br>P0.1<br>P0.2<br>P0.3                                 | I/O         | I/O port with bit programmable pins;<br>Schmitt trigger input or output mode<br>selected by software; software<br>assignable pull-up resistors.<br>(with noise filter and interrupt control).          | D-4             | 26<br>27<br>28<br>29                         | INT0<br>INT1<br>INT2<br>INT3                                 |

| P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6<br>P1.7 | I/O         | I/O port with bit programmable pins;<br>Schmitt trigger input or output mode<br>selected by software; Open-drain output<br>mode can be selected by software;<br>software assignable pull-up resistors. | E-4             | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | T0OUT/T0PWM<br>T0CLK<br>T0CAP<br>-<br>BUZ<br>SO<br>SCK<br>SI |

| P2.0-P2.6<br>P2.7                                            | I/O         | I/O port with bit programmable pins;<br>normal input or output mode selected by<br>software; software assignable pull-up<br>resistors.                                                                 | F-10<br>F-18    | 38-44<br>45                                  | AD0-AD6<br>V <sub>BLDIN</sub> /AD7                           |

| P3.0<br>P3.1<br>P3.2<br>P3.3<br>P3.4                         | I/O         | I/O port with bit programmable pins;<br>Schmitt trigger input or push-pull output<br>with software assignable pull-up<br>resistors.                                                                    | D-3             | 7-11                                         | T3PWM<br>T2OUT/T2PWM<br>T2CLK<br>T2CAP<br>CLKOUT             |

| P4.0-P4.7                                                    | I/O         | I/O port with bit programmable pins;<br>Push-pull or open-drain output and input<br>with software assignable pull-up<br>resistors.                                                                     | H-14            | 73-80                                        | SEG16-SEG23                                                  |

| P5.0-P5.5                                                    | I/O         | Have the same characteristic as port 4.                                                                                                                                                                | H-14            | 1-6                                          | SEG24-SEG29                                                  |

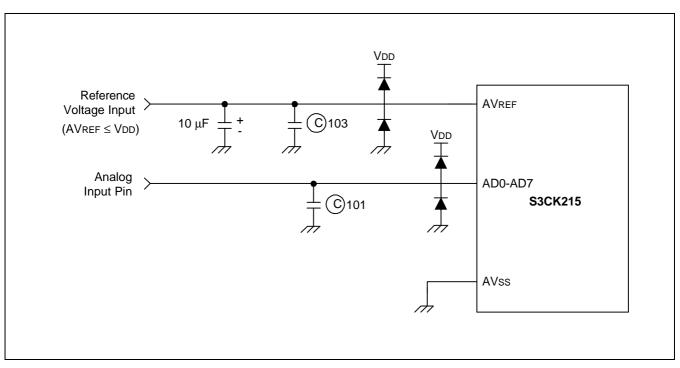

| AD0-AD6<br>AD7                                               | I/O         | A/D converter analog input channels                                                                                                                                                                    | F-10<br>F-18    | 38-44<br>45                                  | P2.0-P2.6<br>P2.7/V <sub>BLDIN</sub>                         |

| AV <sub>REF</sub>                                            | -           | A/D converter reference voltage                                                                                                                                                                        | -               | 46                                           | -                                                            |

| AV <sub>SS</sub>                                             | _           | A/D converter ground                                                                                                                                                                                   | _               | 47                                           | -                                                            |

| INT0-INT3                                                    | I/O         | External interrupt input pins                                                                                                                                                                          | D-4             | 26-29                                        | P0.0-P0.3                                                    |

| RESET                                                        | I           | System reset pin                                                                                                                                                                                       | В               | 19                                           | -                                                            |

| TEST                                                         | I           | Test signal input<br>(must be connected to V <sub>SS</sub> )                                                                                                                                           | _               | 16                                           | -                                                            |

#### Table 1-1. Pin Descriptions

| Pin<br>Names                       | Pin<br>Type | Pin<br>Description                                                                                                      | Circuit<br>Type | Pin<br>Numbers | Share<br>Pins |

|------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|

| V <sub>DD</sub> , V <sub>SS</sub>  | -           | Main power supply and ground                                                                                            | -               | 12,13          | -             |

| X <sub>OUT</sub> , X <sub>IN</sub> | -           | Main oscillator pins                                                                                                    | -               | 14,15          | -             |

| SO, SCK, SI                        | I/O         | Serial I/O interface clock signal                                                                                       | E-4             | 35-37          | P1.5-P1.7     |

| V <sub>BLDIN</sub>                 | I/O         | Voltage detector reference voltage<br>input                                                                             | F-18            | 45             | P2.7/AD7      |

| T3PWM                              | I/O         | Timer 3 PWM output                                                                                                      | D-3             | 7              | P3.0          |

| T2OUT/T2PWM                        | I/O         | Timer 2 output and PWM output                                                                                           | D-3             | 8              | P3.1          |

| T2CLK                              | I/O         | Timer 2 external clock input                                                                                            | D-3             | 9              | P3.2          |

| T2CAP                              | I/O         | Timer 2 capture input                                                                                                   | D-3             | 10             | P3.3          |

| T0OUT/T0PWM                        | I/O         | Timer 0 output and PWM output                                                                                           | E-4             | 30             | P1.0          |

| TOCLK                              | I/O         | Timer 0 external clock input                                                                                            | E-4             | 31             | P1.1          |

| T0CAP                              | I/O         | Timer 0 capture input                                                                                                   | E-4             | 32             | P1.2          |

| COM0-COM3                          | 0           | LCD common signal output                                                                                                | Н               | 53-56          | -             |

| SEG0-SEG15                         | 0           | LCD segment output                                                                                                      | Н               | 57-72          | -             |

| SEG16-SEG23                        | I/O         | LCD segment output                                                                                                      | H-14            | 73-80          | P4.0-P4.7     |

| SEG24-SEG29                        | I/O         | LCD segment output                                                                                                      | H-14            | 1-6            | P5.0-P5.5     |

| $V_{LC0}$ - $V_{LC2}$              | 0           | LCD power supply                                                                                                        | -               | 50-52          | -             |

| BUZ                                | I/O         | 0.5,1,2 or 4 kHz frequency output for<br>buzzer sound with 4.19 MHz main<br>system clock or 32768 Hz subsystem<br>clock | E-4             | 34             | P1.4          |

| CA, CB                             | _           | Capacitor terminal for voltage booster                                                                                  | -               | 48, 49         | -             |

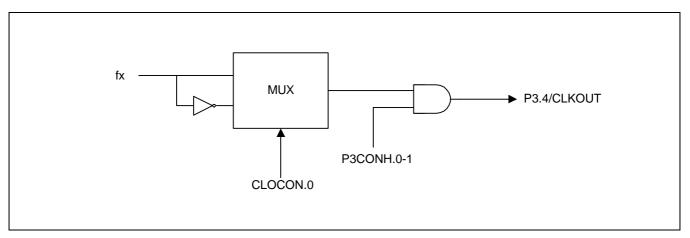

| CLKOUT                             | I/O         | Main oscillator clock output                                                                                            | D-3             | 11             | P3.4          |

| DAO                                | -           | DA converter output                                                                                                     | -               | 20             | _             |

| FILIN, FILOUT                      | -           | Filter amp input and output                                                                                             | -               | 21,22          | _             |

| MICIN, MICOUT                      | -           | MIC amp input and output                                                                                                | -               | 24,25          | -             |

| Vref                               | _           | Reference voltage input for filter amp and MIC amp                                                                      | -               | 23             | _             |

| Table 1-1 | . Pin | Descriptions | (Continued) |

|-----------|-------|--------------|-------------|

|-----------|-------|--------------|-------------|

# **PIN CIRCUITS**

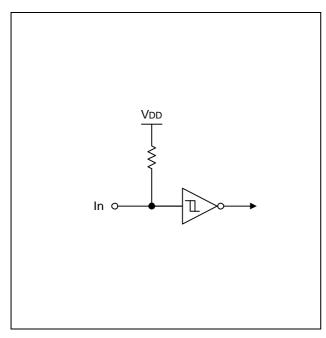

Figure 1-6. Pin Circuit Type B (RESET)

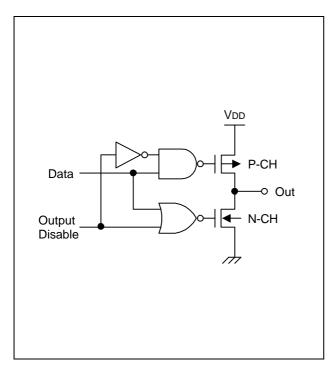

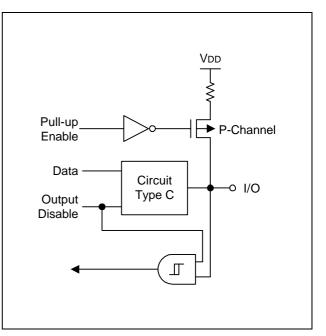

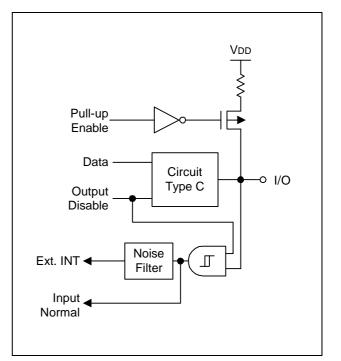

Figure 1-8. Pin Circuit Type C

Figure 1-7. Pin Circuit Type D-3 (P3)

Figure 1-9. Pin Circuit Type D-4 (P0)

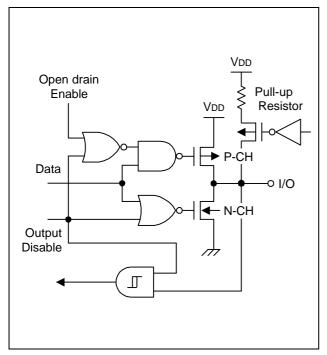

Figure 1-10. Pin Circuit Type E-4 (P1)

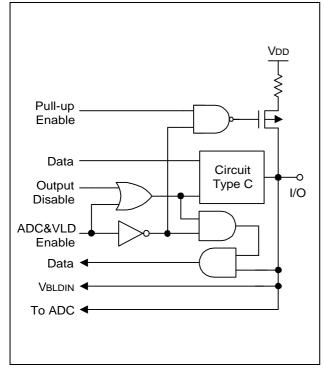

Figure 1-12. Pin Circuit Type F-18 (P2.7/V<sub>BLDIN</sub>)

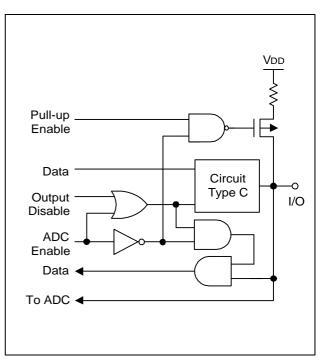

Figure 1-11. Pin Circuit Type F-10 (P2.0-P2.6)

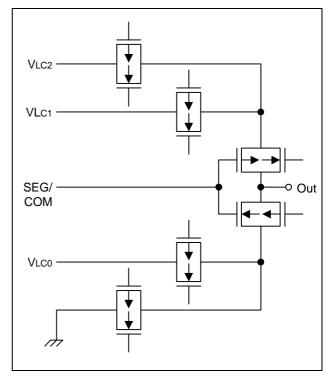

Figure 1-13. Pin Circuit Type H (SEG/COM)

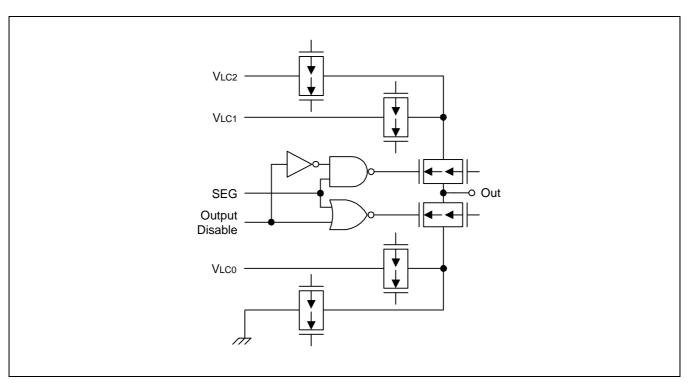

Figure 1-14. Pin Circuit Type H-4

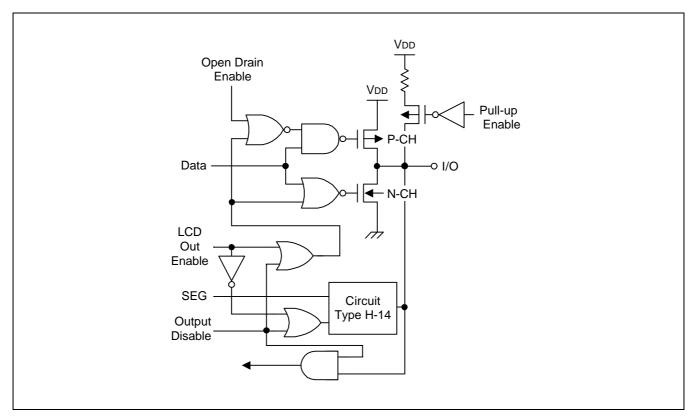

Figure 1-15. Pin Circuit Type H-14 (P4, P5)

NOTES

# **2** ADDRESS SPACES

# OVERVIEW

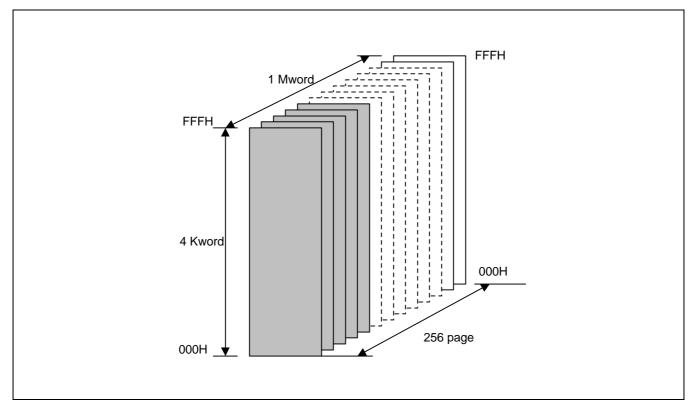

CalmRISC has 20-bit program address lines, *PA[19:0]*, which supports up to 1M words of program memory. The 1M word program memory space is divided into 256 pages and each page is 4K word long as shown in the next page. The upper 8 bits of the program counter, PC[19:12], points to a specific page and the lower 12 bits, PC[11:0], specify the offset address of the page.

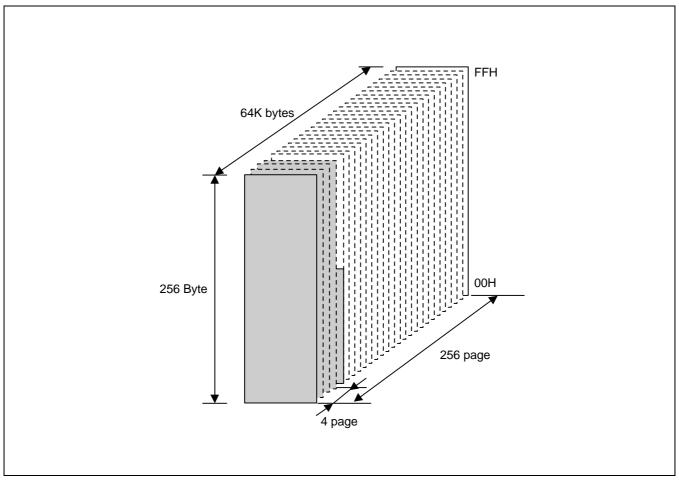

CalmRISC also has 16-bit data memory address lines, DA[15:0], which supports up to 64K bytes of data memory. The 64K byte data memory space is divided into 256 pages and each page has 256 bytes. The upper 8 bits of the data address, DA[15:8], points to a specific page and the lower 8 bits, DA[7:0], specify the offset address of the page.

# **PROGRAM MEMORY (ROM)**

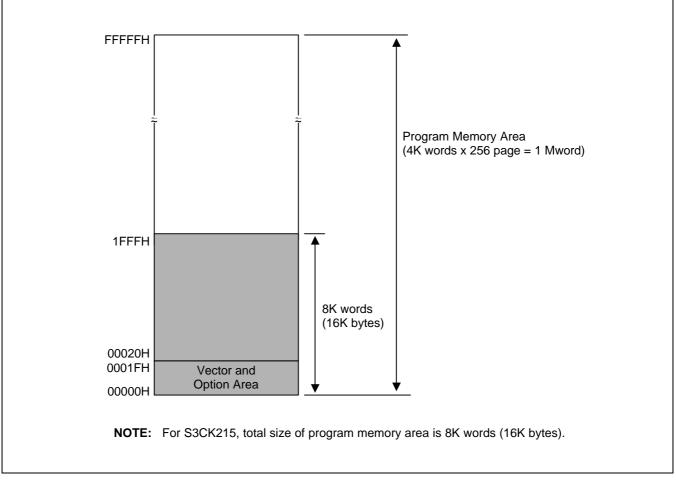

Figure 2-1. Program Memory Organization

For example, if PC[19:0] = 5F79AH, the page index pointed to by PC is 5FH and the offset in the page is 79AH. If the current PC[19:0] = 5EFFFH and the instruction pointed to by the current PC, i.e., the instruction at the address 5EFFFH is *not* a branch instruction, the next PC becomes 5E000H, *not* 5F000H. In other words, the instruction sequence wraps around at the page boundary, unless the instruction at the boundary (in the above example, at 5EFFFH) is a long branch instruction. The only way to change the program page is by long branches (LCALL, LLNK, and LJP), where the absolute branch target address is specified. For example, if the current PC[19:0] = 047ACH (the page index is 04H and the offset is 7ACH) and the instruction pointed to by the current PC, i.e., the instruction at the address 047ACH, is "LJP A507FH" (jump to the program address A507FH), then the next PC[19:0] = A507FH, which means that the page and the offset are changed to A5H and 07FH, respectively. On the other hand, the short branch instructions cannot change the page indices.

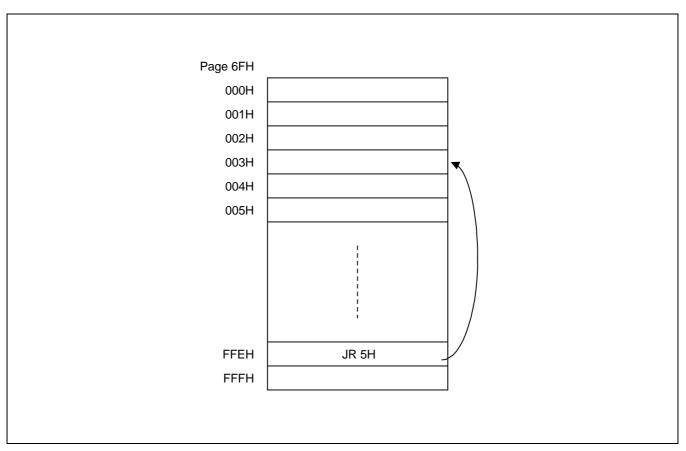

Suppose the current PC is 6FFFEH and its instruction is "JR 5H" (jump to the program address PC + 5H). Then the next instruction address is 6F003H, *not* 70003H. In other words, the branch target address calculation also wraps around with respect to a page boundary. This situation is illustrated below:

Figure 2-2. Relative Jump Around Page Boundary

Programmers do not have to manually calculate the offset and insert extra instructions for a jump instruction across page boundaries. The compiler and the assembler for CalmRISC are in charge of producing appropriate codes for it.

Figure 2-3. Program Memory Layout

From 00000H to 00004H addresses are used for the vector address of exceptions, and 0001EH, 0001FH are used for the option only. Aside from these addresses others are reserved in the vector and option area. Program memory area from the address 00020H to FFFFH can be used for normal programs.

The Program memory size of S3CK215 is 8K word (16K byte), so from the address 00020H to 1FFFH are the program memory area.

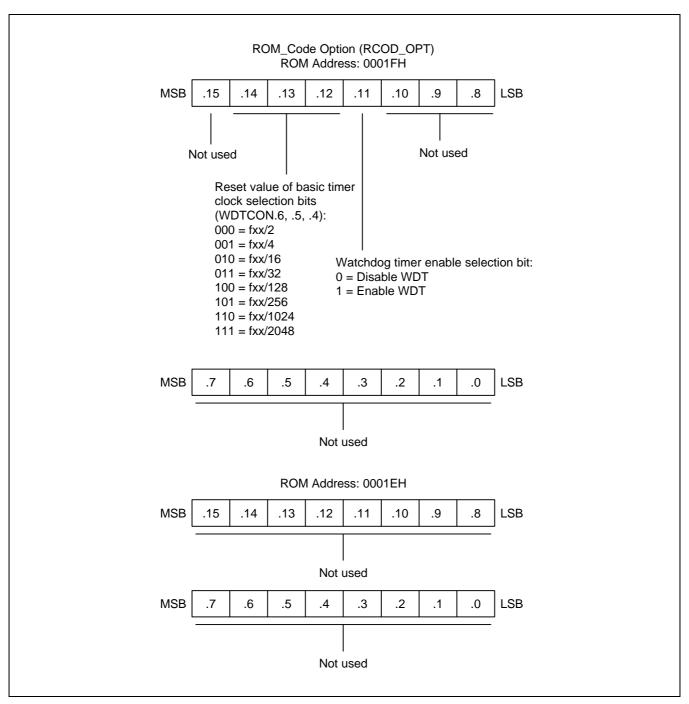

# **ROM CODE OPTION (RCOD\_OPT)**

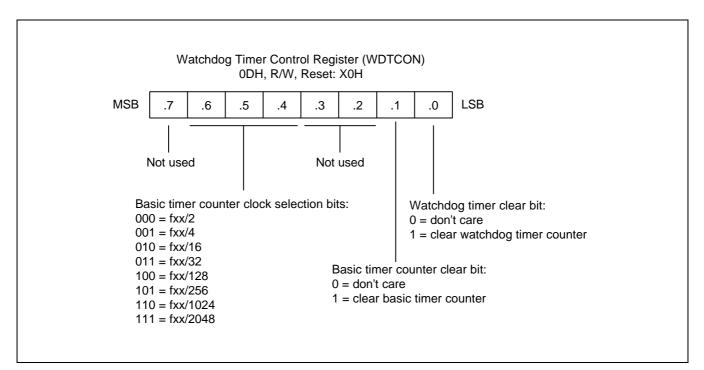

Just after power on, the ROM data located at 0001EH and 0001FH is used as the ROM code option. S3CK215 has ROM code options like the Reset value of Basic timer and Watchdog timer enable.

For example, if you program as below:

| RCOD_OPT | 1EH, 0x0000 |

|----------|-------------|

| RCOD_OPT | 1FH, 0xbfff |

- fxx/32 is used as Reset value of basic timer (by bit.14, 13, 12)

- Watchdog timer is enabled (by bit.11)

If you don't program any values in these option areas, then the default value is "1".

In these cases, the address 0001EH would be the value of "FFFFH".

Figure 2-4. ROM Code Option (RCOD\_OPT)

# DATA MEMORY ORGANIZATION

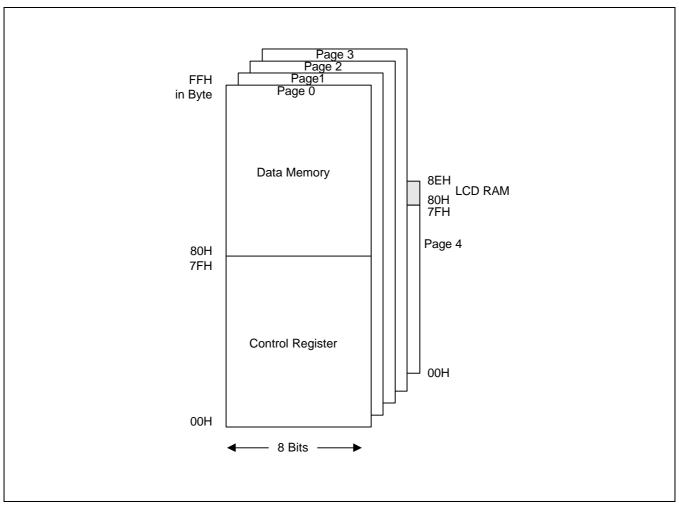

The total data memory address space is 64K bytes, addressed by *DA[15:0]*, and divided into 256 pages, Each page consists of 256 bytes as shown below.

Figure 2-5. Data Memory Map

The data memory page is indexed by SPR and IDH. In data memory index addressing mode, 16-bit data memory address is composed of two 8-bit SPRs, IDH[7:0] and IDL0[7:0] (or IDH[7:0] and IDL1[7:0]). IDH[7:0] points to a page index, and IDL0[7:0] (or IDL1[7:0]) represents the page offset. In data memory direct addressing mode, an 8-bit direct address, adr[7:0], specifies the offset of the page pointed to by IDH[7:0] (See the details for direct addressing mode in the instruction sections). Unlike the program memory organization, data memory address does *not* wrap around. In other words, data memory index addressing with modification performs an addition or a subtraction operation on the whole 16-bit address of IDH[7:0] and IDL0[7:0] (or IDL1[7:0]) and updates IDH[7:0] and IDL0[7:0] (or IDL1[7:0]) accordingly. Suppose IDH[7:0] is 0FH and IDL0[7:0] is FCH and the modification on the index registers, IDH[7:0] and IDL0[7:0], is increment by 5H, then, after the modification (i.e., 0FFCH + 5 = 1001H), IDH[7:0] and IDL0[7:0] become 10H and 01H, respectively.

The S3CK215 has 1024 bytes of data register address from 0080H to 047FH. The area from 0000H to 007FH is for peripheral control, and LCD RAM area is from 0480H to 008EH.

Figure 2-6. Data Memory Map

NOTES

# 3 REGISTERS

# OVERVIEW

The registers of CalmRISC are grouped into 2 parts: general purpose registers and special purpose registers.

| Regi                                            | sters           | Mnemonics                                              | Description                                          | Reset Value |

|-------------------------------------------------|-----------------|--------------------------------------------------------|------------------------------------------------------|-------------|

| General Purpose                                 |                 | R0                                                     | General Register 0                                   | Unknown     |

| Register                                        | Registers (GPR) |                                                        | General Register 1                                   | Unknown     |

|                                                 |                 | R2                                                     | General Register 2                                   | Unknown     |

|                                                 |                 | R3                                                     | General Register 3                                   | Unknown     |

| Special Purpose                                 | Group 0 (SPR0)  | IDL0                                                   | Lower Byte of Index Register 0                       | Unknown     |

| Registers (SPR)                                 | Registers (SPR) |                                                        | Lower Byte of Index Register 1                       | Unknown     |

|                                                 |                 | IDH                                                    | Higher Byte of Index Register                        | Unknown     |

|                                                 |                 | SR0                                                    | Status Register 0                                    | 00H         |

| ILH Instruction<br>Higher By<br>ILL Instruction |                 | Instruction Pointer Link Register for<br>Extended Byte | Unknown                                              |             |

|                                                 |                 | ILH                                                    | Instruction Pointer Link Register for<br>Higher Byte | Unknown     |

|                                                 |                 | ILL                                                    | Instruction Pointer Link Register for Lower Byte     | Unknown     |

|                                                 |                 | SR1                                                    | Status Register 1                                    | Unknown     |

#### Table 3-1. General and Special Purpose Registers

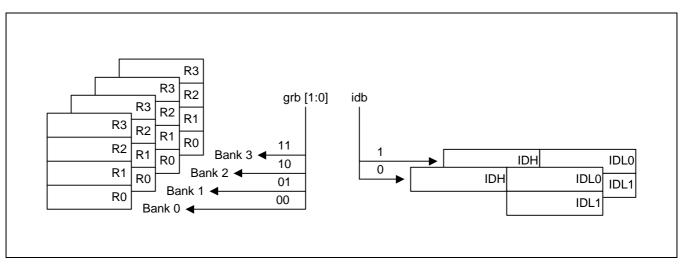

GPR's can be used in most instructions such as ALU instructions, stack instructions, load instructions, *etc* (See the instruction set sections). From the programming standpoint, they have almost no restriction whatsoever. CalmRISC has 4 banks of GPR's and each bank has 4 registers, R0, R1, R2, and R3. Hence, 16 GPR's in total are available. The GPR bank switching can be done by setting an appropriate value in SR0[4:3] (See SR0 for details). The ALU operations between GPR's from different banks are *not* allowed.

SPR's are designed for their own dedicated purposes. They have some restrictions in terms of instructions that can access them. For example, direct ALU operations cannot be performed on SPR's. However, data transfers between a GPR and an SPR are allowed and stack operations with SPR's are also possible (See the instruction sections for details).

#### INDEX REGISTERS: IDH, IDL0 AND IDL1

IDH in concatenation with IDL0 (or IDL1) forms a 16-bit data memory address. Note that CalmRISC's data memory address space is 64 K byte (addressable by 16-bit addresses). Basically, IDH points to a page index and IDL0 (or IDL1) corresponds to an offset of the page. Like GPR's, the index registers are 2-way banked. There are 2 banks in total, each of which has its own index registers, IDH, IDL0 and IDL1. The banks of index registers can be switched by setting an appropriate value in SR0[2] (See SR0 for details). Normally, programmers can reserve an index register pair, IDH and IDL0 (or IDL1), for software stack operations.

#### LINK REGISTERS: ILX, ILH AND ILL

The link registers are specially designed for link-and-branch instructions (See LNK and LRET instructions in the instruction sections for details). When an LNK instruction is executed, the current PC[19:0] is saved into ILX, ILH and ILL registers, i.e., PC[19:16] into ILX[3:0], PC[15:8] into ILH [7:0], and PC[7:0] into ILL[7:0], respectively. When an LRET instruction is executed, the return PC value is recovered from ILX, ILH, and ILL, i.e., ILX[3:0] into PC[19:16], ILH[7:0] into PC[15:8] and ILL[7:0] into PC[7:0], respectively. These registers are used to access program memory by LDC/LDC+ instructions. When an LDC or LDC+ instruction is executed, the (code) data residing at the program address specified by ILX:ILH:ILL will be read into TBH:TBL. LDC+ also increments ILL after accessing the program memory.

There is a special core input pin signal, nP64KW, which is reserved for indicating that the program memory address space is only 64 K word. By grounding the signal pin to zero, the upper 4 bits of PC, PC[19:16], is deactivated and therefore the upper 4 bits, PA[19:16], of the program memory address signals from CalmRISC core are also deactivated. By doing so, power consumption due to manipulating the upper 4 bits of PC can be totally eliminated (See the core pin description section for details). From the programmer's standpoint, when nP64KW is tied to the ground level, then PC[19:16] is not saved into ILX for LNK instructions and ILX is not read back into PC[19:16] for LRET instructions. Therefore, ILX is totally unused in LNK and LRET instructions when nP64KW = 0.

#### **STATUS REGISTER 0: SR0**

SR0 is mainly reserved for system control functions and each bit of SR0 has its own dedicated function.

| Flag Name | Bit | Description                                     |

|-----------|-----|-------------------------------------------------|

| eid       | 0   | Data memory page selection in direct addressing |

| ie        | 1   | Global interrupt enable                         |

| idb       | 2   | Index register banking selection                |

| grb[1:0]  | 4,3 | GPR bank selection                              |

| exe       | 5   | Stack overflow/underflow exception enable       |

| ie0       | 6   | Interrupt 0 enable                              |

| ie1       | 7   | Interrupt 1 enable                              |

Table 3-2. Status Register 0 configuration

SR0[0] (or eid) selects which page index is used in direct addressing. If eid = 0, then page 0 (page index = 0) is used. Otherwise (eid = 1), IDH of the current index register bank is used for page index. SR0[1] (or ie) is the global interrupt enable flag. As explained in the interrupt/exception section, CalmRISC has 3 interrupt sources (non-maskable interrupt, interrupt 0, and interrupt 1) and 1 stack exception. Both interrupt 0 and interrupt 1 are masked by setting SR0[1] to 0 (i.e., ie = 0). When an interrupt is serviced, the global interrupt enable flag ie is automatically cleared. The execution of an IRET instruction (return from an interrupt service routine) automatically sets ie = 1. SR0[2] (or idb) and SR0[4:3] (or grb[1:0]) selects an appropriate bank for index registers and GPR's, respectively as shown below:

Figure 3-1. Bank Selection by Setting of GRB Bits and IDB Bit

SR0[5] (or exe) enables the stack exception, that is, the stack overflow/underflow exception. If exe = 0, the stack exception is disabled. The stack exception can be used for program debugging in the software development stage. SR0[6] (or ie0) and SR0[7] (or ie1) are enabled, by setting them to 1. Even though ie0 or ie1 are enabled, the interrupts are ignored (not serviced) if the global interrupt enable flag ie is set to 0.

#### **STATUS REGISTER 1: SR1**

SR1 is the register for status flags such as ALU execution flag and stack full flag.

| Flag Name | Bit   | Description     |

|-----------|-------|-----------------|

| С         | 0     | Carry flag      |

| V         | 1     | Overflow flag   |

| Z         | 2     | Zero flag       |

| N         | 3     | Negative flag   |

| SF        | 4     | Stack Full flag |

| -         | 5,6,7 | Reserved        |

#### Table 3-3. Status Register 1: SR1

SR1[0] (or C) is the carry flag of ALU executions. SR1[1] (or V) is the overflow flag of ALU executions. It is set to 1 if and only if the carry-in into the 8-th bit position of addition/subtraction differs from the carry-out from the 8-th bit position. SR1[2] (or Z) is the zero flag, which is set to 1 if and only if the ALU result is zero. SR1[3] (or N) is the negative flag. Basically, the most significant bit (MSB) of ALU results becomes N flag. Note a load instruction into a GPR is considered an ALU instruction. However, if an ALU instruction touches the overflow flag (V) like ADD, SUB, CP, *etc*, N flag is updated as exclusive-OR of V and the MSB of the ALU result. This implies that even if an ALU operation results in overflow, N flag is still valid. SR1[4] (or SF) is the stack overflow flag. It is set when the hardware stack is overflowed or under flowed. Programmers can check if the hardware stack has any abnormalities by the stack exception or testing if SF is set (See the hardware stack section for great details).

#### NOTE

When an interrupt occurs, SR0 and SR1 are not saved by hardware, so SR0, and SR1 register values must be saved by software.

# 4 MEMORY MAP

# OVERVIEW

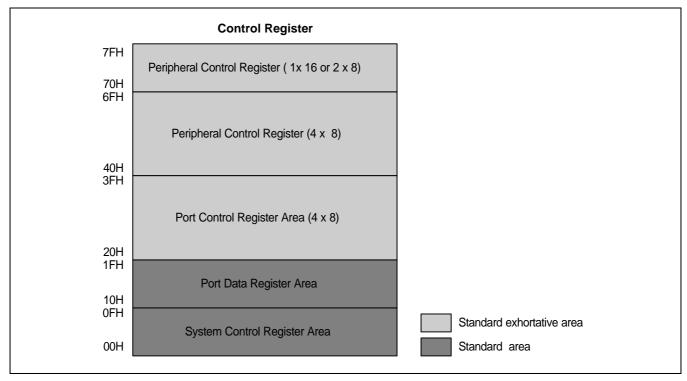

To support the control of peripheral hardware, the address for peripheral control registers are memory-mapped to page 0 of the RAM. Memory mapping lets you use a mnemonic as the operand of an instruction in place of the specific memory location.

In this section, detailed descriptions of the control registers are presented in an easy-to-read format. You can use this section as a quick-reference source when writing application programs.

This memory area can be accessed with the whole method of data memory access.

- If SR0 bit 0 is "0" then the accessed register area is always page 0.

- If SR0 bit 0 is "1" then the accessed register page is controlled by the proper IDH register's value.

So if you want to access the memory map area, clear the SR0.0 and use the direct addressing mode. This method is used for most cases.

This control register is divided into five areas. Here, the system control register area is same in every device.

Figure 4-1. Memory Map Area

| Register Name                   | Mnemonic                 | Decimal | Hex | Reset | R/W |

|---------------------------------|--------------------------|---------|-----|-------|-----|

| Loc                             | ations 16H-1FH are not r | mapped  |     |       |     |

| Port 5 data register            | P5                       | 21      | 15H | 00H   | R/W |

| Port 4 data register            | P4                       | 20      | 14H | 00H   | R/W |

| Port 3 data register            | P3                       | 19      | 13H | 00H   | R/W |

| Port 2 data register            | P2                       | 18      | 12H | 00H   | R/W |

| Port 1 data register            | P1                       | 17      | 11H | 00H   | R/W |

| Port 0 data register            | P0                       | 16      | 10H | 00H   | R/W |

| Loc                             | ations 0EH-0FH are not r | mapped. |     |       |     |

| Watchdog timer control register | WDTCON                   | 13      | 0DH | X0H   | R/W |

| Basic timer counter             | BTCNT                    | 12      | 0CH | 00H   | R   |

| Interrupt ID register 1         | lIR1                     | 11      | 0BH | _     | R/W |

| Interrupt priority register 1   | IPR1                     | 10      | 0AH | _     | R/W |

| Interrupt mask register 1       | IMR1                     | 9       | 09H | 00H   | R/W |

| Interrupt request register 1    | IRQ1                     | 8       | 08H | _     | R   |

| Interrupt ID register 0         | liR0                     | 7       | 07H | _     | R/W |

| Interrupt priority register 0   | IPR0                     | 6       | 06H | _     | R/W |

| Interrupt mask register 0       | IMR0                     | 5       | 05H | 00H   | R/W |

| Interrupt request register 0    | IRQ0                     | 4       | 04H | _     | R   |

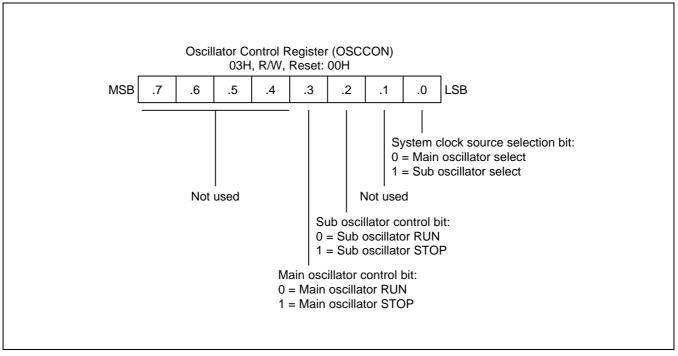

| Oscillator control register     | OSCCON                   | 3       | 03H | 00H   | R/W |

| Power control register          | PCON                     | 2       | 02H | 04H   | R/W |

| Loc                             | ations 00H-01H are not n | napped. |     |       |     |

Table 4-1. Registers

#### NOTES:

1. '-' means undefined.

2. If you want to clear the bit of IRQx, then write the number that you want to clear to IIRx. For example, when clear IRQ0.4 then LD Rx, #04H and LD IIR0, Rx.

| Register Name                       | Mnemonic                | Decimal | Hex | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W |  |  |

|-------------------------------------|-------------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Timer 2 counter                     | T2CNT                   | 82      | 52H | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R   |  |  |

| Timer 2 data register               | T2DATA                  | 81      | 51H | FFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

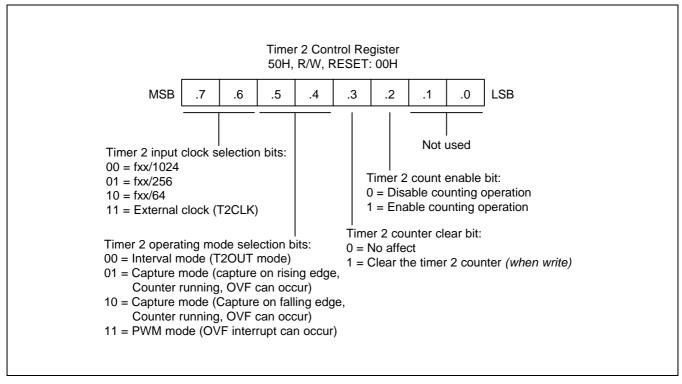

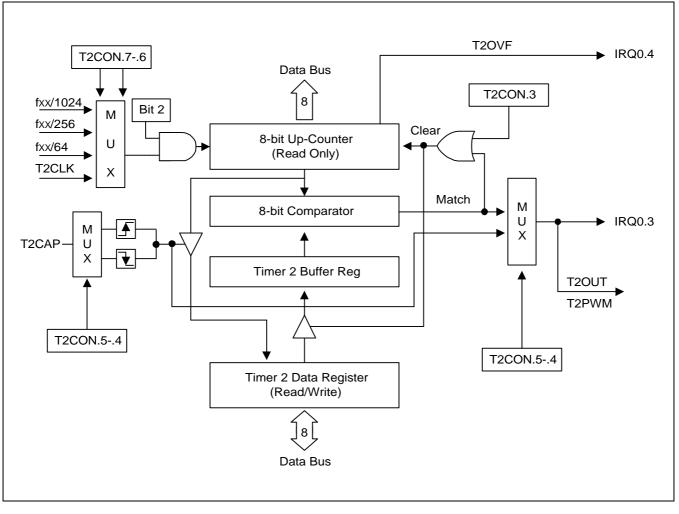

| Timer 2 control register            | T2CON                   | 80      | 50H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | tions 4DH-4FH are not r | napped  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

| Timer 1 counter (low byte)          | T1CNTL                  | 76      | 4CH | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R   |  |  |

| Timer 1 counter (high byte)         | T1CNTH                  | 75      | 4BH | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R   |  |  |

| Timer 1 data register (low byte)    | T1DATAL                 | 74      | 4AH | FFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Timer 1 data register (high byte)   | T1DATAH                 | 73      | 49H | FFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

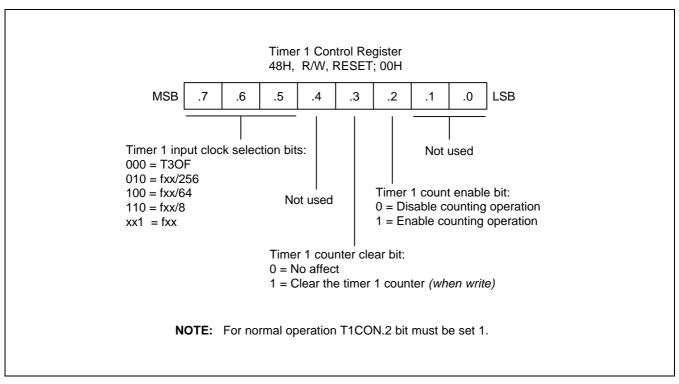

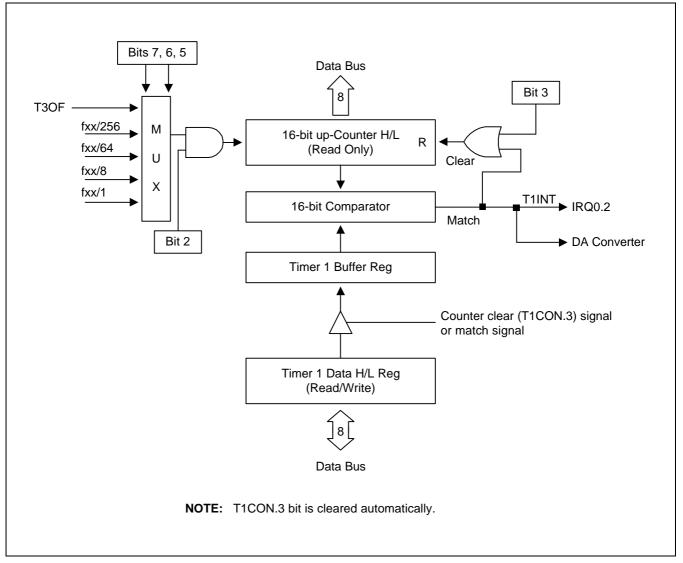

| Timer 1 count register              | T1CON                   | 72      | 48H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | tions 45H-47H are not n | napped  |     | - R<br>- R<br>FFH R/W<br>FFH R/W<br>00H R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |  |  |

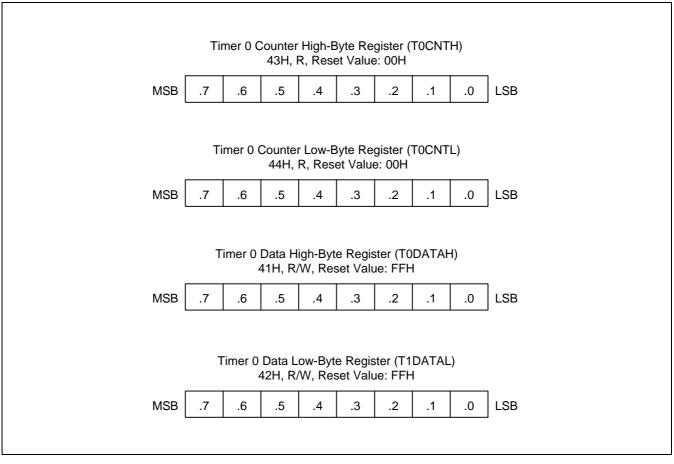

| Timer 0 counter (low byte)          | T0CNTL                  | 68      | 44H | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R   |  |  |

| Timer 0 counter (high byte)         | TOCNTH                  | 67      | 43H | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R   |  |  |

| Timer 0 data register (low byte)    | TODATAL                 | 66      | 42H | FFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Timer 0 data register (high byte)   | TODATAH                 | 65      | 41H | FFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Timer 0 count register              | TOCON                   | 64      | 40H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | ation 36H-3FH are not m | napped  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

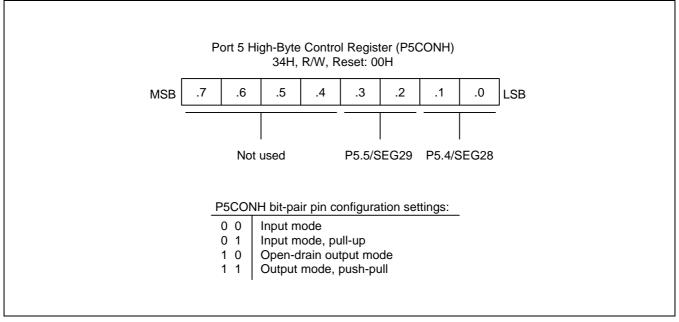

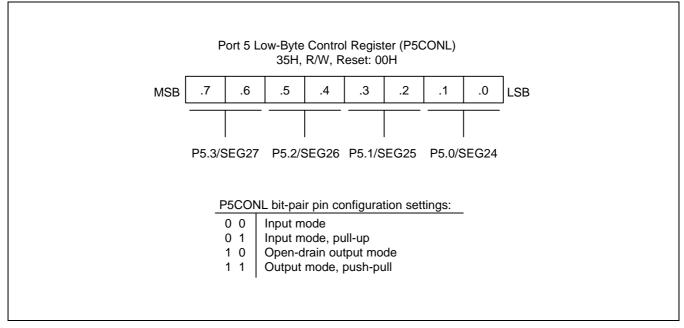

| Port 5 control register (low byte)  | P5CONL                  | 53      | 35H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Port 5 control register (high byte) | P5CONH                  | 52      | 34H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | ation 32H-33H are not m | napped  |     | 00H         R/W           -         R           -         R           FFH         R/W           FFH         R/W           00H         R/W |     |  |  |

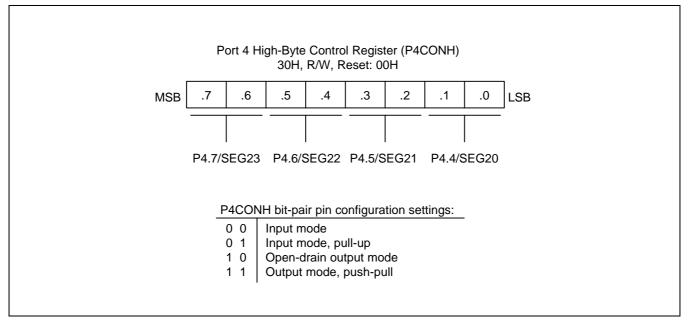

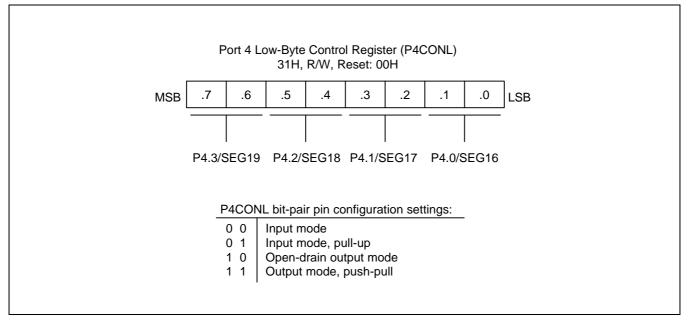

| Port 4 control register (low byte)  | P4CONL                  | 49      | 31H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

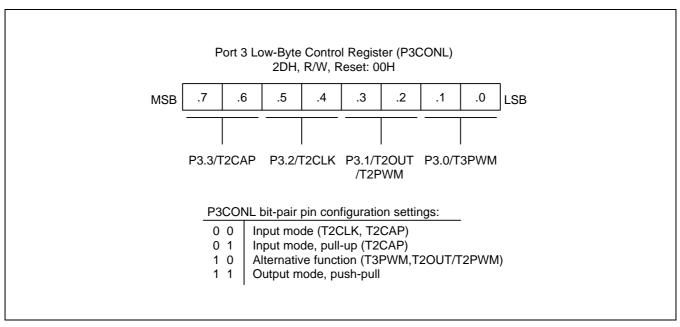

| Port 4 control register (high byte) | P4CONH                  | 48      | 30H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | tions 2EH-2FH are not r | napped  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

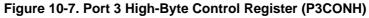

| Port 3 control register (low byte)  | P3CONL                  | 45      | 2DH | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

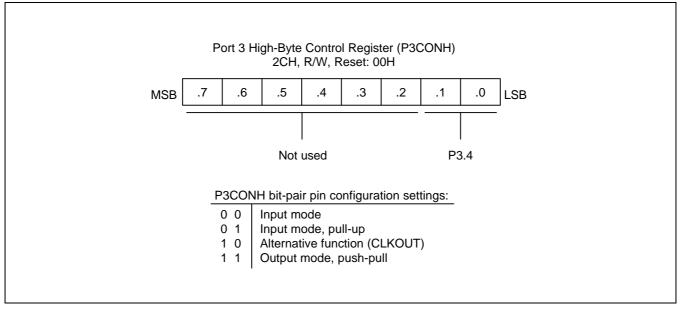

| Port 3 control register (high byte) | P3CONH                  | 44      | 2CH | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | tions 2AH-2BH are not r | mapped  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

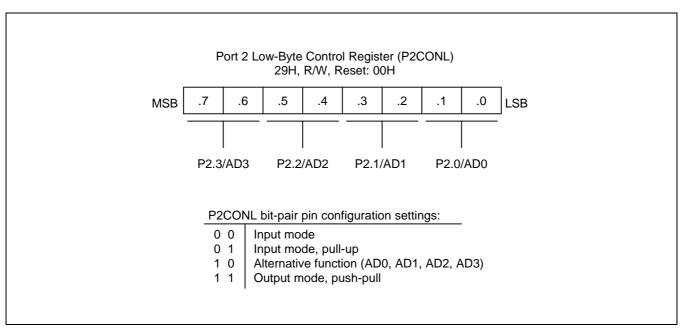

| Port 2 control register (low byte)  | P2CONL                  | 41      | 29H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

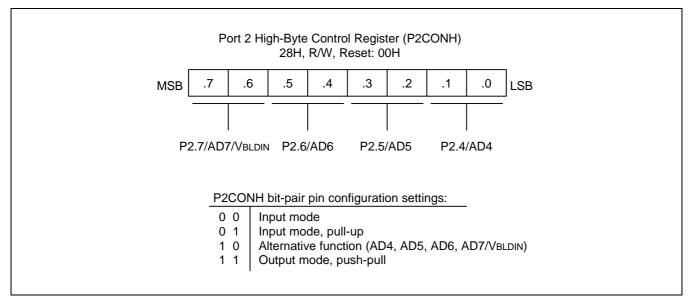

| Port 2 control register (high byte) | P2CONH                  | 40      | 28H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

| Loca                                | tions 24H-27H are not n | napped  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

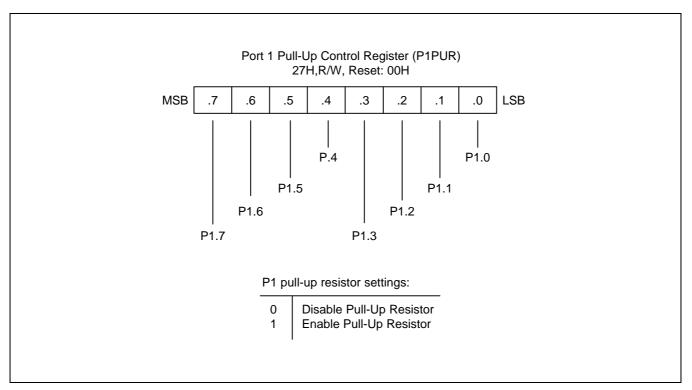

| Port 1 pull-up register             | P1PUR                   | 35      | 23H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

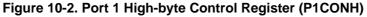

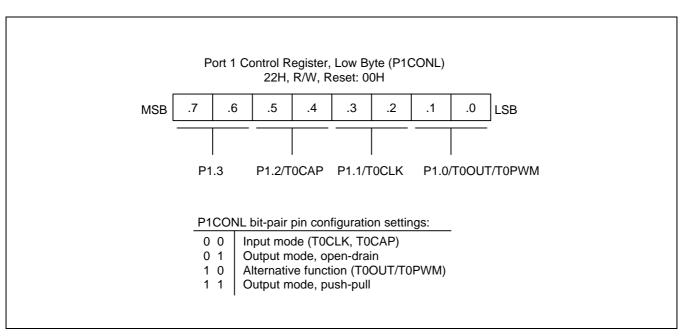

| Port 1 control register (low byte)  | P1CONL                  | 34      | 22H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

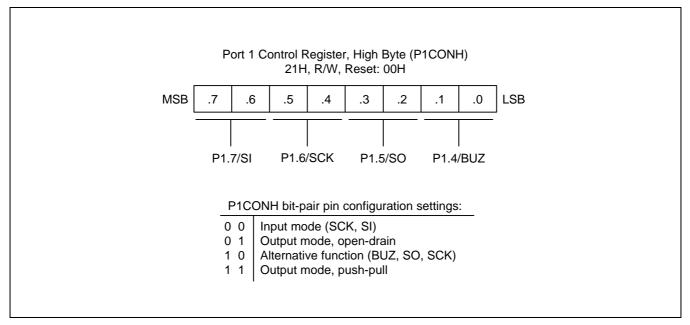

| Port 1 control register (high byte) | P1CONH                  | 33      | 21H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

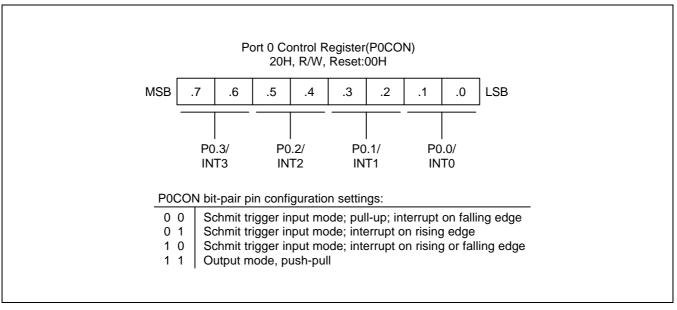

| Port 0 control register             | POCON                   | 32      | 20H | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W |  |  |

# Table 4-1. Registers (continued)

| Register Name                             | Mnemonic             | Decimal | Hex | Reset | R/W |

|-------------------------------------------|----------------------|---------|-----|-------|-----|

| Location                                  | s 7DH-7FH are not    | mapped  |     |       |     |

| Multiplication result (low byte)          | MRL                  | 124     | 7CH | 00H   | R   |

| Multiplication result (high byte)         | MRH                  | 123     | 7BH | 00H   | R   |

| Multiplier Y input register               | MYINP                | 122     | 7AH | 00H   | R/W |

| Multiplier X input register               | MXINP                | 121     | 79H | 00H   | R/W |

| Multiplier control register               | MULCON               | 120     | 78H | 00H   | R/W |

| OP amp control register                   | OPCON                | 119     | 77H | 00H   | R/W |

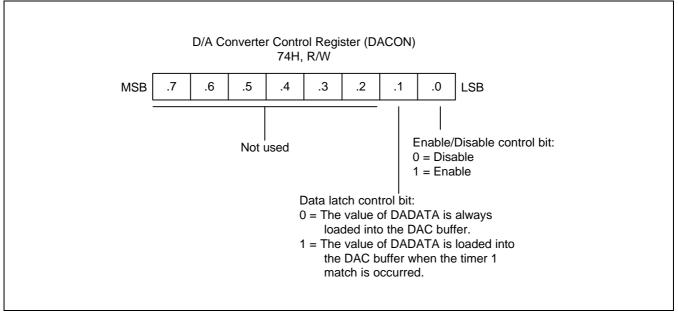

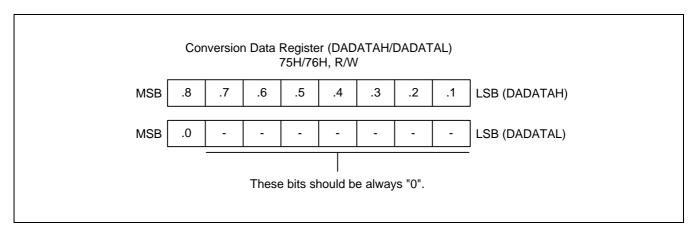

| D/A converter data register (low byte)    | DADATAL              | 118     | 76H | 00H   | R/W |

| D/A converter data register (high byte)   | DADATAH              | 117     | 75H | 00H   | R/W |

| D/A converter control register            | DACON                | 116     | 74H | 00H   | R/W |

| Loca                                      | tions 73H is not map | oped    |     |       |     |

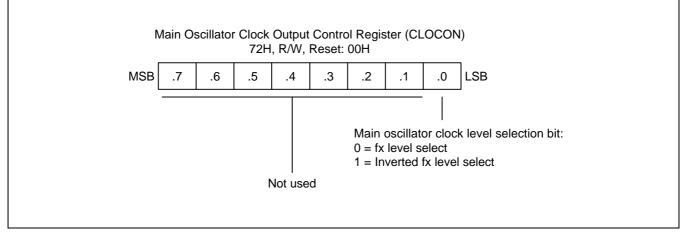

| Main system clock output control register | CLOCON               | 114     | 72H | 00H   | R/W |

| Battery level detector register           | BLDCON               | 113     | 71H | 00H   | R/W |

| Watch timer control register              | WTCON                | 112     | 70H | 00H   | R/W |

| Locatio                                   | n 62H-6FH are not r  | napped  |     |       |     |

| LCD mode register                         | LMOD                 | 97      | 61H | 00H   | R/W |

| LCD control register                      | LCON                 | 96      | 60H | 00H   | R/W |

| Loca                                      | ation 5FH is not map | ped     |     |       |     |

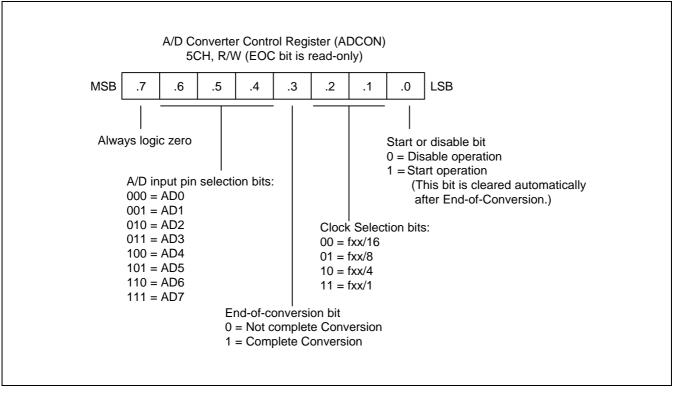

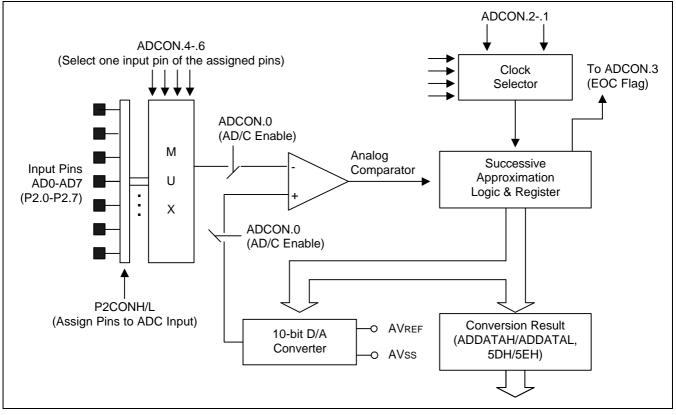

| A/D converter data register (low byte)    | ADDATAL              | 94      | 5EH | -     | R   |

| A/D converter data register (high byte)   | ADDATAH              | 93      | 5DH | -     | R   |

| A/D converter control register            | ADCON                | 92      | 5CH | 00H   | R/W |

| Loca                                      | tions 5BH is not map | pped    |     |       |     |

| Serial I/O data register                  | SIODATA              | 90      | 5AH | 00H   | R/W |

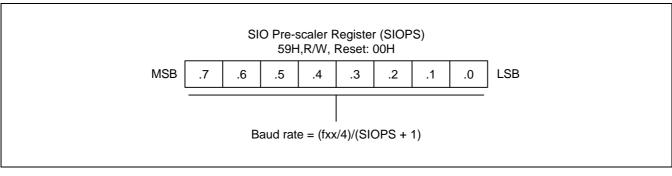

| Serial I/O pre-scale register             | SIOPS                | 89      | 59H | 00H   | R/W |

| Serial I/O control register               | SIOCON               | 88      | 58H | 00H   | R/W |

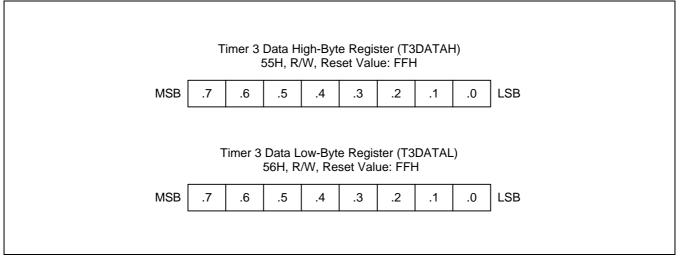

| Timer 3 counter                           | T3CNT                | 87      | 57H | _     | R   |

| Timer 3 data register (low byte)          | T3DATAL              | 86      | 56H | FFH   | R/W |

| Timer 3 data register (high byte)         | T3DATAH              | 85      | 55H | FFH   | R/W |

| Timer 3 control register                  | T3CON                | 84      | 54H | 00H   | R/W |

| Loca                                      | tions 53H is not map | oped    |     |       |     |

Table 4-1. Registers (continued)

# 5 HARDWARE STACK

# OVERVIEW

The hardware stack in CalmRISC has two usages:

- To save and restore the return PC[19:0] on LCALL, CALLS, RET, and IRET instructions.

- Temporary storage space for registers on PUSH and POP instructions.

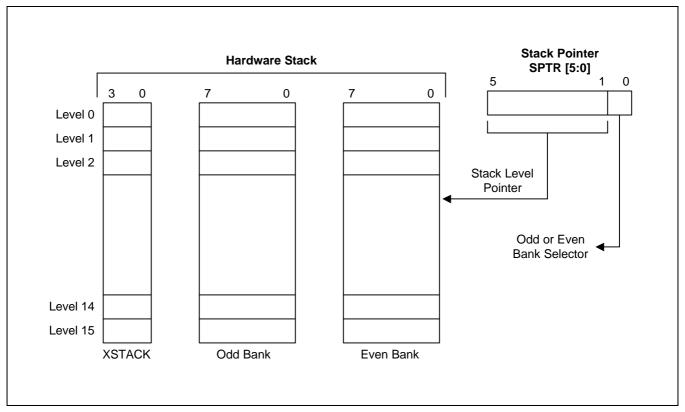

When PC[19:0] is saved into or restored from the hardware stack, the access should be 20 bits wide. On the other hand, when a register is pushed into or popped from the hardware stack, the access should be 8 bits wide. Hence, to maximize the efficiency of the stack usage, the hardware stack is divided into 3 parts: the extended stack bank (XSTACK, 4-bits wide), the odd bank (8-bits wide), and the even bank (8-bits wide).

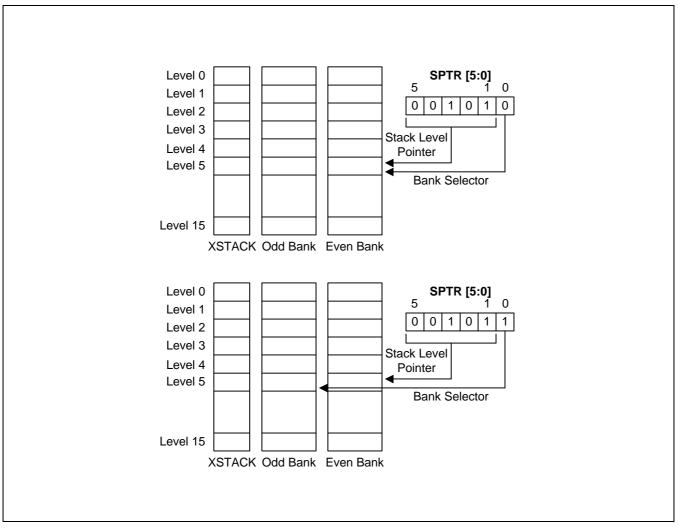

Figure 5-1. Hardware Stack

The top of the stack (TOS) is pointed to by a stack pointer, called **sptr[5:0]**. The upper 5 bits of the stack pointer, sptr[5:1], points to the stack level into which either PC[19:0] or a register is saved. For example, if sptr[5:1] is 5H or TOS is 5, then level 5 of XSTACK is empty and either level 5 of the odd bank or level 5 of the even bank is empty. In fact, sptr[0], the stack bank selection bit, indicates which bank(s) is empty. If sptr[0] = 0, both level 5 of the even and the odd banks are empty. On the other hand, if sptr[0] = 1, level 5 of the odd bank is empty, but level 5 of the even bank is occupied. This situation is well illustrated in the figure below.

Figure 5-2. Even and Odd Bank Selection Example

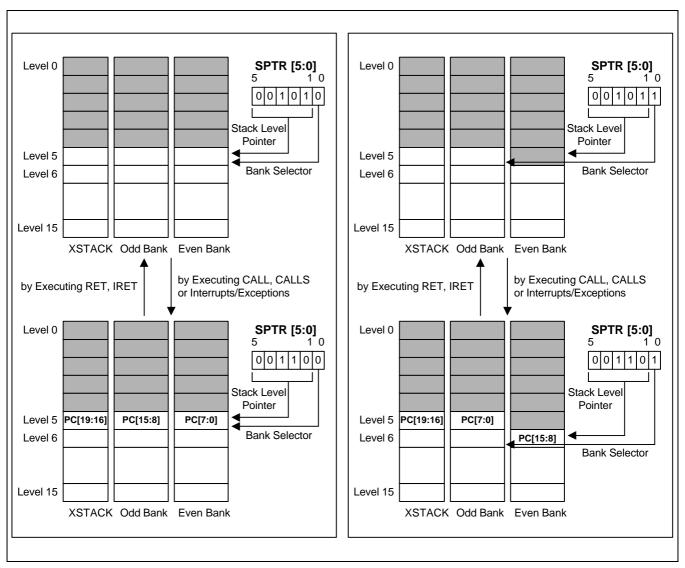

As can be seen in the above example, sptr[5:1] is used as the hardware stack pointer when PC[19:0] is pushed or popped and sptr[5:0] as the hardware stack pointer when a register is pushed or popped. Note that XSTACK is used only for storing and retrieving PC[19:16]. Let us consider the cases where PC[19:0] is pushed into the hardware stack (by executing LCALL/CALLS instructions or by interrupts/exceptions being served) or is retrieved from the hardware stack (by executing RET/IRET instructions). Regardless of the stack bank selection bit (sptr[0]), TOS of the even bank and the odd bank store or return PC[7:0] or PC[15:8], respectively. This is illustrated in the following figures.

Figure 5-3. Stack Operation with PC [19:0]

As can be seen in the figures, when stack operations with PC[19:0] are performed, the stack level pointer sptr[5:1] (*not* sptr[5:0]) is either incremented by 1 (when PC[19:0] is pushed into the stack) or decremented by 1 (when PC[19:0] is popped from the stack). The stack bank selection bit (sptr[0]) is unchanged. If a CalmRISC core input signal *nP64KW* is 0, which signifies that only PC[15:0] is meaningful, then any access to XSTACK is totally deactivated from the stack operations with PC. Therefore, XSTACK has no meaning when the input pin signal, *nP64KW*, is tied to 0. In that case, XSTACK doesn't have to even exist. As a matter of fact, XSTACK is not included in CalmRISC core itself and it is interfaced through some specially reserved core pin signals (*nPUSH, nSTACK, XHSI[3:0], XSHO[3:0]*), if the program address space is more than 64 K words (See the core pin signal section for details).

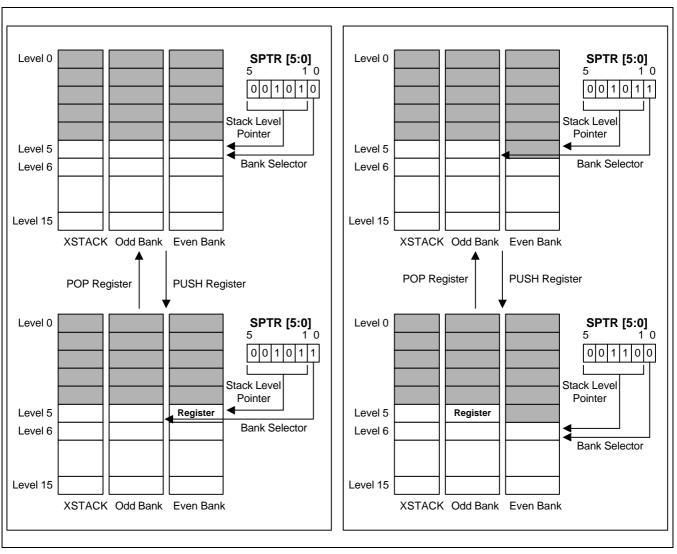

With regards to stack operations with registers, a similar argument can be made. The only difference is that the data written into or read from the stack are a byte. Hence, the even bank and the odd bank are accessed alternately as shown below.

Figure 5-4. Stack Operation with Registers

When the bank selection bit (sptr[0]) is 0, then the register is pushed into the even bank and the bank selection bit is set to 1. In this case, the stack level pointer is unchanged. When the bank selection bit (sptr[0]) is 1, then the register is pushed into the odd bank, the bank selection bit is set to 0, and the stack level pointer is incremented by 1. Unlike the push operations of PC[19:0], any data are not written into XSTACK in the register push operations. This is illustrated in the example figures. When a register is pushed into the stack, sptr[5:0] is incremented by 1 (*not* the stack level pointer sptr[5:1]). The register pop operations are the reverse processes of the register push operations. When a register is popped out of the stack, sptr[5:0] is decremented by 1 (*not* the stack level pointer sptr[5:1]).

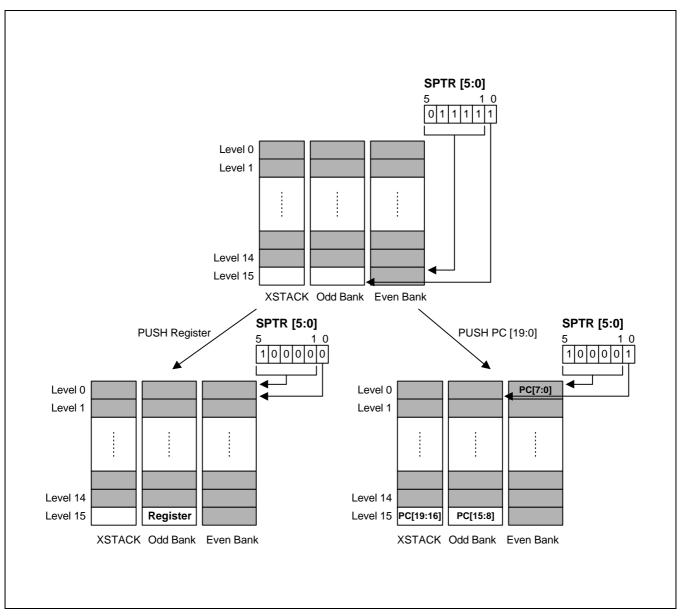

Hardware stack overflow/underflow happens when the MSB of the stack level pointer, sptr[5], is 1. This is obvious from the fact that the hardware stack has only 16 levels and the following relationship holds for the stack level pointer in a normal case.

Suppose the stack level pointer sptr[5:1] = 15 (or 01111B in binary format) and the bank selection bit sptr[0] = 1. Here if either PC[19:0] or a register is pushed, the stack level pointer is incremented by 1. Therefore, sptr[5:1] = 16 (or 10000B in binary format) and sptr[5] = 1, which implies that the stack is overflowed. The situation is depicted in the following.

Figure 5-5. Stack Overflow

The first overflow happens due to a register push operation. As explained earlier, a register push operation increments sptr[5:0] (not sptr[5:1]), which results in sptr[5] = 1, sptr[4:1] = 0 and sptr[0] = 0. As indicated by sptr[5] = 1, an overflow happens. Note that this overflow doesn't overwrite any data in the stack. On the other hand, when PC[19:0] is pushed, sptr[5:1] is incremented by 1 instead of sptr[5:0], and as expected, an overflow results. Unlike the first overflow, PC[7:0] is pushed into level 0 of the even bank and the data that has been there before the push operation is *overwritten*. A similar argument can be made about stack underflows. Note that any stack operation, which causes the stack to overflow or underflow, doesn't necessarily mean that any data in the stack are lost, as is observed in the first example.

In SR1, there is a status flag, SF (Stack Full Flag), which is exactly the same as sptr[5]. In other words, the value of sptr[5] can be checked by reading SF (or SR1[4]). SF is not a sticky flag in the sense that if there was a stack overflow/underflow but any following stack access instructions clear sptr[5] to 0, then SF = 0 and programmers cannot tell whether there was a stack overflow/underflow by reading SF. For example, if a program pushes a register 64 times in a row, sptr[5:0] is exactly the same as sptr[5:0] before the push sequence. Therefore, special attention should be paid.

Another mechanism to detect a stack overflow/underflow is through a stack exception. A stack exception happens only when the execution of any stack access instruction results in SF = 1 (or sptr[5] = 1). Suppose a register push operation makes SF = 1 (the SF value before the push operation doesn't matter). Then the stack exception due to the push operation is immediately generated and served If the stack exception enable flag (exe of SR0) is 1. If the stack exception enable flag is 0, then the generated interrupt is not served but pending. Sometime later when the stack exception enable flag is set to 1, the pending exception request is served even if SF = 0. More details are available in the stack exception section.

# 6 EXCEPTIONS

## OVERVIEW

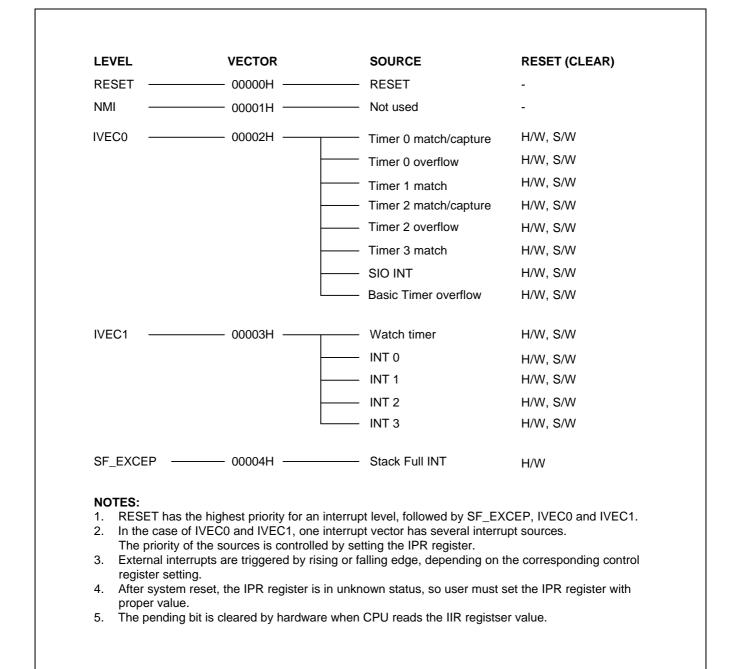

Exceptions in CalmRISC are listed in the table below. Exception handling routines, residing at the given addresses in the table, are invoked when the corresponding exception occurs. The start address of each exception routine is specified by concatenation 0H (leading 4 bits of 0) and the 16-bit data in the exception vector listed in the table. For example, the interrupt service routine for IRQ[0] starts from 0H:PM[00002H]. Note that ":"means concatenation and PM[\*] stands for the 16-bit content at the address \* of the program memory. Aside from the exception due to reset release, the current PC is pushed in the stack on an exception. When an exception is executed due to IRQ[1:0]/IEXP, the global interrupt enable flag, ie bit (SR0[1]), is set to 0, whereas ie is set to 1 when IRET or an instruction that explicitly sets ie is executed.

| Name   | Address | Priority | Description                                                         |

|--------|---------|----------|---------------------------------------------------------------------|

| Reset  | 00000H  | 1st      | Exception due to reset release.                                     |

| -      | 00001H  | —        | Reserved                                                            |

| IRQ[0] | 00002H  | 3rd      | Exception due to <i>nIRQ[0]</i> signal. Maskable by setting ie/ie0. |

| IRQ[1] | 00003H  | 4th      | Exception due to <i>nIRQ[1]</i> signal. Maskable by setting ie/ie1. |

| IEXP   | 00004H  | 2nd      | Exception due to stack full. Maskable by setting exe.               |

| -      | 00005H  | —        | Reserved.                                                           |

| -      | 00006H  | —        | Reserved.                                                           |

| _      | 00007H  | _        | Reserved.                                                           |

#### Table 6-1. Exceptions

**NOTE:** Break mode due to BKREQ has a higher priority than all the exceptions above. That is, when BKREQ is active, even the exception due to reset release is not executed.

## HARDWARE RESET

When Hardware Reset is active (the reset input signal pin nRES = 0), the control pins in the CalmRISC core are initialized to be disabled, and SR0 and sptr (the hardware stack pointer) are initialized to be 0. Additionally, the interrupt sensing block is cleared. When Hardware Reset is released (nRES = 1), the reset exception is executed by loading the JP instruction in IR (Instruction Register) and 0h:0000h in PC. Therefore, when Hardware Reset is released, the "JP {0h:PM[00000h]}" instruction is executed.

## **IRQ[0] EXCEPTION**

When a core input signal *nIRQ[0]* is low, SR0[6] (ie0) is high, and SR0[1] (ie) is high, IRQ[0] exception is generated, and this will load the CALL instruction in IR (Instruction Register) and 0h:0002h in PC. Therefore, on an IRQ[0] exception, the "CALL {0h:PM[00002h]}" instruction is executed. When the IRQ[0] exception is executed, SR0[1] (ie) is set to 0.

## **IRQ[1] EXCEPTION (LEVEL-SENSITIVE)**

When a core input signal *nIRQ[1]* is low, SR0[7] (ie1) is high, and SR0[1] (ie) is high, IRQ[1] exception is generated, and this will load the CALL instruction in IR (Instruction Register) and 0h:0003h in PC. Therefore, on an IRQ[1] exception, the "CALL {0h:PM[00003h]}" instruction is executed. When the IRQ[1] exception is executed, SR0[1] (ie) is set to 0.

## HARDWARE STACK FULL EXCEPTION

A Stack Full exception occurs when a stack operation is performed and as a result of the stack operation sptr[5] (SF) is set to 1. If the stack exception enable bit, exe (SR0[5]), is 1, the Stack Full exception is served. One exception to this rule is when nNMI causes a stack operation that sets sptr[5] (SF), since it has higher priority.

Handling a Stack Full exception may cause another Stack Full exception. In this case, the new exception is ignored. On a Stack Full exception, the CALL instruction is loaded in IR (Instruction Register) and 0h:0004h in PC. Therefore, when the Stack Full exception is activated, the "CALL {0h:PM[00004h]}" instruction is executed. When the exception is executed, SR0[1] (ie) is set to 0.

## **BREAK EXCEPTION**

Break exception is reserved only for an in-circuit debugger. When a core input signal, *BKREQ*, is high, the CalmRISC core is halted or in the break mode, until *BKREQ* is deactivated. Another way to drive the CalmRISC core into the break mode is by executing a break instruction, BREAK. When BREAK is fetched, it is decoded in the fetch cycle (IF stage) and the CalmRISC core output signal *nBKACK* is generated in the second cycle (ID/MEM stage). An in-circuit debugger generates *BKREQ* active by monitoring *nBKACK* to be active. BREAK instruction is exactly the same as the NOP (no operation) instruction except that it does not increase the program counter and activates nBKACK in the second cycle (or ID/MEM stage of the pipeline). There, once BREAK is encountered in the program execution, it falls into a deadlock. BREAK instruction is reserved for in-circuit debuggers only, so it should not be used in user programs.

## **EXCEPTIONS (or INTERRUPTS)**

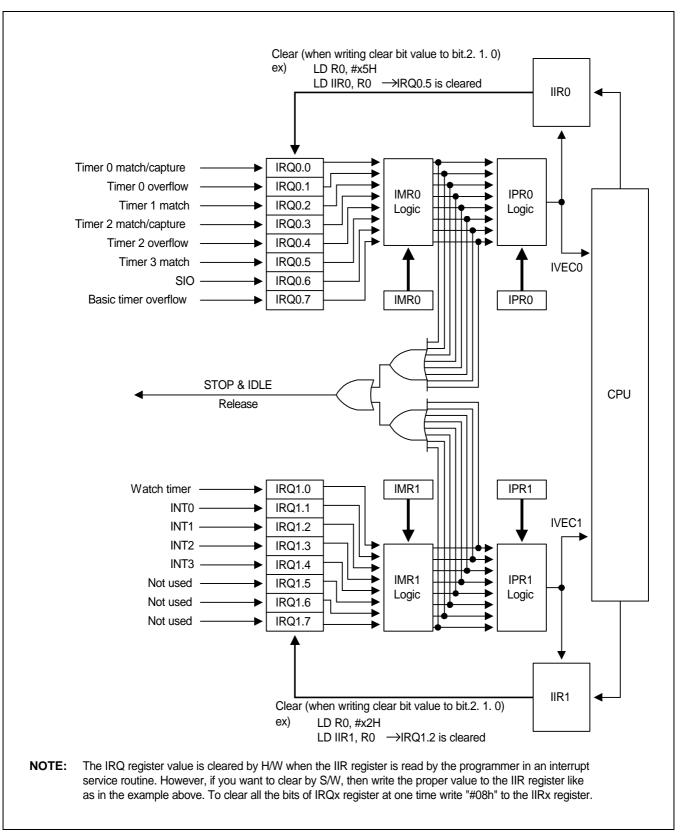

#### Figure 6-1. Interrupt Structure

Figure 6-2. Interrupt Structure

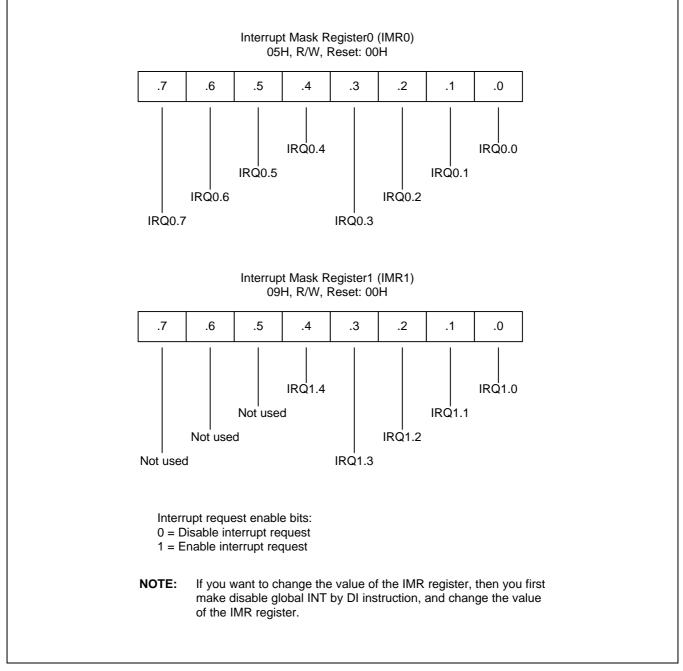

## **INTERRUPT MASK REGISTERS**

Figure 6-3. Interrupt Mask Register

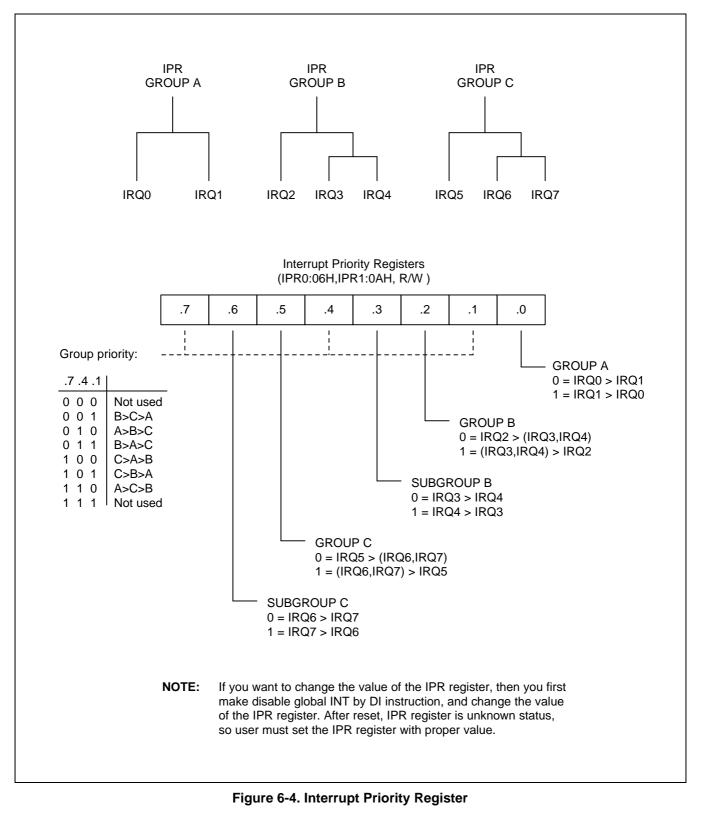

## INTERRUPT PRIORITY REGISTER

# PROGRAMMING TIP — Interrupt Programming Tip 1

Jumped from vector 2

| LTE05    | PUSH<br>PUSH<br>LD<br>CP<br>JR<br>CP<br>JR<br>CP<br>JP<br>CP | SR1<br>R0<br>R0, IIR00<br>R0, #03h<br>ULE, LTE03<br>R0, #05h<br>ULE, LTE05<br>R0, #06h<br>EQ, IRQ6_srv<br>T, IRQ7_srv<br>R0, #04 |                                  |

|----------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LTE03    | JP<br>JP<br>CP<br>JR<br>CP<br>JP<br>JP                       | EQ, IRQ4_srv<br>T, IRQ5_srv<br>R0, #01<br>ULE, LTE01<br>R0, #02<br>EQ, IRQ2_srv<br>T, IRQ3_srv                                   |                                  |

| LTE01    | CP<br>JP<br>JP                                               | R0, #00h<br>EQ, IRQ0_srv<br>T, IRQ1_srv                                                                                          |                                  |

| IRQ0_srv | JF                                                           | 1, 11(Q1_51)                                                                                                                     | ; $\rightarrow$ service for IRQ0 |

|          | •<br>POP<br>POP<br>IRET                                      | R0<br>SR1                                                                                                                        |                                  |

| IRQ1_srv |                                                              |                                                                                                                                  | ; $\rightarrow$ service for IRQ1 |

|          | POP<br>POP<br>IRET                                           | R0<br>SR1                                                                                                                        |                                  |

| IRQ7_srv | •                                                            |                                                                                                                                  | ; $\rightarrow$ service for IRQ7 |

|          | •<br>POP<br>POP<br>IRET                                      | R0<br>SR1                                                                                                                        |                                  |

## NOTE

If the SR0 register is changed in the interrupt service routine, then the SR0 register must be pushed and popped in the interrupt service routine.

## PROGRAMMING TIP — Interrupt Programming Tip 2

Jumped from vector 2

|          | PUSH<br>PUSH<br>LD<br>SL<br>LD<br>ADD<br>PUSH<br>PUSH<br>RET | SR1<br>R0<br>R1<br>R0, IIR00<br>R0<br>R1, < TBL_INTx<br>R0, > TBL_INTx<br>R1<br>R0                       |                                |    |

|----------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------|----|

| TBL_INTx | LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP         | IRQ0_svr<br>IRQ1_svr<br>IRQ2_svr<br>IRQ3_svr<br>IRQ4_svr<br>IRQ5_svr<br>IRQ5_svr<br>IRQ6_svr<br>IRQ7_svr |                                |    |

| IRQ0_srv |                                                              |                                                                                                          | ; $\rightarrow$ service for IR | Q0 |

|          | •                                                            |                                                                                                          |                                |    |

|          | POP<br>POP<br>POP<br>IRET                                    | R1<br>R0<br>SR1                                                                                          |                                |    |

| IRQ1_srv |                                                              |                                                                                                          | ; $\rightarrow$ service for IR | Q1 |

|          | •<br>POP<br>POP<br>POP<br>IRET<br>•                          | R1<br>R0<br>SR1                                                                                          |                                |    |

| IRQ7_srv | •                                                            |                                                                                                          | ; $\rightarrow$ service for IR | Q7 |

|          | •<br>POP<br>POP<br>POP<br>IRET                               | R1<br>R0<br>SR1                                                                                          |                                |    |

## NOTE

- 1. If the SR0 register is changed in the interrupt service routine, then the SR0 register must be pushed and popped in the interrupt service routine.

- 2. Above example is assumed that ROM size is less than 64K-word and all the LJP instructions in the jump table (TBL\_INTx) is in the same page.

# **T** INSTRUCTION SET

## OVERVIEW

## GLOSSARY

This chapter describes the CalmRISC instruction set and the details of each instruction are listed in alphabetical order. The following notations are used for the description.

| Notation         | Interpretation                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <opn></opn>      | Operand N. N can be omitted if there is only one operand. Typically, <op1> is the destination (and source) operand and <op2> is a source operand.</op2></op1> |

| GPR              | General Purpose Register                                                                                                                                      |

| SPR              | Special Purpose Register (IDL0, IDL1, IDH, SR0, ILX, ILH, ILL, SR1)                                                                                           |

| adr:N            | N-bit address specifier                                                                                                                                       |