## **SCANSTA476**

# **Eight Input IEEE 1149.1 Analog Voltage Monitor**

## **General Description**

The SCANSTA476 is a low power, Analog Voltage Monitor used for sampling or monitoring up to 8 analog/mixed-signal input channels. Analog Voltage Monitors are valuable during product development, environmental test, production, and field service for verifying and monitoring power supply and reference voltages. In a supervisory role, the 'STA476 is useful for card or system-level health monitoring and prognostics applications.

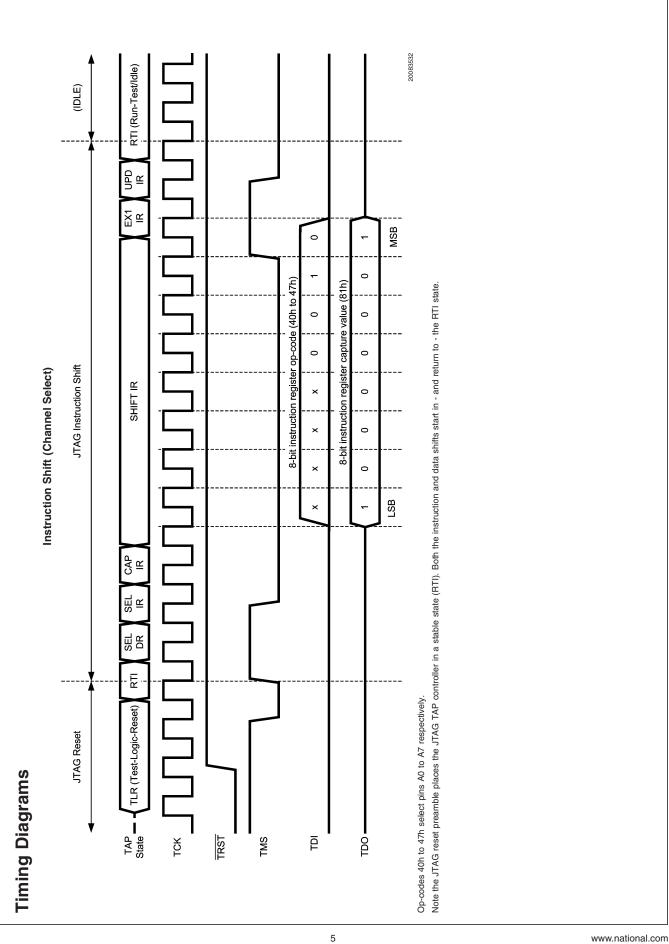

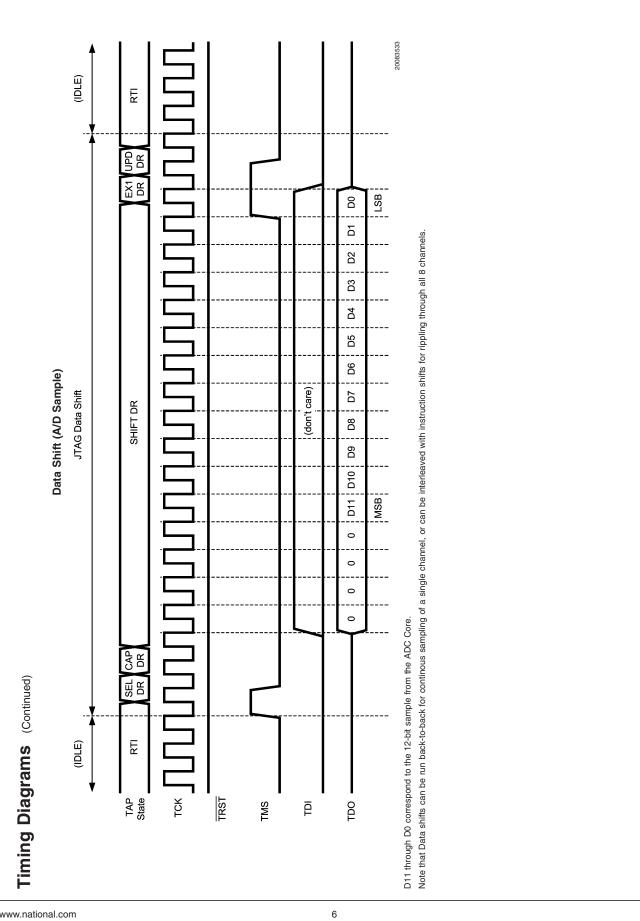

Instead of requiring an external microcontroller with a GPIO interface, the 'STA476 features a common IEEE 1149.1 (JTAG) interface to select the analog input, initiate a measurement, and access the results - further extending the capabilities of an existing JTAG infrastructure.

The SCANSTA476 uses the  $V_{\rm REF}$  input as a reference. This enables the SCANSTA476 to operate with a full-scale input range of 0 to  $V_{\rm DD}$ , which can range from +2.7V to +5.5V.

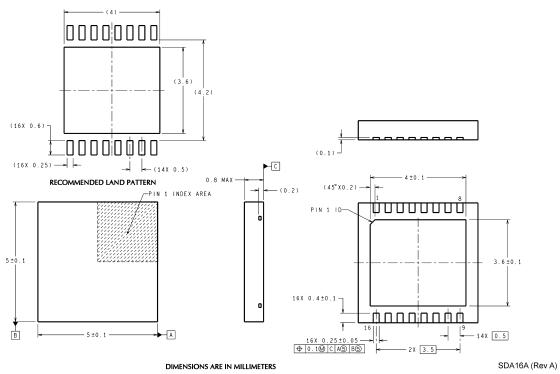

The SCANSTA476 is packaged in a 16-lead non-pullback LLP package that provides an extremely small footprint for applications where space is a critical consideration. This product operates over the industrial temperature range of -40°C to +85°C.

### **Features**

- Eight selectable Analog input channels

- Analog full-scale input range 0V to V<sub>DD</sub>

- Typical accuracy of 2 mV at maximum V<sub>DD</sub>

- Very low power operation

- Small package footprint in 16-lead, 5 x 5 x 0.8 mm LLP

- Single +2.7V to +5.5V supply operation

- IEEE 1149.1 (JTAG) compliant interface

## **Applications**

- Measurement of Point Voltages

- Real-time Signal Monitoring

- System Health Monitoring and Prognostics

- Debug, Environmental Test, Production Test, Field Service

- Supplement In-Circuit Tester (ICT) access

- Vital in Servers, Computing, Telecommunication and Industrial equipment

- Essential in Medical, Data Storage, and Networking equipment

## **Block Diagram**

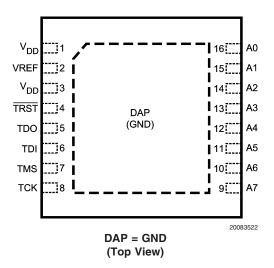

# **Connection Diagram**

# **Pin Descriptions**

| Pin No.     | Symbol           | Description                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ANALOG I/O  |                  |                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 16          | A0               | Analog input 0. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 15          | A1               | Analog input 1. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 14          | A2               | Analog input 2. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 13          | А3               | Analog input 3. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 12          | A4               | Analog input 4. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 11          | A5               | Analog input 5. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 10          | A6               | Analog input 6. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 9           | A7               | Analog input 7. This signal can range from 0V to V <sub>REF</sub> .                                                                                                                                                                                                                 |  |  |  |  |  |

| 2           | V <sub>REF</sub> | Analog reference voltage input. V <sub>REF</sub> must be ≤ V <sub>DD</sub> . This pin should be connected to a quiet                                                                                                                                                                |  |  |  |  |  |

|             |                  | +2.7V to +5.5V source (not directly to $V_{DD}$ ) and bypassed to GND with 0.1 $\mu F$ and 1 $\mu F$                                                                                                                                                                                |  |  |  |  |  |

|             |                  | monolithic capacitors located within 1 cm of the V <sub>REF</sub> pin.                                                                                                                                                                                                              |  |  |  |  |  |

| DIGITAL I/O |                  |                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 6           | TDI              | Test Data Input to support IEEE 1149.1 features                                                                                                                                                                                                                                     |  |  |  |  |  |

| 5           | TDO              | Test Data Ouput to support IEEE 1149.1 features                                                                                                                                                                                                                                     |  |  |  |  |  |

| 7           | TMS              | Test Mode Select to support IEEE 1149.1 features                                                                                                                                                                                                                                    |  |  |  |  |  |

| 8           | TCK              | Test Clock to support IEEE 1149.1 features                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4           | TRST             | Test Reset to support IEEE 1149.1 features                                                                                                                                                                                                                                          |  |  |  |  |  |

| POWER SUF   | PPLY             |                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 1,3         | $V_{DD}$         | Positive supply pin. These pins should be connected to a quiet +2.7V to +5.5V source and bypassed to GND with 0.1 $\mu$ F and 1 $\mu$ F monolithic capacitors located within 1 cm of the power pin.                                                                                 |  |  |  |  |  |

| (Note 1)    | GND              | Ground reference for CMOS circuitry. DAP is the exposed metal contact at the bottom of the LLP package. The DAP is used as the primary GND connection to the device. It should be connected to the ground plane with at least 4 vias for optimal low-noise and thermal performance. |  |  |  |  |  |

Note 1: Note that GND is not an actual pin on the package, the GND is connected thru the DAP on the back side of the LLP package.

## **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage  $V_{DD}$  -0.3V to +6.5V Voltage on Any Analog Pin to GND -0.3V to  $V_{DD}+0.3V$  Voltage on Any Digital Pin to GND -0.3V to  $V_{DD}+0.3V$  Input Current at Any Pin (Note 4)  $\pm 10$  mA ESD Susceptibility

Human Body Model 8000V

Machine Model >250V

Soldering Temperature Refer to AN-1187

Junction Temperature  $+150^{\circ}\text{C}$ Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ Thermal Resistance,  $\theta_{JA}$   $42^{\circ}\text{C/W}$ Thermal Resistance,  $\theta_{JC}$   $14.3^{\circ}\text{C/W}$

# Recommended Operating Conditions

Operating Temperature Range  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$   $V_{DD}$  Supply Voltage +2.7V to +5.5V Digital Input Pins Voltage Range +0V to  $V_{DD}$  Analog Input Pins Voltage Range (Note 5)

### **SCANSTA476 Electrical Characteristics**

The following specifications apply for  $V_{DD}$  = +2.7V to 5.5V,  $f_{TCK}$  = 20 MHz, unless otherwise noted.

| Symbol           | Parameter                                    | Conditions                                                           | Typical | Limits                                          | Units    |

|------------------|----------------------------------------------|----------------------------------------------------------------------|---------|-------------------------------------------------|----------|

| POWER            | SUPPLY CHARACTERISTICS                       |                                                                      | •       |                                                 |          |

|                  | Occurring Malkana                            | 10°0 . T 07°0                                                        |         | 2.7                                             | V (min)  |

| $V_{DD}$         | Supply Voltage                               | $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ 85 $^{\circ}$ C         |         | 5.5                                             | V (max)  |

|                  | Normal Mode (Static)                         | $V_{DD} = +2.7V \text{ to } +5.5V,$                                  | 3.5     | 5.0                                             | mA       |

| DD               | Normal Mode (Operational)                    | $V_{DD} = +2.7V \text{ to } +5.5V,$<br>$f_{TCK} = 1 \text{ MSPS}$    |         | 5.0                                             | mA (max) |

| <b>&gt;</b> D    | Power Consumption, Normal Mode (Operational) | V <sub>DD</sub> = +5.5V, f <sub>TCK</sub> = 1 MSPS                   |         | 27.5                                            | mW (max) |

| ANALOG           | INPUT CHARACTERISTICS (A0-A7)                |                                                                      | •       |                                                 |          |

| V <sub>IN</sub>  | Analog Input Range                           | $V_{REF} \leq V_{DD}$                                                |         | 0 to V <sub>REF</sub>                           | V        |

| V <sub>REF</sub> | Reference Voltage Range                      |                                                                      |         | V <sub>DD</sub> -<br>0.5V to<br>V <sub>DD</sub> | V        |

| DCL              | DC Leakage Current                           |                                                                      | 0.1     | ±10                                             | μΑ (max) |

|                  |                                              | V <sub>DD</sub> = +2.7V                                              | 1       | 7.5                                             | mV       |

| MEAS             | Analog Input Measurement Accuracy            | $V_{DD} = +5.5V$                                                     | 2       | 15                                              |          |

| DIGITAL          | INPUT CHARACTERISTICS (TDI, TMS              | 1                                                                    |         |                                                 |          |

| ,                |                                              | $V_{DD} = +2.7V \text{ to } +3.6V$                                   |         | 2.0                                             | V (min)  |

| $V_{IH}$         | Input High Voltage                           | V <sub>DD</sub> = +5.5V                                              |         | 2.1                                             |          |

| V <sub>IL</sub>  | Input Low Voltage                            | $V_{DD} = +5V$                                                       |         | 0.8                                             | V (max)  |

| / <sub>CL</sub>  | Input Clamp Voltage                          | I <sub>CL</sub> = -18mA                                              | -0.8    | -1.5                                            | V (max)  |

| IN               | Input Current                                | V <sub>IN</sub> = 0V or V <sub>DD</sub>                              | 0.2     | ±10                                             | μA (max) |

| ILR              | Input Current                                | TRST, TDI, TMS only                                                  |         | -300                                            | μA (max) |

| DIGITAL          | OUTPUT CHARACTERISTICS (TDO)                 |                                                                      | •       |                                                 |          |

| V <sub>OH</sub>  |                                              | $I_{OH} = -100 \ \mu A, \ 2.7V \le V_{DD} \le 5.5V$                  |         | V <sub>DD</sub> -0.2                            | V (min)  |

|                  | Output High Voltage                          | $I_{OH} = -4 \text{ mA}, \ 3.0 \text{V} \le V_{DD} \le 5.5 \text{V}$ |         | 2.4                                             | V (min)  |

|                  |                                              | $I_{OH} = -4 \text{ mA}, V_{DD} = 2.7 \text{V}$                      |         | 2.2                                             | V (min)  |

| V <sub>OL</sub>  | Output Low Voltage                           | $I_{OL} = 100 \ \mu A, \ 2.7V \le V_{DD} \le 5.5V$                   |         | 0.2                                             | V (max)  |

|                  | Output Low Voltage                           | $I_{OL} = 4 \text{ mA}, 2.7 \text{V} \le V_{DD} \le 5.5 \text{V}$    |         | 0.4                                             | V (max)  |

| os               | Output Short Circuit Current                 | $V_{OUT} = 0V, V_{DD} = 5.5V$                                        |         | -85                                             | mA (max) |

| oz               | TRI-STATE Leakage Current                    |                                                                      |         | ±10                                             | μA (max) |

|                  | Output Coding                                |                                                                      | Stra    | ight (Natural)                                  | Binary   |

### SCANSTA476 Electrical Characteristics (Continued)

The following specifications apply for  $V_{DD}$  = +2.7V to 5.5V,  $f_{TCK}$  = 20 MHz, unless otherwise noted.

| Symbol                        | Parameter                 | Conditions  | Typical | Limits | Units     |  |  |  |  |

|-------------------------------|---------------------------|-------------|---------|--------|-----------|--|--|--|--|

| AC ELECTRICAL CHARACTERISTICS |                           |             |         |        |           |  |  |  |  |

| F <sub>MAX</sub>              | Throughput Rate           | TCK = 20MHz |         | 1      | MSPS      |  |  |  |  |

|                               |                           |             |         |        | (max)     |  |  |  |  |

| INPUT TIMING CHARACTERISTICS  |                           |             |         |        |           |  |  |  |  |

| t <sub>SET</sub>              | TDI to TCK (H/L)          | (Note 3)    |         | 2.0    | ns (min)  |  |  |  |  |

| t <sub>HOLD</sub>             | TDI to TCK (H/L)          | (Note 3)    |         | 1.5    | ns (min)  |  |  |  |  |

| t <sub>SET</sub>              | TMS to TCK (H/L)          | (Note 3)    |         | 2.0    | ns (min)  |  |  |  |  |

| t <sub>HOLD</sub>             | TMS to TCK (H/L)          | (Note 3)    |         | 2.0    | ns (min)  |  |  |  |  |

| t <sub>W</sub>                | TCK Pulse Width (H/L)     | (Note 3)    |         | 10.0   | ns (min)  |  |  |  |  |

| t <sub>REC</sub>              | Recovery Time TRST to TCK | (Note 3)    |         | 2.0    | ns (min)  |  |  |  |  |

| t <sub>W</sub>                | TRST Pulse Width (L)      | (Note 3)    |         | 2.5    | ns (min)  |  |  |  |  |

| F <sub>MAX</sub>              | TCK                       |             |         | 20     | MHz (min) |  |  |  |  |

**Note 2:** Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not implied. Exposure to maximum ratings for extended periods may affect device reliability.

Note 3: Data sheet min/max specification limits are guaranteed by design or statistical analysis.

Note 4: Except power supply pins.

Note 5: For valid measurements, the analog  $V_{IN} \le V_{REF} \le V_{DD}$ .

## **Applications Information**

### **POWER-UP TIMING**

The SCANSTA476 typically requires 1  $\mu$ s to power up , either after first applying V<sub>DD</sub>, or after an incomplete conversion shift. To return to normal, one "dummy" conversion must be fully completed. After this first dummy conversion, the SCANSTA476 will perform conversions properly.

### STARTUP MODE

When the  $V_{DD}$  supply is first applied, the SCANSTA476 requires one dummy conversion after start-up.

### Physical Dimensions inches (millimeters) unless otherwise noted

LLP, Plastic, Dual Order Number SCANSTA476TSD, **NS Package Number SDA16A**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560