# **3-Phase Stepper Motor Driver ICs**

# **■**Absolute Maximum Ratings

| Parameter                 | Symbol           | Ratings     | Units |

|---------------------------|------------------|-------------|-------|

| Load supply voltage       | V <sub>BB</sub>  | 50          | V     |

| Logic supply voltage      | Vcc              | 7           | V     |

| Input voltage             | Vin              | −0.3 to Vcc | V     |

| Reference input voltage   | V <sub>REF</sub> | −0.3 to Vcc | V     |

| Sense voltage             | Vsense           | 1.5         | V     |

| Package power dissipation | P□               | 1           | W     |

| Junction temperature      | Tj               | -20 to +85  | °C    |

| Operating temperature     | Top              | +125        | °C    |

| Storage temperature       | T <sub>stg</sub> | –55 to +125 | °C    |

# **■**Recommended Operating Voltage Ranges

(Ta=25°C)

| Parameter               | Symbol           | Ratings      | Units |

|-------------------------|------------------|--------------|-------|

| Load supply voltage     | V <sub>BB</sub>  | 15 to 45     | V     |

| Logic supply voltage    | Vcc              | 3 to 5.5     | V     |

| Reference input voltage | V <sub>REF</sub> | 0.2 to Vcc-2 | V     |

### **■**Electrical Characteristics

| Parameter                 | Cumbal            | Ratings             |           |                    | Linita | Conditions                             |

|---------------------------|-------------------|---------------------|-----------|--------------------|--------|----------------------------------------|

|                           | Symbol            | min                 | typ       | max                | Units  | Conditions                             |

| Load supply voltage       | V <sub>BB</sub>   | 15                  |           | 45                 | V      |                                        |

| Logic supply voltage      | Vcc               | 3.0                 |           | 5.5                | V      |                                        |

|                           | V <sub>OL1</sub>  | 8                   |           | 15                 | V      |                                        |

| Output voltage            | V <sub>OL2</sub>  | 0                   |           | 1                  | V      |                                        |

| Output voltage            | Vон1              | V <sub>вв</sub> –15 |           | V <sub>BB</sub> -8 | V      |                                        |

|                           | V <sub>OH2</sub>  | V <sub>BB</sub> -1  |           | V <sub>ВВ</sub>    | V      |                                        |

| Load supply current       | Івв               |                     |           | 25                 | mA     | Vcc=5.5V                               |

| Logic supply current      | Icc               |                     |           | 10                 | mA     | Vcc=5.5V                               |

| Logio input voltago       | VIH               | 3.75                |           |                    | V      |                                        |

| Logic input voltage       | VIL               |                     |           | 1.25               | V      |                                        |

|                           | Ін                |                     |           | 20                 | μΑ     | V <sub>IN</sub> =V <sub>CC</sub> ×0.75 |

| Logic input current       | lıL               | -20                 |           |                    | μΑ     | V <sub>IN</sub> =V <sub>CC</sub> ×0.25 |

| Mandanian ala ali farmina | F                 | 200                 |           |                    | kHz    | Edge=0V                                |

| Maximum clock frequency   |                   | 100                 |           |                    |        | Edge=Vcc                               |

|                           | Vslow             | 1.7                 |           | Vcc                | V      |                                        |

| PFD input voltage         | V <sub>Mix</sub>  | 0.7                 |           | 1.3                | V      |                                        |

|                           | V <sub>Fast</sub> |                     |           | 0.3                | V      |                                        |

| PFD input current         | IPFD              |                     | ±50       |                    | μΑ     |                                        |

| Reference input voltage   | V <sub>REF</sub>  | 0                   |           | Vcc-2              | V      |                                        |

| Reference input current   | IREF              |                     | ±10       |                    | μΑ     | V <sub>REF</sub> =0~Vcc-2V             |

| Sense voltage             | Vs1               |                     | Vref×0.2  |                    | V      | Mode=Vcc, Vref=0~Vcc-2V                |

|                           | V <sub>S2</sub>   |                     | VREFX0.17 |                    | V      | Mode=0V, AVREF=0~Vcc-2V                |

| RC source current         | IRC               |                     | 220       |                    | μΑ     |                                        |

| Off time                  | Toff              |                     | 1.1×Rt×Ct |                    | Sec.   |                                        |

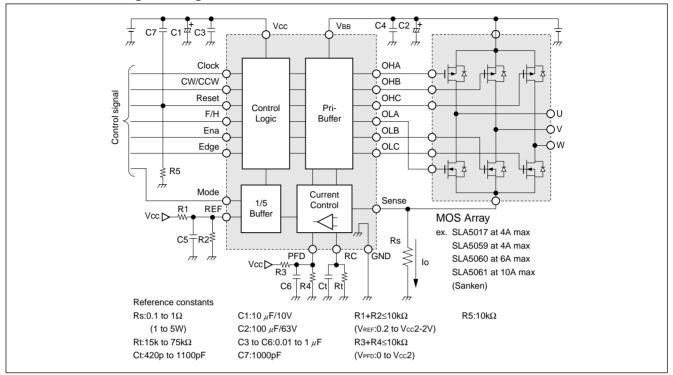

## ■Internal Block Diagram/Diagram of Standard External Circuit

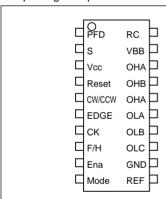

### **■**Terminal Connection

The package shapes of SI-7600 and SI-7600D are different, however the terminal connection is the same.

| Pin No. | Name   | Pin No. | Name      | Pin No. | Name |

|---------|--------|---------|-----------|---------|------|

| Pin1    | PFD    | Pin8    | Full/Half | Pin15   | OLA  |

| Pin2    | Sense  | Pin9    | Enable    | Pin16   | OHC  |

| Pin3    | Vcc    | Pin10   | Mode      | Pin17   | ОНВ  |

| Pin4    | Reset  | Pin11   | REF       | Pin18   | OHA  |

| Pin5    | CW/CCW | Pin12   | GND       | Pin19   | Vвв  |

| Pin6    | Edge   | Pin13   | OLC       | Pin20   | RC   |

| Pin7    | Clock  | Pin14   | OLB       |         |      |

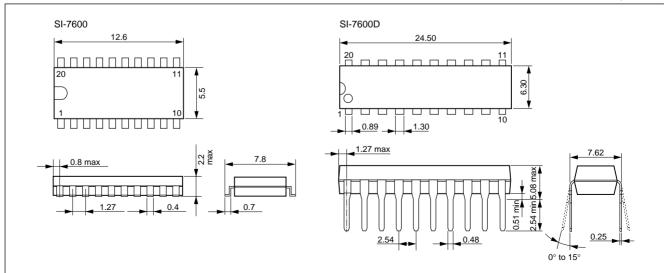

#### **External Dimensions** (Unless specified otherwise, all values are typical)

(Units: mm)

# **Application Notes**

#### 1. Outline

The SI-7600/SI-7600D is a control IC used with a power MOS FET array to drive a 3-phase stepper motor. Select the output-stage MOS FET according to the rated current of the motor. The full step is 2-phase excitation when this IC is in a star connection but 3-phase excitation when it is in a delta connection.

#### 2. Features

- Suitable for both star connection drive and delta connection drive

- Maximum load supply voltage V<sub>BB</sub>=45V

- Control logic supply voltage Vcc=3 to 5.5V

- Supports star connection (2/2-3phase excitation) and delta connection (3/2-3phase excitation)

- Step switching timing by clock signal input

- Forward/reverse, hold, and motor-free control

- Step switching at the positive edge or positive/negative edge of the clock signal

- Control current automatic switching function for 2-3phase excitation (effective for star connection)

(Current control: 86% for 2-phase excitation, 100% for 3-phase excitation)

- Self-excitation constant-current chopping by external C/R

- Slow Decay, Mixed Decay, or Fast Decay selectable

- Two package lineup: SOP (surface mounting) and DIP (lead insertion)

SOP...SI-7600, DIP...SI-7600D

Maximum output current depends on the ratings of the MOS FET array used

### 3. Input Logic Truth Table

| Input terminal | Low level           | High level               |

|----------------|---------------------|--------------------------|

| CW/CCW         | CW                  | CCW                      |

| Full/Half      | 2-3phase excitation | 2-phase excitation       |

| Enable         | Disable             | Enable                   |

| Mode           | Always 100%         | 2-phase excitation: 85%  |

| (Note 1)       | 7 (Ways 1007)       | 3-phase excitation: 100% |

| Edge           | Positive            | Positive/negative        |

| (Note 2)       | 1 contro            | 1 conveying ganve        |

| Reset          | Fnable              | Internal logic reset     |

| (Note 3)       | 2.14010             | output disable           |

Select CW/CCW, Full/Half, or Edge when the clock level is low. Note 1: The control current is always 85% for the full step (2-phase excitation) when the Mode terminal level is high. The value of 100% control current is calculated at the  $V_{\text{REF}}/(5\times Rs)$  terminal because a 1/5 buffer is built into the reference section.

Note 2: When the Edge terminal level is set high, the internal counter increments both at the rising and falling edges.

Therefore, the duty ratio of the input clock should be set at 50%.

Note 3: When the Reset terminal level is set high, the internal

counter is reset. Output remains disabled as long as the Reset terminal level is high.

#### 4. Determining the control current

The control current lo can be calculated as follows:

When the Mode terminal level is low

Io≅VREF/(5×Rs)

When the Mode terminal level is high

Io≅V<sub>REF</sub>/(5×R<sub>S</sub>)→ 3-phase excitation

$Io\cong V_{REF}/(5.88\times Rs) \rightarrow 2$ -phase excitation

The reference voltage can be set within the range of 0.2V to Vcc –2V. (When the voltage is less than 0.2V, the accuracy of the reference voltage divider ratio deteriorates.)

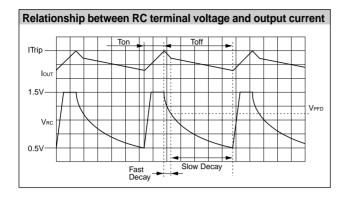

# About the Current Control System (Setting the Constant Ct/Rt)

The SI-7600 uses a current control system of the self-excitation type with a fixed chopping OFF time.

The chopping OFF time is determined by the constant Ct/Rt.

The constant Ct/Rt is calculated by the formula

The recommended range of constant Ct/Rt is as follows:

Ct: 420 to 1100pF

Rt: 15 to  $75k\Omega$

(Slow Decay or Mixed Decay  $\rightarrow$ 560pF/47k $\Omega$ , Fast Decay  $\rightarrow$  470pF/20k $\Omega$ )

Usually, set  $T_{\text{OFF}}$  to a value where the chopping frequency becomes about 30 to 40kHz.

The mode can be set to Slow Decay, Fast Decay, or Mixed Decay depending on the PFD terminal input potential.

PFD applied voltage and decay mode

| PFD applied voltage | Decay mode  |

|---------------------|-------------|

| 0 to 0.3V           | Fast Decay  |

| 0.7V to 1.3V        | Mixed Decay |

| 1.7V to Vcc         | Slow Decay  |

In Mixed Decay mode, the Fast/Slow time ratio can be set using the voltage applied to the PFD terminal. The calculated values are summarized below.

In this mode, the point of switching from Fast Decay to Slow Decay is determined by the RC terminal voltage that determines the chopping OFF time and by the PFD input voltage VPFD.

Formula (1) is used to determine the chopping OFF time.

The Fast Decay time is then determined by the RC discharge time from the RC voltage (about 1.5V) to the PFD input voltage (VPFD) when chopping is turned from ON to OFF.

The Fast Decay time is

$$t_{OFFf} \cong -R_{T} \times C_{T} \times I_{n} \left( \frac{V_{PFD}}{1.5} \right) \cdot \cdot \cdot \cdot \cdot (2)$$

The Slow Decay time (toffs) is calculated by subtracting the value of (2) from that of (1).

# 6. Method of Calculating Power Loss of Output **MOS FET**

The SI-7600 uses a MOS-FET array for output. The power loss of this MOS FET array can be calculated as summarized below. This is an approximate value that does not reflect parameter variations or other factors during use in the actual application. Therefore, heat from the MOS FET array should actually be measured.

#### Parameters for calculating power loss

To calculate the power loss of the MOS FET array, the following parameters are needed:

- (1) Control current lo (max)

- (2) Excitation method

- (3) Chopping ON-OFF time at current control: Ton, Toff, tofff (Ton: ON time, Toff: OFF time, toff: Fast Decay time at OFF)

- (4) ON resistance of MOS FET: RDS (ON)

- (5) Forward voltage of MOS FET body diode: VSD

For (4) and (5), use the maximum values of the MOS FET specifications.

(3) should be confirmed on the actual application.

#### Power loss of Pch MOS FETs

The power loss of Pch MOS FETs is caused by the ON resistance and by the chopping-OFF regenerative current flowing through the body diodes in Fast Decay mode.

(In Slow Decay mode, the chopping-OFF regenerative current does not flow the body diodes.)

The losses are

ON resistance loss P1: P1=I<sub>M</sub><sup>2</sup>×R<sub>DS</sub> (ON)

Body diode loss P2: P2=IMXVSD

With these parameters, the loss Pp per MOS FET is calculated depending on the actual excitation method as follows:

a) 2-phase excitation (T=Ton+Toff)

$P_P = (P1 \times T_{ON}/T + P2 \times t_{OFFf}/T) \times (1/3)$

b) 2-3 phase excitation (T=Ton+Toff)

$P_P = (P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times tofff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times toff/T) \times (1/4) + (0.5 \times P1 \times Ton/T + P2 \times Ton/T + P2$  $T)\times(1/12)$

#### Power loss of Nch MOS FETs

The power loss of Nch MOS FETs is caused by the ON resistance or by the chopping-OFF regenerative current flowing through the body diodes.

(This loss is not related to the current control method, Slow, Mixed, or Fast Decay.)

The losses are

ON resistance loss N1: N1=I<sub>M</sub><sup>2</sup>×R<sub>DS(ON)</sub>

Body diode loss N2: N2=IMXVsD

With these parameters, the loss PN per MOS FET is calculated depending on the actual excitation method as follows:

a) 2-phase excitation (T=Ton+Toff)

$P_N=(N1+N2\times T_{OFF}/T)\times (1/3)$

b) 2-3 phase excitation (T=Ton+Toff)

$P_N = (N1 + N2 \times T_{OFF}/T) \times (1/4) + (0.5N1 + N2 \times T_{OFF}/T) \times (1/12)$

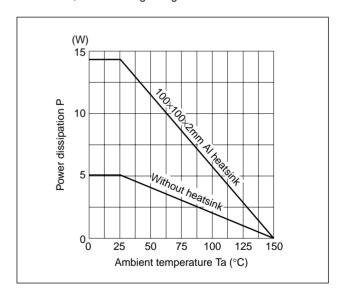

#### ●Determining power loss and heatsink when SLA5017 is used

If the SLA5017 is used in an output section, the power losses of a Pch MOS FET and an Nch MOS FET should be multiplied by three and added to determine the total loss P of SLA5017.

In other words,  $P=3\times P_P+3\times P_N$

The allowable losses of SLA5017 are

Without heatsink: 5W θj-a=25°C/W Infinite heatsink: 35W  $\theta$ j-c=3.57°C/W

Select a heatsink by considering the calculated losses, allowable losses, and following ratings:

When selecting a heatsink for SLA5017, be sure to check the product temperature when in use in an actual application.

The calculated loss is an approximate value and therefore contains a degree of error.

Select a heatsink so that the surface Al fin temperature of SLA5017 will not exceed 100°C under the worst conditions.

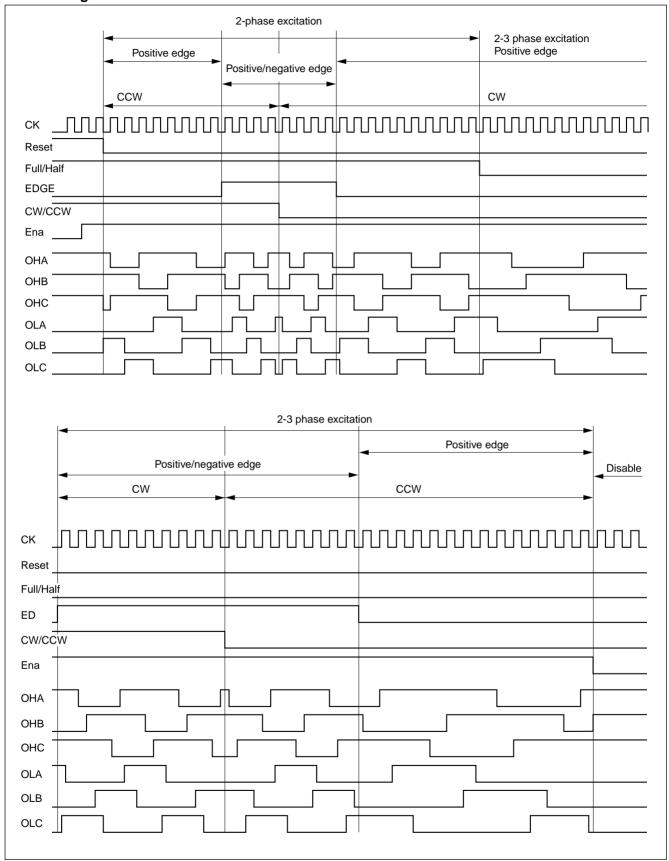

# 7. I/O Timing Chart