# STV2000

# I2C SINGLE FREQUENCY DEFLECTION PROCESSOR AND 70 MHz RGB PREAMPLIFIER

#### PRELIMINARY DATA

### **FEATURES**

### **Horizontal deflection**

- Single frequency, self adaptive oscillator.

- TTL compatible positive going sync.

- I<sup>2</sup>C controlled: H-position, Pin Cushion, Keystone, Parallelogram, Side Pin Balance,Hamplitude.

- DC East/West feedback.

- DC controls: H-width breathing compensation.

- X-Ray protection

### Vertical deflection

- Vertical ramp generator.

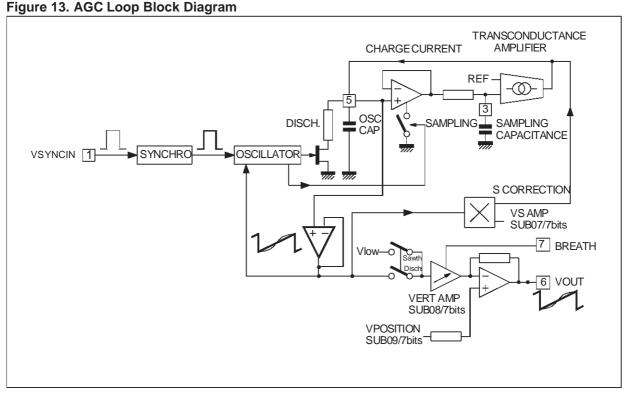

- Wide range AGC loop.

- TTL compatible positive going sync, no extra pulses.

- I<sup>2</sup>C controls: vertical position and S-correction.

- DC controls: height breathing compensation.

### Video preamplifier

- 3-channel 70MHz bandwidth RGB preamplifier.

- 5ns typical rise and fall time at 4V<sub>PP</sub>.

- I<sup>2</sup>C controls: RGB contrast, cut-off, brightness, contrast up-date during vertical retrace time.

- ABL will reduce gain (contrast).

- 0.514V typical video input signal for normal display.

### I<sup>2</sup>C Main features

- I<sup>2</sup>C interface (slave) 100kHz max.

- All I<sup>2</sup>C controlled DAC are 7bit, except for RGB gain and cut-off.

- Power- on- reset at 5 V (V<sub>DD</sub>).

- 0.5 to 4 V static DAC output.

### Supply voltage & power

- 5 V/10.5 V dual supply.

- Max power consumption: 1.2W

### DESCRIPTION

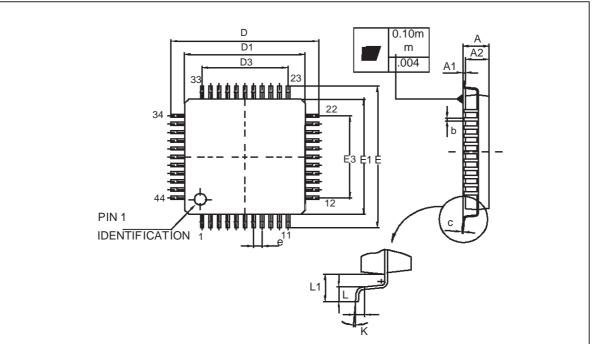

The STV2000 is an I<sup>2</sup>C-controlled monolithic integrated circuit assembled in a TQFP44 plastic package. It combines both a deflection block (horizontal and vertical, single frequency with very powerful geometry correction) and a 70MHz RGB pre-amplifier.

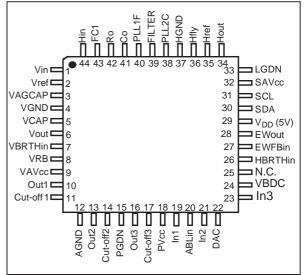

### **PIN CONNECTIONS**

#### Version 3.0

April 2000

This is preliminary information on a new product involved and product in

### — TABLE OF CONTENTS -

| PIN DESCRIPTION               | . 3 |

|-------------------------------|-----|

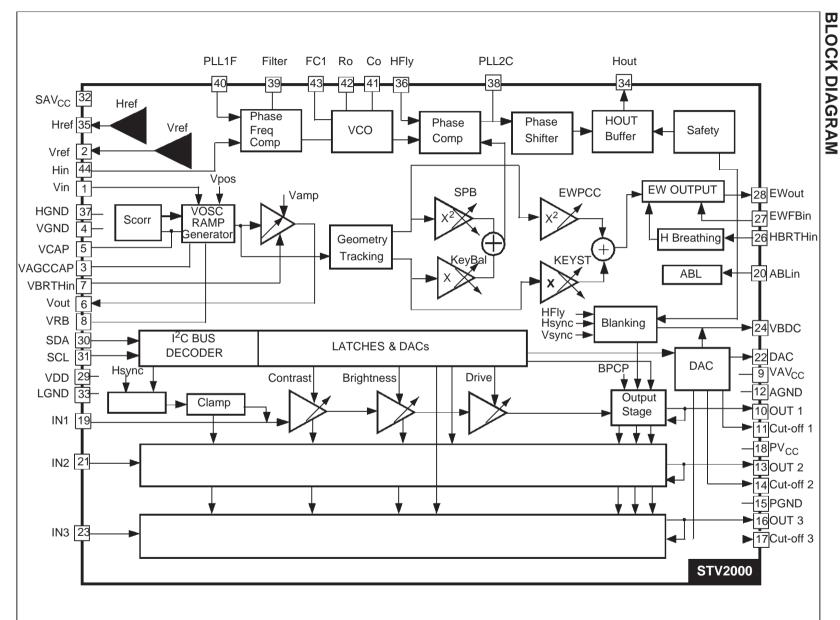

| BLOCK DIAGRAM                 | . 4 |

| ABSOLUTE MAXIMUM RATINGS      | . 5 |

| THERMAL DATA                  | . 5 |

| SYNC INPUT                    | . 5 |

| I2C READ/WRITE                |     |

| HORIZONTAL SECTION            |     |

| VERTICAL SECTION)             | . 8 |

| VIDEO PRE-AMP SECTION         | 11  |

| LOGIC SECTION                 | 12  |

| I2C BUS ADDRESS TABLE         | 13  |

| TYPICAL OUTPUT WAVEFORMS      |     |

| OPERATING DESCRIPTION         |     |

| SCANNING PART                 |     |

| PRE-AMPLIFIER PART            |     |

| STAND-BY MODE AND PROTECTIONS |     |

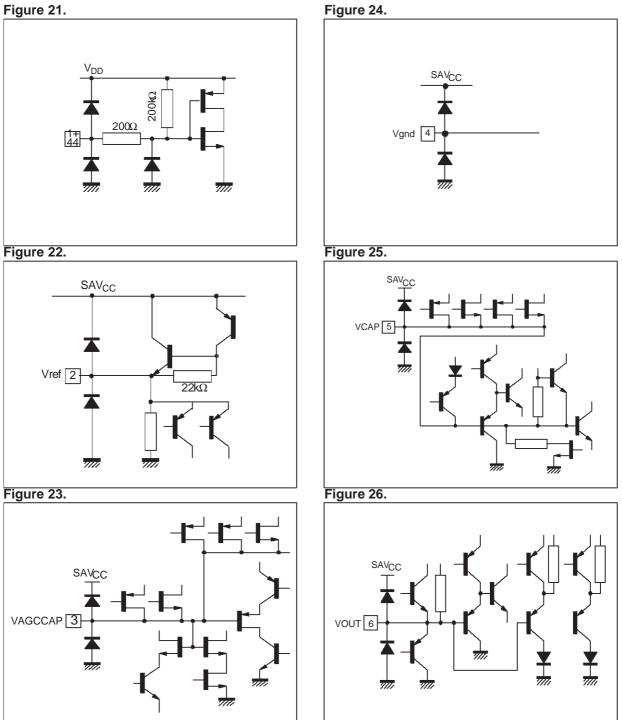

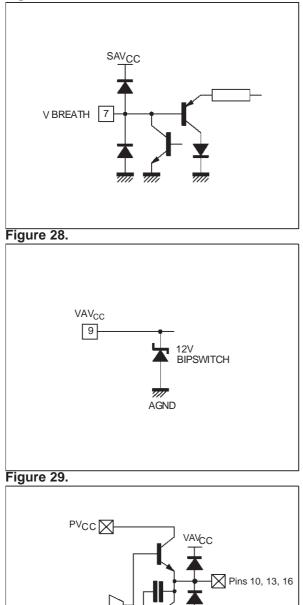

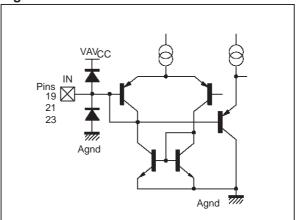

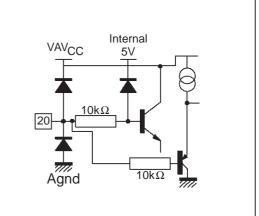

| INTERNAL SCHEMATICS           | 32  |

| PACKAGE MECHANICAL DATA       | 40  |

### **PIN DESCRIPTION**

| Pin      | Name            | Function                                               |

|----------|-----------------|--------------------------------------------------------|

| 1        | Vin             | Vertical Sync Input                                    |

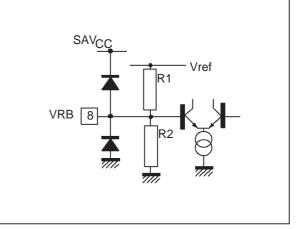

| 2        | Vref            | Vertical Section Reference Voltage                     |

| 3        | VAGCCAP         | Vertical AGC Loop Capacitor                            |

| 4        | VGND            | Vertical Section Ground                                |

| 5        | VCAP            | Vertical Sawtooth Generator Capacitor                  |

| 6        | Vout            | Vertical Output                                        |

| 7        | VBRTHin         | Vertical Breathing DC Input                            |

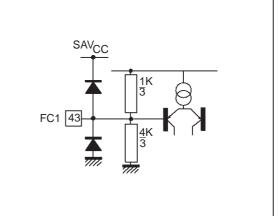

| 8        | VRB             | Vertical Ramp Filter                                   |

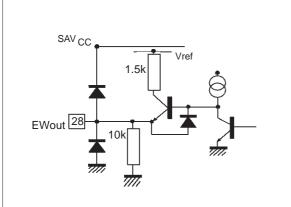

| 9        | VAVcc           | Video Section Analog Supply (10.5V typ)                |

| 10       | OUT1            | Video Output 1                                         |

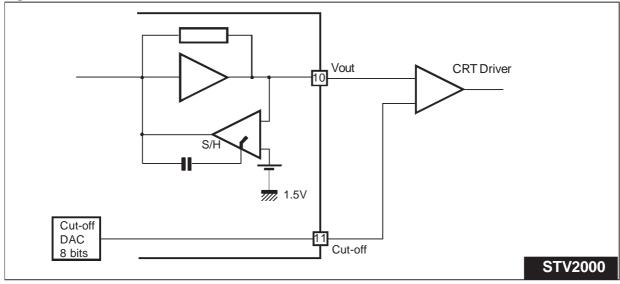

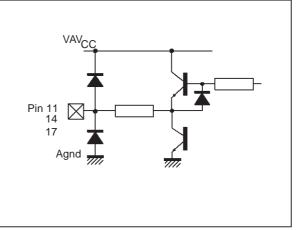

| 11       | Cut-off1        | Cut-off1 DAC voltage output pin                        |

| 12       | AGND            | Video Analog Ground                                    |

| 13       | OUT2            | Video Output 2                                         |

| 14       | Cutoff2         | Cut-off2 DAC voltage output pin                        |

| 15       | PGND            | Video Section Power Ground                             |

| 16       | OUT3            | Video Output 3                                         |

| 17       | Cutoff3         | Cut-off3 DAC voltage output pin                        |

| 18       | PVcc            | Video Section Power Supply (10.5V typ)                 |

| 19       | IN1             | Video Input 1                                          |

| 20       | ABLin           | Video Automatic Beam Current Compensation Input        |

| 21       | IN2             | Video Input 2                                          |

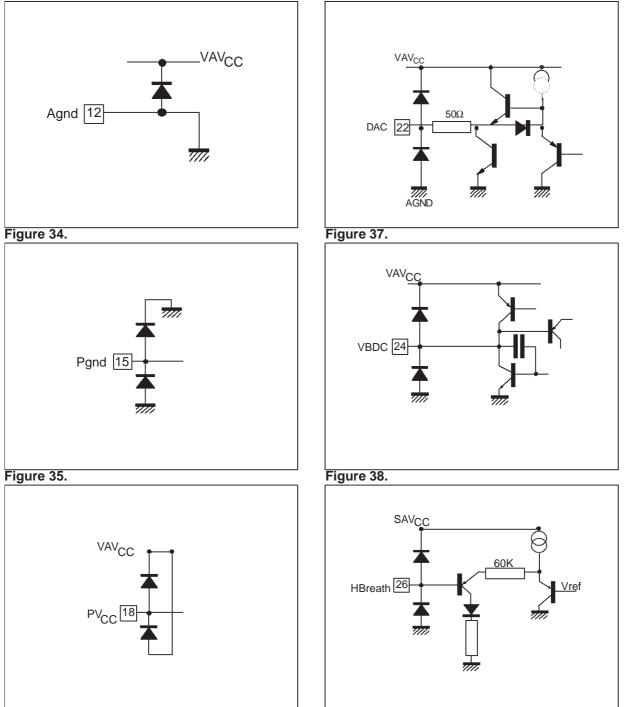

| 22       | DAC             | 7bits DAC Voltage Output                               |

| 23       | IN3             | Video Input 3                                          |

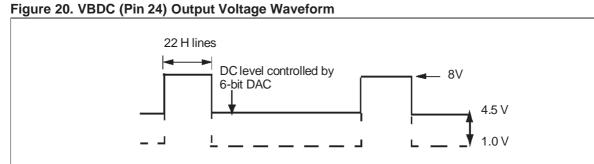

| 24       | VBDC            | Vertical Blanking Output with DC level adjusted by DAC |

| 25       | N.C.            | Not to be connected                                    |

| 26       | HBRTHin         | Horizontal Breathing Compensation DC Input             |

| 27       | EWFBin          | EW Correction Feedback Input                           |

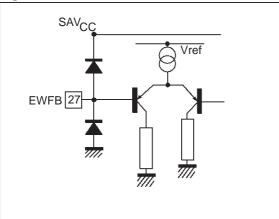

| 28       | EWout           | EW Buffer Output                                       |

| 29       | V <sub>DD</sub> | Bus, Scanning Logic and Video Logic Supply (5V typ)    |

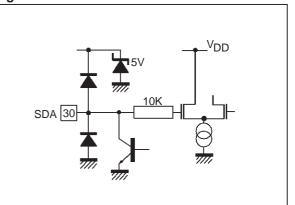

| 30       | SDA             | I <sup>2</sup> C Data Input                            |

| 31       | SCL             | I <sup>2</sup> C Clock Input                           |

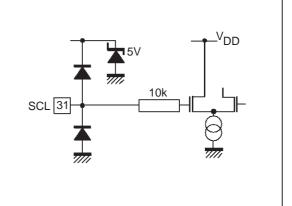

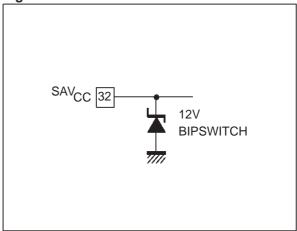

| 32       | SAVcc           | Scanning Section Analog Supply (10.5Vtyp)              |

| 33       | LGND            | Bus and Scanning Power Ground                          |

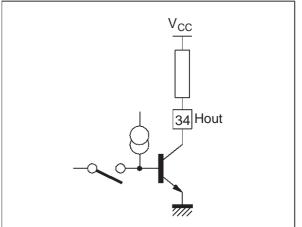

| 34       | Hout            | Horizontal Driver Output, open collector               |

| 35       | Href            | Horizontal Section Reference Voltage                   |

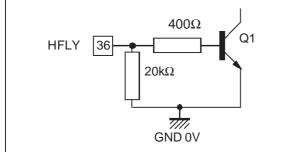

| 36       | Hfly<br>HGND    | Horizontal Flyback Input, Positive                     |

| 37       | PLL2C           | Horizontal Section Ground                              |

| 38       | -               | PLL2 Loop Filter                                       |

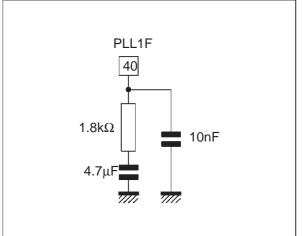

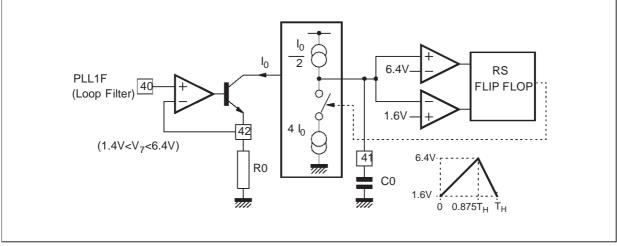

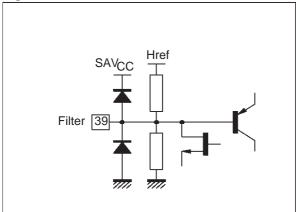

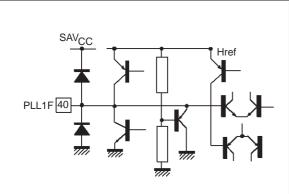

| 39<br>40 | Filter<br>PLL1F | Horizontal Filter Capacitor (HPOS)<br>PLL1 Loop Filter |

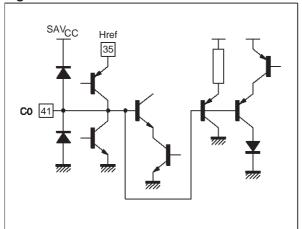

| 40       | Co              | Horizontal Oscillator Capacitor                        |

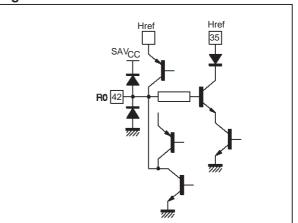

| 41       | Ro              | Horizontal Oscillator Capacitor                        |

| 42       | FC1             | PLL1 filter capacitor                                  |

| 43       | Hin             | Horizontal Sync Input                                  |

| 44       | F100            | Голгоная зулстири                                      |

4/38

STV2000

N

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                                          | Value      | Unit    |

|------------------|------------------------------------------------------------------------------------|------------|---------|

| SAVcc            | Scanning Section Analog Supply Voltage                                             | 13.5       | V       |

| VAVcc            | Video Section Analog Supply Voltage                                                | 13.5       | V       |

| PVcc             | Supply Voltage for Video Pre-Amp Section                                           | 13.5       | V       |

| Vdd              | Logic Section Supply Voltage                                                       | 5.5        | V       |

| V <sub>ESD</sub> | ESD susceptibility HBM model 100pF & 1.5k $\Omega$<br>EIAJ Norm 200pF & 0 $\Omega$ | 2<br>300   | kV<br>V |

| Tstg             | Storage Temperature                                                                | -40 to 150 | °C      |

| Tj               | Junction Temperature                                                               | 150        | °C      |

| Toper            | Operating Temperature (Device ambient)                                             | 0 to 70    | °C      |

### THERMAL DATA

| Symbol               | Parameter                                    | Value | Unit |

|----------------------|----------------------------------------------|-------|------|

| R <sub>TH(j-a)</sub> | Junction to Ambient Thermal Resistance (MAX) | 46    | °C/W |

### SYNC INPUT

### **Operating Conditions** (V<sub>DD</sub> = 5V, T<sub>amb</sub> = 25°C)

| Symbol     | Parameter                                                              | Test Conditions | Min | Тур | Мах | Unit |  |

|------------|------------------------------------------------------------------------|-----------------|-----|-----|-----|------|--|

| HSVR       | Voltage on Hin                                                         | Pin 44          | 0   |     | 5   | V    |  |

| MinD       | Min Hin pulse duration                                                 | Pin 44          | 0.7 |     |     | us   |  |

| Mduty      | Max Hin Duty Cycle                                                     | Pin 44          |     |     | 25  | %    |  |

| VSVR       | Voltage on Vin                                                         | Pin 1           | 0   |     | 5   | V    |  |

| VSW        | Min Vin pulse duration                                                 | Pin 1           | 5   |     |     | us   |  |

| VSD        | Max Vin Duty Cycle                                                     | Pin 1           |     |     | 15  | %    |  |

| Electrical | Electrical Characteristics ( $V_{DD} = 5V$ , $T_{amb} = 25^{\circ}C$ ) |                 |     |     |     |      |  |

| V <sub>INTH</sub> | Horizontal & Vertical Input Logic Level | Low Level<br>High Level | 2.2 |     | 0.8 | V<br>V |  |

|-------------------|-----------------------------------------|-------------------------|-----|-----|-----|--------|--|

| RIN               | Horizontal & Vertical Pull-Up Resistor  |                         |     | 200 |     | kΩ     |  |

## I<sup>2</sup>C READ/WRITE

### **Electrical Characteristics** ( $V_{DD} = 5V$ , $T_{amb} = 25^{\circ}C$ )

| Symbol            | Parameter                                        | Test Conditions | Min | Тур | Мах | Unit |

|-------------------|--------------------------------------------------|-----------------|-----|-----|-----|------|

| F <sub>SCL</sub>  | Maximum Clock Frequency                          |                 |     |     | 100 | kHz  |

| T <sub>LOW</sub>  | Low Period of the SCL Clock                      |                 | 1.3 |     |     | us   |

| T <sub>HIGH</sub> | High Period of SCL Clock                         |                 | 0.6 |     |     | us   |

| V <sub>INL</sub>  | SDA & SCL Input Low Level Voltage                |                 |     |     | 1.5 | V    |

| V <sub>INH</sub>  | SDA & SCL Input High Level Voltage               |                 | 3   |     |     | V    |

| V <sub>ACK</sub>  | Acknowledge Output Voltage on SDA input with 3mA |                 |     |     | 0.4 | V    |

### HORIZONTAL SECTION

### **Operating Conditions**

| Symbol            | Parameter                                               | Test Conditions | Min | Тур  | Max  | Unit |

|-------------------|---------------------------------------------------------|-----------------|-----|------|------|------|

| VCO               | •                                                       |                 | •   | •    |      |      |

| Ro(min)           | Minimum Oscillator Resistor                             |                 | 6   |      |      | kΩ   |

| Co(min)           | Minimum Oscillator Capacitor                            |                 | 390 |      |      | pF   |

| Fmax              | Maximum Oscillator Frequency                            |                 |     |      | 150  | kHz  |

| OUTPUT SE         | CTION                                                   | •               | •   | •    | •    |      |

| I <sub>HFB</sub>  | Horizontal FlyBack Input Maximum<br>Current             |                 |     |      | 5    | mA   |

| I <sub>HOUT</sub> | Horizontal Drive Output Maximum Sink<br>Current         |                 |     |      | 15   | mA   |

| Electrical        | <b>Characteristics</b> ( $V_{DD} = 5V$ , $T_{amb} = 25$ | 5°C)            |     |      |      |      |

| Symbol            | Parameter                                               | Test Conditions | Min | Тур  | Max  | Unit |

| SUPPLY AN         | D REFERENCE VOLTAGES                                    | •               | •   | •    |      |      |

| Vcc               | Supply Voltage                                          |                 | 9.5 | 10.5 | 11.5 | V    |

| Vdd               | Supply Voltage                                          |                 | 4.5 | 5    | 5.5  | V    |

| lcc               | Supply Current                                          |                 |     | 30   |      | mA   |

| Idd               | Supply Current                                          |                 |     | 5    |      | mA   |

| V <sub>HREF</sub> | Horizontal Reference Voltage                            | I=-2mA          | 7.4 | 8    | 8.6  | V    |

| VVREF             | Vertical Reference Voltage                              | I=-2mA          | 7.4 | 8    | 8.6  | V    |

| I <sub>HREF</sub> | Horizontal Reference Maximum Source<br>Current          |                 |     |      | 5    | mA   |

| I <sub>VREF</sub> | Vertical Reference Maximum Source<br>Current            |                 |     |      | 5    | mA   |

### **Operating Conditions**

| Symbol                                      | Parameter                                                            | Test Conditions                               | Min | Тур               | Мах  | Unit                |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|-----|-------------------|------|---------------------|--|--|--|

| 1st PLL SECTION                             |                                                                      |                                               |     |                   |      |                     |  |  |  |

| V <sub>clamp</sub>                          | VCO clamp Voltage range                                              | V <sub>HREF</sub> =8V                         | 3.0 |                   | 3.8  | V                   |  |  |  |

| V <sub>VCO</sub>                            | VCO clamp Voltage, at POR                                            | V <sub>HREF</sub> =8V                         |     | 3.8               |      | V                   |  |  |  |

| A <sub>VCO</sub>                            | VCO Gain                                                             | Ro=6490Ω, Co=820pF,<br>dF/dV=1/11RoCo         |     | 17.1              |      | kHz/V               |  |  |  |

| H <sub>PHASE</sub>                          | Horizontal Phase Adjustment Range                                    | % of Horizontal Period                        |     | +/-10             |      | %                   |  |  |  |

| VPMIN<br>VPTYP<br>VPMAX                     | Horizontal Phase<br>Minimum<br>Typical<br>Maximum                    | SubAdd 07<br>X1111111<br>X1000000<br>X0000000 |     | 2.8<br>3.4<br>4.0 |      | V<br>V<br>V         |  |  |  |

| I <sub>PLL1-UL</sub><br>I <sub>PLL1-L</sub> | PLL1 Charge Pump Current                                             | Unlocked<br>Locked                            |     | +/-140<br>+/-1    |      | μA<br>mA            |  |  |  |

| f <sub>O</sub>                              | Free Running Frequency, no input at POR, lower clamp voltage at max. | Ro=6490Ω, Co=820pF                            |     | 65                |      | kHz                 |  |  |  |

| dfo/dT                                      | Free Running Frequency Thermal Drift                                 |                                               |     |                   | -150 | ppm/ <sup>o</sup> C |  |  |  |

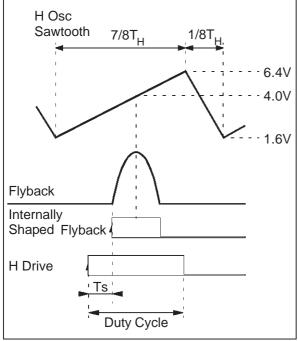

| 2nd PLL SE                                  | CTION & HORIZONTAL OUTPUT SECTIO                                     | N N                                           |     |                   |      |                     |  |  |  |

|                                             |                                                                      |                                               |     |                   |      |                     |  |  |  |

| V <sub>THFB</sub>   | Flyback Input Threshold Voltage                                                                                                       |                         | 0.65 | 0.75       |     | V      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------------|-----|--------|

| Jitter <sub>H</sub> | Horizontal Jitter                                                                                                                     | At 60KHz                |      | 70         |     | ppm    |

| H <sub>DC</sub>     | Horizontal Drive Output Duty Cycle<br>(Ratio of Power Transistor OFF time to<br>Period)                                               |                         |      | 48         |     | %      |

| Vphi2               | Internal Clamp Level on PLL2 Filter                                                                                                   | Low Level<br>High Level |      | 1.6<br>4.0 |     | V<br>V |

| VSCinh              | Threshold Voltage to Stop H-Out, V-Out, Reset ABL when Vcc <vscinh< td=""><td></td><td></td><td>6.9</td><td></td><td>V</td></vscinh<> |                         |      | 6.9        |     | V      |

| Vsat <sub>HD</sub>  | Horizontal Drive Output Saturation Voltage                                                                                            | lout=15mA               |      |            | 0.4 | V      |

### **VERTICAL SECTION**

| Symbol             | Parameter                                                                                                               | Test Conditions                                | Min   | Тур                        | Мах | Unit                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------|----------------------------|-----|---------------------|

| Electrical         | Characteristics (V <sub>DD</sub> = 5V, T <sub>amb</sub> = 25                                                            | 5°C)                                           | _1    |                            |     | 1                   |

| VERTICAL F         | RAMP SECTION                                                                                                            |                                                |       |                            |     |                     |

| V <sub>RBOT</sub>  | Voltage at Ramp Bottom Point                                                                                            | V <sub>VREF</sub> =8V                          |       | 2                          |     | V                   |

| V <sub>RTOP</sub>  | Voltage at Ramp Top Point with Sync                                                                                     | V <sub>VREF</sub> =8V                          |       | 5                          |     | V                   |

| V <sub>RTOPF</sub> | Voltage at Ramp Top Point without Sync                                                                                  | V <sub>VREF</sub> =8V                          |       | V <sub>RTOP</sub> -<br>0.1 |     | V                   |

| T <sub>VDIS</sub>  | Vertical Sawtooth Discharge Time                                                                                        | C <sub>OSC</sub> =150nF                        |       | 70                         |     | μs                  |

| F <sub>FRV</sub>   | Vertical Free Running Frequency<br>(S correction inhibited)                                                             | C <sub>OSC</sub> =150nF                        |       | 100                        |     | Hz                  |

| ASFR               | Auto-Sync Frequency Range                                                                                               | C <sub>OSC</sub> =150nF                        | 50    |                            | 165 | Hz                  |

| RAFD               | Ramp Amplitude Drift Versus Frequency at Maximum Vertical Amplitude                                                     | C <sub>OSC</sub> =150nF 50Hz -<br>165Hz        |       | 200                        |     | ppm/Hz              |

| R <sub>LIN</sub>   | Ramp Linearity at Vcap pin<br>with S Correction inhibited                                                               | 2.5V < VOSC < 4.5V                             |       | 0.5                        |     | %                   |

| V <sub>POS</sub>   | Vertical Position Adjustment Voltage with $V_{\mbox{OUT}}$ mean value                                                   | Sub-Add=09<br>X0000000<br>X1000000<br>X1111111 | 3.65  | 3.2<br>3.5<br>3.8          | 3.3 | V<br>V<br>V         |

| VOR                | Vertical Output Peak to Peak Voltage                                                                                    | Sub-Add=08<br>10000000<br>11000000<br>11111111 | 3.5   | 2.25<br>3<br>3.75          | 2.5 | V<br>V<br>V         |

| I <sub>VOUT</sub>  | Vertical Output Maximum Current                                                                                         |                                                |       | +/-5                       |     | mA                  |

| V <sub>VRB</sub>   | Vertical Ramp Filter Voltage                                                                                            |                                                |       | 2                          |     | V                   |

| dVS                | Max Vertical S-Correction Amplitude<br>S-Correction inhibited, DV/Vpp at TV/4<br>S-correction Maximum,                  | Sub-Add 0A<br>0XXXXXXX                         |       | -4                         |     | %                   |

|                    | DV/Vpp at 3TV/4                                                                                                         | 11111111                                       |       | +4                         |     | %                   |

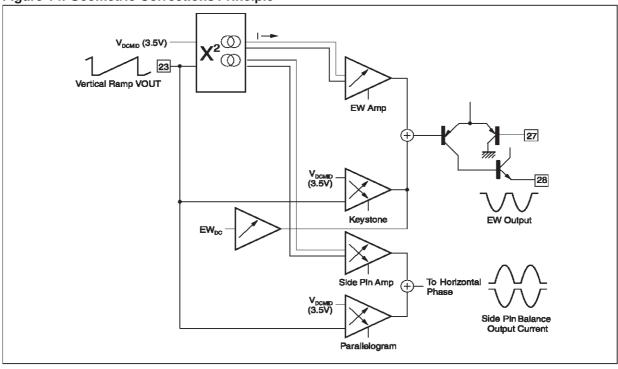

| EAST/WEST          | FUNCTION (output is internal, can be che                                                                                | cked at EWFB pin indire                        | ctly) |                            |     |                     |

| EW <sub>DC</sub>   | DC Output Voltage with Typical VPOS<br>and Keystone inhibited<br>With external driver connected as unity<br>gain buffer |                                                |       | 2.0                        |     | V                   |

| TDEW <sub>DC</sub> | DC Output Voltage Thermal Drift<br>(Non-test Parameter)                                                                 |                                                |       | 100                        |     | ppm/ <sup>o</sup> C |

| EW <sub>PARA</sub> | Parabola Amplitude with Max VAMP,<br>Typ VPOS, Keystone inhibited                                                       | Sub-add 0C<br>11111111<br>11000000<br>10000000 |       | 1.0<br>0.5<br>0            |     | V<br>V<br>V         |

| Symbol              | Parameter                                                                                                                                                      | Test Conditions                                    | Min | Тур          | Мах | Unit                               |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|--------------|-----|------------------------------------|

| EW <sub>track</sub> | Parabola Amplitude Function of VAMP<br>Control (tracking between VAMP & EW)<br>with Typ VPOS, Keystone, Typ EW<br>Amplitude.                                   | Sub-address 08<br>10000000<br>11000000<br>11111111 |     |              |     | V<br>V<br>V                        |

| KeyAdj              | Keystone Adjustment Capability with<br>Typ VPOS, EW inhibited and Max<br>Vertical Amplitude                                                                    | Sub-address 0B<br>10000000<br>11111111             |     | 0.2<br>0.2   |     | V <sub>pp</sub><br>V <sub>pp</sub> |

| KeyTrack            | Intrinsic Keystone Function of VPOS<br>Control (tracking between VPOS and<br>EW) with Max EW Amplitude and<br>Max Vertical Amplitude<br>A/B Ratio<br>B/A Ratio | Sub-add 09<br>X0000000<br>X1111111                 |     | 0.52<br>0.52 |     |                                    |

| INTERNAL [          | DYNAMIC HORIZONTAL PHASE CONTRO                                                                                                                                |                                                    |     |              |     |                                    |

|                     | Sida Din Palanca Darabala Amplituda                                                                                                                            | Sub add 0E                                         |     | 1            |     |                                    |

| SBPpara  | Side Pin Balance Parabola Amplitude<br>with Max VAMP, Typ VPOS and<br>Parallelogram inhibited                                                                           | Sub-add 0E<br>11111111<br>10000000             | +1.4<br>-1.4      | %T <sub>H</sub><br>%T <sub>H</sub>                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-------------------------------------------------------|

| SPBtrack | Side Pin Balance Parabola Amplitude<br>function of VAMP Control (tracking be-<br>tween VAMP & SPB) with Max SPB,<br>Typ VPOS and Parallelogram inhibited                | Sub-add 08<br>10000000<br>11000000<br>11111111 | 0.5<br>0.9<br>1.4 | %T <sub>H</sub><br>%T <sub>H</sub><br>%T <sub>H</sub> |

| ParAdj   | Parallelogram Adjustment Capability<br>with Max VAMP, Typ VPOS and<br>Max SPB                                                                                           | Sub-add 0F<br>11111111<br>10000000             | +1.4<br>-1.4      | %T <sub>H</sub><br>%T <sub>H</sub>                    |

| Partrack | Intrinsic Parallelogram Function of<br>VPOS Control (tracking between VPOS<br>and DHPC) with Max VAMP, Max SPB<br>and Parallelogram inhibited<br>A/B Ratio<br>B/A Ratio | Sub-add 09<br>X0000000<br>X1111111             | 0.52<br>0.52      |                                                       |

VERTICAL BREATHING COMPENSATION

| VBRrng                  | Input DC Breathing Control Range                         |                                     | 1 |          | 10.5 | V      |  |  |  |

|-------------------------|----------------------------------------------------------|-------------------------------------|---|----------|------|--------|--|--|--|

| VBRadj                  | Vertical Output Variation versus DC<br>Breathing Control | Vbrin>V <sub>VREF</sub><br>Vbrin=4V |   | 0<br>-10 |      | %<br>% |  |  |  |

| HORIZONTAL SIZE CONTROL |                                                          |                                     |   |          |      |        |  |  |  |

| Hsize                   | Hsize output DC voltage sitting on top of EWDC=2.0V      | sub-add 0D<br>X0000000<br>X1111111  |   | 0<br>2.4 |      | V<br>V |  |  |  |

| EW OUTPUT BUFFER        |                                                          |                                     |   |          |      |        |  |  |  |

| lewout | EWout pin max source current | 3.0 |     | mA |

|--------|------------------------------|-----|-----|----|

| EWFB   | EWoutput referred DC voltage |     | 2.0 | V  |

| Symbol    | Parameter                                                                       | Min | Тур | Мах | Unit |   |

|-----------|---------------------------------------------------------------------------------|-----|-----|-----|------|---|

| HORIZONTA | L BREATHING COMPENSATION                                                        |     |     |     |      |   |

| HBRdc     | Breathing input DC Control Range                                                |     | 1   |     | 10.5 | V |

| HSC       | Horizontal size compensation, EW DC voltage variation under full range of HBRdc |     |     | 0.4 |      | V |

### **VIDEO PRE-AMP SECTION**

| Symbol                                                                                    | Parameter                           | Test Conditions | Min | Тур  | Мах  | Unit |  |  |  |  |

|-------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----|------|------|------|--|--|--|--|

| <b>DC Electrical Characteristics</b> (VAV <sub>CC</sub> = $PV_{CC}$ = 10.5V, Tamb = 25°C) |                                     |                 |     |      |      |      |  |  |  |  |

| VAV <sub>cc</sub>                                                                         | Video Section Analog Supply Voltage |                 | 9.5 | 10.5 | 11.5 | V    |  |  |  |  |

| PVcc                                                                                      | Power Section Supply Voltage        |                 | 9.5 | 10.5 | 11.5 | V    |  |  |  |  |

| IS                                                                                        | Supply Current of VAVcc & PVcc      |                 |     | 60   |      | mA   |  |  |  |  |

| V <sub>IN</sub>                                                                           | Video Input Voltage Amplitude       |                 |     | 0.7  | 1    | Vpp  |  |  |  |  |

| V <sub>OUT</sub>                                                                          | Typical Output Voltage Range        |                 | 0.5 |      | 7    | V    |  |  |  |  |

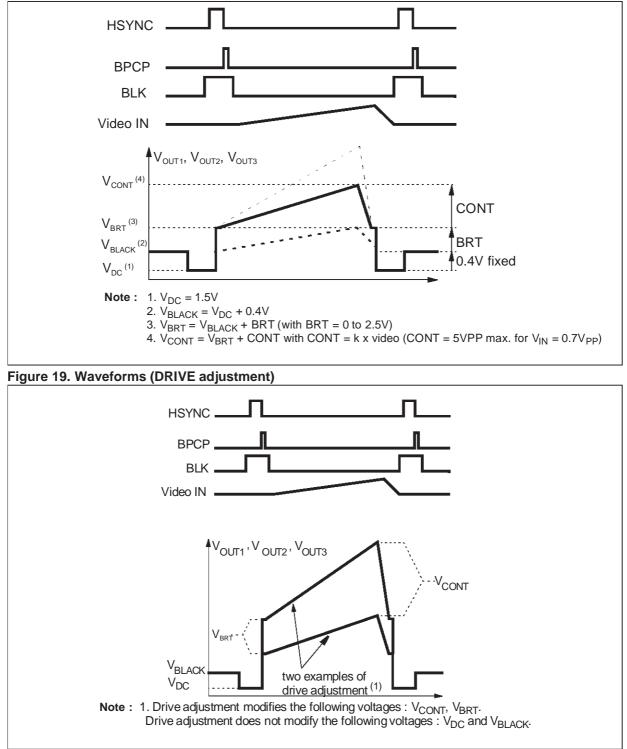

| V <sub>DC</sub>                                                                           | Output DC level (Black level)       |                 |     | 1.5  |      | V    |  |  |  |  |

**AC Electrical Characteristics** (VAV<sub>CC</sub> = PV<sub>CC</sub> = 10.5V, CL = 12pF, RL = 1K $\Omega$ , Tamb = 25°C)

| Symbol                          | Parameter                                                   | Condition                                                                         | Min | Тур      | Мах | Unit   |

|---------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|----------|-----|--------|

| AV                              | Maximum Gain                                                | Max Contrast and Drive<br>I <sup>2</sup> C Gainwin = 1                            |     | 18       |     | dB     |

| CAR                             | Contrast Attenuation Range                                  | V <sub>IN</sub> = 0.7Vpp<br>Contrast and Drive at<br>POR                          |     | 30       |     | dB     |

| DAR                             | Drive Attenuation Range                                     |                                                                                   |     | 30       |     | dB     |

| GM                              | Gain Match                                                  | $V_{IN} = 0.7Vpp,$<br>$V_{OUT} = 4Vpp,$ Contrast<br>and Drive= 0.87Max            |     | +-0.1    |     | dB     |

| BW                              | Large Signal Bandwidth                                      | $V_{IN}$ =0.7Vpp,<br>$V_{OUT}$ = 4Vpp, Contrast<br>and Drive = 0.87Max<br>At -3dB |     | 70       |     | MHz    |

| DIS                             | Video Output Distortion                                     | f=1MHz, V <sub>IN</sub> =1Vpp,<br>V <sub>OUT</sub> = 1Vpp                         |     | 0.3      |     | %      |

| t <sub>R</sub> , t <sub>F</sub> | Video Output Rise and Fall Time                             | V <sub>IN</sub> = 0.7Vpp,<br>V <sub>OUT</sub> =4Vpp,Contrast<br>and Drive=0.87Max |     |          | 5   | ns     |

| dVo                             | Overshoot of output with respect to actual output amplitude | C <sub>LOAD</sub> =5pF                                                            |     | 5        | 7   | %      |

| BRT                             | Brightness max DC level<br>Brightness min DC level          |                                                                                   |     | 2.5<br>0 |     | V<br>V |

| R <sub>L</sub>                  | Equivalent Load on Video Output                             | Tj <tj<sub>MAX</tj<sub>                                                           |     | 1        |     | kΩ     |

| Tsample                         | Hold time                                                   |                                                                                   | 100 |          |     | ms     |

| Parameter                                                             | Test Conditions                                                                                                                                                                                                                                | Min                                                                                                                                                                                                                                                                                                                                       | Тур                                                                                                                                                                                                                                                                                                                                                             | Max                                                                                                                                                                                                                                                                                                                                           | Unit                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample time                                                           |                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               | μs                                                                                                                                                                                                                                                                                                                                                                                                     |

| Crosstalk Between Video Channels                                      | $V_{IN} = 0.7Vpp,$<br>$V_{OUT} = 2.5Vpp,$<br>Contrast and<br>Drive=0.7Max<br>f=1MHz                                                                                                                                                            | 44                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               | dB                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                                                                     |                                                                                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                        |

| CUTOFF DAC output voltage                                             | 00000000<br>10000000<br>11111111                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                           | 0.5<br>2.5<br>4.5                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                               | V<br>V<br>V                                                                                                                                                                                                                                                                                                                                                                                            |

| Output sink current<br>Output source current                          |                                                                                                                                                                                                                                                | 2                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 | 100                                                                                                                                                                                                                                                                                                                                           | μA<br>mA                                                                                                                                                                                                                                                                                                                                                                                               |

| NSATION                                                               |                                                                                                                                                                                                                                                | <u> </u>                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                        |

| ABL Input resistor                                                    |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                               | kΩ                                                                                                                                                                                                                                                                                                                                                                                                     |

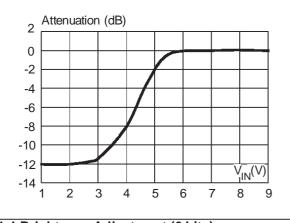

| ABL minimum Attenuation<br>ABL maximum Attenuation                    | V <sub>ABL</sub> =5.3V<br>V <sub>ABL</sub> =2.8V                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                           | 0<br>12                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                               | dB<br>dB                                                                                                                                                                                                                                                                                                                                                                                               |

| ABL latch function activation threshold (High beam current detection) |                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                       | Sample time<br>Crosstalk Between Video Channels<br>CUTOFF DAC output voltage<br>Output sink current<br>Output source current<br>NSATION<br>ABL Input resistor<br>ABL minimum Attenuation<br>ABL maximum Attenuation<br>ABL maximum Attenuation | Sample time VIN = 0.7Vpp,<br>VOUT = 2.5Vpp,<br>Contrast and<br>Drive=0.7Max<br>f=1MHz   CUTOFF DAC output voltage 00000000<br>10000000<br>11111111   Output sink current<br>Output source current 00000000<br>11111111   NSATION ABL Input resistor   ABL maximum Attenuation<br>ABL maximum Attenuation threshold VABL=5.3V<br>VABL=2.8V | Sample time1Crosstalk Between Video Channels $V_{IN} = 0.7Vpp, V_{OUT} = 2.5Vpp, Contrast and Drive=0.7Max f=1MHz44CUTOFF DAC output voltage00000000 10000000 11111111144Output sink current Output source current2NSATION2ABL Input resistor2ABL minimum Attenuation ABL maximum AttenuationV_{ABL}=5.3V V_{ABL}=2.8VABL latch function activation threshold0$ | Sample time1Crosstalk Between Video ChannelsVIN = 0.7Vpp,<br>VOUT = 2.5Vpp,<br>Contrast and<br>Drive=0.7Max<br>f=1MHz44CUTOFF DAC output voltage00000000<br>10000000<br>111111110.5<br>2.5<br>4.5Output sink current<br>Output source current2INSATION2ABL Input resistor10<br>VABL=5.3V<br>VABL=2.8VABL latch function activation threshold0 | Sample time1Crosstalk Between Video ChannelsVIN = 0.7Vpp,<br>VOUT = 2.5Vpp,<br>Contrast and<br>Drive=0.7Max<br>f=1MHz44CUTOFF DAC output voltage00000000<br>1000000<br>11111110.5<br>2.5<br>4.5Output sink current<br>Output source current2100NSATION2100ABL Input resistor10ABL minimum Attenuation<br>ABL maximum AttenuationVABL=5.3V<br>VABL=2.8V0<br>12ABL latch function activation threshold01 |

DAC

| VDAC | I <sub>LOAD</sub> =100uA | sub-add 12<br>00000000<br>01000000<br>01111111 |     | 0.5<br>2.25<br>4.0 | V<br>V<br>V |

|------|--------------------------|------------------------------------------------|-----|--------------------|-------------|

| IDAC | Source current           |                                                | 1.5 | 2                  | mA          |

### LOGIC SECTION

DC Electrical Characteristics (VAV<sub>CC</sub> = PV<sub>CC</sub> = 10.5V, Tamb =  $25^{\circ}$ C)

| Symbol                   | Parameter                                       | Condition                         | Min | Тур      | Мах | Unit    |  |  |  |  |  |  |

|--------------------------|-------------------------------------------------|-----------------------------------|-----|----------|-----|---------|--|--|--|--|--|--|

| V BLANKING               | V BLANKING OUTPUT SECTION                       |                                   |     |          |     |         |  |  |  |  |  |  |

|                          | Blanking output high voltage                    |                                   | 7   |          |     | V       |  |  |  |  |  |  |

| VBDC                     | Blanking output low voltage<br>I2C adjustable   | sub-add10<br>1X000000<br>1X111111 |     | 1<br>4.5 |     | V<br>V  |  |  |  |  |  |  |

| I <sub>BLK</sub>         | Output sink current                             |                                   |     |          | 0.3 | mA      |  |  |  |  |  |  |

| T <sub>BLK</sub>         | Vertical blanking time<br>(gated with Hflyback) |                                   |     | 22       |     | H cycle |  |  |  |  |  |  |

| SUPPLY VOLTAGE THRESHOLD |                                                 |                                   |     |          |     |         |  |  |  |  |  |  |

| V <sub>THPD1</sub>       | Supply first threshold voltage                  |                                   |     | 8.5      |     | V       |  |  |  |  |  |  |

| V <sub>THPD2</sub>       | Supply second threshold voltage                 |                                   |     | 6.9      |     | V       |  |  |  |  |  |  |

# I<sup>2</sup>C BUS ADDRESS TABLE

|                       | D8                    | D7         | D6    | D5           | D4                 | D3            | D2           | D1  |

|-----------------------|-----------------------|------------|-------|--------------|--------------------|---------------|--------------|-----|

| WRI                   | E MODE (SLA)          | /E ADDRESS | = 8C) | •            |                    |               |              |     |

| 00                    | Video: 1, on          |            |       |              | Contrast           |               |              |     |

|                       | [0], off              | [1]        | [0]   | [1]          | [1]                | [0]           | [1]          | [0] |

| 01                    | [4]                   | [0]        | [4]   | Drive        |                    | [4]           | [0]          | [0] |

|                       | [1]                   | [0]        | [1]   | [1]<br>Drive | [0]                | [1]           | [0]          | [0] |

| 02                    | [1]                   | [0]        | [1]   | [1]          | [0]                | [1]           | [0]          | [0] |

|                       | [.]                   |            |       | Drive        |                    | [.]           |              | [0] |

| 03                    | [1]                   | [0]        | [1]   | [1]          | [0]                | [1]           | [0]          | [0] |

| 04                    |                       |            |       | Cut o        |                    |               | -            |     |

| 01                    | [0]                   | [0]        | [0]   | [0]          | [1]                | [0]           | [0]          | [0] |

| 05                    | [0]                   | [0]        | [0]   | Cut o        |                    | [0]           | [0]          | [0] |

|                       | [0]                   | [0]        | [0]   | [0]<br>Cut o | [1]                | [0]           | [0]          | [0] |

| 06                    | [0]                   | [0]        | [0]   | [0]          | [1]                | [0]           | [0]          | [0] |

|                       | Hout                  | [0]        |       |              | tal Phase Adj      |               | [0]          | [0] |

| 07                    | 0, off                | [4]        | [0]   | i            |                    |               | [0]          | [0] |

|                       | [1], on               | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | Vramp                 |            | ·     | Vertical Rai | mp Amplitude       | Adjustment    | i            |     |

| 08                    | 0, off<br>[1], on     | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | Xray                  |            |       | l<br>Vertica | l<br>Position Adju | Istment       |              |     |

| 09                    | 1, reset              |            | 101   |              | , í                |               | 101          | [0] |

|                       | [0]                   | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

| S Select S Correction |                       |            |       |              |                    |               |              |     |

| 0A                    | 1, on                 | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | [0], off<br>EW Key    |            |       |              | Keystone           |               |              |     |

| 0B                    | 0, off                |            |       |              |                    | 101           |              | 101 |

| -                     | [1], on               | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | EW Select             |            |       |              | EW Amplitude       |               |              |     |

| 0C                    | 0, off                | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | [1], on               |            |       |              | izontal Amplit     |               |              |     |

| 0D                    | х                     | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | SPB Sel               |            |       |              | ide Pin Baland     |               | [0]          | [0] |

| 0E                    | 0, off                | [4]        | [0]   |              |                    |               | [0]          | [0] |

|                       | [1], on               | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

| <b>0F</b>             | Parallelog            |            |       |              | Parallelogram      |               |              |     |

| 0F                    | 0, off<br>[1], on     | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       | VBDC                  | Gainwin    |       |              | Vertical Blan      | king DC level |              |     |

| 10                    | 1, on                 | [0], 1X    | [4]   | [4]          |                    |               | [4]          | [4] |

|                       | [0], off              | 1, 1.5X    | [1]   | [1]          | [1]                | [1]           | [1]          | [1] |

|                       | POR Powsav Brightness |            |       |              |                    |               |              |     |

| 11                    | [0], off              | 1, on      | [1]   | [0]          | [1]                | [1]           | [0]          | [1] |

|                       | 1, reset              | [0], off   |       |              | DAC                |               |              |     |

| 12                    |                       | [1]        | [0]   | [0]          | [0]                | [0]           | [0]          | [0] |

|                       |                       |            |       |              |                    |               | ge clamp (FV |     |

| 13                    | х                     | х          | х     | x            | [0]                | [0]           | [0]          | [0] |

[0] denotes POR value, X denotes unused data bit and must be set to 0.

| D8                             | D7 | D6       | D5 | D4 | D3 | D2 | D1 |  |  |

|--------------------------------|----|----------|----|----|----|----|----|--|--|

| READ MODE (SLAVE ADDRESS = 8D) |    |          |    |    |    |    |    |  |  |

| Hlock                          |    | Xray     |    |    |    |    |    |  |  |

| 0, lock                        |    | 1, on    |    |    |    |    |    |  |  |

| [1], unlock                    |    | [0], off |    |    |    |    |    |  |  |

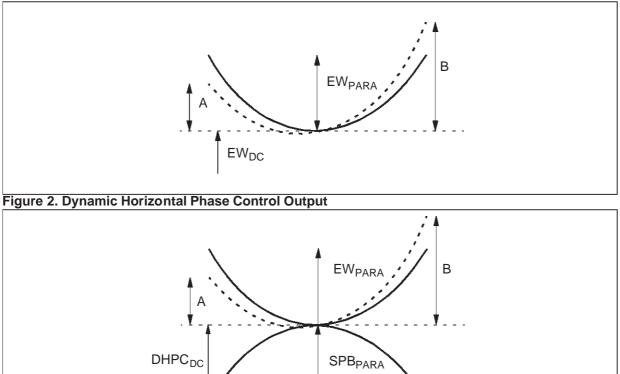

### Figure 1. EW Output Referred Voltage

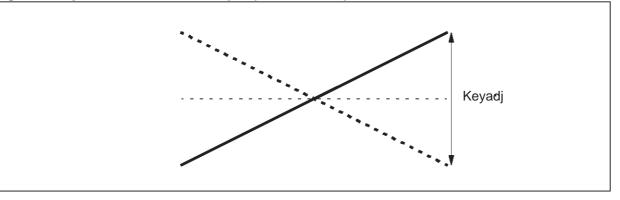

Figure 3. Keystone Effect on EW Output (PCC Inhibited)

### **TYPICAL OUTPUT WAVEFORMS**

| Function                   | Sub<br>Address | Pin | Byte                                    | Specification                                                                          | Effect on Screen |

|----------------------------|----------------|-----|-----------------------------------------|----------------------------------------------------------------------------------------|------------------|

| Vertical Size              |                |     | 10000000                                | 2.25 V<br>3.75 V                                                                       |                  |

| Vertical<br>Position       |                |     | x0000000<br>x1000000<br>x1111111        | V <sub>OUTDC</sub> = 3.2 V<br>V <sub>OUTDC</sub> = 3.5 V<br>V <sub>OUTDC</sub> = 3.8 V | <b>Å</b>         |

| Vertical<br>S<br>Linearity |                |     | 00000000<br>Inhibited<br>11111111       | V <sub>PP</sub>                                                                        |                  |

| Keystone                   |                |     | EW<br>Inhibited<br>10000000             | 2.0V<br>2.0V<br>2.0V<br>0.2Vpp<br>0.2Vpp                                               |                  |

| EW<br>Pin Cushion          |                |     | EW<br>Inhibited<br>10000000<br>11111111 | 2.0 V<br>2.0 V                                                                         |                  |

| Function                        | Sub<br>Address | Pin | Byte                                               | Specification                                  | Effect on Screen |

|---------------------------------|----------------|-----|----------------------------------------------------|------------------------------------------------|------------------|

| H Amplitude                     |                |     | 10000000<br>11111111                               |                                                |                  |

| H Phase                         |                |     | 00000000<br>01111111<br>5                          | 5 <u>V</u>                                     |                  |

| Side Pin<br>Ballance<br>Control |                |     | Parallelogram<br>Inhibited<br>10000000<br>11111111 | 3.7 V<br>3.7 V<br>3.7 V<br>1.4% T              |                  |

| Parallelo-<br>gram<br>Control   |                |     | SPB<br>Inhibited<br>10000000<br>11111111           | 3.7 V<br>3.7 V<br>3.7 V<br>1.4% T <sub>H</sub> | X                |

| Hex | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Vpp   | G(dB) | POR |

|-----|----|----|----|----|----|----|----|----|-------|-------|-----|

|     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | -     |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0.015 | -30   |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0.031 | -24   |     |

|     | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0.062 | -18   |     |

|     | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0.125 | -12   |     |

|     | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0.25  | -6    |     |

|     | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0.5   | 0     |     |

|     | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 2     | 12    |     |

|     | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 2.812 | 15    | Х   |

|     | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 4     | 18    |     |

# Contrast Register (Video IN = $0.5V_{PP}$ , Drive at maximum, I<sup>2</sup>C Gainwin=1)

Brightness Register (Drive at maximum)

| Hex | b5 | b4 | b3 | b2 | b1 | b0 | Vpp   | POR |

|-----|----|----|----|----|----|----|-------|-----|

|     | 0  | 0  | 0  | 0  | 0  | 0  | 0     |     |

|     | 0  | 0  | 0  | 0  | 0  | 1  | 0.010 |     |

|     | 0  | 0  | 0  | 0  | 1  | 0  | 0.020 |     |

|     | 0  | 0  | 0  | 1  | 0  | 0  | 0.040 |     |

|     | 0  | 0  | 1  | 0  | 0  | 0  | 0.08  |     |

|     | 0  | 1  | 0  | 0  | 0  | 0  | 0.16  |     |

|     | 1  | 0  | 0  | 0  | 0  | 0  | 0.32  |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  | 0.64  |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  | 1.28  |     |

|     | 1  | 0  | 1  | 1  | 0  | 1  | 1.8   | Х   |

|     | 1  | 1  | 1  | 1  | 1  | 1  | 2.56  |     |

**Drive1, Drive2, Drive3 Registers** (Video IN =  $0.5V_{PP}$ , Contrast at maximum, I<sup>2</sup>C Gainwin=1)

| Hex | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Vpp   | G(dB) | POR |

|-----|----|----|----|----|----|----|----|----|-------|-------|-----|

| 00  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | -     |     |

| 01  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0.015 | -30   |     |

| 02  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0.031 | -24   |     |

| 04  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0.062 | -18   |     |

| 08  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0.125 | -12   |     |

| 10  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0.25  | -6    |     |

| 20  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0.5   | 0     |     |

| 40  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1     | 6     |     |

| 80  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 2     | 12    |     |

| B4  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 2.812 | 15    | Х   |

| FF  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 4     | 18    |     |

| Hex | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | FB pin | POR |

|-----|----|----|----|----|----|----|----|----|--------|-----|

| 00  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0.5    |     |

| 01  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |        |     |

| 02  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |        |     |

| 04  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |        |     |

| 08  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0.625  | Х   |

| 10  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |        |     |

| 20  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |        |     |

| 40  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |        |     |

| 80  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |        |     |

| B4  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  |        |     |

| FF  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 4.5    |     |

### Cutoff1, Cutoff2, Cutoff3 Output values

### DAC Output DC voltage

| Hex | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Output dc | POR |

|-----|----|----|----|----|----|----|----|-----------|-----|

|     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0.5       |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  | 1  |           |     |

|     | 0  | 0  | 0  | 0  | 0  | 1  | 0  |           |     |

|     | 0  | 0  | 0  | 0  | 1  | 0  | 0  |           |     |

|     | 0  | 0  | 0  | 1  | 0  | 0  | 0  |           |     |

|     | 0  | 0  | 1  | 0  | 0  | 0  | 0  |           |     |

|     | 0  | 1  | 0  | 0  | 0  | 0  | 0  |           |     |

|     | 1  | 0  | 0  | 0  | 0  | 0  | 0  |           |     |

|     | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 2.25      | Х   |

|     | 0  | 1  | 1  | 0  | 1  | 0  | 0  |           |     |

|     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 4.0       |     |

### Vertical Blanking Output DC voltage

| Hex | b5 | b4 | b3 | b2 | b1 | b0 | Output dc | POR |

|-----|----|----|----|----|----|----|-----------|-----|

|     | 0  | 0  | 0  | 0  | 0  | 0  | 1.0       |     |

|     | 0  | 0  | 0  | 0  | 0  | 1  |           |     |

|     | 0  | 0  | 0  | 0  | 1  | 0  |           |     |

|     | 0  | 0  | 0  | 1  | 0  | 0  |           |     |

|     | 0  | 0  | 1  | 0  | 0  | 0  |           |     |

|     | 0  | 1  | 0  | 0  | 0  | 0  |           |     |

|     | 1  | 0  | 0  | 0  | 0  | 0  |           |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  |           |     |

|     | 0  | 0  | 0  | 0  | 0  | 0  |           |     |

|     | 1  | 1  | 0  | 1  | 0  | 0  |           |     |

|     | 1  | 1  | 1  | 1  | 1  | 1  | 4.5       | Х   |

### **OPERATING DESCRIPTION**

### **A SCANNING PART**

#### 1. GENERAL CONSIDERATIONS

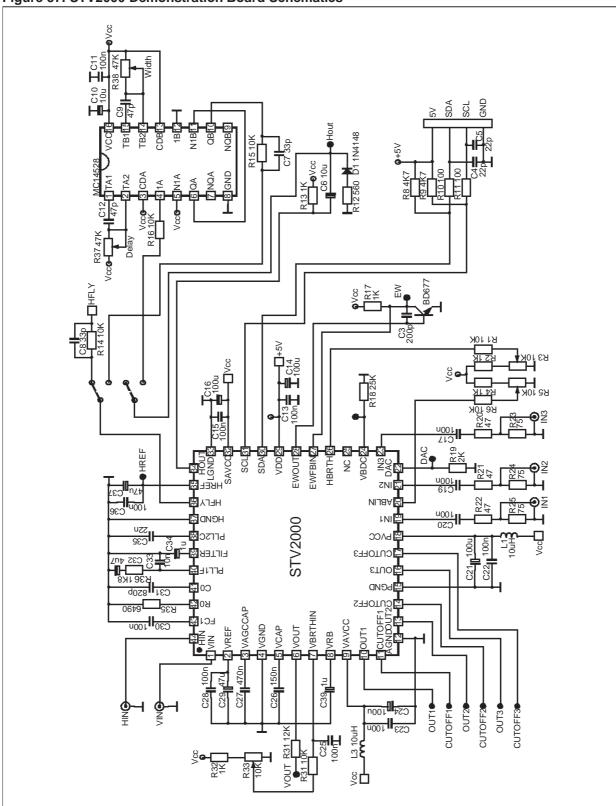

#### 1.1 Power Supply

Typical power supply voltages are 10.5 V for the Deflection and Preamplifier sections (SAV<sub>CC</sub>, VAV<sub>CC</sub> and PV<sub>CC</sub>) and 5.0 V for the logic section (Vdd). Optimum operation is obtained between 9.5 and 11.5 for V<sub>CC</sub>, and between 4.5 and 5.5 V for V<sub>DD</sub>.

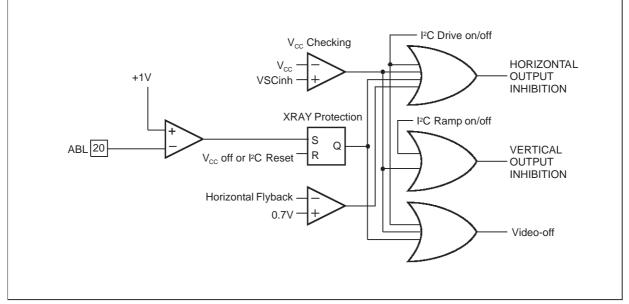

$V_{CC}$  is monitored during the transient phase when switched either on or off, to avoid erratic operation of the circuit. If  $V_{CC}$  is inferior to 6.9 V typ., the circuit outputs are inhibited. Similarly, before  $V_{DD}$  reaches 4 V, all the I<sup>2</sup>C registers are reset to their default value (see I<sup>2</sup>C Control Table).

The circuit is internally supplied by several voltage references (typ. value: 8 V) to ensure a good power supply rejection. Two of these voltage references are externally accessible respectively for the vertical and horizontal parts. They can be used to bias external circuitry if  $I_{LOAD}$  is inferior to 5 mA. To minimize the noise and consequently the "jitter" on vertical and horizontal output signals, the reference voltages must be filtered by external capacitors connected to the ground.

#### **1.2 I<sup>2</sup>C Control**

STV2000 belongs to the I<sup>2</sup>C-controlled device family. Each adjustment can be made via the I<sup>2</sup>C Interface, instead of being controlled by DC voltages on dedicated control pins. The I<sup>2</sup>C bus is a serial bus with a clock and a data input. General function and bus protocol are specified in the Philips-bus data sheets. The interface (Data and Clock) is TTL-compatible. Spikes up to 50 ns are filtered by an integrator and the maximum clock speed is limited to 100 kHz.

The data line (SDA) can be used bidirectionally. In read mode, the IC sends reply information (1 byte) to the micro-processor.

The bus protocol prescribes a full-byte transmission in all cases. The first byte after the start condition is used to transmit the IC address (hexa 8C for write, 8D for read).

All bytes are sent MSB bit first and the write data transfer is closed by a stop.

#### 1.3 Write Mode

In write mode, the second byte contains the subaddress of the selected function to adjust (or controls to effect) and the third byte the corresponding data byte. More than one data byte can be sent to the IC. If after the third byte no stop or start condition is detected, the circuit automatically increments the momentary subaddress in the subaddress counter (auto-increment mode) by one. Thus it is possible to immediately transmit the following data bytes without sending the IC address or subaddress. This can be useful for reinitializing all the controls very quickly (flash manner). This procedure is ended with a stop condition.

There are 19 adjustment capabilities for the circuit: 3 for the horizontal part, 3 for the vertical, 3 for the E/W correction, 2 for the dynamic horizontal phase control, 7 for the preamplifier and 1 for the blanking DC. 14 bits are also dedicated to several controls (ON/OFF).

#### 1.4 Read Mode

In the read mode the second byte transmits the reply information. The reply byte contains the horizontal and vertical lock/unlock status, the XRAY activation status. A stop condition always stops all the activities of the bus decoder and switches both the data and clock line (SDA and SCL) to high impedance. See I<sup>2</sup>C subaddress and control tables.

#### 1.5 Sync Processor

The internal sync processor allows the device to receive separate horizontal & vertical TTL-compatible sync signals.

#### 1.6 IC Status

The IC informs the MCU about both the 1st horizontal PLL (locked or not) and the XRAY protection (activated or not). The XRAY internal latch is reset either directly via the  $I^2C$  interface or by decreasing the V<sub>CC</sub> supply.

#### **1.7 Sync Inputs**

Both HIN and VIN inputs are TTL compatible triggers with hysterisis to avoid erratic detection. Both inputs include a pull-up resistor connected to  $V_{DD}$ . Synchro pulses must be positive.

#### 1.8 Sync Processor Output

The sync processor indicates whether 1st PLL is locked to an incoming horizontal sync or not. This is indicated on the D8 bit of the status register . PLL1 level is low when locked.

### 2. HORIZONTAL PART

#### 2.1 Internal Input Conditions

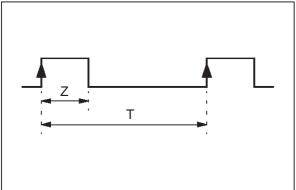

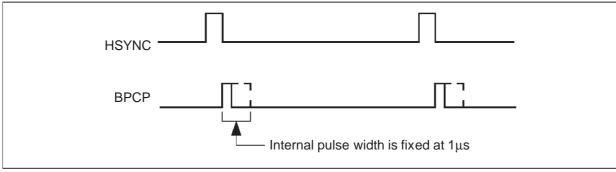

A digital signal (horizontal sync pulse) is sent by the sync processor to the horizontal input. It must be positive (see Figure 4).

Synchronization occurs on the leading edge of the internal sync signal.

The minimum value of Z is 0.7  $\mu$ s.

Vertical synchro extraction is not allowed.

#### Figure 4.

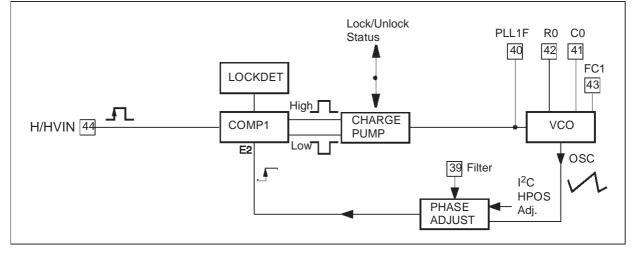

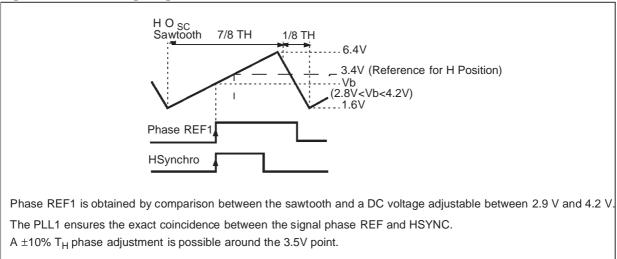

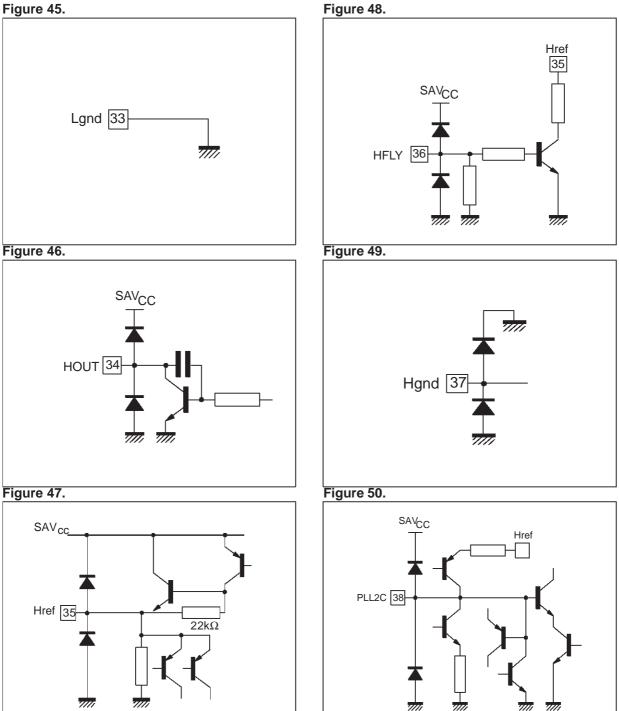

### 2.2 PLL1

57

The PLL1 consists of a phase comparator, an external filter and a voltage-controlled oscillator (VCO). The phase comparator is a "phase frequency" type designed in CMOS technology. This kind of phase detector avoids locking on wrong

#### Figure 6. Block Diagram