# STV9936P/S

# 120-MHz On-Screen Display for Monitors with 4 True Independent Window Displays

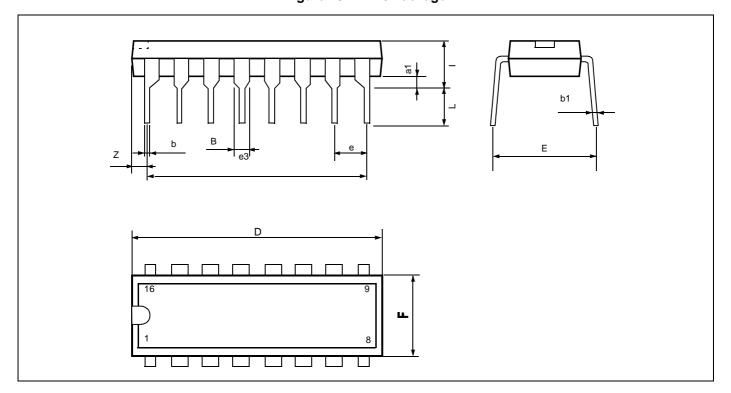

PDIP16 (Plastic Dual In line Package)

ORDER CODE: STV9936P

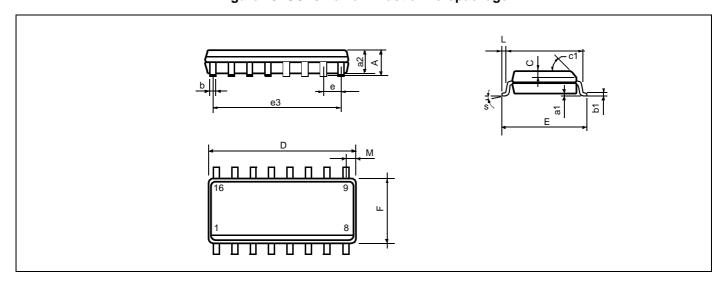

SO16 Narrow (Plastic Micropackage)

ORDER CODE: STV9936S

#### **Main Features**

- Horizontal frequency up to 150 kHz

- On-chip Pixel Clock Generator from 7.68 MHz to 120 MHz, without crystal oscillator

- 16-pin Narrow SO or DIP packages

- Programmable horizontal resolutions from 384 to 1524 dots per scan line

- 4 independent windows all with character display

- Overlapping windows with automatic control of display priorities and scrolling menu effects

- Independent and programmable displays, positions and sizes for each window

- Transparent or 8 programmable background colors for each window

- Window size up to 16 rows of 32 characters

- Each window has its own bordering or shadowing effects with programmable color, height and width

- Each window can be separately erased

- Programmable common positioning to easily control centered display

- 256 standard and 16 multi-color characters or graphic fonts in ROM. Character fonts can be customized using a mask-programmable ROM

#### ■ Characters

- Common character height and row space.

Character height from 18 to 127 lines and space lines from 0 to 62 split above and below character rows

- 12 x 18 dot matrix per character

- Display of up to 704 characters

- Programmable shadow/border effects for characters in each separate window

- 32 programmable background, foreground, blinking character colors for each character (8 possibilities per window)

- 8 selectable colors for standard characters

- Transparent and 8 selectable colors for background

#### ■ On-Screen Effects

- Fade-in/Fade-out effects

- Possibility of full-screen display with a selectable color

- I<sup>2</sup>C interface for microcontrollers with slave address BA(h) in Read and Write modes

# **Table of Contents**

| Chapter 1 | General Description                                                                                                                                                                          | 5              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1       | Pin Description                                                                                                                                                                              | 7              |

| Chapter 2 | Register Addressing                                                                                                                                                                          | 8              |

| 2.1       | I <sup>2</sup> C Protocol                                                                                                                                                                    | 8              |

|           | 2.1.1 Data to Write                                                                                                                                                                          |                |

| 2.2       | Format Changing                                                                                                                                                                              | 10             |

| 2.3       | Read Mode                                                                                                                                                                                    | 11             |

| 2.4       | Addressing Map                                                                                                                                                                               | 11             |

| Chapter 3 | Window Specifications                                                                                                                                                                        | 12             |

| 3.1       | Enable Display                                                                                                                                                                               | 13             |

| 3.2       | Origin Positions for the 4 Windows  3.2.1 General Horizontal Delay (HD)  3.2.2 General Vertical Delay (VD)                                                                                   | 13             |

| 3.3       | Window Positions in the Frame                                                                                                                                                                | 14             |

| 3.4       | Window Size: Number of Character Rows and Character Columns                                                                                                                                  | 15             |

| 3.5       | Window Background Color                                                                                                                                                                      | 16             |

| 3.6       | Window Bordering and Shadowing Effects  3.6.1 Enable Bordering or Shadowing Effects  3.6.2 Bordering or Shadowing Selection  3.6.3 Border or Shadow Color  3.6.4 Bordering or Shadowing Size | 16<br>16<br>17 |

| 3.7       | Window Display Priority Management                                                                                                                                                           | 18             |

| Chapter 4 | Character Specifications                                                                                                                                                                     | 19             |

| 4.1       | General Description                                                                                                                                                                          | 19             |

| 4.2       | Horizontal Resolution                                                                                                                                                                        | 19             |

| 4.3       | Character Height                                                                                                                                                                             | 19             |

### STV9936P/S

| 4.4        | Row Height (Space Lines)              | 20 |

|------------|---------------------------------------|----|

| 4.5        | Character Colors                      | 21 |

|            | 4.5.1 Character Background Color      |    |

|            | 4.5.2 Character Color                 |    |

| 4.6        | Multicolor Characters                 | 23 |

| 4.7        | Character Shadowing                   | 23 |

| 4.8        | Character Font                        | 25 |

| Chapter 5  | RAM Specification                     | 28 |

| 5.1        | Character Coding                      | 28 |

| 5.2        | Window Memory Allocation              | 28 |

| 5.3        | Memory Size Allocation                | 28 |

| 5.4        | Window Reset                          | 30 |

| Chapter 6  | Pixel Clock Generator                 | 31 |

| Chapter 7  | General OSD Programming               | 32 |

| 7.1        | Enable OSD                            | 32 |

| 7.2        | Fade-in and Fade-out Effect           | 32 |

| 7.3        | Full Screen Display                   | 32 |

| 7.4        | Signal Polarity and Triggering        | 33 |

| 7.5        | Reset                                 | 34 |

| Chapter 8  | Registers                             | 35 |

| 8.1        | Register Specification                | 35 |

| Chapter 9  | Application Hints                     | 38 |

| 9.1        | Software Hints                        | 38 |

|            | 9.1.1 Programming Recommendations     |    |

| 9.2        | Hardware Hints                        |    |

| 3.2        | Tiaraware Firites                     |    |

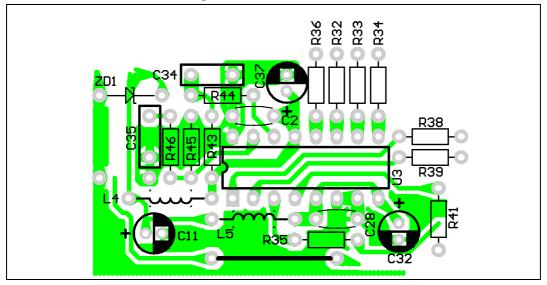

| Chapter 10 | Application Diagrams                  |    |

| Chapter 11 | Electrical and Timing Characteristics | 42 |

| 11.1       | Absolute Maximum Ratings              | 42 |

| 11.2       | Operating Conditions                  | 42 |

|            |                                       |    |

| Chanter 13 | Revision History                      | 47 |

|------------|---------------------------------------|----|

| 12.2       | Dual In-line Plastic Package          | 45 |

| 12.1       | SO16 Narrow Plastic Micropackage      | 44 |

| Chapter 12 | Package Mechanical Data               |    |

|            | -                                     |    |

| 11.3       | Electrical and Timing Characteristics | 42 |

### 1 General Description

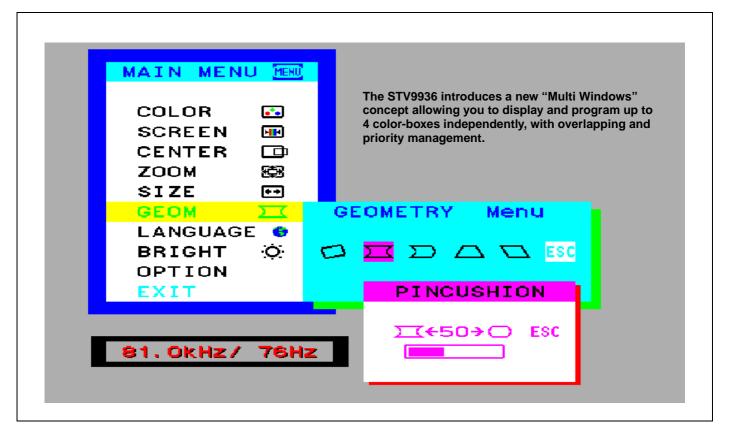

The STV9936 is a new On-Screen Display (OSD) device with multiple menu displays for monitor applications.

In addition to the standard features of an OSD, the special features of the STV9936 are listed below:

- Simultaneous display of up to 4 menus anywhere on the screen. Each of the 4 independent windows, all displaying characters, can be overlapped and display priorities are automatically controlled. Window sizes and positions are independently programmable as well as scrolling menu effects.

- Programming of the general OSD and of the 4 windows is controlled by an I<sup>2</sup>C bus in Read and Write modes, to suit the various CRT displays.

- Associated with an easily programmable character height, the internal PLL generates the

programmable pixel clock, without using a crystal oscillator, that defines the character width

making the device suitable for multi-sync applications.

- A maximum of 704 characters, defined in the mask-programmable ROM, are distributed among the 4 windows and displayed simultaneously.

Figure 1: Multi-window Concept with Character Display

General Description STV9936P/S

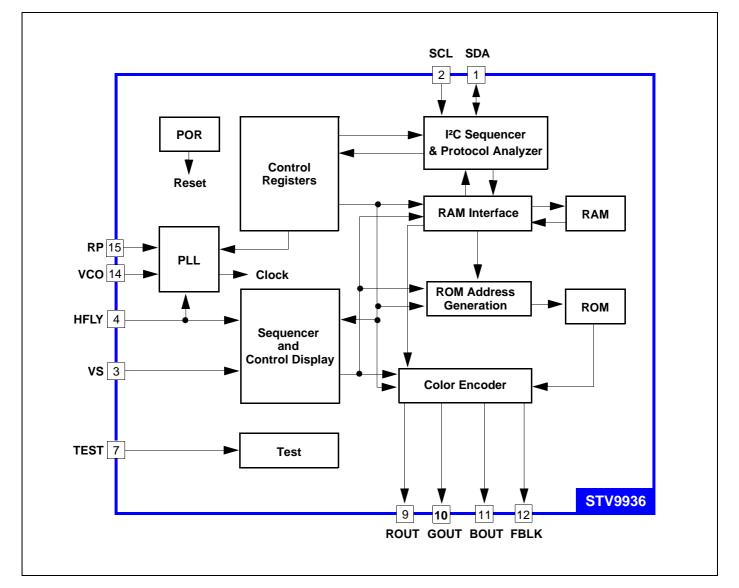

Figure 2: STV9936 Block Diagram

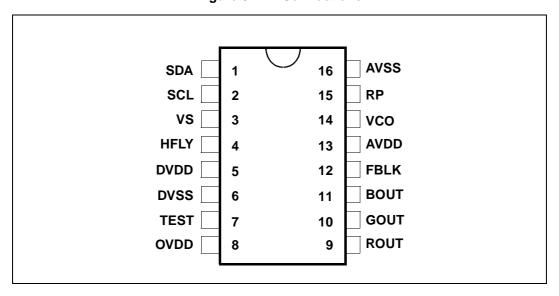

# 1.1 Pin Description

**Figure 3: Pin Connections**

**Table 1: Pin Descriptions**

| N° | Pin Name | Direction | Digital/<br>Analog | Function                              |

|----|----------|-----------|--------------------|---------------------------------------|

| 1  | SDA      | I/O       | Digital            | Serial Data of I <sup>2</sup> C bus   |

| 2  | SCL      | Input     | Digital            | Serial Clock of I <sup>2</sup> C bus  |

| 3  | vs       | Input     | Digital            | Vertical Synchronization Input        |

| 4  | HFLY     | Input     | Digital            | Horizontal Synchronization Input      |

| 5  | DVDD     | -         | Supply             | Digital Power Supply                  |

| 6  | DVSS     | -         | Supply             | Digital Ground                        |

| 7  | TEST     | Input     | Digital            | Remains at 0 (for test purposes only) |

| 8  | OVDD     | -         | Supply             | Digital Power Supply                  |

| 9  | ROUT     | Output    | Digital            | Red Color Output                      |

| 10 | GOUT     | Output    | Digital            | Green Color Output                    |

| 11 | BOUT     | Output    | Digital            | Blue Color Output                     |

| 12 | FBLK     | Output    | Digital            | Fast Blanking Output                  |

| 13 | AVDD     | -         | Supply             | Analog Power Supply                   |

| 14 | vco      | I/O       | Analog             | for VCO                               |

| 15 | RP       | I/O       | Analog             | for VCO                               |

| 16 | AVSS     | -         | Supply             | Analog Ground                         |

# 2 Register Addressing

All control registers are located in Window 0, Row 0. All color-box data is located in Window 0, Row 2.

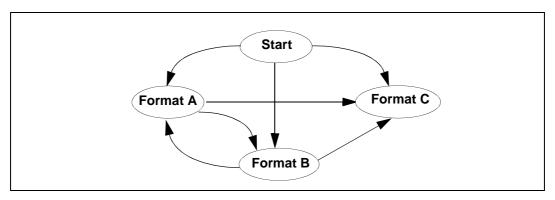

Three formats are available: A, B and C, as described in the I<sup>2</sup>C protocol (see Section 2.1: I<sup>2</sup>C Protocol on page 8).

All addresses (FAC and FWR bytes) are based on Formats A or B, and are written in hexadecimal format.

Data in Window 0, Row 1 is reserved. DO NOT write to this location.

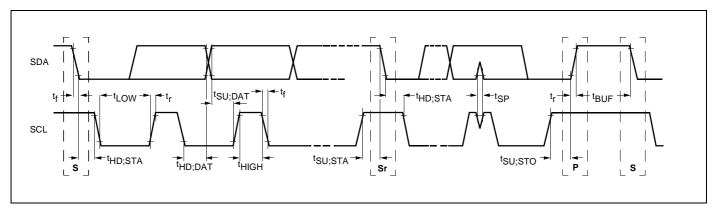

#### 2.1 I<sup>2</sup>C Protocol

The serial interface with the microcontroller is an I<sup>2</sup>C bus with 2 wires: SCL and SDA. The OSD is a slave circuit with 2 modes: Write and Read.

#### 2.1.1 Data to Write

In the OSD, the I2C bus is used to write - read:

- the control data

- the character codes and their respective color codes

- the color-boxes (8 color-boxes per window).

A color-box contains the character color, character background color and blink data. There are 8 color-boxes for each OSD window which are used to define the colors available for all the characters of the given OSD window. 3 bits are required to code the 8 color-boxes. These bits are the color code.

For more information, refer to Section 4.5: Character Colors on page 21.

Each character code is related to its own window, row and column. Consequently, the protocol of the I<sup>2</sup>C transmission includes this information (window, row and column) to define the position of the character on the screen. These 3 pieces of information about the position are transmitted in 2 bytes.

As each character on the screen has its own color code, the same protocol is used to write all the color codes and character codes. Only the bit called 'A' allows you to distinguish the character codes from the color codes corresponding to 1 position on the screen.

The control data is also written with the same protocol using windows, rows and columns. Window 0 is reserved for control data and color boxes.

#### 2.1.2 Transmission Formats

There are 3 transmission formats to suit the amount of data to update. The transmission format is coded in the "window/row/column" bytes.

Format A is suitable for updating small amounts of data which are allocated to different window, row and column addresses.

Format B is recommended for updating data for the same window and the same row address, but with a different column address and when changing the Character/Color-code attribute (bit A), or when writing to a different I<sup>2</sup>C control register.

Format C is appropriate for updating large amounts of data from a full window or full screen. The window, row and column addresses are incremented automatically when this format is applied. Data is written to fill all the allocation memory of the windows.

The transmission formats are as follows:

- 1. Format A: S-FWR-FAC-D → FWR-FAC-D → FWR-FAC-D...Stop

- 2. Format B: S-FWR-FAC-D  $\rightarrow$  FAC-D  $\rightarrow$  FAC-D  $\rightarrow$  FAC-D...Stop

- 3. Format C: S-FWR-FAC-D  $\rightarrow$  D  $\rightarrow$  D  $\rightarrow$  D...Stop

#### Where:

**S** = Slave address = BAh

FWR = Format, Window and Row address

**FAC** = Format, Attribute and Column address

**D** = Control data, Color codes (3 bits) or Character codes (8 bits).

In Format C, the order of automatic incrementation for data D is first the column value, then the row value, and then the window value.

Table 2: Various Bytes coded in the I<sup>2</sup>C Transmission

| Byte                               | Bit 7 | Bit 6  | Bit 5 | Bit 4             | Bit 4 Bit 3 Bit 2 Bit 1 |        |  |  |  |

|------------------------------------|-------|--------|-------|-------------------|-------------------------|--------|--|--|--|

| FWR                                | 1     | W[2:0] |       |                   |                         | R[3:0] |  |  |  |

| FAC                                | 0     | F      | Α     | C[4:0]            |                         |        |  |  |  |

| D: Control Data (in window 0 only) |       |        |       | D[7               | ':0]                    |        |  |  |  |

| D: Color Code                      | 0     | 0      | 0     | 0 0 <b>D[2:0]</b> |                         |        |  |  |  |

| D: Character Code                  |       |        |       | D[7               | ':0]                    |        |  |  |  |

#### 2.1.3 Format, Window and Row Address (FWR)

Bit 7 indicates the 'Window & Row' byte when set to 1.

W[2:0]: Window Number

000: Control Data and Color boxes

001: Window 1 010: Window 2 011: Window 3 100: Window 4

R[3:0]: Row Number from 0 to 15. Each window has a maximum number of 16 rows.

#### 2.1.4 Format, Attribute and Column Address (FAC)

Bit 7 indicates the 'Attribute & Column' byte when set to 0.

F: Format

0: Format A or B

1: Format C

A: Transmission of character code or color code

0: Character Code

#### 1: Color Code

When reading or writing control data and/or color boxes, bit A must be set to 0. For Character codes, A must be set to 1.

#### C[4:0]: Column Number

There are 32 possible columns.

00000: 1 column 11111: 32 columns

#### 2.1.5 Control Data, Color Codes or Character Codes (D)

Color codes are stored on 3 bits. Control data and Character codes are stored on 8 bits.

### 2.1.6 Configuration of Transmission Formats

**Table 3: Configuration of Transmission Formats**

|                               |                  | Byte | Format    | Bit 7 | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|-------------------------------|------------------|------|-----------|-------|------------|--------|--------|--------|--------|-------|-------|

| Address bytes                 | Windows & Rows   | FWR  | A, B or C | 1     |            | W[2:0] | R[3:0] |        |        |       |       |

| for Characters                | Column (A and B) | FAC  | A or B    | 0     | 0          | 0      |        | C[4:0] |        |       |       |

| Codes                         | Column (C)       | FAC  | С         | 0     | 1          | 0      | C[4:0] |        |        |       |       |

|                               | Windows & Rows   | FWR  | A, B or C | 1     |            | W[2:0] | R[3:0] |        |        | 3:0]  |       |

| Address bytes for Color Codes | Column (A and B) | FAC  | A or B    | 0     | 0 1 C[4:0] |        |        |        |        |       |       |

|                               | Column (C)       | FAC  | С         | 0     | 1          | 1      |        |        | C[4:0] |       |       |

All formats must start with the S, FWR and FAC bytes.

All FAC values referred to in this datasheet correspond to transmission formats A or B.

### 2.2 Format Changing

#### To change from Format A to Format B

S-FWR[0]- FAC[0]-D[0]  $\rightarrow$  FWR[1]- FAC[1]- D[1]  $\rightarrow$  FWR[2]- FAC[2]- D[2]  $\rightarrow$  FAC[3]- D[3]  $\rightarrow$  FAC[4]- D[4]  $\rightarrow$  FAC[5]- D[5]...

The F bit from the FAC byte is always 0 in this case.

#### To change from Format A to Format C

$S \text{ - FWR[0]- FAC[0]- D[0]} \rightarrow \text{FWR[1]- FAC[1]- D[1]} \rightarrow \text{FWR[2]- FAC[2]- D[2]} \rightarrow \text{D[3]} \rightarrow \text{D[4]} \rightarrow \text{D[5]}...$

The "F" bit from the FAC byte is as follows:

#### To change from Format B to Format A

S - FWR[0]- FAC[0]-D[0]  $\rightarrow$  FAC[1]- D[1]  $\rightarrow$  FAC[2]-D[2]  $\rightarrow$  FWR[3]- FAC[3]- D[3]  $\rightarrow$  FWR[4]- FAC[4]- D[4]...

The F bit from the FAC byte is always 0 in this case.

#### To change from Format B to Format C

$S \text{ - FWR[0]- FAC[0]- D[0]} \rightarrow \text{FAC[1]- D[1]} \rightarrow \text{FAC[2]- D[2]} \rightarrow \text{D[3]} \rightarrow \text{D[4]}...$

The "F" bit from the FAC byte is as follows: F[0] = F[1] = "0" and F[2] = "1"

It is not possible to change from Format C back to Format A or B.

**Figure 4: Format Changing Sequences**

#### 2.3 Read Mode

The transmission format is shown as below:

Start - S(w) - FWR- FAC - Stop - Start - S(r) - D

$$\rightarrow$$

D  $\rightarrow$  D  $\rightarrow$  D...Stop

Where:

S(w) = Slave address in write mode = BAh = 10111010,

S(r) = Slave address in read mode = BBh = 10111011.

Registers and data in RAM are readable.

This mode is useful when developing OSD applications.

### 2.4 Addressing Map

**Table 4: Window Addressing Map**

| Window                | Row                       | Column                       | Data                        |

|-----------------------|---------------------------|------------------------------|-----------------------------|

| Window 0              | Row 0                     | Columns 0 to 31              | Control Data (8 bits)       |

| Window 0              | Row 1                     | Columns 0 to 31              | Reserved (Do Not Write)     |

| Window 0              | Row 2                     | Columns 0 to 31              | Color-boxes (8 bits)        |

| Windows 1, 2, 3 and 4 | Rows 0 to n (n = 15 max.) | Columns 0 to m (m = 31 max.) | Characters Coding (11 bits) |

# 3 Window Specifications

Four different independent windows with separate character displays can be simultaneously displayed on screen. It is possible to have overlapping windows with an automatic control of display priorities: downscale priorities from Window 4 to Window 1.

Window 1 is well-adapted for the OSD general menu.

The 4 windows, each with its own character display, can be positioned anywhere on the screen.

The following characteristics are defined for each window:

- Enable Display

- Position

- Size, adjustable with memory allocation

- Background Color

- Bordering or Shadowing effects with programmable color, height and width.

Axis HD

Origin

VD

Window 1

Window 3

Window 4

Figure 5: Example of Window Displays

### 3.1 Enable Display

The Enable Display command for each window is selected by bits ENW1, ENW2, ENW3 and ENW4. If the ENWi bit is set to 1, the corresponding window is displayed.

**Table 5: Enable Display**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 07h | 0h      |       |       |       |       | ENW4  | ENW3  | ENW2  | ENW1  |

### 3.2 Origin Positions for the 4 Windows

The 4 windows are arranged in a vertical frame whose origin coordinates are the horizontal delay (HD) and the vertical delay (VD) located at the upper left-hand corner of the monitor screen. When the HD and VD values are changed, the 4 windows within the frame position are automatically shifted by the same value. The origin (HD, VD) can be programmed anywhere on the screen. Adjusting the origin position is used to globally reposition the OSD windows.

The advantages of this system are easier programming, the possibility to adapt the position of all windows at a single time without changing the relative position of each window and the possibility for the user to program all 4 window positions.

#### 3.2.1 General Horizontal Delay (HD)

Table 6: Origin of Windows on Horizontal Axis: Horizontal Delay

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|---------|-------|-------|-------|

| 80h | 04h | 0h      |       |       |       |       | HD[6:0] |       |       |       |

The general horizontal delay defines the horizontal position of the origin coordinate for all four OSD windows. The horizontal delay is selected by bits HD[6:0]. A general horizontal offset is also applied:

General Horizontal Offset = 50 pixels – Phase Error Detection Pulse Width (in pixels)

The range of the horizontal delay is from 50 to 812 pixels, in steps of 6 pixels each.

General Horizontal Delay = HD[6:0] x 6 pixels + General Offset (in pixels)

The default value is 0h (left-hand side of the monitor screen).

#### 3.2.2 General Vertical Delay (VD)

Table 7: Origin of Windows on Vertical Axis: Vertical Delay

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 05h | 0h      |       |       |       | VD[   | [7:0] |       |       |       |

The general vertical delay defines the vertical position of the origin coordinate for all four OSD windows. The vertical delay is selected by bits VD[7:0]. A general vertical offset of 2 scan lines is also applied.

The range of the vertical delay is from 2 to 1022 scan lines, in steps of 4 scan lines each.

General Vertical Delay = VD[7:0] x 4 + 2

The default value is 0h (top of screen).

#### 3.3 Window Positions in the Frame

All values are referenced to the origin coordinates (HD, VD). For more information, refer to Figure 5 on page 12.

#### 3.3.1 Window Horizontal Delay

The window horizontal delay defines the horizontal start position for each separate OSD window. This value is selected by bits HDW1[6:0], HDW2[6:0], HDW3[6:0] and HDW4[6:0], respectively.

**Table 8: Window Horizontal Delay**

| FWR | FAC                   | Default             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|-----|-----------------------|---------------------|-------|-------|-------|-------|-----------|-------|-------|-------|

| 80h | 0Ch, 11h,<br>16h, 1Bh | 0h, 20h,<br>0h, 10h |       |       |       |       | HDWi[6:0] |       |       |       |

The range of the window horizontal delay is from 0 to 1524 pixels, in steps of 12 pixels each.

Window Horizontal Delay = HDWi[6:0] x 12 pixels

The total horizontal delay of a window is:

General Horizontal Delay + HDWi[6:0] x 12 pixels; or,

HD[6:0] x 6 pixels + HDWi[6:0] x 12 pixels + (50 pixels - Phase Error Detection Pulse Width).

The default values for the window horizontal delay for each of the four OSD windows is given in Table 8.

#### 3.3.2 Window Vertical Delay

The window vertical delay defines the vertical start position for each separate OSD window. This value is selected by bits VDW1[5:0], VDW2[5:0], VDW3[5:0] and VDW4[5:0], respectively.

**Table 9: Window Vertical Delay**

| FWR | FAC                   | Default           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 |

|-----|-----------------------|-------------------|-------|-------|-------|-------|-------|---------|-------|-------|

| 80h | 0Dh, 12h,<br>17h, 1Ch | 0h, 0h,<br>Ch, Ch |       |       |       |       | VDW   | /i[5:0] |       |       |

The range of the window vertical delay is from 0 to 63 rows of characters, in steps of 1 character row each. It is important to note that the height of each character row is defined by the row height parameter. For more information, refer to Section 4.4: Row Height (Space Lines) on page 20.

Window Vertical Delay = VDWi[5:0] x Row\_Height

The total vertical delay of a window is:

General Vertical Delay + VDWi[5:0] x Row\_Height (in scan lines); or, (VD[7:0] x 4 + 2) + VDWi[5:0] x Row\_Height (in scan lines).

The default values for the window vertical delay for each of the four OSD windows is given in Table 9.

#### 3.4 Window Size: Number of Character Rows and Character Columns

#### 3.4.1 Window Horizontal Size

The window horizontal size defines the number of characters displayed for character row for each separate OSD window. This value is selected by bits HSW1[4:0], HSW2[4:0], HSW3[4:0] and HSW4[4:0], respectively.

**Table 10: Window Horizontal Size**

| FWR | FAC                   | Default            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 |

|-----|-----------------------|--------------------|-------|-------|-------|-------|-------|-----------|-------|-------|

| 80h | 0Eh, 13h,<br>18h, 1Dh | 19h, 9h,<br>Fh, Fh |       |       |       |       |       | HSWi[4:0] |       |       |

The range of the window horizontal size is from 1 to 32 characters, in steps of 1 character each. Each character is 12 pixels long. There is an offset of 1 character.

Window Horizontal Size = HSWi[4:0] +1 characters

The default values for the window horizontal size for each of the four OSD windows is given in Table 10.

#### 3.4.2 Window Vertical Size

The window vertical size defines the number of character rows displayed for each separate OSD window. This value is selected by bits VSW1[3:0], VSW2[3:0], VSW3[3:0] and VSW4[3:0], respectively.

**Table 11: Window Vertical Size**

| FWR | FAC                   | Default           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|-----|-----------------------|-------------------|-------|-------|-------|-------|-------|-------|---------|-------|

| 80h | 0Fh, 14h,<br>19h, 1Eh | Bh, 4h,<br>7h, 7h |       |       |       |       |       | VSW   | 'i[3:0] |       |

The range of the window vertical size is from 1 to 16 character rows, in steps of 1 character row each. It is important to note that the height of each character row is defined by the row height parameter. For more information, refer to Section 4.4: Row Height (Space Lines) on page 20. There is an offset of 1 character row.

Window Vertical Size = (VSWi[3:0] + 1) x Row\_Height (in scan lines)

Row\_Height = Character\_Height + 2 x Space\_Lines

The default values for the window vertical size for each of the four OSD windows is given in Table 11.

Table 12 shows an example of the origin and size of windows based on the example shown in Figure 5,

**Table 12: Example of Origin and Size of Windows**

| Window i | HD | VD | HSWi | VSWi |

|----------|----|----|------|------|

| Window 1 | 0  | 2  | 7    | 4    |

| Window 2 | 5  | 0  | 4    | 5    |

| Window 3 | 6  | 4  | 6    | 3    |

| Window 4 | 3  | 7  | 4    | 4    |

### 3.5 Window Background Color

The window background color for each separate OSD window is coded over 4 bits as shown in Table 13. The first bit (Ti) specifies whether the background is transparent or if a color is displayed.

If the background is transparent (Ti = 1), the active video is displayed as background.

If a color is displayed (Ti = 0), the background color for each separate OSD window is coded over the last three bits (RWi, GWi and BWi, respectively). Windows are displayed with a white background by default (7h).

**Table 13: Background Color of Each Window**

| FWR | FAC                  | Default           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------------------|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 10h, 15h<br>1Ah, 1Fh | 7h, 7h,<br>7h, 7h |       |       |       |       | Ti    | RWi   | GWi   | BWi   |

### 3.6 Window Bordering and Shadowing Effects

#### 3.6.1 Enable Bordering or Shadowing Effects

Bordering or shadowing effects are enabled for each separate OSD window by bits ENBS1, ENBS2, ENBS3 and ENBS4, respectively.

#### 3.6.2 Bordering or Shadowing Selection

Either the bordering or the shadowing effect is selected for each separate OSD window by bits BSW1, BSW2, BSW3 and BSW4, respectively.

**Table 14: Bordering and Shadowing Parameter Selection**

| Bit   | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| ENBSi | No Bordering, No Shadowing (Default Value)     Bordering or Shadowing is selected. |

| BSWi  | Bordering is selected (Default Value)     Shadowing is selected.                   |

**Table 15: Enable Bordering or Shadowing Effects**

| FWR | FAC                  | Default           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------------------|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 07h                  | 0h                | ENBS4 | ENBS3 | ENBS2 | ENBS1 |       |       |       |       |

| 80h | 10h, 15h<br>1Ah, 1Fh | 0h, 0h,<br>0h, 0h |       |       |       | BSWi  |       |       |       |       |

#### 3.6.3 Border or Shadow Color

The border or shadow color is separately programmable for each separate OSD window. This value is selected by bits WSRi, WSGi and WSBi for each of the four OSD windows. The value for each color is shown in Table 17.

**Table 16: Border or Shadow Color**

| FWR | FAC                  | Default           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------------------|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 10h, 15h<br>1Ah, 1Fh | 0h, 0h,<br>0h, 0h | WSRI  | WSGI  | WSBI  |       |       |       |       |       |

Table 17: Bordering and Shadowing Color Selection (WSRGBi)

| Value | Color           | Value | Color   |

|-------|-----------------|-------|---------|

| 000   | Black (Default) | 100   | Red     |

| 001   | Blue            | 101   | Magenta |

| 010   | Green           | 110   | Yellow  |

| 011   | Cyan            | 111   | White   |

#### 3.6.4 Bordering or Shadowing Size

The size of the bordering or shadowing width is separately programmable for each separate OSD window. This value is selected by bits BSWWi[2:0] for each of the four OSD window. The width size is from 0 to 14 pixels, in steps of 2 pixels each.

Width Size = BSWWi[2:0] x 2 pixels

The size of the bordering or shadowing height is selected by bits BSHWi[3:0] for each of the four windows. The height size is from 0 to 30 lines, in steps of 2 scan lines each.

Height Size = BSHWi[3:0] x 2 scan lines.

Table 18: Bordering or Shadowing Size

| FWR | FAC                  | Default           | Bit 7      | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|----------------------|-------------------|------------|------------|-------|-------|-------|-------|-------|-------|

| 80h | 0Eh, 13h<br>18h, 1Dh | 0h, 0h,<br>0h, 0h |            | BSWWi[2:0] | 1     |       |       |       |       |       |

| 80h | 0Fh, 14h<br>19h, 1Eh | 0h, 0h,<br>0h, 0h | BSHWi[3:0] |            |       |       |       |       |       |       |

M pixels

N scan lines

Window Shadowing

N scan lines

M pixels

M pixels

Figure 6: Illustration of Window Bordering and Shadowing Effects

### 3.7 Window Display Priority Management

The OSD windows are displayed with the following priority: Window 4 (top), 3, 2 and 1 (bottom).

This order of priority is shown the example given in Figure 7.

Axis HD

Origin

VD

Window 1

Window 3

Window 4

Figure 7: Example of Window Displays

# 4 Character Specifications

#### 4.1 General Description

There are:

- 256 monochrome characters and 16 multi-color characters in ROM

- 32 to 127 characters per line

- character height varies between 18 and 127 scan lines

- 0 to 62 scan space lines between character rows, with the same number of lines above and below the rows of characters.

With the possibility to select:

- blinking effect for each character

- shadowing effect for characters in each window

- background and foreground character colors: for each character, among a Color-shop of 8

Color-boxes per window. There is a Color-shop for each window. The Color-boxes define the

background colors and the foreground character colors and blinking effect.

#### 4.2 Horizontal Resolution

**Table 19: Horizontal Resolution**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|---------|-------|-------|-------|

| 80h | 01h | 20h     |       |       |       |       | HR[6:0] |       |       |       |

The horizontal resolution defines the number of pixels per line expressed in characters unit. This value is selected by bits HR[6:0].

The range of the horizontal resolution is from 32 to 127 characters, in steps of one character. The default value is 32 characters per line (20h). If bits HR[6:0] are programmed with a value less than 32, the horizontal resolution will be 32 characters per line (minimum value).

HR[6:0] = Number of characters per line

It is important that the maximum pixel frequency must be respected ( $f_{PIXEL}$  = 120 MHz maximum). As each character is 12 pixels long, the number of pixels per line varies from 384 to 1524. For more information, refer to Section 6: Pixel Clock Generator on page 31.

### 4.3 Character Height

**Table 20: Vertical Character Height**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|---------|-------|-------|-------|

| 80h | 02h | 12h     |       |       |       |       | CH[6:0] |       |       |       |

The vertical height defines the number of scan lines used to display the characters. This value is selected by bits CH[6:0].

The range of the vertical height is from 18 to 127 lines.

CH[6:0] = Number of scan lines used to display the characters

The characters stored in ROM are coded on 18 lines. If bits CH[6:0] are programmed with a value less than 18, the characters will be automatically displayed with a height of 18 scan lines (minimum value).

When a multiple of 18 scan lines are displayed, all ROM lines are repeated N number of times, with N in the range of 1 to 7, so as not to exceed the display of 127 scan lines. For example, if CH[6:0] = 36, each ROM line is repeated twice.

If the number of scan lines displayed is not a multiple of 18, certain ROM lines are repeated more often than others, as shown in Table 21. For example, if CH[6:0] = 40, each ROM line is repeated twice and ROM lines 3, 7, 10 and 14 are repeated three times.

Table 21 shows which ROM lines, from 0 to 17, are repeated depending on the CH[6:0] value.

**CH Value** Α 0 1 2 3 5 6 8 10 11 12 13 14 15 16 17 18, 36, 54, 72, 90, 108, 126 0 19, 37, 55, 73, 91, 109, 127 1 R 20, 38, 56, 74, 92, 110, 2 R R 21, 39, 57, 75, 93, 111 3 R R R 22, 40, 58, 76, 94, 112 4 R R R R 23, 41, 59, 77, 95, 113 5 R R R R R 6 R 24, 42, 60, 78, 96, 114 R R R R R 7 R R 25, 43, 61, 79, 97, 115 R R R R R 26, 44, 62, 80, 98, 116 8 R R R R R R R R 9 R R R 27, 45, 63, 81, 99, 117 R R R R R R 28, 46, 64, 82, 100, 118 10 R R R R R R R R R R 29, 47, 65, 83, 101, 119 11 R R R R R R R R R R R 30, 48, 66, 84, 102, 120 12 R R R R R R R R R R R R 31, 49, 67, 85, 103, 121 13 R R R R R R R R R R R R R 32, 50, 68, 86, 104, 122 14 R R R R R R R R R R R R R R 33, 51, 69, 87, 105, 123 R R R R R R R R R R R R R R R 15 34, 52, 70, 88, 106, 124 R R 16 R R R R R R R R R R R R R R 35, 53, 71, 89, 107, 125 17 R R R R R R R R R R R R R R R R R

Table 21: Repeated ROM Lines<sup>1</sup>

### 4.4 Row Height (Space Lines)

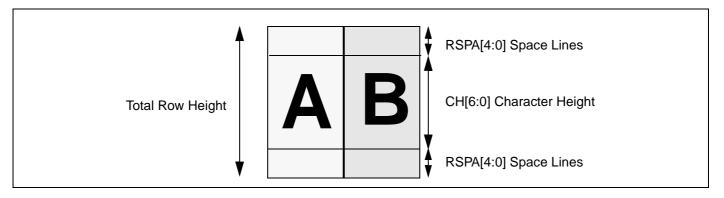

The row height defines the number of scan lines above and below each character row. This value is selected by bits RSPA[4:0]. The total row height is defined as follows:

Row\_Height = Character\_Height + 2 x Space\_Lines (see Figure 8)

<sup>1. &#</sup>x27;R' = Repeated ROM lines

<sup>&#</sup>x27;A' = Number of additional repeated lines

The range of spacing lines for the row height is from 0 to 31 scan lines, in steps of one scan line each. Accordingly, the number of scan lines between each character row is multiplied by two; the bottom space line of a given character row being added to the top space line of the following character row. The default value is 0 scan lines.

The space lines are displayed in the color of the associated character background.

Table 22: Row Height (Space Lines)

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-----------|-------|-------|-------|-------|

| 80h | 03h | 0h      |       |       |       | RSPA[4:0] |       |       |       |       |

Figure 8: Row Height Definition

#### 4.5 Character Colors

The colors for the characters, character background and blinking effect are separately programmable for each OSD window. The color values are stored in a color-shop of 8 color-boxes for each window. There are 4 color-shops, 1 per window, offering the user 32 possibilities of character coloring.

As the color-boxes are in RAM, the user must write to the color-box prior to using it.

Color-box data is stored in Window 0, Row 2. For more information, refer to Section 2.4: Addressing Map on page 11.

Table 23: color-box

| FWR | FAC           | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|---------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 82h | 00h to<br>1Fh |         | ВС    | BR    | BG    | ВВ    | BLINK | FR    | FG    | FB    |

#### 4.5.1 Character Background Color

A character background color can be separately programmed for each of the four color-boxes. This value is selected by bits BC, BR, BG and BB.

Bit BC is used to define if a specific character background color will be displayed or if the character background color is the color of the window background.

If a specific character background color is selected in a color box, the character background color is selected by bits BR, BG and BB.

**Table 24: Character Background Color**

| Color                                | вс | BR | BG | ВВ |

|--------------------------------------|----|----|----|----|

| Black                                | 1  | 0  | 0  | 0  |

| Blue                                 | 1  | 0  | 0  | 1  |

| Green                                | 1  | 0  | 1  | 0  |

| Cyan                                 | 1  | 0  | 1  | 1  |

| Red                                  | 1  | 1  | 0  | 0  |

| Magenta                              | 1  | 1  | 0  | 1  |

| Yellow                               | 1  | 1  | 1  | 0  |

| White                                | 1  | 1  | 1  | 1  |

| Window Background Color <sup>1</sup> | 0  |    |    |    |

<sup>1.</sup> See Table 25

**Table 25: Background Color Priority**

| ВС | TI | Background Color                           |

|----|----|--------------------------------------------|

| 1  | Х  | Character Background Color (BR, BG and BB) |

| 0  | 0  | Window Background Color (RGBWi)            |

| 0  | 1  | Transparent Background (Video active)      |

#### 4.5.2 Character Color

A character color can be separately programmed for each of the color-boxes. This value is selected by bits FR, FG and FB.

**Table 26: Character Colors**

| Color   | FR | FG | FB |

|---------|----|----|----|

| Black   | 0  | 0  | 0  |

| Blue    | 0  | 0  | 1  |

| Green   | 0  | 1  | 0  |

| Cyan    | 0  | 1  | 1  |

| Red     | 1  | 0  | 0  |

| Magenta | 1  | 0  | 1  |

| Yellow  | 1  | 1  | 0  |

| White   | 1  | 1  | 1  |

#### 4.5.3 Character Blinking Effect

A character blinking effect can be programmed for each of the color boxes. This value is selected by the BLINK bit. When this bit is set to 1, the blinking effect is enabled and the characters blink.

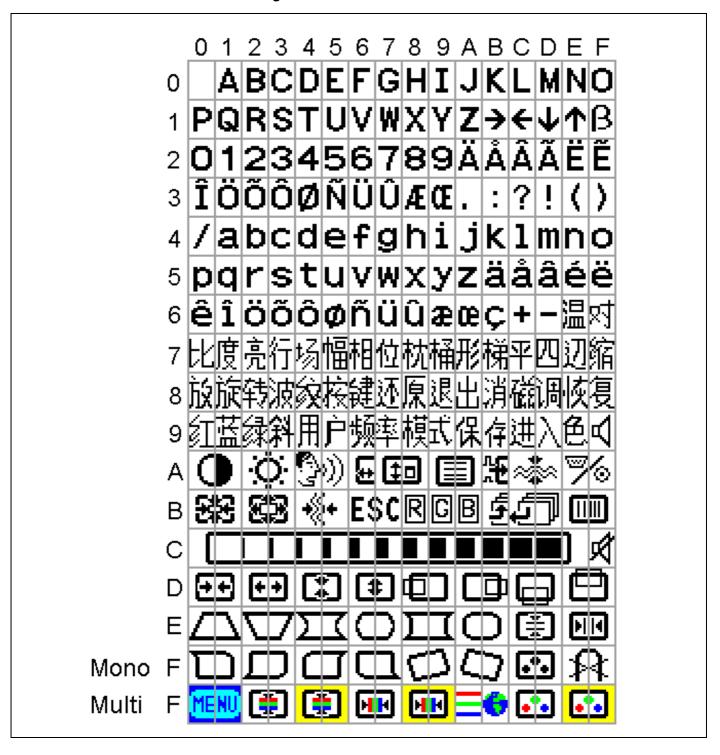

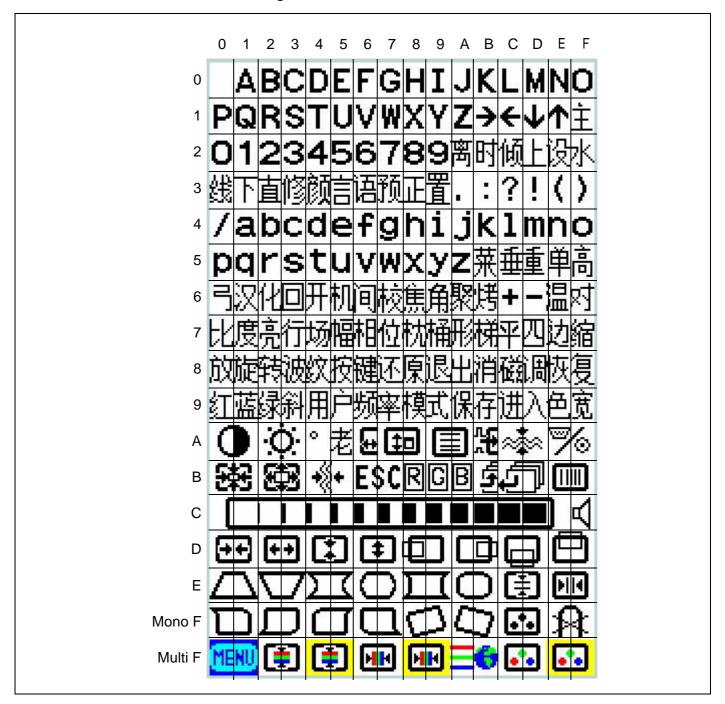

#### 4.6 Multicolor Characters

16 multicolor characters can be separately programmed for each of the color-boxes. These special characters are stored in the character font (see Figure 10) and are selected by bits MCOLOR[3:0].

MCOLOR[3] for Window 4

MCOLOR[2] for Window 3

MCOLOR[1] for Window 2

MCOLOR[0] for Window 1

If the MCOLOR bit is set to 0 for a specific color-box, the 256 monochrome ROM characters from \$00 to \$FF are available (default value).

If the MCOLOR bit is set to 1, the 240 monochrome ROM characters from \$00 to \$EF and the 16 multicolor characters from \$F0 to \$FF are available.

No shadowing effects on multicolor characters.

No background effects on multicolor characters.

Blinking on multicolor characters: background color coded in the associated color-box.

**Table 27: Multicolor Characters**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|---------|-------|-------|-------|-------|-------|

| 80h | 08h | 0h      |       | MCOL  | OR[3:0] |       |       |       |       |       |

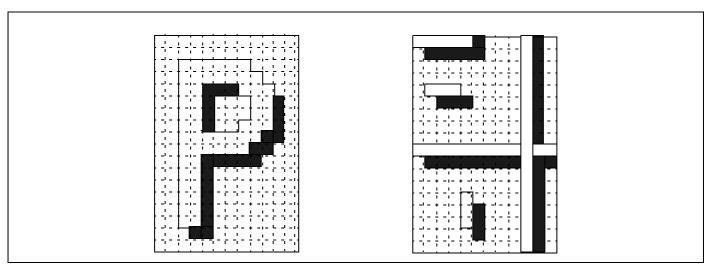

### 4.7 Character Shadowing

A character shadowing effect can be separately programmed for each of the four color-boxes. This value is selected by bits CSHA[3:0], respectively. The shadowing color is black.

When this bit is set to 1, the characters of the corresponding OSD window are displayed with a shadowing effect, as shown in Figure 9. The default value is 0 (no shadowing effect).

Figure 9: Character Shadowing

#### **Table 28: Character Shadowing**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------|-------|--------|-------|

| 80h | 08h | 0h      |       |       |       |       |       | CSH   | A[3:0] |       |

#### 4.8 Character Font

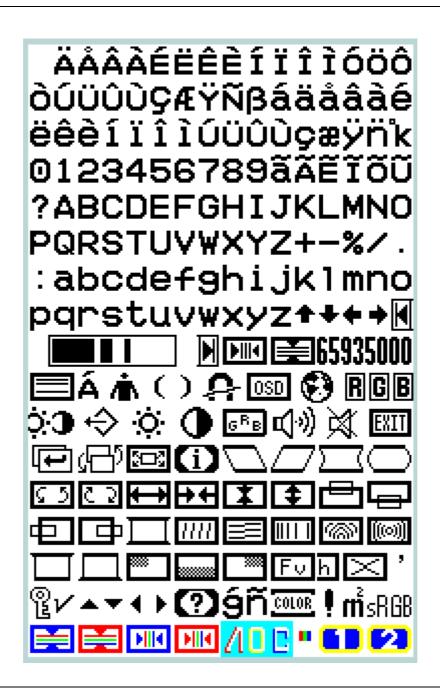

Figure 10 shows the available character font stored in ROM. For more information concerning the display of mono- or multi-color characters, refer to Section 4.6: Multicolor Characters.

Figure 10: /AA Character Fonts

Figure 11: /AB Character Fonts

Figure 12: /AC Character Fonts

RAM Specification STV9936P/S

# 5 RAM Specification

#### 5.1 Character Coding

Each character to display is coded with 11 bits in the RAM with the following addressing method:

- Character Code: Bits RC[7:0] are used to address the ROM Code

- Color Code: Bits CB[2:0] are used to select 1 of the 8 color-boxes in the color shop of the corresponding OSD window.

**Table 29: Character Coding**

| FWR                 | FAC | Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| See Table 3 CB[2:0] |     | RC[7:0] |       |       |       |       |       |       |       |       |       |       |

### 5.2 Window Memory Allocation

The 4 OSD windows can be distributed differently. But the displayable windows will always contain a total of 22 blocks (1 block consists of 32 characters).

10 Blocks

Window 0

Color-boxes

Window 1

A Blocks

Window 2

Window 3

Window 4

Window 4

Figure 13: Window Memory Space

### 5.3 Memory Size Allocation

The total number of characters or spaces is up to 704 with a maximum window size of 16 rows of 32 characters.

The character codes of each window are allocated to a specific memory space. This memory space is programmable for each window. The window size must be less than or equal to its memory allocation. Any window size can be modified within its specific memory space, the other windows are not affected by this operation.

STV9936P/S RAM Specification

The user must reserve a memory space for the largest window. According to the example shown in Figure 5, the total number of characters/spaces are:

Table 30: Window Sizes

| Window   | Size |

|----------|------|

| Window 1 | 28   |

| Window 2 | 20   |

| Window 3 | 18   |

| Window 4 | 16   |

| Total    | 82   |

For example, to change the size of Window 3 from 3 rows of 6 characters to 5 rows of 4 characters, the resulting size is 20 characters. The number of rows increases and the number of characters per row decreases. The required memory is at least 20 characters.

Note: A space is considered as being a character.

The memory allocation is made by blocks of 32 characters.

The maximum size of a window is 16 rows of 32 characters, or 512 characters. This corresponds to 16 blocks of 32 characters.

1 block is reserved for the color-boxes (see Chapter 4: Character Specifications on page 19), leaving 22 blocks of 32 characters for character codes (704 characters maximum).

The RAM allocation for each window is coded in bits ALWi[3:0]. Window 4 memory allocation uses the remaining memory space.

**Table 31: Window RAM Allocation**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0 |

|-----|-----|---------|-------|-------|--------|-------|-----------|-------|--------|-------|

| 80h | 09h | 39h     |       | ALW   | 2[3:0] |       | ALW1[3:0] |       |        |       |

| 80h | 0Ah | 3h      |       |       |        |       |           | ALW:  | 3[3:0] |       |

The number of memory blocks allocated for window "i" is (ALWi +1), the range of allocation is 1 to 16 blocks of 32 characters. The total number of blocks is 22.

Note: If the user changes only 1 window allocation, the RAM addresses of the following windows change. Consequently we advise you to write the allocation when the windows are not displayed to avoid false images.

RAM Specification STV9936P/S

The default window RAM allocations are listed in Table 32.

**Table 32: Window RAM Default Values**

| ALWi | Default | Description                  |  |  |  |

|------|---------|------------------------------|--|--|--|

| ALW1 | 9h      | 320 Characters (10 blocks)   |  |  |  |

| ALW2 | 3h      | 3h 128 Characters (4 blocks) |  |  |  |

| ALW3 | 3h      | 128 Characters (4 blocks)    |  |  |  |

Window 1: 10 blocks of 32 words = 320 characters (ALW1 = 9).

Window 2: 4 blocks of 32 words = 128 characters (ALW2 = 3).

Window 3: 4 blocks of 32 words = 128 characters (ALW3 = 3).

Window 4: the remaining RAM (4 blocks = 128 characters).

#### 5.4 Window Reset

All the RAM data from one of the four OSD windows can be reset by writing to bits RESETW[3:0].

When the RESETW bit is set to 1,all the RAM data in the allocation memory space of the corresponding OSD window is reset. These bits are automatically cleared when the RAM allocation reset is finished.

All programmable registers are in Row 0 (Column i, Row 0).

**Table 33: RAM Allocation Enable and Reset**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------------|-------|-------|-------|

| 80h | 0Bh | 0h      |       |       |       |       | RESETW[3:0] |       |       |       |

STV9936P/S Pixel Clock Generator

### 6 Pixel Clock Generator

The Pixel Clock Generator is used to synchronize the display clock with the horizontal flyback (HFLY) signal. This generator is based on a PLL function used to perform correct jitter. The pixel frequency is defined with the horizontal line frequency and the horizontal resolution.

Pixel Frequency  $(f_{PIXEL}) = 12 \times HR[6:0] \times f_{HLINE}$

The VCO[1:0] value is used to select the appropriate curve partition of the VCO.

**Table 34: VCO Curve Partition**

| VCO Value (Binary) | VCO Curve Partition                                    |

|--------------------|--------------------------------------------------------|

| 00                 | 7.68 MHz < H <sub>PIXEL</sub> < 15 MHz (Default Value) |

| 01                 | 15 MHz < H <sub>PIXEL</sub> < 30 MHz                   |

| 10                 | 30 MHz < H <sub>PIXEL</sub> < 60 MHz                   |

| 11                 | 60 MHz < H <sub>PIXEL</sub> < 120 MHz                  |

**Table 35: VCO Range**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 00h | 0h      |       |       |       |       |       |       | VCO   | [1:0] |

# 7 General OSD Programming

#### 7.1 Enable OSD

The OSD window displays are enabled by the ENOSD bit.

ENOSD = 1: OSD window displays are active.

ENOSD = 0: OSD window displays are inactive. Pin FBLK = 0 and pins ROUT, GOUT and BOUT pins = 0 (bit RGBPOL is 0). The default value is 0.

Table 36: Enable OSD

| FWR | FAC | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 00h |       |       |       | ENOSD |       |       |       |       |

#### 7.2 Fade-in and Fade-out Effect

The Fade-in and Fade-out effect is used to progressively increase/decrease the OSD window to/ from its full size in just a few milliseconds. This effect is enabled by the FADE bit.

FADE = 1: Fade effect is active

FADE = 0: Fade effect is inactive (default value)

Table 37: Fade

| FWR | FAC | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 00h |       |       | FADE  |       |       |       |       |       |

### 7.3 Full Screen Display

The STV9936 allows a full screen display with a selectable color programmable by the FBK bit as follows:

FBK = 1: The video area is replaced by the color coded in bits FSR, FSG and FSB (full screen color values). Pin FBLK is always 1.

FBK = 0: Normal video mode whether or not the OSD menu is displayed. The default value of bit FBK is 0.

**Table 38: Full Screen Registers**

| FWR | FAC | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 80h | 01h | 0h      | FBK   |       |       |       |       |       |       |       |

| 80h | 03h | 0h      | FSR   | FSG   | FSB   |       |       |       |       |       |

**Table 39: Full Screen Colors**

| Color                 | FSR | FSG | FSB |

|-----------------------|-----|-----|-----|

| Black (Default Value) | 0   | 0   | 0   |

| Blue                  | 0   | 0   | 1   |

| Green                 | 0   | 1   | 0   |

**Table 39: Full Screen Colors (Continued)**

| Color   | FSR | FSG | FSB |

|---------|-----|-----|-----|

| Cyan    | 0   | 1   | 1   |

| Red     | 1   | 0   | 0   |

| Magenta | 1   | 0   | 1   |

| Yellow  | 1   | 1   | 0   |

| White   | 1   | 1   | 1   |

### 7.4 Signal Polarity and Triggering

**Table 40: Signal Polarity**

| FWR | FAC | Default | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|-----|---------|--------|--------|-------|-------|-------|-------|-------|-------|

| 80  | 00  |         | FBKPOL | RGBPOL |       |       | VSP   | HSP   |       |       |

#### **Vertical Sync Triggering (VS input)**

The active edge of the VS pin used for vertical synchronization is selected by bit VSP.

VSP = 0: The falling edge is active. (Default Value)

VSP = 1: The rising edge is active.

#### **Horizontal Sync Triggering (HFLY input)**

The active edge of the HFLY pin used for horizontal synchronization is selected by bit HSP.

HSP = 0: The falling edge is active. (Default Value)

HSP = 1: The rising edge is active.

#### **RGB Output Polarity (ROUT, GOUT and BOUT outputs)**

The output polarity of pins ROUT, GOUT and BOUT is selected by bit RGBPOL.

RGBPOL = 0: RGB active at 1 (Default Value)

RGBPOL = 1: RGB active at 0

**Table 41: RGB Output Control**

| ENOSD Bit | RGBPOL Bit | RGB Outputs | Display |

|-----------|------------|-------------|---------|

| 1         | 0          | Active at 1 | OSD     |

| 1         | 1          | Active at 0 | OSD     |

| 0         | 0          | 000         | Video   |

| 0         | 1          | 111         | Video   |

#### **Fast Blanking Output Polarity (FBLK output)**

The output polarity of the FBLK pin is selected by bit FBLKPOL. The default value is 0.

**Table 42: Fast Blanking Output Polarity Selection**

| FBLKPOL | Description                                               |  |  |  |  |  |

|---------|-----------------------------------------------------------|--|--|--|--|--|

| 0       | When OSD display, FBLK = 1<br>When active video, FBLK = 0 |  |  |  |  |  |

| 1       | When OSD display, FBLK = 0<br>When active video, FBLK = 1 |  |  |  |  |  |

**Table 43: FBLK Output Control**

| ENOSD Bit | FBLKPOL Bit | FBK Bit | FBLK Output | Display |                  |

|-----------|-------------|---------|-------------|---------|------------------|

| 1         | 0           | 0       | 0           | Video   | Default Value    |

| 1         | 0           | 0       | 1           | OSD     | - Delault Value  |

| 1         | 0           | 1       | 1           | OSD     | Full Screen      |

| 1         | 1           | 0       | 0           | OSD     | FBLK Inverted    |

| 1         | 1           | 0       | 1           | Video   | - I BER Inverted |

| 1         | 1           | 1       | 0           | OSD     | Full Screen      |

| 0         | 0           | х       | 0           | Video   | No OSD           |

| 0         | 1           | х       | 1           | Video   | No OSD           |

#### 7.5 Reset

#### **Power On Reset**

The digital core and the PLL are asynchronously reset at Power On.

#### **Soft Reset**

A soft reset is enabled by the RST bit.

RST = 1: The digital core is reset. All control registers, except PLL registers, are reset at the same value as at power on reset.

It is not necessary to write RST = 0 to stop the reset. This bit is automatically cleared.

#### **PLL Register Reset**

The Pixel Clock Generator (VCO[1:0]) and Horizontal Resolution (HR[6:0]) bits are reset by the RST\_PLL bit.

RST\_PLL = 1: HR[6:0] and VCO[1:0] are reset to the same value as the power-on reset.

It is not necessary to write RST\_PLL = 0 to stop the reset. This bit is automatically cleared.

Table 44: Reset

| FWR | FAC | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|-----|-----|-------|-------|-------|-------|-------|-------|---------|-------|

| 80h | 06h |       |       |       |       |       |       | RST_PLL | RST   |

STV9936P/S Registers

# 8 Registers

### 8.1 Register Specification

Control registers are located at address in Window 0, Row 0.

Color-boxes are located at addresses in Window 0, Row 2. See Section 4.5 on page 21.

Character codes are located at addresses in Windows 1 to 4, as described in Section 5.1 on page 28.

**Table 45: Non-Displayable Window Register Mapping**

| Register            | Window | Row | FWR Code     |

|---------------------|--------|-----|--------------|

| Control Registers   | 0      | 0   | 80h          |

| Reserved            | 0      | 1   | DO NOT WRITE |

| Color-box Registers | 0      | 2   | 82h          |

Registers STV9936P/S

Table 46: Control Registers: Window 0, Row = 0

| FWR | FAC | Col | Default | Bit 7                                                                                              | Bit 6                                                         | Bit 5                | Bit 4                                       | Bit 3                                            | Bit 2                     | Bit 1                 | Bit 0 |  |

|-----|-----|-----|---------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------|---------------------------------------------|--------------------------------------------------|---------------------------|-----------------------|-------|--|

| 80h | 00h | 0h  | 0h      | <b>FBKPOL</b> = 0                                                                                  | RGBPOL = 0                                                    | <b>FADE</b> = 0      | ENOSD = 0                                   | <b>VSP</b> = 0                                   | <b>HSP</b> = 0            | <b>VCO[1:0]</b> = 00  |       |  |

| 80h | 01h | 1h  | 20h     | FBK = 0 HR[6:0] :Horizontal Resolution = 32 characters                                             |                                                               |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 02h | 2h  | 12h     | CH[6:0] = Character Height = 18                                                                    |                                                               |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 03h | 3h  | 0h      | full screen                                                                                        | RGB = FS RG                                                   | <b>B</b> = 000       | RSPA[4:0] = Row Spacing = 0                 |                                                  |                           |                       |       |  |

| 80h | 04h | 4h  | 0h      | HD[6:0] = Horizontal Delay Reference = 0 (50 pixels)                                               |                                                               |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 05h | 5h  | 0h      |                                                                                                    | VD[7:0] = Vertical Delay Reference = 0 (2 lines)              |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 06h | 6h  | 0h      |                                                                                                    |                                                               |                      |                                             |                                                  |                           | RST_PLL = 0           | RST = |  |

| 80h | 07h | 7h  | 0h      |                                                                                                    | ENBS4/3/2/                                                    | <b>/1</b> = 0000     |                                             | <b>ENW4/3/2/1</b> = 0000                         |                           |                       |       |  |

| 80h | 08h | 8h  | 0h      | MCOLOR4/3/2/1 = 0000                                                                               |                                                               |                      |                                             | CSHA4/3/2/1 = 0000                               |                           |                       |       |  |

| 80h | 09h | 9h  | 39h     | <b>ALW2[3:0]</b> = 3 (4 blocks = 128 characters) <b>ALW1[3:0]</b> = 9 (10 blocks = 320 characters) |                                                               |                      |                                             |                                                  |                           | acters)               |       |  |

| 80h | 0Ah | Ah  | 2h      |                                                                                                    |                                                               |                      |                                             | <b>ALW3[3:0]</b> = 3 (4 blocks = 128 characters) |                           |                       |       |  |

| 80h | 0Bh | Bh  | 0h      |                                                                                                    |                                                               |                      |                                             | <b>RESETW4/3/2/1</b> = 0000                      |                           |                       |       |  |

| 80h | 0Ch | Ch  | 0h      |                                                                                                    | HDW1[6:0] = 0                                                 |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 0Dh | Dh  | 0h      |                                                                                                    | VDW1[5:0] = 0                                                 |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 0Eh | Eh  | 19h     | BS                                                                                                 | <b>BSWW1[2:0]</b> = 000 <b>HSW1[4:0]</b> = 25 (26 characters) |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 0Fh | Fh  | Bh      |                                                                                                    | <b>BSHW1[3:0]</b> = 0000                                      |                      |                                             | <b>VSW1[3:0]</b> = 11 (12 rows of characters)    |                           |                       |       |  |

| 80h | 10h | 10h | 7h      | WS R                                                                                               | <b>RGB 1</b> = 000 : black <b>BSW1</b> =0                     |                      |                                             | <b>T1</b> = 0                                    | <b>RGB W1</b> = 111:white |                       |       |  |

| 80h | 11h | 11h | 20h     |                                                                                                    | HDW2[6:0] = 32                                                |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 12h | 12h | 0h      |                                                                                                    |                                                               | <b>VDW2[5:0]</b> = 0 |                                             |                                                  |                           |                       |       |  |

| 80h | 13h | 13h | 9h      | BS                                                                                                 | SWW2[2:0] = 000 HSW2[4:0] = 9 (10 characters)                 |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 14h | 14h | 4h      | <b>BSHW2[3:0]</b> = 0000                                                                           |                                                               |                      |                                             | VSW2[3:0] =4 (5 rows of characters)              |                           |                       |       |  |

| 80h | 15h | 15h | 7h      | WS R                                                                                               | <b>GB 2</b> = 000 : black <b>BSW2</b> =0                      |                      |                                             | <b>T2</b> = 0                                    | RO                        | <b>GB W2</b> = 111:wh | ite   |  |

| 80h | 16h | 16h | 0h      |                                                                                                    | <b>HDW3[6:0]</b> = 0                                          |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 17h | 17h | Ch      |                                                                                                    | VDW3[5:0] =12                                                 |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 18h | 18h | Fh      | BSI                                                                                                | <b>WW3[2:0]</b> = 000                                         |                      |                                             | <b>HSW3[4:0]</b> = 15 (16 characters)            |                           |                       |       |  |

| 80h | 19h | 19h | 7h      |                                                                                                    | BSHW3[3:0                                                     |                      | <b>VSW3[3:0]</b> = 7 (8 rows of characters) |                                                  |                           |                       |       |  |

| 80h | 1Ah | 1Ah | 7h      | WS R                                                                                               | <b>GB 3</b> = 000 : b                                         | lack                 | <b>BSW3</b> =0                              | <b>T3</b> = 0                                    | RO                        | <b>GB W3</b> = 111:wh | ite   |  |

| 80h | 1Bh | 1Bh | 10h     |                                                                                                    | <b>HDW4[6:0]</b> = 16                                         |                      |                                             |                                                  |                           |                       |       |  |

| 80h | 1Ch | 1Ch | Ch      |                                                                                                    |                                                               |                      | <b>VDW4[5:0]</b> = 12                       |                                                  |                           |                       |       |  |

| 80h | 1Dh | 1Dh | Fh      | BS                                                                                                 | <b>NW4[2:0]</b> = 000                                         |                      |                                             | <b>HSW4[4:0]</b> = 15 (16 characters)            |                           |                       |       |  |

| 80h | 1Eh | 1Eh | 7h      |                                                                                                    | BSHW4[3:0                                                     | <b>D]</b> = 0000     |                                             | VSW                                              | <b>/4[3:0]</b> = 7 (8     | rows of charact       | ers)  |  |

| 80h | 1Fh | 1Fh | 7h      | WS R                                                                                               | <b>GB 4</b> = 000 : b                                         | lack                 | <b>BSW4</b> =0                              | <b>T4</b> = 0                                    | RO                        | <b>GB W4</b> = 111:wh | ite   |  |

STV9936P/S Registers

Table 47: Color Registers: Window 0, Row = 2

| FWR | FAC | Col | Bit 7   | Bit 6                                            | Bit 5        | Bit 4         | Bit 3    | Bit 2 | Bit 1 | Bit 0 |  |

|-----|-----|-----|---------|--------------------------------------------------|--------------|---------------|----------|-------|-------|-------|--|

| 82h | 00h | 0h  | WINDOW1 | Color-b                                          | ox 1: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 01h | 1h  | WINDOW1 | /INDOW1 Color-box 2: BC- BR-BG-BB-blink-FR-FG-FB |              |               |          |       |       |       |  |

| 82h | 02h | 2h  | WINDOW1 | NDOW1 Color-box 3: BC- BR-BG-BB-blink-FR-FG-FB   |              |               |          |       |       |       |  |

| 82h | 03h | 3h  | WINDOW1 | Color-b                                          | ox 4: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 04h | 4h  | WINDOW1 | Color-b                                          | ox 5: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 05h | 5h  | WINDOW1 | Color-b                                          | ox 6: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 06h | 6h  | WINDOW1 | Color-b                                          | ox 7: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 07h | 7h  | WINDOW1 | Color-b                                          | ox 8: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 08h | 8h  | WINDOW2 | Color-b                                          | ox 1: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 09h | 9h  | WINDOW2 | Color-b                                          | ox 2: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Ah | Ah  | WINDOW2 | Color-b                                          | ox 3: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Bh | Bh  | WINDOW2 | Color-b                                          | ox 4: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Ch | Ch  | WINDOW2 | Color-b                                          | ox 5: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Dh | Dh  | WINDOW2 | Color-b                                          | ox 6: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Eh | Eh  | WINDOW2 | Color-b                                          | ox 7: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Fh | Fh  | WINDOW2 | Color-b                                          | ox 8: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 10h | 10h | WINDOW3 | Color-b                                          | ox 1: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 11h | 11h | WINDOW3 | Color-b                                          | ox 2: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 12h | 12h | WINDOW3 | Color-b                                          | ox 3: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 13h | 13h | WINDOW3 | Color-b                                          | ox 4: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 14h | 14h | WINDOW3 | Color-b                                          | ox 5: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 15h | 15h | WINDOW3 | Color-b                                          | ox 6: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 16h | 16h | WINDOW3 | Color-b                                          | ox 7: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 17h | 17h | WINDOW3 | Color-b                                          | ox 8: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 18h | 18h | WINDOW4 | Color-b                                          | ox 1: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 19h | 19h | WINDOW4 | Color-b                                          | ox 2: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Ah | 1Ah | WINDOW4 | Color-b                                          | ox 3: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Bh | 1Bh | WINDOW4 | Color-b                                          | ox 4: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Ch | 1Ch | WINDOW4 | Color-b                                          | ox 5: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Dh | 1Dh | WINDOW4 | Color-b                                          | ox 6: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Eh | 1Eh | WINDOW4 | Color-b                                          | ox 7: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

| 82h | 1Fh | 1Fh | WINDOW4 | Color-b                                          | ox 8: BC- BR | -BG-BB-blink- | FR-FG-FB |       |       |       |  |

Application Hints STV9936P/S

## 9 Application Hints

#### 9.1 Software Hints

#### 9.1.1 Programming Recommendations