### **FEATURES**

- Protocol transparent MUX/DEMUX operation up to 2.7GHz

- Programmable to 4, 5, 8, or 10 bit parallel interfaces

- Differential clock and serial inputs/outputs

- **■** Easily controlled by framer logic

- Synchronous frame boundary indication

- HSPC (High Speed PECL Compatible) inputs and outputs

- 3.3V power supply

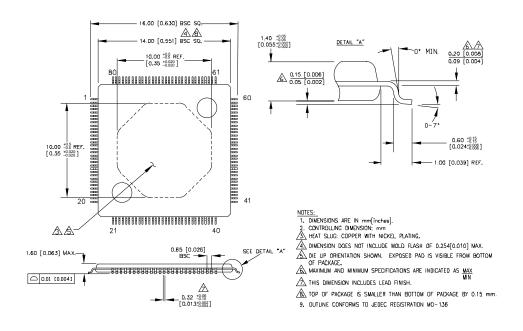

- Available in 80-pin LQFP-PQ2 package

## **DESCRIPTION**

The SY87724L is a complete serial data multiplexer and demultiplexer, capable of operating at up to 2.7GHz. The device provides for muxing and demuxing to 4, 5, 8, or 10 bit wide buses.

The SY87724L can accept a synchronous code group or octet boundary input, and uses this input for parallel data alignment.

The SY87724L is manufactured in Micrel's high performance ASSET2™ silicon bipolar process.

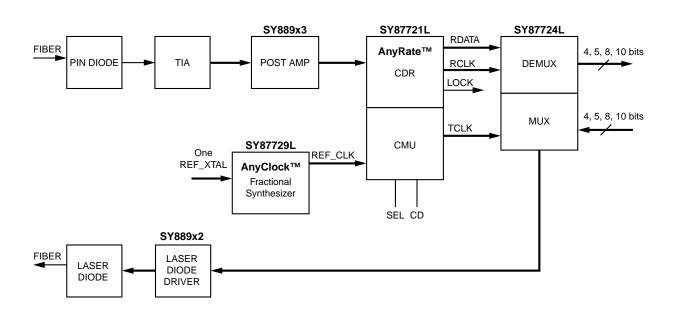

Micrel provides a complete protocol transparent solution with the AnyRate<sup>®</sup> SY87721L CDR/CMU SY87729L, and the SY87724L integrated MUX/DEMUX.

## **APPLICATIONS**

- OC-3, OC-12, OC-48, ATM, InfiniBand

- **■** Gigabit Ethernet

- **■** Fibre Channel, 2X Fibre Channel

- SMPTE-259 and 292

- Proprietary optical transport

- ITU G. 975 Solutions

### SYSTEM BLOCK DIAGRAM

AnyRate is a registered trademark of Micrel, Inc.

## **PACKAGE/ORDERING INFORMATION**

# Ordering Information<sup>(1)</sup>

| Part Number               | Package<br>Type | Operating<br>Range | Package<br>Marking                         | Lead<br>Finish       |

|---------------------------|-----------------|--------------------|--------------------------------------------|----------------------|

| SY87724LHI                | H80-1           | Industrial         | SY87724LHI                                 | Sn-Pb                |

| SY87724LHY <sup>(2)</sup> | H80-1           | Industrial         | SY87724LHY with Pb-Free bar line indicator | Matte Tin<br>Pb-Free |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25$ °C, DC Electricals only.

- 2. Pb-Free package is recommended for new designs.

**80-Pin EPAD TQFP (H80-1)**

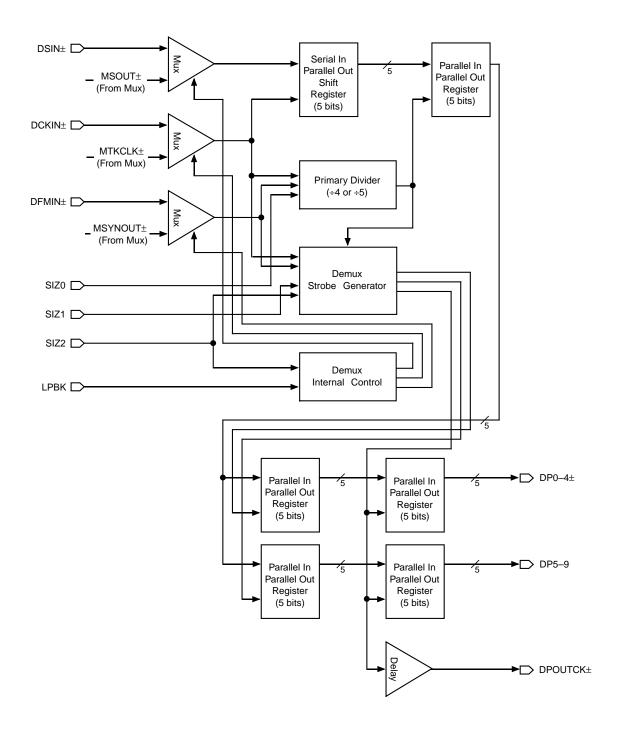

## **FUNCTIONAL BLOCK DIAGRAM**

## **DEMUX**

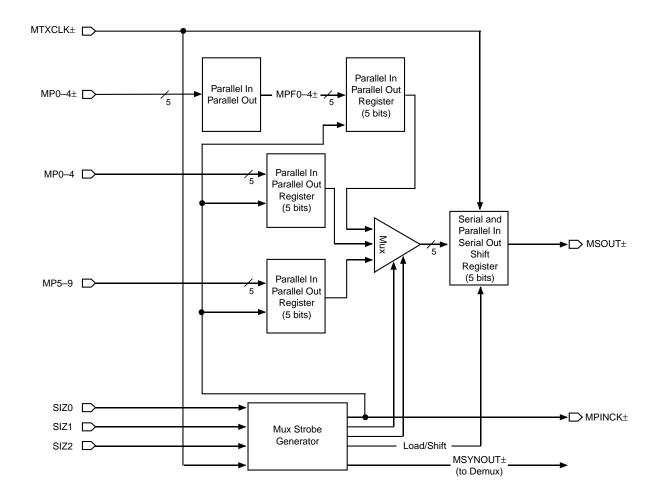

## **FUNCTIONAL BLOCK DIAGRAM**

## MUX

### **PIN NAMES**

#### **COMMON**

### LPBK - TTL Input

This pin defines whether a device exhibits local loopback or not, as per the following table. Loopback internally connects mux serial out to demux serial in, thus the user may expect mux side parallel data to appear on the demux parallel output pins.

| LPBK | Functioning |  |  |  |

|------|-------------|--|--|--|

| 0    | Loopback    |  |  |  |

| 1    | Normal      |  |  |  |

#### SIZ0, SIZ1, SIZ2 - TTL Input

These three signals determine the width of the parallel output, as well as the width of parallel input. The following table describes the parallel width options.

| Width     | SIZ0 | SIZ1 | SIZ2 <sup>(1)</sup> |

|-----------|------|------|---------------------|

| 4         | 0    | 0    | 0                   |

| 5         | 1    | 0    | 0                   |

| 8         | 0    | 1    | 0                   |

| 10        | 1    | 1    | 0                   |

| Undefined | Х    | X    | 1                   |

Note:

1. Pin 8 (SIZ2) should always be tied to a TTL logic level LOW.

#### **DEMUX**

#### **DSIN± - Differential HSPC Input**

This is the serial input to the SY87724L demux. It accepts the serial data and converts it to parallel data. It is ignored during loopback.

#### DCKIN± - Differential HSPC Input

This is the bit rate clock that feeds serial data into the demux shift register. This signal also feeds the demux strobe generator and primary divider, except during loopback.

#### **DFMIN± – Differential HSPC Input**

This is the frame alignment input signal. This signal resets the primary divider, as well as the strobe generator. This effectively sets the alignment for the parallel data being demuxed. Usually, DFMIN± asserts one DCKIN± before a parallel word boundary, and continues to assert one clock before every boundary. However, DFMIN± need only occur once for proper operation. Should DFMIN± assert at other than a previously set boundary, the DPOUTCK± signal will always occur later than would be expected. That is, there will never be a short DPOUTCK± pulse.

### DP0± through DP4± – Differential PECL Output

These signals may be used as either differential, or single-ended. When converting to 4 or 5 bits, speed issues may encourage the use of these signals differentially. When converting to wider than 5 bits, these signals are to be used single-ended. Please refer to the applications section for further details.

#### **DP5 through DP9 - PECL Output**

These are the rest of the parallel output bits, to be used when converting to wider than 5 bits. Which bits are valid depends on the values of SIZ0, SIZ1, and SIZ2. Please refer to the table in the applications section for further details.

#### DPOUTCK± - Differential HSPC Output

This signal is used to strobe the DP0-9 data. It is used differentially when converting to 4 or 5 bits, and is used single-ended when converting to wider than 5 bits. The clock rate of the line will be determined by the DCKIN signal, and by the setting of the SIZ bits. This output always provides valid differential logic levels.

#### MUX

#### MP0-9 - PECL Input

These bits accept data for muxing wider than 5 bits. MPINCK+, used single-ended, determines when this data may change. Please refer to the table in the description for which pins represent what bits for various widths.

### MPF0-4± - Differential PECL Input

These signals are used when muxing 4 or 5 bits of parallel data. MPINCK± determines when this data may change. Please refer to the Mux table in the description for which pins represent what bits for various widths.

### MTXCLK± - Differential HSPC Input

This is the serial rate clock input to the mux. It determines the rate at which serial data will be shifted out of the mux.

#### MSOUT± - Differential PECL Output

This signal is the serialized data output.

#### MPINCK± - Differential PECL Output

This signal indicates when the next set of parallel bits may be presented to the SY87724L for muxing. For muxing wider than 5 bits, MPINCK+ is used single-ended. These signals always provide valid differential clock signals regardless of single-ended or differential data mode.

#### **OTHER**

V<sub>CC</sub> Supply Voltage

V<sub>CCO</sub> Output Supply Voltage

GND Ground

NC These pins are reserved and are to be left

unconnected.

#### Note:

All differential outputs always provide valid differential logic levels regardless of differential or single-ended use.

### **DESCRIPTION**

#### General

The SY87724L MDM is designed to perform muxing and demuxing at up to 2.7GHz speeds. The device can simultaneously mux and demux up to 10 bits of full duplex data. In addition, a full parallel-to-parallel loopback function is implemented, such that parallel data out will loop back to parallel data in, with the device internally connecting the serial output to the serial input.

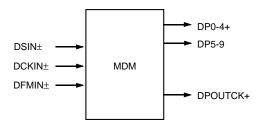

#### **Narrow Demux**

In this example, serial data is converted into 4 or 5 bit wide data. Because this can result in very high data rates on the parallel outputs, they are differential. The DFMIN± input indicates, synchronously with DCKIN±, and one clock ahead, the start of a 4 or 5 bit boundary.

Figure 1. Narrow Demux

Every DFMIN± assertion will trigger a new 4 or 5 bit boundary. Should only one DFMIN± assertion occur, then DPOUTCK± will continue to assert every 4 or 5 DCKIN± clocks. Should a subsequent DFMIN± assertion reset the 4 or 5 bit boundary, then DPOUTCK± will always result in a longer assertion, not a shorter one.

For example, if a subsequent DFMIN± resets a 5 bit boundary after the second bit in relation to a previous boundary, then the next DPOUTCK± will always occur 7 DCKIN± later, never 2 DCKIN± later. For four bit output, DP5+ are not used.

#### **Wide Demux**

The more typical case will be to convert the serial data stream into 8 or 10 bit wide data. Because the worst case parallel transfer rate is on the order of 250 to 340 Megatransfers per second, single ended parallel output is preferred. Thus, only the single-ended side of the differential outputs is used.

This example is much like the narrow demux, except now DFMIN± indicates 8 or 10 bit boundaries.

Figure 2. Wide Demux

As in the narrow case, DPOUTCK± will never assert twice in 8 or 10 DCKIN± cycles. Should a DFMIN± assertion change the MDM's 8 or 10 bit boundary, DPOUTCK± assertion will be delayed and there will never be a short assertion.

For 8 bit output, DP4± and DP9 are not used.

The following table summarizes the available bit widths. The right column shows the parallel bits, in sequence from first in serially, to last in.

| Width | Sequence                                              |

|-------|-------------------------------------------------------|

| 4     | DP0±, DP1±, DP2±, DP3±                                |

| 5     | DP0±, DP1±, DP2±, DP3±, DP4±                          |

| 8     | DP0+, DP1+, DP2+, DP3+, DP5, DP6, DP7, DP8            |

| 10    | DP0+, DP1+, DP2+, DP3+, DP4+, DP5, DP6, DP7, DP8, DP9 |

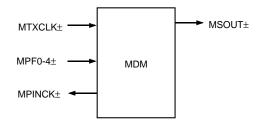

#### **Narrow Mux**

In this scenario, 4 or 5 bit wide parallel data is converted to a serial bit stream. Because this can result in very high data rates on the parallel inputs, they are differential. In this mode of operation, there is no external synchronization, and the MPINCK $\pm$  signal pair has arbitrary phase with respect to the MTXCLK $\pm$  clock, which clocks the mux output shift register.

Figure 4. Narrow Mux

MPINCK± indicates when MDM is ready to accept more data. It is derived from MTXCLK±, with an arbitrary phase relationship.

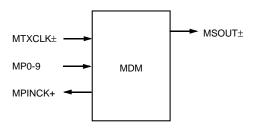

#### **Wide Mux**

The more typical case will be to convert 8 or 10 bit wide parallel data words into a serial bit stream. Because the worst case parallel input rate is on the order of 250 to 340 Mega-transfers per second, single ended parallel inputs are used.

This scenario is much like the narrow mux case, except now MPINCK+ clocks slower, for 8 or 10 bit parallel words.

Figure 5. Wide Mux

Note that the input data indication is now single ended, and that completely different input pins are used, as compared to the 4 or 5 bit case.

The following table summarizes the available bit widths. The right column shows the parallel input bits, such as they will appear in the serial output stream.

| Width | Sequence                                         |

|-------|--------------------------------------------------|

| 4     | MPF0±, MPF1±, MPF2±, MPF3±                       |

| 5     | MPF0±, MPF1±, MPF2±, MPF3±, MPF4±                |

| 8     | MP5, MP6, MP7, MP8, MP0, MP1, MP2, MP3           |

| 10    | MP5, MP6, MP7, MP8, MP9, MP0, MP1, MP2, MP3, MP4 |

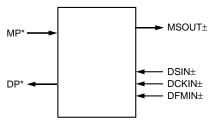

#### Loopback

To ease system design, the SY87724L MDM has the capability to loop parallel data in, through the mux, into the demux, and back to parallel data out. This permits system check-out through to the individual MDM device. Note that, for a full check-out, some form of loopback further down the serial stream is required.

Loopback is incorporated into MDM by modifying the serial clock, data, and sync inputs to the demux stage.

During loopback, the source of serial information for the demux is changed. The MSOUT±, MTXCLK± and MSYNOUT± are internally muxed to the DSIN±, DCKIN±, and DFMIN± nodes of the demux section. The MSYNOUT± signal has the same characteristics as the DFMIN logic expects.

This exercises the internal data path, both mux and demux, for MDM, and also the control logic. The parallel data presented to the parallel inputs will appear, some small but unspecified time later, at the parallel outputs.

\* Number of wires depends on the SIZX bits.

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol             | Parame                   | eter                  | Rating                                 | Unit |

|--------------------|--------------------------|-----------------------|----------------------------------------|------|

| V <sub>CC</sub>    | Power Supply Voltage     |                       | -0.5 to +3.8                           | V    |

| V <sub>I</sub>     | Input Voltage            |                       | –0.5 to V <sub>CC</sub> <sup>(2)</sup> | V    |

| I <sub>OUT</sub>   | ECL Output Current       | —Continuous<br>—Surge | 50<br>100                              | mA   |

| T <sub>store</sub> | Storage Temperature Rang | ge                    | -65 to +150                            | °C   |

| T <sub>A</sub>     | Operating Temperature Ra | inge                  | -40 to +85                             | °C   |

### NOTES:

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. The maximum value is specified at  $V_{CC}$  up to  $V_{CC}$  = +6V.

## DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = V_{CCA} = 3.15V \text{ to } 3.45V$

| Symbol          | Parameter            | Min. | Тур. | Max. | Unit | Condition |

|-----------------|----------------------|------|------|------|------|-----------|

| V <sub>CC</sub> | Power Supply Voltage | 3.15 | 3.3  | 3.45 | V    |           |

| I <sub>CC</sub> | Power Supply Current | _    | 650  | 750  | mA   |           |

#### NOTE:

1. Operating temperature range from -40°C to +85°C.

## HSPC DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = V_{CCA} = 3.15V \text{ to } 3.45V$

| Symbol           | Parameter                            | Min.                    | Тур. | Max.                    | Unit | Condition                          |

|------------------|--------------------------------------|-------------------------|------|-------------------------|------|------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                   | V <sub>CC</sub> – 1.165 |      | V <sub>CC</sub> – 0.880 | V    |                                    |

| V <sub>IL</sub>  | Input LOWVoltage                     | V <sub>CC</sub> – 1.810 | _    | V <sub>CC</sub> – 1.475 | V    |                                    |

| I <sub>IL</sub>  | Input LOW Current                    | -0.5                    | 1    |                         | μΑ   | $V_{IN} = V_{IL}(Min)$             |

| V <sub>OH</sub>  | Output HIGH Voltage                  | V <sub>CC</sub> – 1.0   |      | V <sub>CC</sub> – 0.75  | V    | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OL</sub>  | Output LOW Voltage                   | V <sub>CC</sub> – 1.55  |      | V <sub>CC</sub> – 1.25  | V    | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OSW</sub> | Output Voltage<br>Differential Swing | 0.3                     |      | _                       | V    |                                    |

### NOTE:

1. Operating temperature range from -40°C to +85°C.

## PECL DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = V_{CCA} = 3.15V \text{ to } 3.45V$

| Symbol           | Parameter                            | Min.                    | Тур. | Max.                    | Unit | Condition                          |

|------------------|--------------------------------------|-------------------------|------|-------------------------|------|------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                   | V <sub>CC</sub> – 1.165 | -    | V <sub>CC</sub> – 0.880 | V    |                                    |

| V <sub>IL</sub>  | Input LOW Voltage                    | V <sub>CC</sub> – 1.810 | _    | V <sub>CC</sub> – 1.475 | V    |                                    |

| I <sub>IL</sub>  | Input LOW Current                    | -0.5                    | _    | _                       | μΑ   | $V_{IN} = V_{IL}(Min)$             |

| V <sub>OH</sub>  | Output HIGH Voltage                  | V <sub>CC</sub> – 1.075 | _    | V <sub>CC</sub> - 0.830 | V    | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OL</sub>  | Output LOW Voltage                   | V <sub>CC</sub> – 1.860 | _    | V <sub>CC</sub> – 1.570 | V    | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OSW</sub> | Output Voltage<br>Differential Swing | 0.6                     |      | _                       | V    |                                    |

### NOTE:

1. Operating temperature range from -40°C to +85°C.

# TTL DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = V_{CCA} = 3.15 \text{V to } 3.45 \text{V}$

| Symbol          | Parameter          | Min. | Тур. | Max. | Unit | Condition                                      |

|-----------------|--------------------|------|------|------|------|------------------------------------------------|

| V <sub>IH</sub> | Input HIGH Voltage | 2.0  |      |      | ٧    |                                                |

| $V_{IL}$        | Input LOW Voltage  |      |      | 0.8  | ٧    |                                                |

| I <sub>IH</sub> | Input HIGH Current |      |      | +20  | μΑ   | $V_{IN} = 2.7V$ , $V_{CC} = Max$ .             |

|                 |                    |      |      | +100 | μΑ   | $V_{IN} = V_{CC}, V_{CC} = Max.$               |

| I <sub>IL</sub> | Input LOW Current  |      |      | 300  | μΑ   | V <sub>IN</sub> = 0.5V, V <sub>CC</sub> = Max. |

#### NOTE:

1. Operating temperature range from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# AC ELECTRICAL CHARACTERISTICS

$V_{\rm CC} = V_{\rm CCA} = 3.15 \text{V to } 3.45 \text{V}$

| Symbol                                       | Parameter                                                      | Min.                     | Тур.     | Max.       | Unit | Condition                                         |

|----------------------------------------------|----------------------------------------------------------------|--------------------------|----------|------------|------|---------------------------------------------------|

| f <sub>MAX</sub>                             | Maximum Operating Frequency                                    | 2.7                      | _        | _          | GHz  |                                                   |

| t <sub>DCKPWH</sub> ,<br>t <sub>DCKPWH</sub> | Demux Clock Pulse Duty Cycle                                   | 45                       |          | 55         | %    |                                                   |

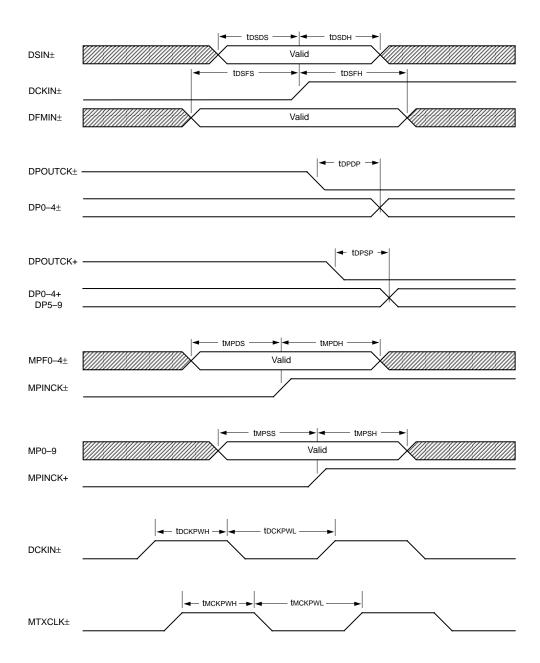

| t <sub>DSDS</sub>                            | Demux Serial Data Setup                                        | 200                      | ı        | ı          | ps   |                                                   |

| t <sub>DSDH</sub>                            | Demux Serial Data Hold                                         | 0                        |          |            | ps   |                                                   |

| t <sub>DSFS</sub>                            | Demux Serial Frame Setup                                       | 150                      | _        | _          | ps   |                                                   |

| t <sub>DSFH</sub>                            | Demux Serial Frame Hold                                        | 50                       | _        | _          | ps   |                                                   |

| t <sub>DPDP</sub>                            | Demux Parallel<br>Differential Propagation                     | +200                     | _        | +800       | ps   |                                                   |

| t <sub>DPSP</sub>                            | Demux Parallel<br>Single-Ended Propagation                     | +200                     | _        | +1200      | ps   |                                                   |

| t <sub>MCKPWH</sub> ,<br>t <sub>MCKPWL</sub> | Mux Clock Pulse Duty Cycle                                     | 45                       | _        | 55         | %    |                                                   |

| t <sub>MPDS</sub>                            | Mux Parallel Differential Setup <sup>(2)</sup>                 | T <sub>cyc</sub> +650    | _        | _          | ps   |                                                   |

| t <sub>MPDH</sub>                            | Mux Parallel Differential Hold <sup>(2)</sup>                  | –(T <sub>cyc</sub> +250) | _        | _          | ps   |                                                   |

| t <sub>MPSS</sub>                            | Mux Parallel Single-Ended Setup <sup>(2)</sup>                 | T <sub>cyc</sub> +850    | _        | _          | ps   |                                                   |

| t <sub>MPSH</sub>                            | Mux Parallel Single-Ended Hold <sup>(2)</sup>                  | -(T <sub>cyc</sub> +50)  | _        | _          | ps   |                                                   |

| t <sub>r</sub> , t <sub>f</sub>              | Output Rise/Fall Times<br>MCKOUT, MSOUT, MSYNOUT<br>All Others |                          | 100<br>— | 120<br>500 | ps   | $50\Omega$ to V <sub>CC</sub> $-$ 2V (20% to 80%) |

#### NOTES:

<sup>1.</sup> Operating temperature range from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

<sup>2.</sup>  $T_{cyc}$  = the period of the clock being fed into MTXCLK.

## **TIMING WAVEFORMS**

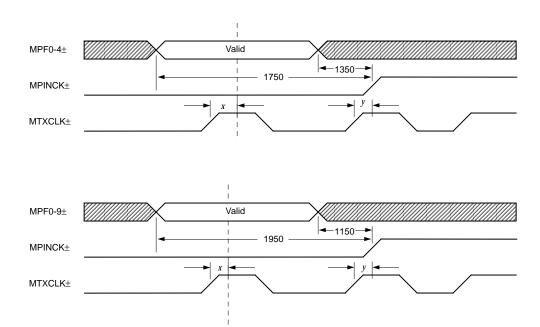

## **TIMING APPLICATION EXAMPLE**

#### NOTES:

- 1. MTXCLK = 1Gbps

- 2. Time "x" is approximately equal to time "y."

- Setup and hold for MPF0-4± is conditioned on the MTXCLK± rising edge just prior to the MTXCLK± rising edge that causes an MPINCK± rising edge.

## 80-PIN LQFP-PQ2 (DIE UP) (H80-1)

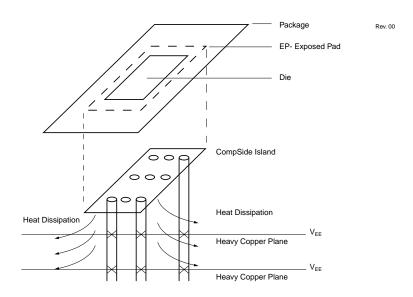

PCB Thermal Consideration for 80-Pin EPAD-TQFP Package

## MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.