# **TMC2074**

# Dual Mode CircLink<sup>™</sup> Controller

#### **Datasheet**

### PRODUCT FEATURES

- Low Power CMOS, 3.3 Volt Power Supply with 5 Volt Tolerant I/O

- Supports 8/16-Bit Data Bus

- Both 86xx and 68hxx Platforms

- 1K On-chip Dual Port Buffer Memory

- Sequential I/O Mapped Access

- Enhanced Token Passing Protocol from ARCNET

- Maximum 31 Nodes per Network

- Token Retry Mechanism

- Maximum 256 Bytes per Packet

- Consecutive Node ID Assignment

- Memory Mirror

- Shared Memory within Network

- Network Standard Time

- Network Time Synchronization

- Automatic Time Stamping

- Coded Mark Inversion

- Intelligent 1-Bit Error Correction

- Magnetic Saturation Prevention

- Dual Operation Modes

- Peripheral (Host) Mode Operates with MCU

- Standalone (I/O) Mode Operates without MCU

- Supports 8 Bit Programmable General Purpose I/O at peripheral Mode

- Supports 16 Bit Input and 16 Bit Output at Standalone Mode

- Dual Communication Modes (with Peripheral Mode)

- Free Format Mode

- Remote Buffer Mode

- 3 Port Hub Integrated

- 1 Internal and 2 External

- Flexible Topologies

- Bus, Star and Tree

- Low Cost Media can be Used

- RS485 Differential Driver

- Fiber Optics and Twisted Pair Cable Supported

- 128-Pin VTQFP Package; Green, Lead-free Package also Available

- Temperature Range from 0 to 70 Degrees C

### ORDERING INFORMATION

Order Number(s):

TMC2074-NE for 128 pin VTQFP package

TMC2074-NU for 128 pin VTQFP package (green, lead-free)

80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123

Copyright © 2006 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or rerors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **TABLE OF CONTENTS**

| Chap             | ter 1 General Description                                                       | 6  |

|------------------|---------------------------------------------------------------------------------|----|

| 1.1              | About CircLink                                                                  | 6  |

| 1.2              | About TMC2074                                                                   | 7  |

| 1.3              | Internal Block Diagram                                                          | 8  |

| 1.4              | Pin Configuration                                                               | 9  |

| 1.5              | Pin Description by Functions                                                    | 13 |

| 1.5.1            | CPU Interface Pins (27)                                                         | 13 |

| 1.5.2            | Transceiver Interface Pins (5)                                                  |    |

| 1.5.3            | Setup Pins (37)                                                                 | 14 |

| 1.5.4            | External Output or I/O Pins (10)                                                |    |

| 1.5.5            | Test Pins (5)                                                                   |    |

| 1.5.6            | Clock Pins (3)                                                                  |    |

| 1.6              | Setup Pins                                                                      |    |

| 1.6.1            | CPU Type Selection                                                              |    |

| 1.6.2<br>1.6.3   | Address Multiplex Selection                                                     |    |

| 1.6.4            | Write Timing Selection                                                          |    |

| 1.6.4            |                                                                                 |    |

| 1.6.6            | Data Bus Width Selection                                                        |    |

| 1.6.7            | Data Strobe Polarity Specification                                              |    |

| 1.6.8            | Page Size Selection                                                             |    |

| 1.6.9            | Maximum Node (MAXID) Number Setup                                               |    |

| 1.6.10           |                                                                                 |    |

| 1.6.11           |                                                                                 |    |

| 1.6.12           |                                                                                 |    |

| 1.6.13           |                                                                                 |    |

| 1.6.14           |                                                                                 |    |

| 1.6.15           |                                                                                 |    |

| 1.6.16           | NST Carry Output Digit Select                                                   | 23 |

| 1.6.17           | 7 CMI Bypass Specification                                                      | 23 |

| 1.6.18           |                                                                                 |    |

| 1.6.19           |                                                                                 |    |

| 1.6.20           |                                                                                 |    |

| 1.6.21           |                                                                                 |    |

| 1.6.22           |                                                                                 |    |

| Chap             | ter 2 Functional Description                                                    | 25 |

| 2.1              | Communication Specification                                                     | 25 |

| 2.2              | Message Class                                                                   | 25 |

| 2.3              | CircLink Network Communication Protocol Overview                                | 26 |

| 2.4              | CircLink Protocol Enhancement                                                   | 27 |

| 2.4.1            | Reducing Token Loss                                                             |    |

| 2.4.2            | Reduction of Network Reconfiguration Time                                       |    |

| 2.4.3            | Reduction of Reconfiguration Burst Signal Send Time                             |    |

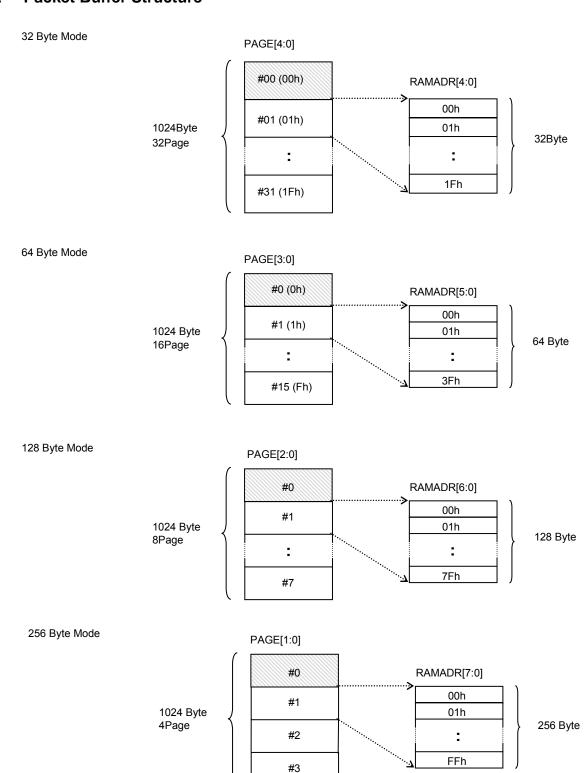

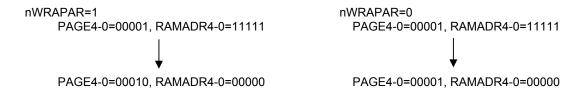

| 2.5              | RAM Page Expansion                                                              | 28 |

| 2.5.1            | RAM Access                                                                      |    |

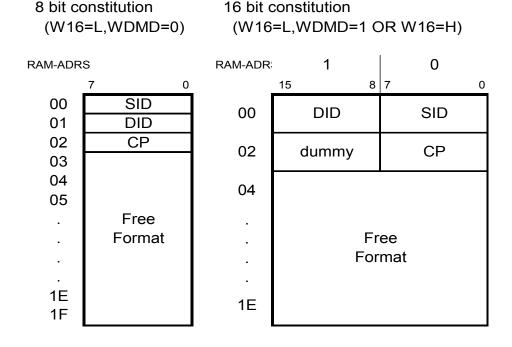

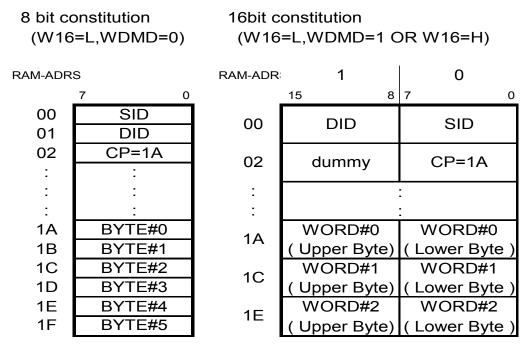

| 2.5.2            | Packet Buffer Structure                                                         |    |

| 2.5.3            | Packet Data Structure                                                           |    |

| 2.0              | CPU Interface                                                                   |    |

| <b>2.6</b> 2.6.1 |                                                                                 |    |

|                  | C. C. GOTHINGGROTI GITG COTTINGRALINITY NOTWOOTI TITOLGRIG WIGHTING I TOUGGGOIG |    |

|                                                                                                                                                                   | Interface Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

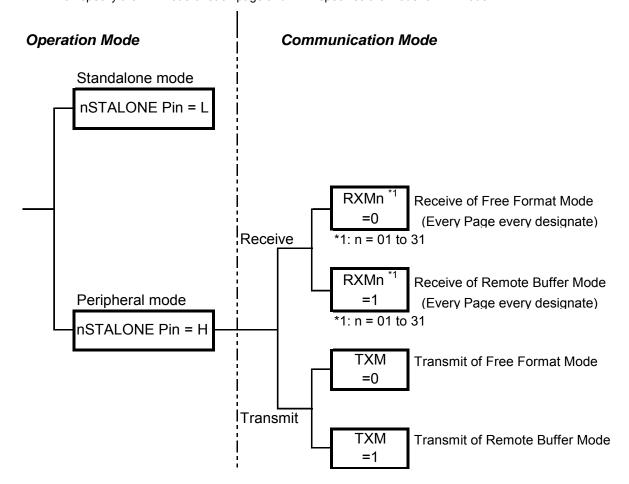

| 2.7                                                                                                                                                               | CircLink Operation and Communication Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                           |

| 2.7.1                                                                                                                                                             | Operational Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                           |

| 2.7.2                                                                                                                                                             | Communication Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                           |

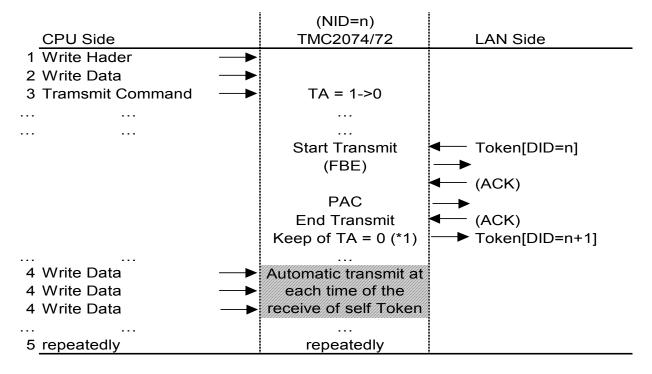

| 2.8                                                                                                                                                               | Sending in Peripheral Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                           |

| 2.8.1                                                                                                                                                             | Example of Sending Control from CPU in Free Format Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| 2.8.2                                                                                                                                                             | TX Control from CPU in Remote Buffer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

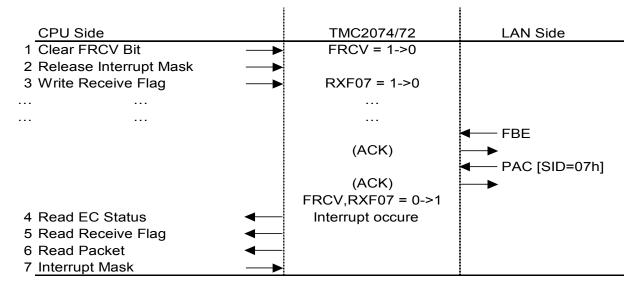

| <b>2.9</b><br>2.9.1                                                                                                                                               | Receive in Peripheral Mode  Temporary Receive and Direct Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

| 2.9.1                                                                                                                                                             | Example of Receive Flow in Free Format Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

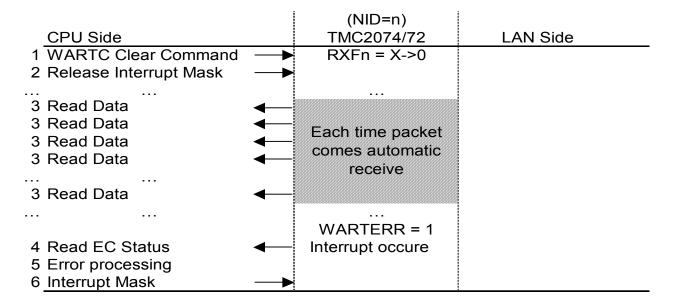

| 2.9.3                                                                                                                                                             | Example of Receive Flow in Remote Buffer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

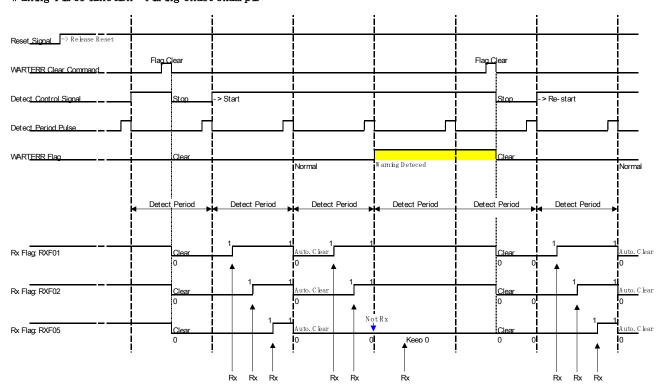

| 2.9.4                                                                                                                                                             | Warning Timer (WT) at Remote Buffer Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| 2 4 0                                                                                                                                                             | Standalone Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

| <b>2.10</b><br>2.10.1                                                                                                                                             | General Description of Standalone Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| 2.10.1                                                                                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| 2.10.3                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

| 0.44                                                                                                                                                              | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| 2.11                                                                                                                                                              | Diagnostic Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                           |

| 2.12                                                                                                                                                              | Network Standard Time (NST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| 2.12.1                                                                                                                                                            | Functions Provided by NST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| 2.12.2                                                                                                                                                            | <b>/</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| 2.12.3<br>2.12.4                                                                                                                                                  | Phase ErrornNSTCOUT Pulse Generation Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

|                                                                                                                                                                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| 2.13                                                                                                                                                              | CMI Modem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62                                           |

| 2.14                                                                                                                                                              | HUB Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                           |

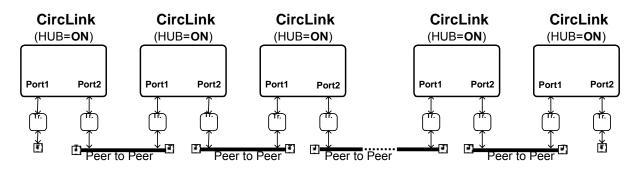

| 2.14.1                                                                                                                                                            | Operation Example of HUB Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                           |

| 2.14.2                                                                                                                                                            | Timer Expansion in Multi-stage Cascade Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

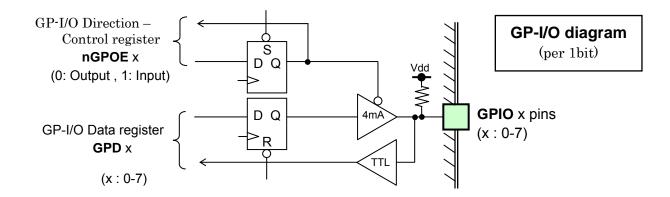

| 2.15                                                                                                                                                              | 8-Bit General-purpose I/O Port (New function)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                           |

| Chapte                                                                                                                                                            | er 3 Description of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67                                           |

| =                                                                                                                                                                 | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |

|                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

|                                                                                                                                                                   | Details of Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                           |

| 3.2.1                                                                                                                                                             | COMR0 Register: Status/interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                           |

| 3.2.2                                                                                                                                                             | COMR1 Register: Diagnostic/Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| 3.2.3<br>3.2.4                                                                                                                                                    | COMR2 Register: Page Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

|                                                                                                                                                                   | COMP5 Pagietar: Sub-addrace Pagietar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |

| 3.2.5                                                                                                                                                             | COMR5 Register: Sub-address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77                                           |

| 3.2.5<br>3.2.6                                                                                                                                                    | COMR6 Register: Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77<br>78                                     |

| 3.2.5<br>3.2.6<br>3.2.7                                                                                                                                           | COMR6 Register: Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77<br>78<br>80                               |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8                                                                                                                                  | COMR6 Register: Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9                                                                                                                         | COMR6 Register: Configuration Register  COMR7 Register.  NST Register: Network Standard Time.  INTSTA Register: EC Interrupt Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11                                                                                                     | COMR6 Register: Configuration Register COMR7 Register. NST Register: Network Standard Time. INTSTA Register: EC Interrupt Status INTMSK Register: EC Interrupt Mask. ECCMD Register: EC Command Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12                                                                                           | COMR6 Register: Configuration Register COMR7 Register.  NST Register: Network Standard Time INTSTA Register: EC Interrupt Status INTMSK Register: EC Interrupt Mask ECCMD Register: EC Command Register RSID Register: Receive SID                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13                                                                                 | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14                                                                       | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side)                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15                                                             | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side)  RXFL Register: Receive Flag (lower side)                                                                                                                                                                                                                                                                                                                          |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16                                                   | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side)  RXFL Register: Receive Flag (lower side)  CMID Register: Clock Master Node ID                                                                                                                                                                                                                                                                                     |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17                                         | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side).  RXFL Register: Receive Flag (lower side).  CMID Register: Clock Master Node ID  MODE Register: Operation Mode Setup Register                                                                                                                                                                                                                                     | 77 78 80 80 84 84 87 88 89 90 91             |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16                                                   | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side)  RXFL Register: Receive Flag (lower side)  CMID Register: Clock Master Node ID  MODE Register: Operation Mode Setup Register  CARRY Register: Carry Selection for External Output                                                                                                                                                                                  |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17<br>3.2.18                               | COMR6 Register: Configuration Register  COMR7 Register  NST Register: Network Standard Time  INTSTA Register: EC Interrupt Status  INTMSK Register: EC Interrupt Mask  ECCMD Register: EC Command Register  RSID Register: Receive SID  SSID Register: SID.  RXFH Register: Receive Flag (higher side).  RXFL Register: Receive Flag (lower side).  CMID Register: Clock Master Node ID  MODE Register: Operation Mode Setup Register                                                                                                                                                                                                                                     |                                              |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17<br>3.2.18<br>3.2.19<br>3.2.20<br>3.2.21 | COMR6 Register: Configuration Register  COMR7 Register.  NST Register: Network Standard Time.  INTSTA Register: EC Interrupt Status.  INTMSK Register: EC Interrupt Mask.  ECCMD Register: EC Command Register.  RSID Register: Receive SID.  SSID Register: SID.  RXFH Register: Receive Flag (higher side).  RXFL Register: Receive Flag (lower side).  CMID Register: Clock Master Node ID.  MODE Register: Operation Mode Setup Register.  CARRY Register: Carry Selection for External Output.  RXML Register: Receive Mode (lower side).  RXML Register: Receive Mode (lower side).  MAXID Register: Selection of Max. ID.                                          | 77 78 80 80 84 84 87 88 89 90 91 91 92 93    |

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17<br>3.2.18<br>3.2.19<br>3.2.20           | COMR6 Register: Configuration Register  COMR7 Register.  NST Register: Network Standard Time.  INTSTA Register: EC Interrupt Status.  INTMSK Register: EC Interrupt Mask.  ECCMD Register: EC Command Register.  RSID Register: Receive SID.  SSID Register: SID.  RXFH Register: Receive Flag (higher side).  RXFL Register: Receive Flag (lower side).  CMID Register: Clock Master Node ID.  MODE Register: Operation Mode Setup Register.  CARRY Register: Carry Selection for External Output.  RXML Register: Receive Mode (lower side).  RXML Register: Receive Mode (lower side).  MAXID Register: Selection of Max. ID.  NID Register: Selection of the Node ID. | 77 78 80 80 84 84 84 87 88 89 90 91 91 92 93 |

#### Datasheet

| 3.2.24<br>3.2.25       | CKP Register: Communication Rate Selection                                  |       |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| 3.2.26                 | PININFO Register: Pin Setup Information                                     |       |  |  |  |  |  |  |

| 3.2.27                 | ERRINFO Register: Error Information                                         | 102   |  |  |  |  |  |  |

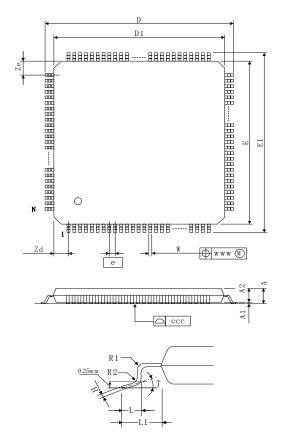

| A-1 Outli              | ne                                                                          | 104   |  |  |  |  |  |  |

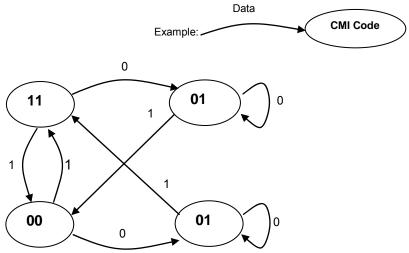

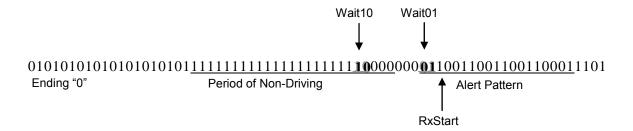

| A-2 CMI (              | Code                                                                        | 104   |  |  |  |  |  |  |

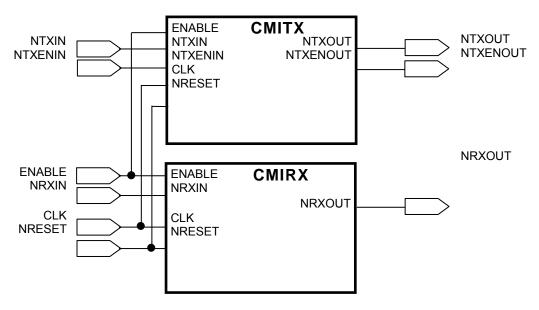

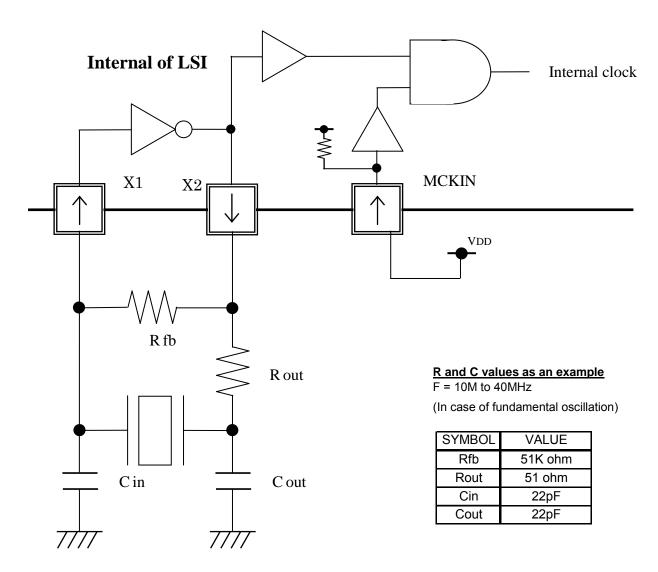

| A-3 CMI N              | Modem Configuration                                                         | 105   |  |  |  |  |  |  |

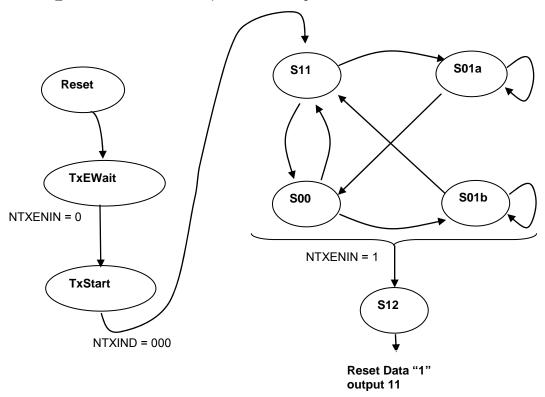

| A-4 CMIT               | X Block                                                                     | 106   |  |  |  |  |  |  |

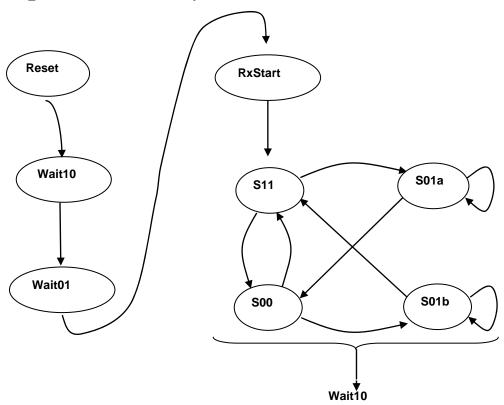

| A-5 CMIR               | MIRX Block                                                                  |       |  |  |  |  |  |  |

| A-6 Detai              | Is Regarding Reception                                                      | 108   |  |  |  |  |  |  |

| LIST (                 | OF FIGURES                                                                  |       |  |  |  |  |  |  |

| Figure 1               | - TMC2074 Block Diagram                                                     | 8     |  |  |  |  |  |  |

| Figure 2               | - Pin Names: Pin Name in Peripheral Mode/Pin Name in Standalone Mode        |       |  |  |  |  |  |  |

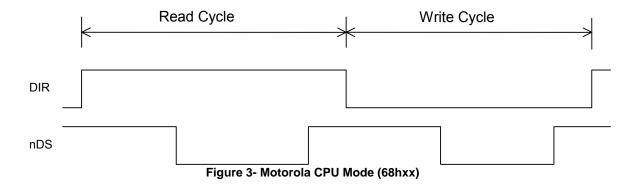

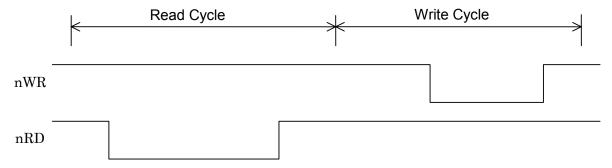

| Figure 3               | - Motorola CPU Mode (68hxx)                                                 |       |  |  |  |  |  |  |

| Figure 4               | - Intel CPU Mode (86xx)                                                     |       |  |  |  |  |  |  |

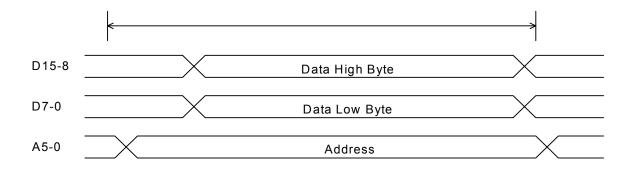

| Figure 5               | - Non-Multiplex Bus<br>- Multiplex (Ale Falling-Edge Type)                  |       |  |  |  |  |  |  |

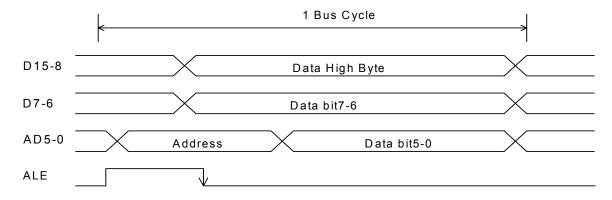

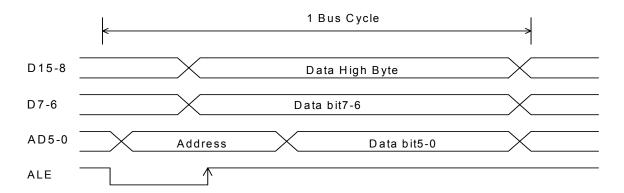

| Figure 6<br>Figure 7   | - Multiplex (Ale Rising-Edge Type)                                          |       |  |  |  |  |  |  |

| Figure 8               | - Packet Structure of Free Format Mode (Example of 32 bytes/page)           |       |  |  |  |  |  |  |

| Figure 9               | - Packet Structure of Remote Buffer Mode (Example of 32 bytes/page)         |       |  |  |  |  |  |  |

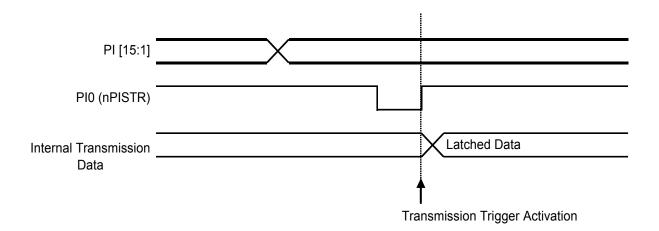

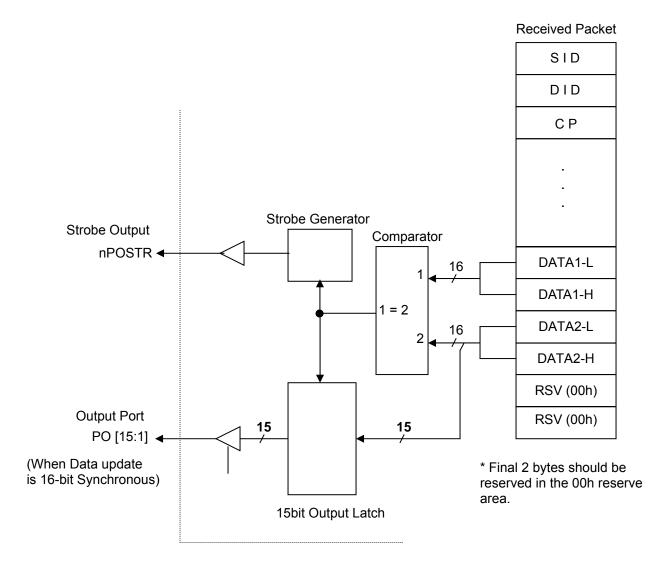

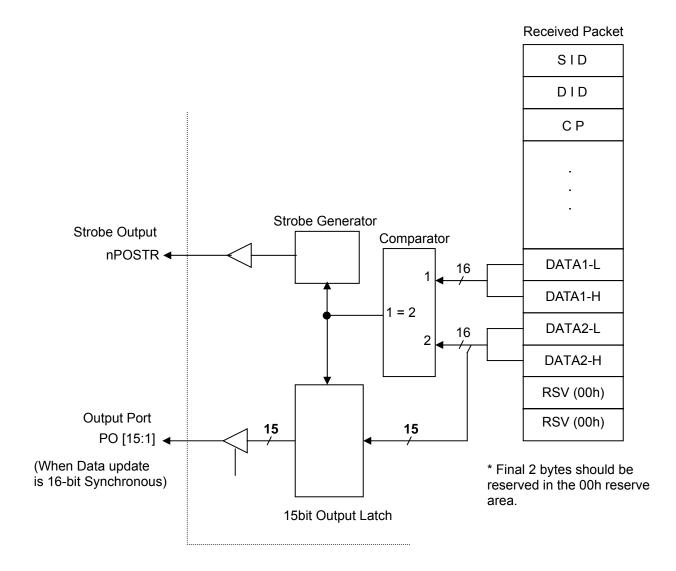

| Figure 10              | - Data Import Timing in Standalone Mode and External Trigger Mode (Mode 3)  |       |  |  |  |  |  |  |

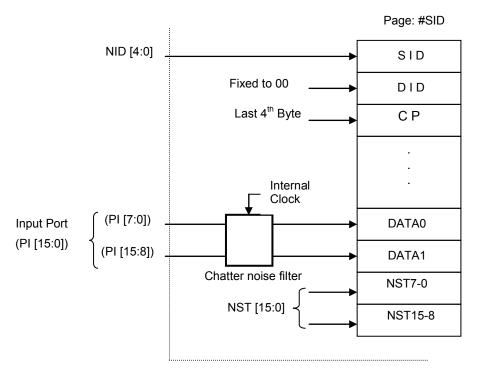

| Figure 11              | - Transmission Packet Buffer Configuration (Mode 1, 2)                      |       |  |  |  |  |  |  |

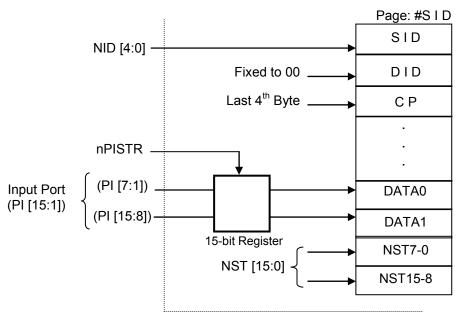

| Figure 12              | - Transmission Packet Buffer Configuration (Mode 3)                         |       |  |  |  |  |  |  |

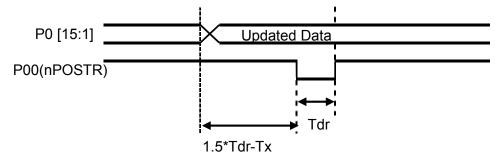

| Figure 13              | - Strobe Output Timing in Standalone Mode, External Trigger Mode (Mode 3)   |       |  |  |  |  |  |  |

| Figure 14              | - Reception Packet Buffer Configuration (SPRE [2:0] = other than 111)       |       |  |  |  |  |  |  |

| Figure 15              | - Reception Packet Buffer Configuration (SPRE [2:0]=111)                    |       |  |  |  |  |  |  |

| Figure 16              | - Internal 3 Port HUB Block Diagram                                         |       |  |  |  |  |  |  |

| Figure 17              | - CMI Coding State transition diagram                                       |       |  |  |  |  |  |  |

| Figure 18              | - CMI Modem Block Diagram                                                   |       |  |  |  |  |  |  |

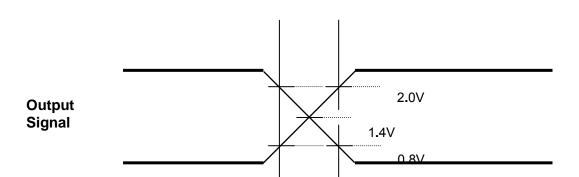

| Figure 19              | - Example of Unstable Comparator Output                                     |       |  |  |  |  |  |  |

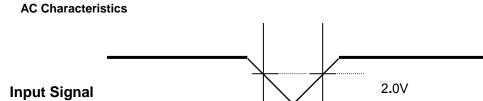

| Figure 20<br>Figure 21 | - Timing Measurement Points                                                 |       |  |  |  |  |  |  |

| LICT                   | DE TARLES                                                                   |       |  |  |  |  |  |  |

| LIST (                 | OF TABLES                                                                   |       |  |  |  |  |  |  |

| Table 1                | - Pin Lists Sorted by Function                                              |       |  |  |  |  |  |  |

| Table 2                | - The Number of Nodes and RAM Page Size                                     |       |  |  |  |  |  |  |

| Table 3                | - CPU Type                                                                  | 33    |  |  |  |  |  |  |

| Table 4                | - Distinction and Matching of the CPU Type                                  |       |  |  |  |  |  |  |

| Table 5<br>Table 6     | - Page Format of Packet Buffer Transmission Period According to Timer Setup |       |  |  |  |  |  |  |

| Table 6                | - CircLink Register Map                                                     |       |  |  |  |  |  |  |

| Table 8                | - TMC2074 128 Pin Package Parameters                                        |       |  |  |  |  |  |  |

| . abic o               | e_ee                                                                        | 1 1 1 |  |  |  |  |  |  |

# **Chapter 1 General Description**

### 1.1 About CircLink

The CircLink networking controller was developed for small control-oriented local network data communication based on ARCNET's token-passing protocol that guarantees message integrity and calculatable maximum cycle time.

In a CircLink network, when a node receives the token it becomes the temporary master of the network for a fixed, short period of time. No node can dominate the network since token control must be relinquished when transmission is complete. Once a transmission is completed the token is passed on to the next node (logical neighbor), allowing it to be come the master.

Because of this token passing scheme, maximum waiting time for network access can be calculated and the time performance of the network is predictable or deterministic. Control networking applications require predictable performance to ensure that controlled events occur when required. However, reconfiguration of a regular ARCNET network becomes necessary when the token is missed due to electronic and magnetic noise. In these cases, the maximum wait time for sending datagrams cannot be guaranteed and the real-time characteristic is impaired. CircLink makes several modification to the original ARCNET protocol (such as maximum and consecutive node ID assignment) to avoid token missing as much as possible and reduce the network reconfiguration time.

CircLink implements other enhancements to the ARCNET protocol including a smaller-sized network , shorter packet size, and remote buffer mode operation that enable more efficient and reliable small, control-oriented LANs. In addition, CircLink introduces several unique features for reducing overall system cost while increasing system reliability.

CircLink can operate under a special mode called "Standalone" or "I/O" mode. In this mode, CircLink does not need an administrating CPU for each node. Only one CPU is needed to manage a CircLink network composed up to maximum 31 nodes, reducing cost and complexity.

In a CircLink network, the data sent by the source node is received by all other nodes in the network and stored according to node source ID. For the target node the received data is executed per ARCNET flow control and the data is stored in its buffer RAM. The receiving node processes the data while the remaining nodes on the network discard the data when the receiving node has completed. This memory-mirroring function assures higher reliability and significantly reduces network traffic.

Network Standard Time (NST) is also a unique CircLink feature. NST is realized by synchronizing the individual local time on each network node to the clock master in the designated node from which the packet is sent. CircLink also uses CMI code for transmitting signals, rather than the dipulse or bipolar signals that are the standard ARCNET signals. Since CMI encoding eliminates the DC element, a simple combination of a standard RS485 IC and a pulse transformer can be used to implement a transformer-coupled network.

### 1.2 About TMC2074

The TMC2074 network controller is CircLink technology's flagship product. The TMC2074's flexibility and rich feature set enable a high-reliability and high-performance, real-time and control-oriented network without the cumbersome middle layer protocol stacks and complex packet prioritization schemes typically required.

TMC2074 operates at network data transfer rates up to 5 Mbps. Its embedded 1 kByte RAM can be configured into a maximum of 32 pages to implement a 31-node network where each node in the network has the same local memory.

The TMC2074 has two operational modes: "Peripheral Mode" and "Standalone Mode". It can operate with or without the existence of a system CPU on a network node. In Peripheral Mode, the TMC2074 has two selectable communication modes, "Free Format Mode" and "Remote Buffer Mode". Free Format mode, retained from ARCNET, is "packet oriented" communication. Remote Buffer mode communication is a CircLink-specific feature, and is a token oriented communication, which includes automatic data transmission when the token arrives.

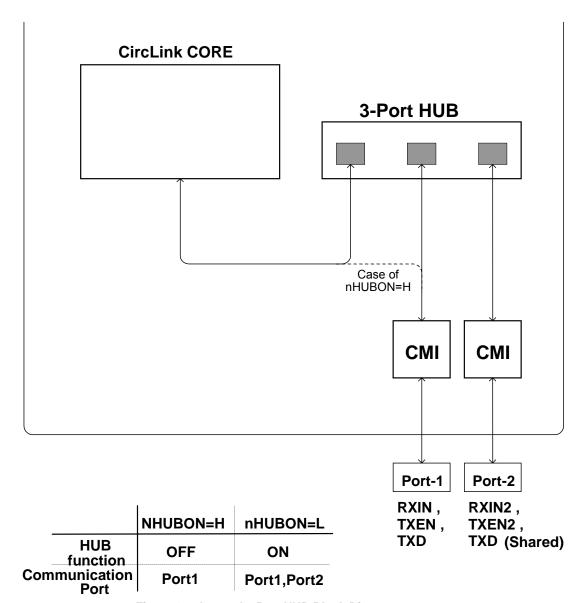

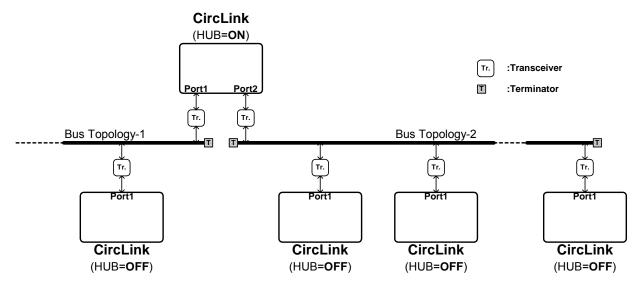

The TMC2074 has a flexible 8-bit or 16-bit databus to interface various CPU types including X86, 68XX, and SHX with multiplexed or non-multiplexed address/data. When operating in Peripheral mode, the TMC2074 has 8-bit programmable I/O available. When operating in Standalone mode, the TMC2074's I/O configuration is16-bit. The TMC2074 also integrates a 3-port hub (two ports for external connection) to accommodate various network topologies (Bus, Star, etc.) and combinations.

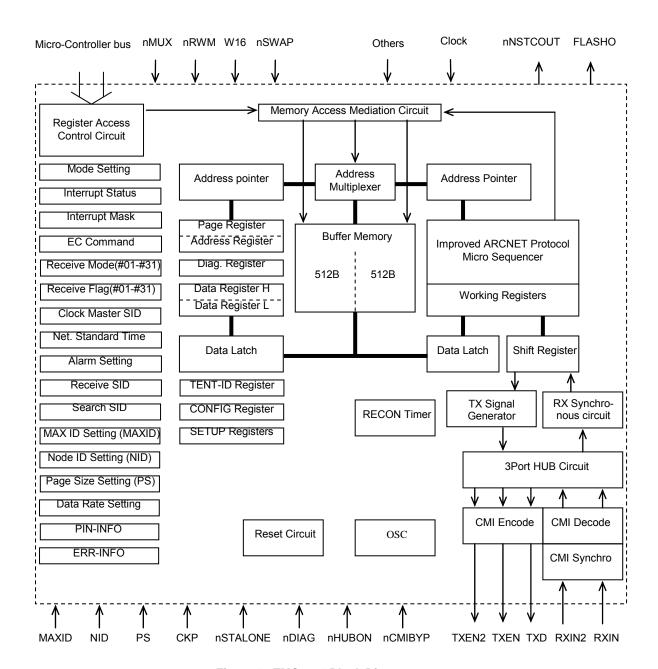

# 1.3 Internal Block Diagram

Figure 1 - TMC2074 Block Diagram

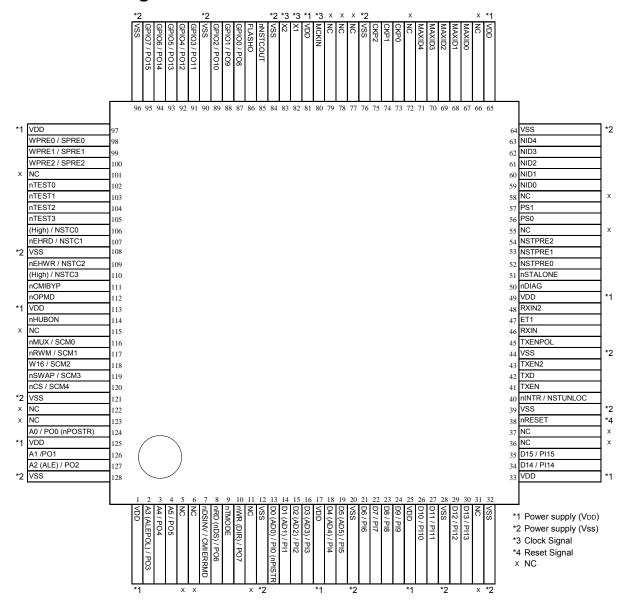

# 1.4 Pin Configuration

Figure 2 - Pin Names: Pin Name in Peripheral Mode/Pin Name in Standalone Mode

**Table 1- Pin Lists Sorted by Function**

| Pin           |           | Peripheral Mode |           | Standalone Mode |           | Input Buffer |       | Output Buffer |      |

|---------------|-----------|-----------------|-----------|-----------------|-----------|--------------|-------|---------------|------|

| Count Pin NO. |           | Pin Name        | Direction | Pin Name        | Direction | Pull-Up      | Type  | Drive         | Type |

| CPU I         | nterface  |                 |           |                 |           |              |       |               |      |

| 1             | 38        | nRESET          | IN        | nRESET          | IN        | Internal     | T-NRM |               |      |

| 2             | 120       | nCS             | IN        | SCM4            | IN        | Internal     | T-NRM |               |      |

| 3             | 124       | A0              | IN        | PO0/nPOSTR      | 3s/O      | Internal     | T-NRM | 4mA           |      |

| 4             | 126       | A1              | IN        | PO1             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 5             | 127       | A2/ALE          | IN        | PO2             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 6             | 2         | A3/ALEPOL       | IN        | PO3             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 7             | 3         | A4              | IN        | PO4             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 8             | 4         | A5              | IN        | PO5             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 9             | 8         | nRD/nDS         | IN        | PO6             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 10            | 10        | nWR/DIR         | IN        | PO7             | 3s.O      | Internal     | T-NRM | 4mA           |      |

| 11            | 13        | D0/AD0          | BI        | PI0/nPISTR      | IN        | Internal     | T-NRM | 4mA           |      |

| 12            | 14        | D1/AD1          | BI        | PI1             | IN        | Internal     | T-NRM | 4mA           |      |

| 13            | 15        | D2/AD2          | BI        | PI2             | IN        | Internal     | T-NRM | 4mA           |      |

| 14            | 16        | D3/AD3          | BI        | PI3             | IN        | Internal     | T-NRM | 4mA           |      |

| 15            | 18        | D4/AD4          | BI        | PI4             | IN        | Internal     | T-NRM | 4mA           |      |

| 16            | 19        | D5/AD5          | BI        | PI5             | IN        | Internal     | T-NRM | 4mA           |      |

| 17            | 21        | D6              | BI        | Pl6             | IN        | Internal     | T-NRM | 4mA           |      |

| 18            | 22        | D7              | BI        | PI7             | IN        | Internal     | T-NRM | 4mA           |      |

| 19            | 23        | D8              | BI        | PI8             | IN        | Internal     | T-NRM | 4mA           |      |

| 20            | 24        | D9              | BI        | PI9             | IN        | Internal     | T-NRM | 4mA           |      |

| 21            | 26        | D10             | BI        | PI10            | IN        | Internal     | T-NRM | 4mA           |      |

| 22            | 27        | D11             | BI        | PI11            | IN        | Internal     | T-NRM | 4mA           |      |

| 23            | 29        | D12             | BI        | PI12            | IN        | Internal     | T-NRM | 4mA           |      |

| 24            | 30        | D13             | BI        | PI13            | IN        | Internal     | T-NRM | 4mA           |      |

| 25            | 34        | D14             | BI        | PI14            | IN        | Internal     | T-NRM | 4mA           |      |

| 26            | 35        | D15             | BI        | PI15            | IN        | Internal     | T-NRM | 4mA           |      |

| 27            | 40        | nINTR           | OUT       | NSTUNLOC        | OUT       |              |       | 4mA           |      |

| Total:27      |           |                 |           |                 |           |              |       |               |      |

| Trans         | ceiver In | terface         |           |                 |           |              |       |               |      |

| 1             | 46        | RXIN            | IN        | RXIN            | IN        | Internal     | T-NRM |               |      |

| 2             | 41        | TXEN            | OUT       | TXEN            | OUT       |              |       | 4mA           |      |

| 3             | 42        | TXD             | OUT       | TXD             | OUT       |              |       | 4mA           |      |

| 4             | 48        | RXIN2           | IN        | RXIN2           | IN        | Internal     | T-NRM |               |      |

| 5             | 43        | TXEN2           | OUT       | TXEN2           | OUT       |              |       | 4mA           |      |

| Total:5       |           |                 |           |                 |           |              |       |               |      |

| Clock         |           |                 |           |                 |           |              |       |               |      |

| 1             | 82        | X1              | IN        | X1              | IN        |              |       |               |      |

| 2             | 83        | X2              | OUT       | X2              | OUT       |              |       |               |      |

| 3             | 80        | MCKIN           | IN        | MCKIN           | IN        | Internal     | T-NRM |               |      |

| Total:3       |           | I I             |           | 1               |           | •            | •     |               | •    |

| Pin      |            | Peripheral Mode |          | Standalone Mode |           | Input Buffer |       | Output Buffer |      |

|----------|------------|-----------------|----------|-----------------|-----------|--------------|-------|---------------|------|

| Count    | Pin NO.    | Pin Name        | Directon | Pin Name        | Direction | Pull-Up      | Type  | Drive         | Туре |

| Setup    | Pins       |                 | •        |                 |           |              |       |               |      |

| 1        | 116        | nMUX            | IN       | SCM0            | IN        | Internal     | T-NRM | _             |      |

| 2        | 117        | nRVM            | IN       | SOM             | IN        | Internal     | T-NRM | _             |      |

| 3        | 118        | W16             | IN       | SCM2            | IN        | Internal     | T-NRM | _             |      |

| 4        | 119        | nSWAP           | IN       | SOMB            | IN        | Internal     | T-NRM | _             |      |

| 5        | 52         | NSTPRE0         | IN       | NSTPRE0         | IN        | Internal     | T-NRM | -             |      |

| 6        | 53         | NSTPRE1         | IN       | NSTPRE1         | IN        | Internal     | T-NRM | _             | _    |

| 7        | 54         | NSTPRE2         | IN       | NSTPRE2         | IN        | Internal     | T-NRM | -             |      |

| 8        | 56         | PS0             | IN       | PS0             | IN        | Internal     | T-NRM | -             | _    |

| 9        | 57         | PS1             | IN       | PS1             | IN        | Internal     | T-NRM | _             | _    |

| 10       | 59         | NID0            | IN       | NID0            | IN        | Internal     | T-NRM | _             | _    |

| 11       | 60         | NID1            | IN       | ND1             | IN        | Internal     | T-NRM | -             |      |

| 12       | 61         | NID2            | IN       | NID2            | IN        | Internal     | T-NRM | -             | _    |

| 13       | 62         | NID3            | IN       | NID3            | IN        | Internal     | T-NRM | _             | _    |

| 14       | 63         | NID4            | IN       | ND4             | IN        | Internal     | T-NRM | -             | _    |

| 15       | 67         | MAXID0          | IN       | MAXID0          | IN        | Internal     | T-NRM | _             |      |

| 16       | 68         | MAXID1          | IN       | MAXID1          | IN        | Internal     | T-NRM | _             | _    |

| 17       | 69         | MAXID2          | IN       | MAXID2          | IN        | Internal     | T-NRM | _             |      |

| 18       | 70         | MAXID3          | IN       | MAXID3          | IN        | Internal     | T-NRM | _             |      |

| 19       | 71         | MAXID4          | IN       | MAXID4          | IN        | Internal     | T-NRM | _             | _    |

| 20       | 73         | CKP0            | IN       | CKP0            | IN        | Internal     | T-NRM | -             |      |

| 21       | 74         | CKP1            | IN       | CKP1            | IN        | Internal     | T-NRM | _             |      |

| 22       | <i>7</i> 5 | CKP2            | IN       | CKP2            | IN        | Internal     | T-NRM | _             |      |

| 23       | 51         | nSTALONE⇒H      | N        | nSTALONE⊨L      | IN        | Internal     | T-NRM | _             |      |

| 24       | 50         | nDIAG           | IN       | nDIAG           | IN        | Internal     | T-NRM | _             |      |

| 25       | 45         | TXENPOL         | IN       | TXENPOL         | IN        | Internal     | T-NRM | _             |      |

| 26       | 98         | WPRE0           | IN       | SPRE0           | IN        | Internal     | T-NRM | _             |      |

| 27       | 99         | WPRE1           | IN       | SPRE1           | IN        | Internal     | T-NRM | _             | _    |

| 28       | 100        | WPRE2           | IN       | SPRE2           | IN        | Internal     | T-NRM | _             |      |

| 29       | 106        | Un-USE(High)    | IN       | NSTCO           | IN        | Internal     | T-NRM | _             |      |

| 30       | 107        | n⊟⊣RD           | IN       | NSTC1           | IN        | Internal     | T-NRM | _             | _    |

| 31       | 109        | n⊟HWR           | IN       | NSTC2           | IN        | Internal     | T-NRM | _             |      |

| 32       | 110        | Un-USE(High)    | IN       | NSTC3           | IN        | Internal     | T-NRM | _             |      |

| 33       | 7          | nDSINV          | IN       | CMERRIMD        | IN        | Internal     | T-NRM | _             | _    |

| 34       | 111        | nCMBYP          | IN       | nCMBYP          | IN        | Internal     | T-NRM | _             | _    |

| 35       | 114        | nHJBON          | IN       | nHJBON          | IN        | Internal     | T-NRM | _             |      |

| 36       | 112        | nOPMD           | IN       | nOPMD           | IN        | Internal     | T-NRM | _             |      |

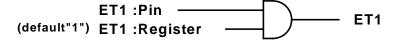

| 37       | 47         | ET1             | IN       | ET1             | IN        | Internal     | T-NRM | _             |      |

| Total:37 |            | LI.             | 1        | ı               |           | 1            |       | 1             | I .  |

| Pin      |                    | Peripheral Mode |           | Standalone Mode |           | Input Buffer |       | Output Bufer |      |

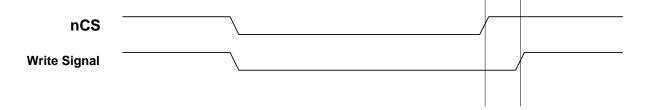

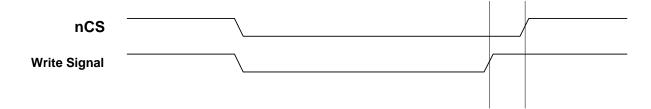

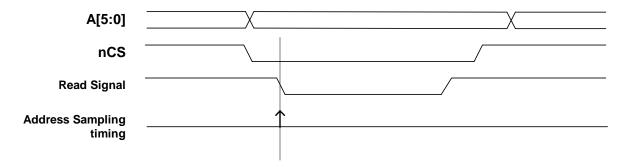

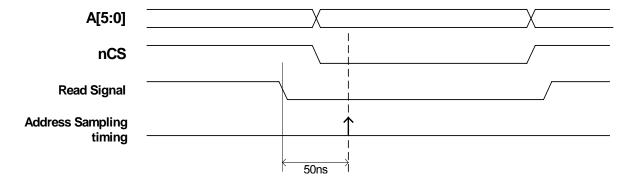

|----------|--------------------|-----------------|-----------|-----------------|-----------|--------------|-------|--------------|------|