# VRM10.0 COMPLIANT PROGRAMMABLE FEEDBACK DIVIDER

#### **FEATURES**

- VRM 10.x VID Code Table

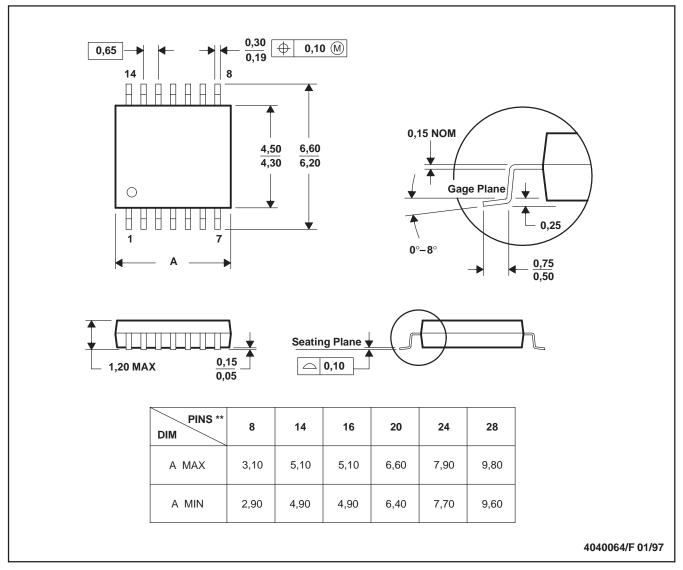

- 14-Pin TSSOP

#### **APPLICATIONS**

- Voltage Regulator Modules VRM/EVRD 10.x

- Multiphase Processor Power Supplies

#### **DESCRIPTION**

The TPS40120 is a 6-bit digitally programmed feedback divider designed to work with TPS40090 multiphase controller or other controllers having 0.7-V internal reference to support VRM 10.x compliant power supplies. The TPS40120 is designed to support discrete DC/DC converters for Intel<sup>®</sup> processors using 5-bit (Pentium<sup>®</sup> 4 or Xeon<sup>™</sup>) or 6-bit VID codes with 12.5 mV steps.

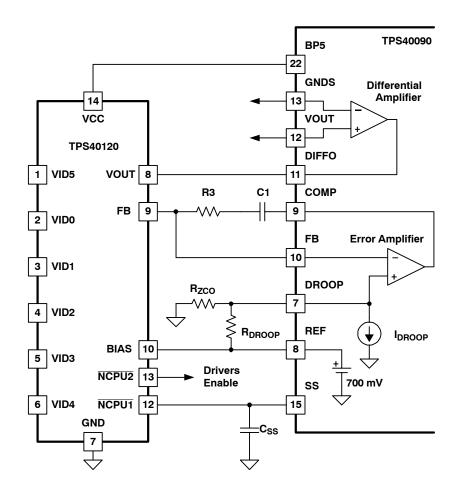

#### **TYPICAL APPLICATION**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOSFET gates.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PLASTIC HTTSOP <sup>(1)</sup> |

|----------------|-------------------------------|

| -40°C to 85°C  | TPS40120PW                    |

The PW package is available taped and reeled. Add an R suffix to the device type (i.el TPS40120PWR).

## **ABSOLUTE MAXIMUM RATING<sup>(1)</sup>**

over operating free-air temperature range unless otherwise noted

|                  |                                      |                                          | TPS40120    | UNITS |

|------------------|--------------------------------------|------------------------------------------|-------------|-------|

| V <sub>IN</sub>  | Input voltage range                  | VID0, VID1, VID2, VID3, VID4, VID5, VOUT | -0.3 to 5.5 | V     |

|                  | Output voltage range                 | FB, NCPU2                                | -0.3 to 5.5 |       |

| V <sub>OUT</sub> | Output voltage range                 | VCC, NCPU1                               | -0.3 to 7.0 | ] '   |

| T <sub>A</sub>   | Operating ambient temperature range  |                                          |             | - °C  |

| T <sub>stg</sub> | T <sub>stg</sub> Storage temperature |                                          |             | ]     |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

### RECOMMENDED OPERATING CONDITIONS

|                                                |                                          | MIN  | NOM | MAX | UNIT |

|------------------------------------------------|------------------------------------------|------|-----|-----|------|

| Supply voltage, VCC                            |                                          | 4.3  | 5.0 | 5.5 |      |

| I/O voltage range                              | VID0, VID1, VID2, VID3, VID4, VID5, VOUT | -0.1 | •   | 5.5 | V    |

| Operating free-air temperature, T <sub>A</sub> |                                          | -40  |     | 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                     | TEST CONDITIONS                                            | MIN                       | TYP | MAX                    | UNIT |

|--------------------|-------------------------------|------------------------------------------------------------|---------------------------|-----|------------------------|------|

| V <sub>VCC</sub>   | Supply voltatge               |                                                            | 4.3                       | 5.0 | 5.5                    | V    |

| I <sub>VCC</sub>   | Supply current                | All VID inputs low                                         |                           |     | 1                      | mA   |

| R <sub>FB</sub>    | Resistance between FB and OUT |                                                            | 7.5                       | 10  | 14.5                   | kΩ   |

|                    | Divider accuracy              |                                                            | -0.5%                     |     | 0.5%                   |      |

| VID <sub>THD</sub> | VID input logic high          |                                                            | 0.85                      |     |                        |      |

| VID <sub>THD</sub> | VID input logic low           |                                                            |                           |     | 0.3                    | V    |

| I <sub>BIAS</sub>  | BIAS input leakage            | V <sub>BIAS</sub> = 0.7 V                                  |                           |     | 100                    | μΑ   |

|                    | Logic low voltage             | I <sub>PULLUP</sub> = 1 mA                                 |                           |     | 0.8                    | V    |

|                    | Logic high leakage current    |                                                            |                           |     | 1                      | μΑ   |

|                    | No CPU output voltage         | I <sub>L(SNK)</sub> = 0.5 mA, I <sub>L(SRC)</sub> = 0.5 mA | V <sub>VSS</sub> +<br>0.5 |     | V <sub>VCC</sub> - 0.5 | V    |

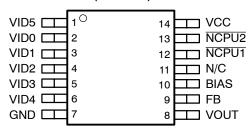

### **DEVICE INFORMATION**

#### PW PACKAGE (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TERMINAL |     | 1/0 | DECORIDATION                                                                                                                    |  |  |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                     |  |  |  |  |

| BIAS     | 10  | I   | Provides controller's reference voltage into the divider for improved tolerance.                                                |  |  |  |  |

| FB       | 9   | 0   | Middle point of the feedback divider connected to the inverting input of the controller's error amplifier                       |  |  |  |  |

| GND      | 7   | -   | Signal ground pin.                                                                                                              |  |  |  |  |

| NCPU1    | 12  | 0   | Signals no CPU state. VID = x111111. Open drain output.                                                                         |  |  |  |  |

| NCPU2    | 13  | 0   | Signals no CPU state. VID = x111111. TTL logic output.                                                                          |  |  |  |  |

| VCC      | 14  | I   | Power to the device.                                                                                                            |  |  |  |  |

| VID0     | 2   | I   |                                                                                                                                 |  |  |  |  |

| VID1     | 3   | I   |                                                                                                                                 |  |  |  |  |

| VID2     | 4   | I   | Voltage identification inputs. V <sub>REF</sub> voltage is set in accordance with VRM 10.x codes applied to                     |  |  |  |  |

| VID3     | 5   | I   | these pins.                                                                                                                     |  |  |  |  |

| VID4     | 6   | I   |                                                                                                                                 |  |  |  |  |

| VID5     | 1   | I   |                                                                                                                                 |  |  |  |  |

| VOUT     | 8   | 1   | This pin is connected to the output of the VR module or to the output of the differential amplifier of the TPS40090 controller. |  |  |  |  |

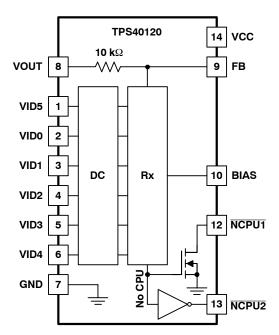

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **DETAILED DESCRIPTION**

## Operation

The digitally programmed feedback divider TPS40120 substitutes for a discrete output voltage set-divider and allows for multiphase PWM controllers such as the TPS4009x, TPS40130 and with internal reference of 0.7 V to provide voltage identification (VID) feature to power supply designs.

The TPS40120 operates as a resistive divider with constant value of the upper resistor and variable and code determined value of the lower resistor, refer to the functional block diagram. The VID code truth table is presented in Table 1.

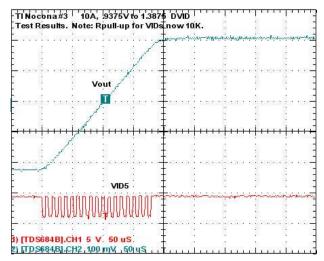

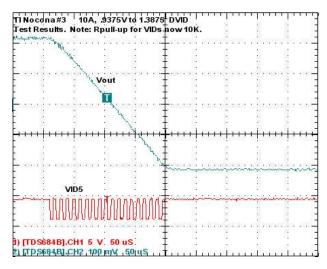

## **Dynamic VID**

Most modern processors adjust their core voltage depending on the workload and clock frequency by commanding voltage identification (VID) codes to the power supply. The power supply reads these VID codes and adjusts the output voltage in a control manner per processor requirements. To provide safe transition from one VID code to another (and to ensure that no erroneous output voltage is produced by the power supply), the TPS40120 VID inputs have internal anti-skew circuit with approximately 500 ns of filtering time. With a rate of change of 12.5 mV in 5  $\mu$ s, nothing else is required to achieve smooth upward and downward core voltage transitions. See Figure 1 and Figure 2.

Figure 2. VID Step-Down Transition

## **DETAILED DESCRIPTION (continued)**

Table 1. Voltage Identification (VID)

| PROCESSOR PINS (0=LOW, 1=HIGH) |      |      |      |      |      |                      |

|--------------------------------|------|------|------|------|------|----------------------|

| VID4                           | VID3 | VID2 | VID1 | VID0 | VID5 | V <sub>REF</sub> (V) |

| 0                              | 1    | 0    | 1    | 0    | 0    | 0.8375               |

| 0                              | 1    | 0    | 0    | 1    | 1    | 0.8500               |

| 0                              | 1    | 0    | 0    | 1    | 0    | 0.8625               |

| 0                              | 1    | 0    | 0    | 0    | 1    | 0.8750               |

| 0                              | 1    | 0    | 0    | 0    | 0    | 0.8875               |

| 0                              | 0    | 1    | 1    | 1    | 1    | 0.9000               |

| 0                              | 0    | 1    | 1    | 1    | 0    | 0.9125               |

| 0                              | 0    | 1    | 1    | 0    | 1    | 0.9250               |

| 0                              | 0    | 1    | 1    | 0    | 0    | 0.9375               |

| 0                              | 0    | 1    | 0    | 1    | 1    | 0.9500               |

| 0                              | 0    | 1    | 0    | 1    | 0    | 0.9625               |

| 0                              | 0    | 1    | 0    | 0    | 1    | 0.9750               |

| 0                              | 0    | 1    | 0    | 0    | 0    | 0.9875               |

| 0                              | 0    | 0    | 1    | 1    | 1    | 1.0000               |

| 0                              | 0    | 0    | 1    | 1    | 0    | 1.0125               |

| 0                              | 0    | 0    | 1    | 0    | 1    | 1.0250               |

| 0                              | 0    | 0    | 1    | 0    | 0    | 1.0375               |

| 0                              | 0    | 0    | 0    | 1    | 1    | 1.0500               |

| 0                              | 0    | 0    | 0    | 1    | 0    | 1.0625               |

| 0                              | 0    | 0    | 0    | 0    | 1    | 1.075                |

| 0                              | 0    | 0    | 0    | 0    | 0    | 1.0875               |

| 1                              | 1    | 1    | 1    | 1    | 1    | OFF <sup>(1)</sup>   |

| 1                              | 1    | 1    | 1    | 1    | 0    | OFF <sup>(1)</sup>   |

| 1                              | 1    | 1    | 1    | 0    | 1    | 1.1000               |

| 1                              | 1    | 1    | 1    | 0    | 0    | 1.1125               |

| 1                              | 1    | 1    | 0    | 1    | 1    | 1.1250               |

| 1                              | 1    | 1    | 0    | 1    | 0    | 1.1375               |

| 1                              | 1    | 1    | 0    | 0    | 1    | 1.1500               |

| 1                              | 1    | 1    | 0    | 0    | 0    | 1.1625               |

| 1                              | 1    | 0    | 1    | 1    | 1    | 1.1750               |

| 1                              | 1    | 0    | 1    | 1    | 0    | 1.1875               |

| 1                              | 1    | 0    | 1    | 0    | 1    | 1.2000               |

| 1                              | 1    | 0    | 1    | 0    | 0    | 1.2125               |

| 1                              | 1    | 0    | 0    | 1    | 1    | 1.2250               |

| 1                              | 1    | 0    | 0    | 1    | 0    | 1.2375               |

| 1                              | 1    | 0    | 0    | 0    | 1    | 1.2500               |

| 1                              | 1    | 0    | 0    | 0    | 0    | 1.2625               |

| 1                              | 0    | 1    | 1    | 1    | 1    | 1.2750               |

| 1                              | 0    | 1    | 1    | 1    | 0    | 1.2875               |

| 1                              | 0    | 1    | 1    | 0    | 1    | 1.3000               |

| 1                              | 0    | 1    | 1    | 0    | 0    | 1.3125               |

| 1                              | 0    | 1    | 0    | 1    | 1    | 1.3250               |

| 1                              | 0    | 1    | 0    | 1    | 0    | 1.3375               |

| 1                              | 0    | 1    | 0    | 0    | 1    | 1.3500               |

<sup>(1)</sup>  $\overline{\text{NCPU1}}$  and  $\overline{\text{NCPU2}}$  outputs go low.

## **DETAILED DESCRIPTION (continued)**

## Table 1. Voltage Identification (VID) (continued)

| PROCESSOR PINS (0=LOW, 1=HIGH) |      |      |      |      |      |                        |

|--------------------------------|------|------|------|------|------|------------------------|

| VID4                           | VID3 | VID2 | VID1 | VID0 | VID5 | - V <sub>REF</sub> (V) |

| 1                              | 0    | 1    | 0    | 0    | 0    | 1.3625                 |

| 1                              | 0    | 0    | 1    | 1    | 1    | 1.3750                 |

| 1                              | 0    | 0    | 1    | 1    | 0    | 1.3875                 |

| 1                              | 0    | 0    | 1    | 0    | 1    | 1.4000                 |

| 1                              | 0    | 0    | 1    | 0    | 0    | 1.4125                 |

| 1                              | 0    | 0    | 0    | 1    | 1    | 1.4250                 |

| 1                              | 0    | 0    | 0    | 1    | 0    | 1.4375                 |

| 1                              | 0    | 0    | 0    | 0    | 1    | 1.4500                 |

| 1                              | 0    | 0    | 0    | 0    | 0    | 1.4625                 |

| 0                              | 1    | 1    | 1    | 1    | 1    | 1.4750                 |

| 0                              | 1    | 1    | 1    | 1    | 0    | 1.4875                 |

| 0                              | 1    | 1    | 1    | 0    | 1    | 1.500                  |

| 0                              | 1    | 1    | 1    | 0    | 0    | 1.5125                 |

| 0                              | 1    | 1    | 0    | 1    | 1    | 1.5250                 |

| 0                              | 1    | 1    | 0    | 1    | 0    | 1.5375                 |

| 0                              | 1    | 1    | 0    | 0    | 1    | 1.5500                 |

| 0                              | 1    | 1    | 0    | 0    | 0    | 1.5625                 |

| 0                              | 1    | 0    | 1    | 1    | 1    | 1.5750                 |

| 0                              | 1    | 0    | 1    | 1    | 0    | 1.5875                 |

| 0                              | 1    | 0    | 1    | 0    | 1    | 1.6000                 |

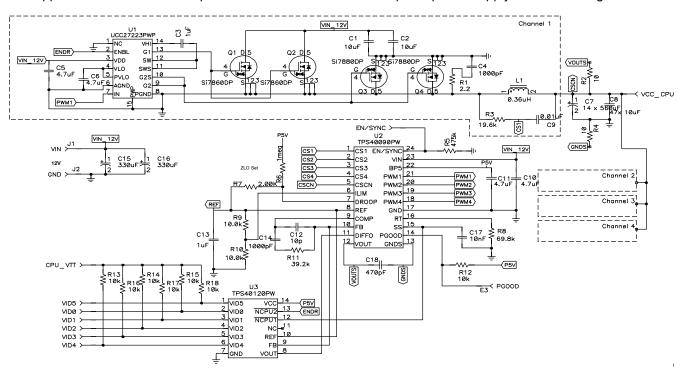

#### **APPLICATION INFORMATION**

Typical application circuit for TPS40120 and TPS40090 combination is presented on the front page. Normally, the TPS40120 accepts power from the BP5 pin of the TPS40090 multiphase controller which simplifies its enable/disable control. The upper resistor of the programmable divider (pin 8) is connected to the output of the differential amplifier DIFFO. The center tap of the divider (pin 9) is connected to the joint point of the FB pin of the multi-phase controller and error amplifier compensation network. TPS40120 has two logic NCPUx outputs that can be used to control output and the gate drivers in a multi-phase power supply when no-CPU code is asserted. The NCPU1 output is an open drain that can be useful by discharging the soft-start capacitor and bringing the output voltage down. The push-pull NCPU2 output can be used to control gate drivers to provide high impedance of the power supply output in off state.

The application circuit for a four-phase 105-A CPU VRM10.x compliant power supply is shown in Figure 3.

Figure 3. VRM 10.x Compliant CPU Power Supply

For detailed information on TPS40090 multiphase controller and design example request the TPS4009x datasheet (SLUS578) and the user's guide (SLUU026).

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| e               |

|-----------------|

| d               |

| trol            |

|                 |

| work            |

|                 |

|                 |

|                 |

|                 |

| d<br>trol<br>wo |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated