# X80070, X80071, X80072, X80073

### Data Sheet

### March 15, 2005

```

FN8150.0

```

## Hot Swap Controller with Advanced Fault Protection and Voltage Regulator Output

#### FEATURES

- Hot swap controller

- Overvoltage and undervoltage protection

- Undervoltage lockout for battery/redundant supplies

- Electronic circuit breaker

- Slew Rate for External FET Gate Control

- Overcurrent Detection and Gate Shut-off

- 3X overcurrent limit on insertion

- 5µs overcurrent filter

- Hardshort Retry and Indicator

- Typically operates from -30V to -80V. Tolerates transients to -200V (limited by external components)

- Positive Voltages (low side switching) from 12V to 60V

- Soft Re-insertion

- Soft extraction

- Battery backup mode

- Hardshort retry

- Overcurrent Filter

- Insertion Limits.

- Selectable Gate Current

- Voltage Regulator Output for Supervisory Functions

1

- Debounced manual reset input

- Available packages

- 20-lead Quad No-Lead Frame (QFN)

#### **APPLICATIONS**

- -48V Hot Swap Power Backplane/Distribution Central Office, Ethernet for VOIP

- Positive Voltage Hotswap 12V to 60V Applications (low side switching)

- Card Insertion Detection

- IP Phone Applications

- Databus Power Interfacing

- Custom Industrial Power Backplanes

- Distributed Power Systems

#### DESCRIPTION

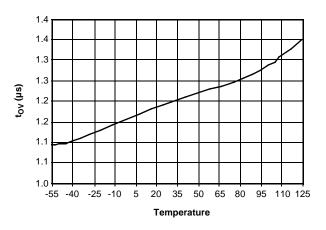

The X80070 is a hot swap controller that allows a board to be safely inserted and removed from a live backplane without turning off the main power supply.

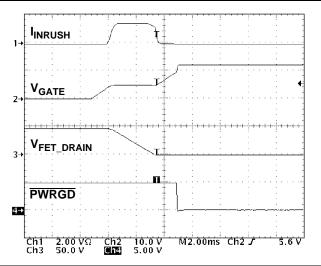

During insertion, the gate of an external power MOSFET is clamped low to suppress contact bounce. The undervoltage/overvoltage circuits and the power-on reset circuitry suppress the gate turn on until the mechanical bounce has ended. The X80070 turns on the gate with a slew rate to limit the inrush current and incorporates an electronic circuit breaker set by a sense resistor. After the load is successfully charged, the PWRGD signal is asserted; indicating that the device is ready to power sequence the DC-DC power bricks.

At all times, the X80070 monitors for undervoltage, overvoltage, and overcurrent conditions. If any fault occurs, the gate will be immediately shut off and the PWRGD will be returned to the inactive state. The X80070 contains overvoltage, undervoltage and overcurrent detection, hardshort retry, gate control slew rate and power good control.

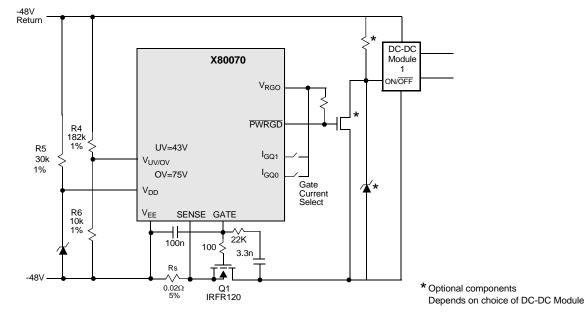

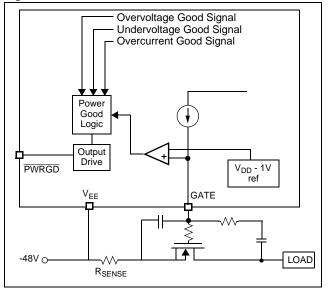

### TYPICAL APPLICATION

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-352-6832 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2005. All Rights Reserved All other trademarks mentioned are the property of their respective owners.

## ORDERING INFORMATION

| ORDER<br>NUMBER | 0V<br>(V) | UV1<br>(V) | UV2<br>(V) | t <sub>NF</sub><br>(us) | V <sub>OC</sub><br>(mV) | V <sub>OCI</sub><br>(mV) | Over-<br>current<br>Retry | Retry<br>Delay<br>(ms) | I <sub>GATE</sub><br>(uA) | T <sub>DELAY</sub><br>(ms) | t <sub>POR</sub><br>(ms) | Temp          | PART<br>MARK |

|-----------------|-----------|------------|------------|-------------------------|-------------------------|--------------------------|---------------------------|------------------------|---------------------------|----------------------------|--------------------------|---------------|--------------|

| X80070Q20I      | 74.9      | 42.4       | 33.2       | 5                       | 50                      | 150                      | Always                    | 100                    | 50                        | 100                        | 100                      | -40°C to 85°C | 800701       |

| X80071Q20I      | 68.0      | 42.4       | 33.2       | 5                       | 50                      | 150                      | Always                    | 100                    | 50                        | 100                        | 100                      | -40°C to 85°C | 800711       |

| X80072Q20I      | 74.9      | 42.4       | 33.2       | 5                       | 50                      | 150                      | 5 retries                 | 100                    | 50                        | 100                        | 100                      | -40°C to 85°C | 800721       |

| X80073Q20I      | 68.0      | 42.4       | 33.2       | 5                       | 50                      | 150                      | 5 retries                 | 100                    | 50                        | 100                        | 100                      | -40°C to 85°C | 800731       |

## ABSOLUTE MAXIMUM RATINGS

| Temperature under bias                  | 65°C to +135°C |

|-----------------------------------------|----------------|

| Storage temperature                     | 65°C to +150°C |

| Voltage on given pin (Hot Side Function | is):           |

|                                       | 5.5V + V <sub>FF</sub>            |

|---------------------------------------|-----------------------------------|

| V <sub>ov / uv pin</sub><br>SENSE pin | 400mV + V <sub>EE</sub>           |

| V <sub>EE</sub> pin                   | 80V                               |

| PWRGD pin                             | 7 V + V <sub>EE</sub>             |

| GATE pin                              | V <sub>DD</sub> + V <sub>EE</sub> |

| FAR pin                               |                                   |

| MR pin                                | 5.5V + V <sub>EE</sub>            |

| BATT-ON pin                           | 5.5V + V <sub>EE</sub>            |

Voltage on given pin (Cold Side Functions):

| IGQ1 and IGQ0 pins                       | 5.5V + V <sub>EE</sub> |

|------------------------------------------|------------------------|

| V <sub>DD</sub> pin                      | 14V + V <sub>EE</sub>  |

| D.C. output current                      | 5mĀ                    |

| Lead temperature (soldering, 10 seconds) | 300°C                  |

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Temperature           | Min.  | Max.  |  |  |  |  |

|-----------------------|-------|-------|--|--|--|--|

| Industrial            | -40°C | +85°C |  |  |  |  |

| Supply Voltage        |       |       |  |  |  |  |

| V <sub>DD</sub> = 12V |       |       |  |  |  |  |

## ELECTRICAL CHARACTERISTICS (Standard Settings)

(Over the recommended operating conditions unless otherwise specified).

| Symbol                          | Parameter                                                           | Min.                      | Тур.         | Max.                        | Unit | Test Conditions                                                                                                                                                  |

|---------------------------------|---------------------------------------------------------------------|---------------------------|--------------|-----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Charao                       | cteristics                                                          |                           |              |                             |      |                                                                                                                                                                  |

| V <sub>DD</sub>                 | Supply Operating Range                                              | 10                        | 12           | 14                          | V    |                                                                                                                                                                  |

| I <sub>DD</sub>                 | Supply Current                                                      |                           | 2.5          | 5                           | mA   |                                                                                                                                                                  |

| V <sub>RGO</sub>                | Regulated 5V output                                                 | 4.5                       |              | 5.5                         |      | I <sub>RGO</sub> = 10uA                                                                                                                                          |

| I <sub>RGO</sub>                | V <sub>RGO</sub> current output                                     |                           |              | 50                          | μA   |                                                                                                                                                                  |

| I <sub>GATE</sub>               | Gate Pin Current                                                    | 46.2                      | 52.5         | 58.8                        | μA   | Gate Drive On,<br>V <sub>GATE</sub> = V <sub>EE</sub> ,<br>V <sub>SENSE</sub> = V <sub>EE</sub> (sourcing)                                                       |

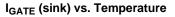

|                                 |                                                                     |                           | 9            |                             | mA   | $V_{GATE} - V_{EE} = 3V$<br>$V_{SENSE} - V_{EE} = 0.1V$ (sinking)                                                                                                |

| V <sub>GATE</sub>               | External Gate Drive (Slew Rate Con-<br>trol)                        | V <sub>DD</sub> -1        |              | V <sub>DD</sub>             | V    | I <sub>GATE</sub> = 50uA                                                                                                                                         |

| V <sub>PGA</sub>                | Power Good Threshold<br>(PWRGD High to Low)                         | 0.9                       | 1            | 1.1                         | V    | Referenced to V <sub>EE</sub><br>V <sub>UV1</sub> < V <sub>UV/OV</sub> < V <sub>OV</sub>                                                                         |

| V <sub>IHB</sub>                | Voltage Input High (BATT-ON)                                        | V <sub>EE</sub> + 4       |              | V <sub>EE</sub> + 5         | V    |                                                                                                                                                                  |

| $V_{ILB}$                       | Voltage Input Low (BATT-ON)                                         |                           |              | V <sub>EE</sub> + 2         | V    |                                                                                                                                                                  |

| I <sub>LI</sub>                 | Input Leakage Current (MR, IGQ0, IGQ1)                              |                           |              | 10                          | μA   | $V_{IL} = GND$ to $V_{CC}$                                                                                                                                       |

| ILO                             | Output Leakage Current (PWRGD)                                      |                           |              | 10                          | μA   | Gate is Off                                                                                                                                                      |

| V <sub>IL</sub>                 | Input LOW Voltage (MR, IGQ0, IGQ1)                                  | -0.5 + V <sub>EE</sub>    |              | (V <sub>EE</sub> + 5) x 0.3 | V    |                                                                                                                                                                  |

| VIH                             | Input HIGH Voltage (MR, IGQ0, IGQ1)                                 | $(V_{EE} + 5) \times 0.7$ |              | $(V_{EE} + 5) + 0.5$        | V    |                                                                                                                                                                  |

| V <sub>OL</sub>                 | Output LOW Voltage<br>(FAR, PWRGD)                                  |                           |              | V <sub>EE</sub> + 0.4       | V    | $I_{OL} = 4.0 \text{ mA}$<br>(V <sub>EE</sub> + 2.7 to V <sub>EE</sub> + 5.5V)<br>$I_{OL} = 2.0 \text{ mA}$<br>(V <sub>EE</sub> + 2.7 to V <sub>EE</sub> + 3.6V) |

| C <sub>OUT</sub> <sup>(1)</sup> | Output Capacitance (FAR)                                            |                           |              | 8                           | pF   | V <sub>OUT</sub> = 0V                                                                                                                                            |

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance (MR)                                              |                           |              | 6                           | pF   | $V_{IN} = 0V$                                                                                                                                                    |

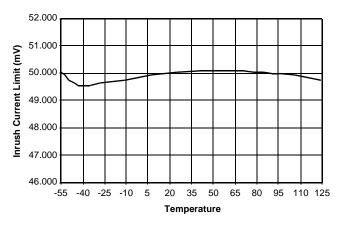

| V <sub>OC</sub>                 | Overcurrent threshold                                               | 45                        | 50           | 55                          | mV   | $V_{OC} = V_{SENSE} - V_{EE}$                                                                                                                                    |

| V <sub>OCI</sub>                | Overcurrent threshold (Insertion)                                   | 135                       | 150          | 165                         | mV   | V <sub>OC</sub> = V <sub>SENSE</sub> - V <sub>EE</sub><br>PWRGD = HIGH<br>Initial Power-up condition                                                             |

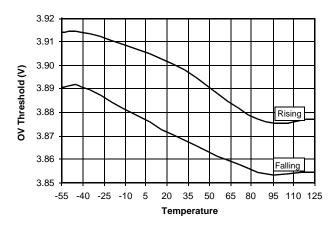

| V <sub>OVR</sub>                | Overvoltage threshold (rising)<br>X80070, X80072<br>X80071, X80073  | 3.85<br>3.49              | 3.90<br>3.54 | 3.95<br>3.59                | V    | Referenced to V <sub>EE</sub>                                                                                                                                    |

| V <sub>OVF</sub>                | Overvoltage threshold (falling)<br>X80070, X80072<br>X80071, X80073 | 3.82<br>3.46              | 3.87<br>3.51 | 3.92<br>3.56                | V    | Referenced to V <sub>EE</sub>                                                                                                                                    |

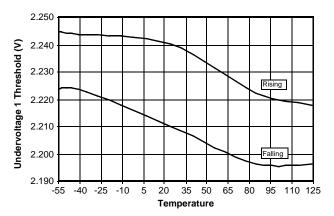

| V <sub>UV1R</sub>               | Undervoltage 1 threshold (rising)                                   | 2.19                      | 2.24         | 2.29                        | V    | Referenced to V <sub>EE</sub>                                                                                                                                    |

| V <sub>UV1F</sub>               | Undervoltage 1 threshold (falling)                                  | 2.16                      | 2.21         | 2.26                        | V    | BATT-ON = V <sub>EE</sub>                                                                                                                                        |

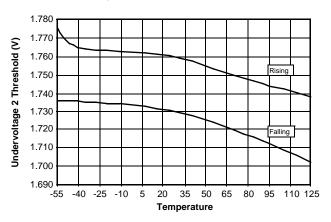

| $V_{UV2R}$                      | Undervoltage 2 threshold (rising)                                   | 1.71                      | 1.76         | 1.81                        | V    | Referenced to V <sub>EE</sub>                                                                                                                                    |

| V <sub>UV2F</sub>               | Undervoltage 2 threshold (falling)                                  | 1.68                      | 1.73         | 1.78                        | V    | BATT-ON = V <sub>RGO</sub>                                                                                                                                       |

| AC | Characteristics |

|----|-----------------|

|    |                 |

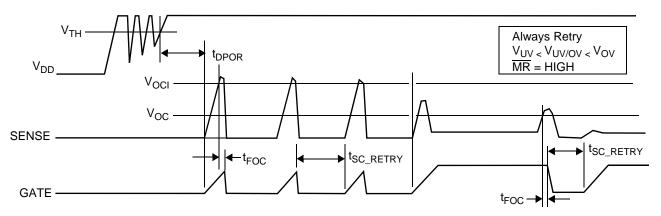

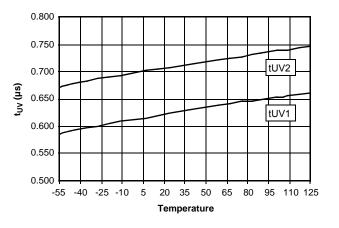

| t <sub>FOC</sub> Sense High to Gate Low | 1.5 | 2.5 | 3.5 | μS |  |

|-----------------------------------------|-----|-----|-----|----|--|

l

## ELECTRICAL CHARACTERISTICS (Standard Settings) (Continued)

(Over the recommended operating conditions unless otherwise specified).

| Symbol                | Parameter                                                           | Min. | Тур. | Max. | Unit | Test Conditions                                                         |

|-----------------------|---------------------------------------------------------------------|------|------|------|------|-------------------------------------------------------------------------|

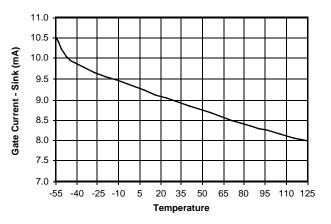

| t <sub>FUV</sub>      | Undervoltage conditions to Gate Low                                 | 0.5  | 1.0  | 1.5  | μS   |                                                                         |

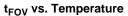

| t <sub>FOV</sub>      | Overvoltage Conditions to Gate Low                                  | 1.0  | 1.5  | 2    | μS   |                                                                         |

| t <sub>VFR</sub>      | Overvoltage/undervoltage failure re-<br>covery time to Gate =1V.    | 1.2  | 1.6  | 2    | μS   | V <sub>DD</sub> does not drop below 3V,<br>No other failure conditions. |

| t <sub>BATT-ON</sub>  | Delay BATT-ON Valid                                                 |      | 100  |      | ns   |                                                                         |

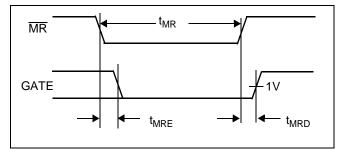

| t <sub>MR</sub>       | Minimum time high for reset valid on the $\overline{\text{MR}}$ pin | 5    |      |      | μS   |                                                                         |

| t <sub>MRE</sub>      | Delay from MR enable to Gate Pin<br>LOW                             | 1.0  | 1.6  | 2.4  | μS   | I <sub>GATE</sub> = 60μΑ, No Load                                       |

| t <sub>MRD</sub>      | Delay from MR disable to GATE reaching 1V                           | 1.8  |      | 2.6  | μS   | I <sub>GATE</sub> = 60μA, No Load                                       |

| t <sub>QC</sub>       | Delay from IGQ1 and IGQ0 to valid<br>Gate pin current               |      |      | 1    | μS   |                                                                         |

| t <sub>SC_RETRY</sub> | Delay between Retries                                               | 90   | 100  | 110  | ms   |                                                                         |

| t <sub>NF</sub>       | Noise Filter for Overcurrent                                        | 4.5  | 5    | 5.5  | μs   |                                                                         |

| t <sub>DPOR</sub>     | Device Delay before Gate assertion                                  | 45   | 50   | 55   | ms   |                                                                         |

Notes: (1) This parameter is based on characterization data.

## EQUIVALENT A.C. OUTPUT LOAD CIRCUIT

## A.C. TEST CONDITIONS

| Input pulse levels             | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9 |

|--------------------------------|------------------------------------------------|

| Input rise and fall times      | 10ns                                           |

| Input and output timing levels | V <sub>CC</sub> x 0.5                          |

| Output load                    | Standard output load                           |

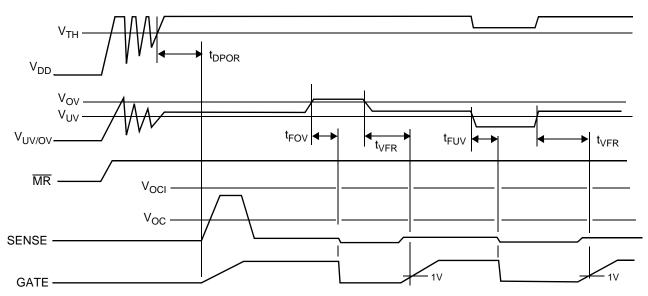

## Figure 1. Overvoltage/Undervoltage GATE Timing

## Figure 2. Overcurrent GATE Timing

## TYPICAL PERFORMANCE CHARACTERISTICS

**Overcurrent Threshold vs. Temperature**

**Overvoltage Threshold vs. Temperature**

Undervoltage 1 Threshold vs. Temperature

Undervoltage 2 Threshold vs. Temperature

## t<sub>FUV</sub> vs. Temperature

## Figure 4. Block Diagram

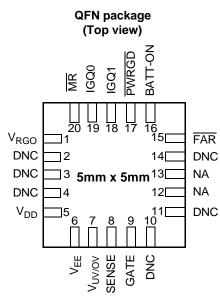

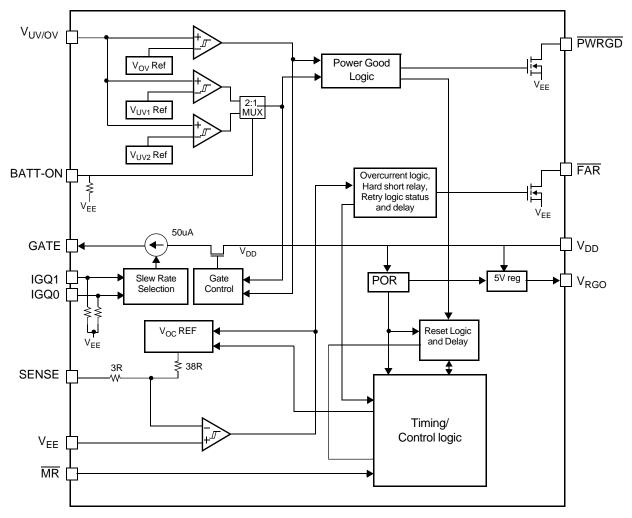

## PIN CONFIGURATION

NA2 pins connect to V<sub>EE</sub>

| Pin | Name               | Description                                   |

|-----|--------------------|-----------------------------------------------|

| 1   | V <sub>RGO</sub>   | Regulated 5V output. Used to pull-up          |

|     | KGO                | user programmable inputs IGQ0, IGQ1,          |

|     |                    | BATT-ON and MRH (if needed).                  |

| 2   | DNC                | Pin not used. Do not connect to this pin.     |

| 3   | NA2                | Not Available. Connect to V <sub>EE</sub> .   |

| 4   | NA2                | Not Available. Connect to V <sub>EE</sub> .   |

| 5   | V <sub>DD</sub>    | Positive Supply Voltage Input.                |

| 6   | V <sub>EE</sub>    | Negative Supply Voltage Input.                |

| 7   | V <sub>UV/OV</sub> | Analog Undervoltage and Overvoltage           |

|     |                    | Input. Turns off the external N-channel       |

|     |                    | MOSFET when there is an undervoltage          |

|     |                    | or overvoltage condition.                     |

| 8   | SENSE              | Circuit Breaker Sense Input. This input       |

|     |                    | pin detects the overcurrent condition.        |

| 9   | GATE               | FET Gate Drive. This pin supplies the cur-    |

|     |                    | rent to turn on the FET.                      |

| 10  | DNC                | Pin not used. Do not connect to this pin.     |

| 11  | DNC                | Pin not used. Do not connect to this pin.     |

| 12  | NA1                | Not Available. Connect to V <sub>RGO</sub> .  |

| 13  | NA1                | Not Available. Connect to V <sub>RGO</sub> .  |

| 14  | NA2                | Not Available. Connect to V <sub>EE</sub> .   |

| 15  | FAR                | Failure After Re-try (FAR) output signal.     |

| 16  | BATT-ON            | Battery On Input. This input signals that     |

|     |                    | the battery backup (or secondary supply)      |

|     |                    | is supplying power to the backplane. It has   |

|     |                    | an internal pulldown resistor. (>10M $\Omega$ |

|     |                    | typical)                                      |

| 17  | PWRGD              | Power Good Output. This output pin en-        |

|     |                    | ables a power module.                         |

| Pin | Name | Description                                                                                                                                                                                                                                                      |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | IGQ1 | Gate Current Quick Select Bit 1 Input.<br>This pin is used to change the gate current<br>drive and is intended to allow for current<br>ramp rate control of the gate pin of an<br>external FET. It has an internal pulldown<br>resistor. (>10M $\Omega$ typical) |

| 19  | IGQ0 | Gate Current Quick Select Bit 0 Input.<br>This pin is used to change the gate current<br>drive and is intended to allow for current<br>ramp rate control of the gate pin of an<br>external FET. It has an internal pulldown<br>resistor. (>10M $\Omega$ typical) |

| 20  | MR   | <b>Manual Reset.</b> Pulling the $\overline{MR}$ pin LOW initiates a GATE pin reset (GATE pin pulled LOW). The $\overline{MR}$ signal must be held LOW for 5µsecs (minimum).                                                                                     |

## FUNCTIONAL DESCRIPTION

### Hot Circuit Insertion

When circuit boards are inserted into a live backplane, the bypass capacitors at the input of the board's power module or DC/DC converter can draw huge transient currents as they charge up. This transient current can cause permanent damage to the board's components and cause transients on the system power supply.

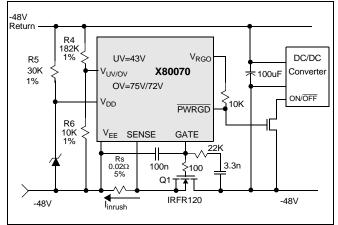

The X80070 is designed to turn on a board's supply voltage in a controlled manner (see Figure 5), allowing the board to be safely inserted or removed from a live backplane. The device also provides undervoltage, overvoltage and overcurrent protection while keeping the power module (dc-dc converter) off until the backplane input voltage is stable and within tolerance.

### Figure 6. Typical -48V Hotswap Application circuit

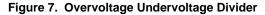

#### Overvoltage and Undervoltage Shutdown

The X80070 provides overvoltage and undervoltage protection circuits.

When an overvoltage (V<sub>OV</sub>) or undervoltage (V<sub>UV1</sub> and V<sub>UV2</sub>) condition is detected, the GATE pin immediately pulls low turning off the supply to the system. The undervoltage threshold V<sub>UV1</sub> applies to the normal operation with a main supply. The undervoltage threshold V<sub>UV2</sub> assumes the system is powered by a battery. When using a battery backup, the BATT-ON pin is pulled to V<sub>RG0</sub>. The default thresholds have been set so the external resistance values in Figure 6 provide an overvoltage threshold of 74.9V (X80070 and X80072) or 68V (X80071 and X80073), a main undervoltage threshold of 43V and a battery undervoltage threshold of 33.8V.

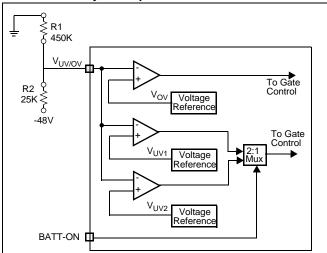

As shown in Figure 9, this circuit block contains comparators and voltage references to monitor for a single overvoltage and dual undervoltage trip points. The overvoltage and undervoltage trip points as shown in Table 1 below.

|                  |                            | Threshold |        |                         |                                 |

|------------------|----------------------------|-----------|--------|-------------------------|---------------------------------|

| Symbol           | Description                | falling   | rising | Max/Min<br>Voltage<br>1 | Lockout<br>Voltage <sup>2</sup> |

| V <sub>OV</sub>  | Overvoltage (X80070/72)    | 3.87V     | 3.9V   | 74.3                    | 74.9                            |

| V <sub>OV</sub>  | Overvoltage<br>(X80071/73) | 3.51V     | 3.54V  | 67.4                    | 68                              |

| V <sub>UV1</sub> | Undervoltage 1             | 2.21V     | 2.24V  | 43.0                    | 42.4                            |

| V <sub>UV2</sub> | Undervoltage 2             | 1.73V     | 1.76V  | 33.8                    | 33.2                            |

Notes: 1: Max/Min Voltage is the maximum and mimimum operating voltage assuming the recommended V<sub>UV/OV</sub> resistor divider.

2: Lockout voltage is the voltage where the X8007x turns off the FET.

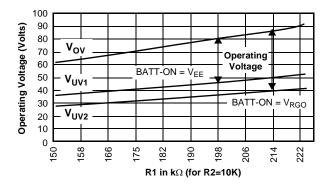

A resistor divider connected between the plus and minus input voltages and the  $V_{UV/OV}$  pin (see Figure 7) determines the overvoltage and undervoltage shutdown voltages and the operating voltage range. Using the thresholds in Table 1 and

the equations of Figure 7 the desired operating voltage can be determined. Figure 8 shows the resistance values for various operating voltages (X80070 and X80072).

Figure 8. Operating voltage vs. resistor ratio

#### Battery back up operations

An external signal, BATT-ON is provided to switch the undervoltage trip point. The BATT-ON signal is a LOGIC HIGH if  $V_{IHB} > V_{EE} + 4V$  and is a LOGIC LOW if  $V_{ILB} < V_{EE} + 2V$ . The time from a BATT-ON input change to a valid new undervoltage threshold is 100ns. See Electrical Specifications for more details.

Note: The V<sub>UV/OV</sub> pin must be limited to less than V<sub>EE</sub> + 5.5V. in worst case conditions. Values for R1 and R2 must be chosen such that this condition is met. Intersil recommends R1 =  $182k\Omega$  and R2 =  $10k\Omega$  to conform to factory settings. These should be 1% resistors.

Table 2. Selecting between Undervoltage Trip Points

|         | -           |                                          |

|---------|-------------|------------------------------------------|

| Pin     | Description | Trip Point Selection                     |

| BATT-ON | 0           | If BATT-ON = $0$ ,                       |

|         | Trip Point  | V <sub>UV1</sub> trip point is selected; |

|         |             | If BATT-ON = 1,                          |

|         |             | V <sub>UV2</sub> trip point is selected. |

$V_{UV1}$  and  $V_{UV2}$  are undervoltage thresholds.

#### Figure 9. Overvoltage/Undervoltage for Primary and Battery Backup

### **Overcurrent Protection (Circuit Breaker Function)**

The X80070 overcurrent circuit provides the following functions:

- Overcurrent shut-down of the power FET and external power good indicators.

- Noise filtering of the current monitor input.

- Relaxed overcurrent limits for initial board insertion.

- Overcurrent recovery retry operation.

#### **Overcurrent shut-down**

A sense resistor, placed in the supply path between V<sub>EE</sub> and SENSE (see Figure 6) generates a voltage internal to the X80070. When this voltage exceeds 50mV, an overcurrent condition exists and an internal "circuit breaker" trips, turning off the gate drive to the external FET. The actual overcurrent level is dependent on the value of the current sense resistor. For example a 20m $\Omega$  sense resistor sets the overcurrent level to 2.5A.

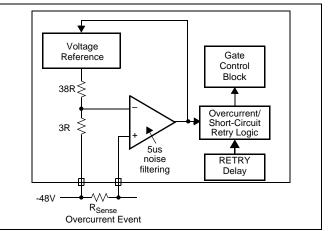

As shown in Figure 10, this overcurrent circuit block contains a resistor ladder, a comparator, a noise filter and a voltage reference to monitor for overcurrent conditions.

The overcurrent voltage threshold (V\_{OC}) is 50mV. This can be factory set, by special order, to any setting between 30mV and 100mV.

If an overcurrent condition is detected, the GATE output is shut down and the power good indicator goes inactive.

#### **Overcurrent during insertion**

Insertion is defined as the first plug-in of the board to the backplane. In this case, the X80070 is initially fully powered off prior to the hot plug connection to the main supply. This condition is different from a situation where the main supply has temporarily failed resulting in a partial recycle of the power. This second condition will be referred to as a power cycle.

During insertion, the board can experience high levels of current for short periods of time as power supply capacitors charge up on the power bus. To prevent the overcurrent sensor from turning off the FET inadvertently, the X80070 has the ability to allow more current to flow through the power FET and the sense resistor for a short period of time until the FET turns on and the <u>PWRGD</u> signal goes active.

In the X80070, 150mV is allowed across sense resistor during insertion (7.5A assuming a 20mW resistor). This provides a mechanism to reduce insertion issues associated with huge current surges. Insertion currents of 1X, 2X, or 4X are also available. Please contact Intersil for these factory options.

After the PWRGD signal is asserted, the X80070 switches back to the normal overcurrent setting.

#### Hardshort Protection - (Retry)

In the event on an overcurrent or hard short condition, the X80070 includes a retry circuit. This circuit waits for 100ms, then attempts to again turn on the FET. If the fault condition still exists, the FET turns off and the sequence repeats. For versions X80070 and X80072, this process continues indefinely until the overcurrent condition does not exist. For the X80071 and X80073, this process repeats five times only, then will keep the FET off and set the FAR pin active. After FAR is asserted, it can be cleared using the master reset pin, MR, or cycling the power-on  $V_{\text{DD}}$ . When using the MR pin, the FAR output is cleared upon MR assertion.

If an overcurrent condition does not occur on any retry, the gate pin will proceed to open at the user defined slew rate.

#### Figure 10. Overcurrent Detection/Short Circuit Protection.

#### **Overcurrent noise filter**

The X80070 has a noise (low pass) filter built into the overcurrent comparator. The comparator will thus require the current spikes to exceed the overcurrent limit for more than  $5\mu$ s.

#### Gate Drive Output Slew Rate (Inrush Current) Control

The gate output drives an external N-Channel FET. The GATE pin goes high when no overcurrent, undervoltage or overvoltage conditions exist.

The X80070 provides an  $I_{GATE}$  current of 50uA to provide onchip slew rate control to minimize inrush current and provide the best turn on time for a given load, while avoiding overcurrent conditions.

#### Slew Rate (Gate) Control

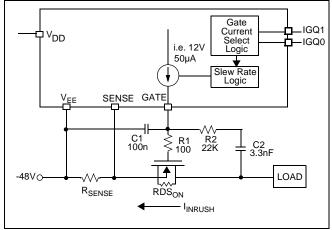

As shown in Figure 11, this circuit block contains a current source ( $I_{GATE}$ ) that drives the 50uA current into the GATE pin. This current provides a controlled slew rate for the FET.

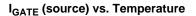

To give the designer flexibility in the design of the hot swap circuit, the X80070 provides two external pins, IGQ1 and IGQ0. These pins allow the user to switch to different GATE currents on-the-fly by selecting one of four pre-selected I<sub>GATE</sub> currents. When IGQ0 and IGQ1 are left unconnected, the gate current is 50uA. The other three settings are 10uA, 70uA and 150uA, as shown in Table 3.

Table 3. IGQ Gate Current Selection

| IGQ1<br>pin | IGQ0<br>pin | Operation                     |  |

|-------------|-------------|-------------------------------|--|

| 0           | 0           | Defaults to gate current 50µA |  |

| 0           | 1           | Gate Current is 10µA          |  |

| 1           | 0           | Gate Current is 70µA          |  |

| 1           | 1           | Gate Current is 150µA         |  |

Typically, the delay from IGQ1 and IGQ0 selection to a change in the GATE pin current is less than 1  $\mu second.$

Figure 11. Slew Rate (Inrush Current) Control

## Gate Capacitor, Filtering and Feedback

The FET control circuit includes an FET feedback capacitor  $C_2$ , which provides compensation for the FET during turn on. The capacitor value depends on the load, the choice of FET (because of the FET internal capacitances) and the FET gate current.

The value of C2 can be selected with the following formula.

$$C2 = \frac{I_{GATE} \times C_{LOAD}}{I_{INRUSH}}$$

Where:

I<sub>GATE</sub> = FET Gate current

I<sub>INRUSH</sub> = Maximum desired inrush current

C<sub>LOAD</sub> = DC/DC bulk capacitance

With the X80070, there is some control of the gate current with the IGQ pins, so one selection of C2 can cover a wide range of possible loading conditions. Typical values for C2 range from 2.2 to 4.7nF.

When power is applied to the system, the FET tries to turn on due to its internal gate to drain capacitance (Cgd) and the feedback capacitor C2 (see Figure 11.) The X80070 device, when powered, pulls the gate output low to prevent the gate voltage from rising and keep the FET from turning on. However, unless  $V_{DD}$  powers up very quickly, there will be a brief period of time during initial application of power when the X80070 circuits cannot hold the gate low. The use of an external capacitor (C1) prevents this. Capacitors C1 and C2 form a voltage divider to prevent the gate voltage from rising above the FET turn on threshold before the X80070 can hold the gate low. Use the following formula for choosing C1.

$$C1 = \frac{V1 - V2}{V2}C2$$

Where:

V1 = Maximum input voltage,

V2 = FET threshold Voltage,

- C1 = Gate capacitor,

- C2 = Feedback capacitor.

In a system where V<sub>DD</sub> rises very fast, a smaller value of C1 may suffice as the X80070 will control voltage at the gate before the voltage can rise to the FET turn on threshold. The circuit of Figure 11 assumes that the input voltage can rise to 80V before the X80070 sees operational voltage on V<sub>DD</sub>. If C1 is used then the series resistor R1 will be required to revent high frequency oscillations.

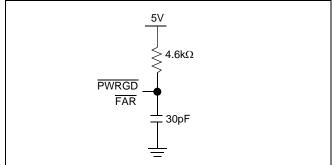

### **Power Good Indication**

The PWRGD signal asserts (Logic LOW) only when all of the below conditions are true:

- there is no overvoltage or no undervoltage condition, (i.e. undervoltage < V<sub>EE</sub> < overvoltage.)</li>

- There is no overcurrent condition (i.e. V<sub>EE</sub> V<sub>SENSE</sub> < V<sub>OC</sub>.)

- The FET is turned on (i.e.  $V_{GATE} > V_{DD} 1V$ )

As shown in Figure 12, this circuit block contains a comparator, and an internal voltage reference. These provide a circuit to determine the whether the gate drive to the FET has fully turned on as requested. If so, the power good indicator (PWRGD) goes active.

#### Figure 12. Power Good Indicator

## Manual Reset

The X80070 has a manual reset pin.  $\overline{\text{MR}}$  (manual reset). The  $\overline{\text{MR}}$  signal is used as a manual reset for the GATE pin. This pin is used to initiate Soft Reinsert. When  $\overline{\text{MR}}$  is pulled LOW the GATE pin will be pulled LOW. It also clears the  $\overline{\text{FAR}}$  signal. When the  $\overline{\text{MR}}$  pin goes HIGH, it removes the override signal and the gate will turn on based on the selected gate control mechanism. (See Figure 3.)

| Table 4. | Manual Reset | (Gate Signal) |

|----------|--------------|---------------|

|----------|--------------|---------------|

| MR | Gate Pin    | Requirements                   |

|----|-------------|--------------------------------|

| 1  | Operational | When MR is HIGH the reset      |

|    |             | function is disabled           |

| 0  | OFF         | MR must be held LOW minimum of |

|    |             | 5µsecs                         |

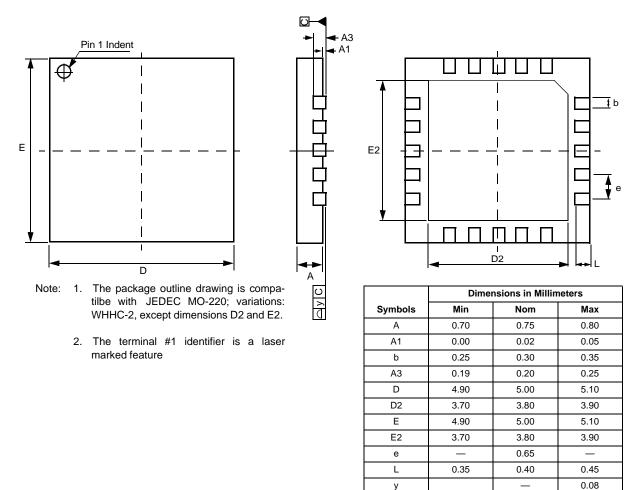

### PACKAGING INFORMATION

20-Lead Quad Flat No Lead Package (Package Code: Q20) 5mm x 5mm Body with 0.65mm Lead Pitch

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com