# **Product Description**

Sirenza Microdevices' **XD010-12S-D4F** 15W power module is a robust 2-stage Class A/AB amplifier module for use in the driver stages of cellular base station power amplifiers. The power transistors are fabricated using Sirenza's latest, high performance LDMOS process. It is a drop-in, no-tune, solution for high power applications requiring high efficiency, excellent linearity, and unit-to-unit repeatability. This unit operates from a single voltage supply and has internal temperature compensation of the bias voltage to ensure stable performance over the full temperature range. It is internally matched to 50 ohms.

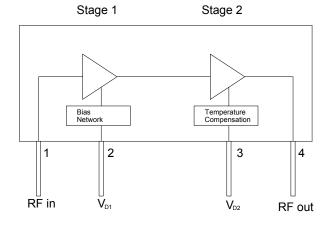

### **Functional Block Diagram**

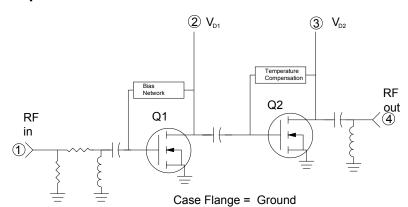

Case Flange = Ground

# XD010-12S-D4F

# 869-894 MHz Class AB 15W Power Amplifier Module

#### **Product Features**

- 50  $\Omega$  RF impedance

- 15W Output P<sub>1dB</sub>

- Single Supply Operation : Nominally 28V

- High Gain: 32 dB at 880 MHz

- Robust 8000V ESD (HBM), Class 3B

- XeMOS II LDMOS FETS

- Temperature Compensation

# **Applications**

- Base Station PA driver

- Repeater

- CDMA / WCDMA

- GSM / EDGE

### **Key Specifications**

| Symbol               | Parameter                                                                                               | Unit | Min. | Тур. | Max. |

|----------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| Frequency            | Frequency of Operation                                                                                  | MHz  | 869  | -    | 894  |

| P <sub>1dB</sub>     | Output Power at 1dB Compression, 880MHz                                                                 | W    | 12   | 15   | -    |

| Gain                 | Gain at 1W Output Power, 880MHz                                                                         | dB   | 30   | 32   | -    |

| Gain Flatness        | Peak to Peak Gain Variation, 869 - 894MHz                                                               | dB   | -    | 0.2  | 1.0  |

| IRL                  | Input Return Loss 1W Output Power, 869 - 894MHz                                                         | dB   | 14   | 17   | -    |

|                      | Drain Efficiency at 12W CW, 880MHz                                                                      | %    | 27   | 33   | -    |

| Efficiency           | Drain Efficiency at 2W CDMA (Single Carrier IS-95)                                                      | %    | -    | 12   | -    |

|                      | Drain Efficiency at 1W CDMA (Single Carrier IS-95)                                                      | %    | -    | 7    | -    |

|                      | ACPR at 2W CDMA (Single Carrier IS-95, 9 Ch Fwd, Off-<br>set=750KHz, ACPR Integrated Bandwidth), 880MHz | dB   | -    | -51  | -    |

| Linearity            | ALT-1 at 2W CDMA (Single Carrier IS-95, 9 Ch Fwd, Offset=1980KHz, ACPR Integrated Bandwidth), 880MHz    | dB   | -    | -70  | -    |

|                      | 3 <sup>rd</sup> Order IMD at 12W PEP (Two Tone), 880MHz                                                 | dBc  | -    | -36  | -32  |

|                      | 3 <sup>rd</sup> Order IMD at 1W PEP (Two Tone), 880MHz                                                  | dBc  | -    | -45  | -    |

| Delay                | Signal Delay from Pin 1 to Pin 4                                                                        | nS   | -    | 2.5  | -    |

| Phase Linearity      | Deviation from Linear Phase (Peak to Peak)                                                              | Deg  | -    | 0.5  | -    |

| R <sub>TH, j-l</sub> | Thermal Resistance Stage 1 (Junction to Case)                                                           | °C/W | -    | 11   | -    |

| R <sub>TH, j-2</sub> | Thermal Resistance Stage 2 (Junction to Case)                                                           | °C/W | -    | 4    | -    |

# **Quality Specifications**

| Parameter  |                                                  | Unit  | Typical               |

|------------|--------------------------------------------------|-------|-----------------------|

| ESD Rating | Human Body Model, JEDEC Document - JESD22-A114-B | V     | 8000                  |

| MTTF       | 85°C Leadframe, 200°C Channel                    | Hours | 1.2 X 10 <sup>6</sup> |

### Pin Description

| Pin#   | Function        | Description                                                                                                                                                                                                                                   |  |  |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1      | RF Input        | Module RF input. This pin is internally connected to DC ground. Do not apply DC voltages to the RF leads. Care must be taken to protect against video transients that may damage the active devices.                                          |  |  |

| 2      | V <sub>D1</sub> | This is the drain voltage for the first stage. Nominally +28Vdc                                                                                                                                                                               |  |  |

| 3      | $V_{D2}$        | This is the drain voltage for the 2 <sup>nd</sup> stage of the amplifier module. The 2 <sup>nd</sup> stage gate bias is temperature compensated to maintain constant quiscent drain current over the operating temperature range. See Note 1. |  |  |

| 4      | RF Output       | Module RF output. This pin is internally connected to DC ground. Do not apply DC voltages to the RF leads. Care must be taken to protect against video transients that may damage the active devices.                                         |  |  |

| Flange | Gnd             | Exposed area on the bottom side of the package needs to be mechanically attached to the ground plane of the board for optimum thermal and RF performance. See mounting instructions in application note AN-060 on Sirenza's web site.         |  |  |

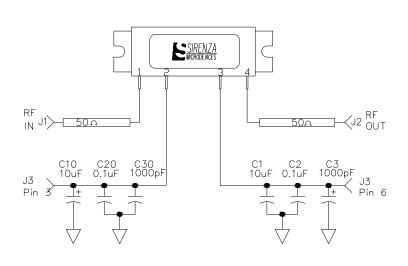

# **Simplified Device Schematic**

### **Absolute Maximum Ratings**

| - 110 C C 1 C C C C C C C C C C C C C C C              |             |      |  |  |

|--------------------------------------------------------|-------------|------|--|--|

| Parameters                                             | Value       | Unit |  |  |

| 1 <sup>st</sup> Stage Bias Voltage (V <sub>D1</sub> )  | 35          | V    |  |  |

| 2 <sup>nd</sup> Stage Bias Voltage (V <sub>D2</sub> )  | 35          | V    |  |  |

| RF Input Power                                         | +20         | dBm  |  |  |

| Load Impedance for Continuous Operation Without Damage | 5:1         | VSWR |  |  |

| Output Device Channel Temperature                      | +200        | °C   |  |  |

| Operating Temperature Range                            | -20 to +90  | °C   |  |  |

| Storage Temperature Range                              | -40 to +100 | °C   |  |  |

Operation of this device beyond any one of these limits may cause permanent damage. For reliable continuous operation see typical setup values specified in the table on page one.

#### **Caution: ESD Sensitive**

Appropriate precaution in handling, packaging and testing devices must be observed.

#### Note 1:

The internally generated gate voltage is thermally compensated to maintain constant quiescent current over the temperature range listed in the data sheet. No compensation is provided for gain changes with temperature. This can only be accomplished with AGC external to the module.

#### Note 2:

Internal RF decoupling is included on all bias leads. No additional bypass elements are required, however some applications may require energy storage on the drain leads to accommodate time-varying waveforms.

#### Note 3:

This module was designed to have its leads hand soldered to an adjacent PCB. The maximum soldering iron tip temperature should not exceed 700° C, and the soldering iron tip should not be in direct contact with the lead for longer than 10 seconds. Refer to app note AN060 (www.sirenza.com) for further installation instructions.

Phone: (800) SMI-MMIC

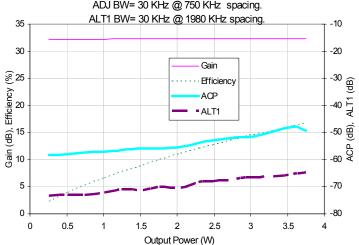

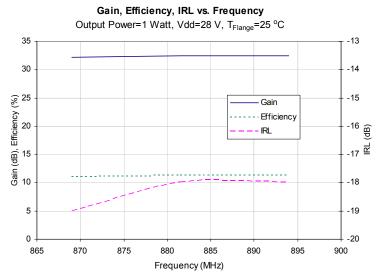

# **Typical Performance Curves**

Freq=881 MHz, Vdd=28 V,  $T_{Flange}$ =25 °C IS95 standard, channel BW= 1.23 MHz. ADJ BW= 30 KHz @ 750 KHz spacing.

Gain, Efficiency, ACP, ALT1 vs. Output Power

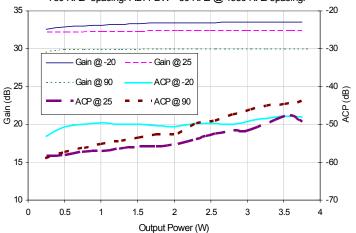

#### Gain, ACP vs. Output Power over Temperature

Freq=881 MHz, Vdd=28 V,  $T_{Flange}$ =-20 °C, 25 °C, 90 °C IS95 standard, channel BW= 1.23 MHz. ADJ BW= 30 KHz @ 750 KHz spacing. ALT1 BW= 30 KHz @ 1980 KHz spacing.

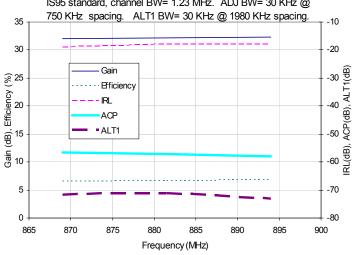

#### Gain, Efficiency, IRL, ACP, ALT1 vs. Frequency

Output Power= 1 Watt Vdd=28 V,  $T_{Flange}$ =25 °C IS95 standard, channel BW= 1.23 MHz. ADJ BW= 30 KHz @

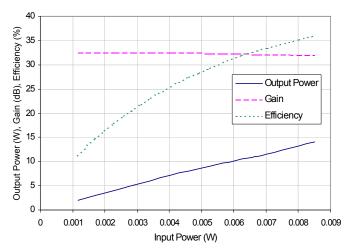

#### Output Power, Gain, Efficiency vs. Input Power

Freq=881 MHz, Vdd=28 V,  $T_{Flange}$ =25 $^{\circ}$ C

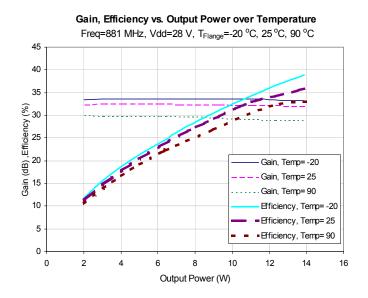

# **Typical Performance Curves (cont'd)**

# Test Board Schematic with module connections shown

### **Test Board Bill of Materials**

| Component          | Description                                                         | Manufacturer |  |

|--------------------|---------------------------------------------------------------------|--------------|--|

| РСВ                | Rogers 4350, $\varepsilon_{\rm r}$ =3.5<br>Thickness=30mils         | Rogers       |  |

| J1, J2             | SMA, RF, Panel Mount Tab W / Flange                                 | Johnson      |  |

| J3                 | MTA Post Header, 6 Pin, Rect-<br>angle, Polarized, Surface<br>Mount | AMP          |  |

| C1, C10            | Cap, 10 $\mu$ F, 35V, 10%, Tant, Elect, D                           | Kemet        |  |

| C2, C20            | Cap, 0.1 $\mu$ F, 100V, 10%, 1206                                   | Johanson     |  |

| C3, C30            | Cap, 1000pF, 100V, 10%, 1206                                        | Johanson     |  |

| C25, C26           | Cap, 68pF, 250V, 5%, 0603                                           | ATC          |  |

| C21, C22           | Cap, 0.1 $\mu$ F, 100V, 10%, 0805                                   | Panasonic    |  |

| C23, C24           | Cap, 1000pF, 100V, 10%, 0603                                        | AVX          |  |

| Mounting<br>Screws | 4-40 X 0.250"                                                       | Various      |  |

|                    |                                                                     |              |  |

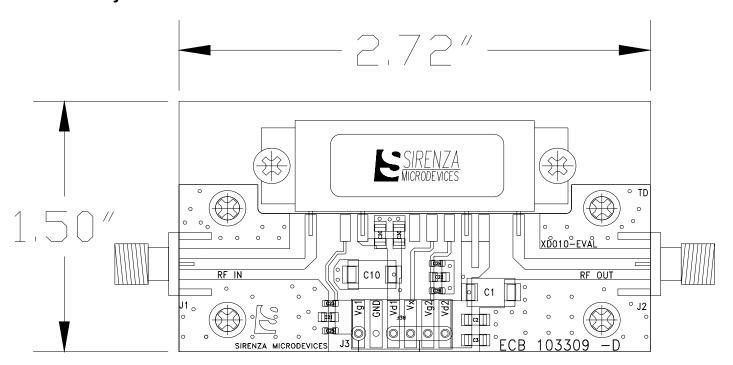

# **Test Board Layout**

To receive Gerber files, DXF drawings, a detailed BOM, and assembly recommendations for the test board with fixture, contact applications support at <a href="mailto:support@sirenza.com">support@sirenza.com</a>. Data sheet for evaluation circuit (XD010-EVAL) available from Sirenza website.

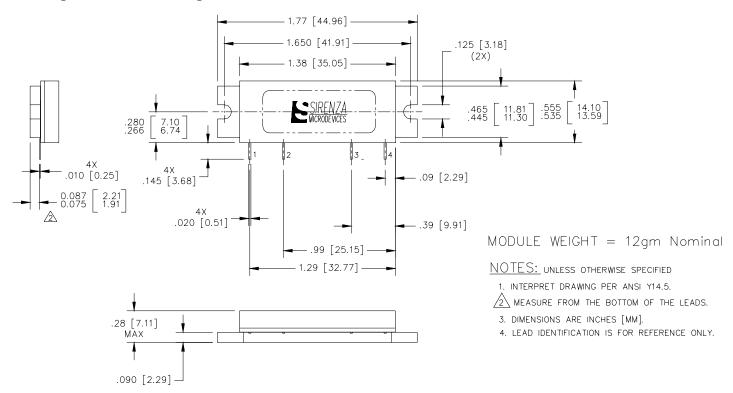

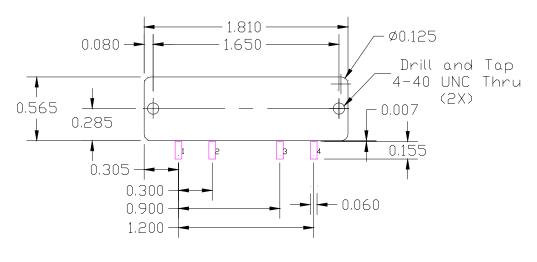

# **Package Outline Drawing**

# Recommended PCB Cutout and Landing Pads for the D4F Package

Note 3: Dimensions are in inches

Refer to Application note AN-060 "Installation Instructions for XD Module Series" for additional mounting info. App note availbale at at www.sirenza.com