# DSP控制器及貝应用

章 云 谢莉萍 熊红艳 编著

# 目 录

| 前音                                | 3.2.1 结构概述                                                | 67  |

|-----------------------------------|-----------------------------------------------------------|-----|

| Andre a state door to be          | 3.2.2 模/数转换控制与操作                                          | 70  |

| 第 1 章 概述                          | ··· 1 3.3 SCI 串行通信接口模块 ···········                        | 71  |

| 1.1 引言                            | <sub>1</sub> 3.3.1 串行通信的工作原理 ············                 | 71  |

| 1.2 二进制、补码及其运算                    | 990 电分隔传换电槽块 501 66                                       |     |

| 1.2.1 数制                          | 6+ M                                                      | 74  |

| 1.2.2 补码与加、乘运算                    | o o o Ar-Mar VE Ar-                                       | 83  |

| 1.3 DSP 控制器的基本原理 ·············    | 이 4 CDT 由 红 시 2/L +ò rz +# ++                             | 84  |

|                                   | 3.4.1 串行外设接口结构与工作                                         |     |

| 第2章 总体结构                          | ・ 11 原理                                                   | 85  |

| 2.1 总线结构                          | · 12 3.4.2 SPI 的多机通信 ···································· | 91  |

| 2.2 中央处理单元                        | う ょう CDI 司 脚 th 能 64 44 怪                                 | 94  |

| 2.2.1 输入比例部分                      | 9 5 数字 1/0 端月                                             | 95  |

| 2.2.2 中央算术逻辑部分                    | 2.5.1 数字 1/0 端口螺丝                                         | 95  |

| 2.2.3 乘法部分                        | 9 5 9 数字 7/0 磁点要发腿                                        | 97  |

| 2.3 辅助寄存器算术单元                     | った 軽け焼 医が叶蛙                                               | 98  |

| 2.4 状态寄存器 STO 和 ST1 ············· | 2.7 由斯倫理系统                                                | 02  |

| 2.5 存储器与 I/O 空间                   | 2.7.1 DSD (杜拉比斯                                           | 02  |

| 2.5.1 与外部存储器和 I/O 空间接口            | 3.7.2 事件管理模块的中断 ········ 1                                | 06  |

| 的信号                               | . 70 3.7.3 系统模块中断 1                                       | 10  |

| 2.5.2 程序存储器                       |                                                           | 112 |

| 2.5.3 局部数据存储器                     | No. 1 - 1 14 4 15 144 1                                   | 12  |

| 2.5.4 全局数据存储器                     | , a <u>===================================</u>            | 12  |

| 2.5.5 1/0 空间                      |                                                           | 12  |

| 2.6 程序控制                          | · 26 4.1.2 直接寻址 ················ I                        |     |

| 2.7 时钟源模块                         | 4.1.2 阿林里村 t                                              | 14  |

| 2.8 系统复位                          | 4 0 年                                                     | 17  |

| 2.0 未乳及证                          | 4.2.1 汇编句法格式 1                                            | 17  |

| 第3章 片内外设                          | · 35 4.2.2 指令分类表 ······· I                                | 19  |

| 3.1 事件管理模块                        | 35 4.3 传送指令                                               | 23  |

| 3.1.1 適用定时器                       | <del>/// 1. 14 // 1// /</del>                             | 42  |

| 3.1.2 比较单元与 PWM 发                 | 4.5 逻辑运算指令                                                | 55  |

| 生器                                | 50 4.6 分支转移指令                                             | 61  |

| 3.1.3 梢获单元                        | 61                                                        |     |

| 3.1.4 正交编码脉冲电路                    | 70 4 TE NV ED 312 100                                     | 70  |

| 3.2 模/数转换模块                       |                                                           |     |

|       | 频 | 器            | 170 | <b>小是</b> |     |          |           | <br>182 |

|-------|---|--------------|-----|-----------|-----|----------|-----------|---------|

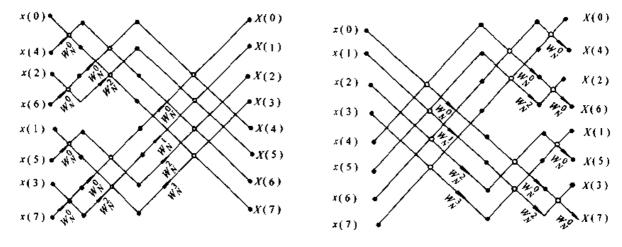

| 5.2   | 快 | 速傳里叶变换 (FFT) | 173 | PI) 35    |     |          |           | 102     |

| 5. 2. | 1 | 快速傅里叶变换的基本   |     | 附录 A      | A I | DSP240 引 | 脚说明       | <br>182 |

|       |   | 原理           | 173 | 附录E       | 3 ī | 可编程寄存    | 字器汇总      | <br>189 |

| 5. 2. | 2 | 快速傅里叶变换的 DSP |     | 附录(       | 2 1 | 指令汇总     |           | <br>191 |

|       |   | 实现           | 177 | 参考文       | 捕さ  |          | ********* | <br>197 |

# 第1章 概 述

### 1.1 引言

随着 1946 年第一台电子计算机的诞生,一场数字化的技术革命悄然地引发。如果说当初计算机的出现纯粹是为了解决日益复杂的计算问题,那么现在计算机已无处不在。自动控制与计算机几乎是同步地发展着。自动控制系统的核心问题是如何寻找和实现最佳的控制律。在 A/D、D/A 以及 I/O 技术出现并成熟之后,最佳控制律的实现问题就变成了最佳控制律的运算 (代数、微分、积分等运算)问题,从而计算机作为自动控制系统的核心部分就是自然之事。

计算机真正在自动控制系统中发挥重要作用还得缘起 20 世纪 70 年代微处理器(Microprocessor)的出现,它使得计算机在体积、价格上得以突破,为计算机在各种技术领域的应用提供了可能。微处理器即计算机的中央处理单元(CPU)和控制单元的集成,它配上一定的存储器、I/O 接口和其它外设,就可构成自动控制系统的通用控制器。70 年代 Intel 公司的8080,Motorola 公司的 M6800 和 Zilog 公司的 Z80 是当时三个著名的 8 位徽处理器。

随着大规模集成电路技术不断改进,一方面微处理器由 8 位向 16 位、32 位甚至 64 位发展,在配上外围设备后便形成单板机或微型机(也称为个人计算机,Personal Computer),使得计算机不但在计算、控制中应用,而且使得计算机逐步地走人了家庭;另一方面将微处理器与外围设备集成到一块芯片形成单片机(Single\_chip Microcomputer),以适应控制器体积越来越小的工程要求。

正是由于单片机的出现,计算机在控制领域的应用又得到了一次突破。单片机不但小巧、成本低,而且由于众多设备集成到了一块芯片上带来了功耗小和抗干扰能力强的优点。另外,它可以方便地组成各种智能式控制设备和仪器,做到机电仪一体化;也可以方便地实现多机和分布式控制,使整个控制系统的效率和可靠性大为提高。单片机有许多类型,有低档的1位、4位和8位单片机,也有高档的8位、16位单片机。其中Intel公司的MCS-51系列、Motorola公司的68系列和Zilog公司的Z8系列为大家所知。

DSP (Digital Signal Processor) 实际上也是一种单片机,它同样是将中央处理单元、控制单元和外围设备集成到一块芯片上。DSP 最早是针对数字信号处理,特别是语音、图像信号的各种处理而开发的。由于这类信号处理的算法复杂,要求 DSP 必须具有强大快速的运算能力。因此,DSP 有别于普通的单片机,它采用了多组总线技术实现并行运行机制,从而极大地提高了运算速度,也提供了非常灵活的指令系统。近些年来,各种集成化单片 DSP 的性能不断得以改进,相应的软件和开发工具日臻完善,价格迅速下降,使得 DSP 在控制领域的应用倍受关注。

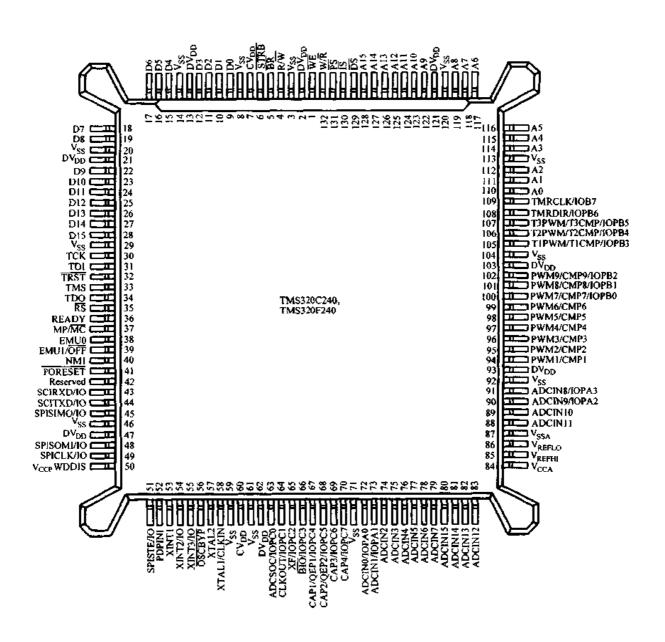

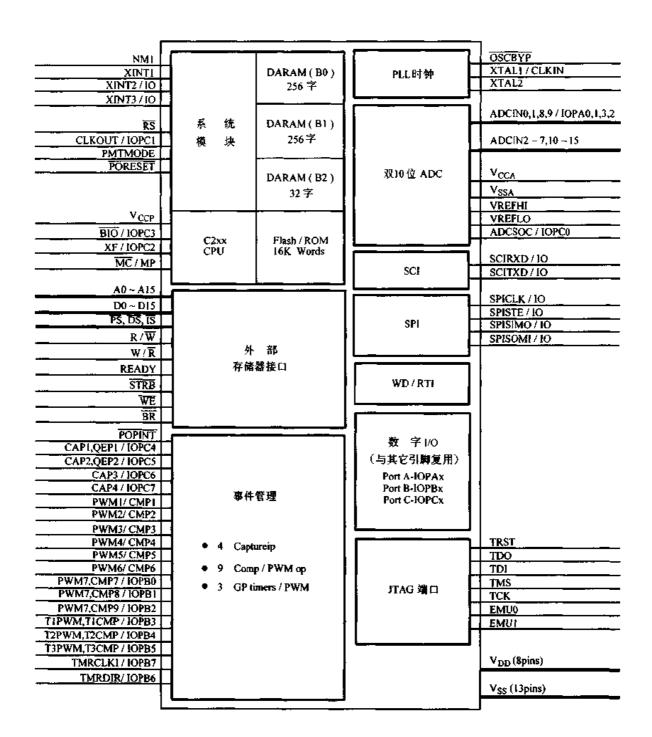

在 DSP 领域中, 德州仪器 (TI) 公司的产品及其配套技术与开发工具最有强大的竞争力, 其中 TMS320 DSP 是它的代表系列, 本书以 TMS320C24X 进行介绍。TMS320C24X 也称为 DSP 控制器, 是 TI 公司专门针对电机、逆变器、机器人、数控机床等控制而设计的。它以 C2XLP 16bit 定点 DSP CPU 为内核,配置了完善的外围设备,包括事件管理模块(EV)、A/D 转换模块(ADC)、串行通信接口模块(SCI)、串行外设接口模块(SPI)、中断管理系统和系统监视模块,其中事件管理模块(EV)含有通用定时器、比较器、PWM 发生器、捕获器。

DSP 控制器的结构和主要特性如下:

- □中央处理单元

- 32 位中央算术逻辑单元 (CALU)。

- ●32 位累加器。

- 16 位×16 位乘法器。

- ●3个比例移位器。

- ●间接寻址用的 8 个 16 位辅助寄存器和它的辅助算术单元 (ARAU)。

- □存储器

- 544 字片内双口 RAM, 其中 288 字用于数据, 256 字用于程序/数据。

- ●16K 字片内 ROM 或 FLASH EEPROM, 用作程序存储器。

- ●244K 字可寻址空间,程序存储空间 64K 字,数据存储空间 64K 字, I/O 空间 64K 字,还有 32K 字全局存储空间。

- ●外部有 16 位地址总线, 16 位数据总线, 支持软件、硬件等待状态。

- □程序控制

- ●4级流水线操作。

- ●8级硬件堆栈。

- 6 个外部中断:电源保护、复位、不可屏蔽中断(NMI)和 3 个可屏蔽中断。

- □指令集

- ●源代码与定点 TMS320C2X、C2XX、C5X 兼容。

- ●单周期相乘/累加指令。

- ●单指令重复操作。

- ●程序/数据存储器中的块移动。

- ●丰富的变址寻址能力。

- ●具有基于 2 的 FFT 倒位序变址寻址能力。

- □事件管理模块

- ●3个16位通用定时器。

- ●3个全比较/PWM单元。

- ●3个简单比较/PWM单元。

- ●4个捕获单元。

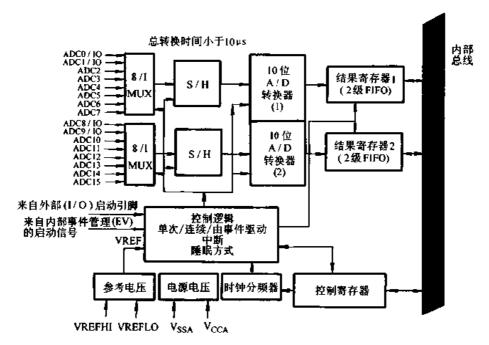

- □2 个 8 通道 10 位 A/D 转换器

- □串行异步数字通信接口模块(SCI)

- □串行外设接口模块(SPI)

- □中断管理系统

- □由看门狗和实时中断定时器组成的系统监视模块

- □28 个可独立编程的 I/O 引脚

- □速度

●单周期指令执行时间为 50ns (20MIPS)。

### □电源

- 5V 或 3. 3V 静态 CMOS 工艺。

- ●4种降低功耗的方式。

### 1.2 二进制、补码及其运算

DSP 控制器就是一款高性能的单片机。运算是单片机(计算机)的主要任务,为此首先 简单介绍二进制、补码及其运算的实现方法。

二进制数是计算机原理看似最简单的内容,但却是最容易弄混淆的。对于计算机,它的基本任务是:从某个"地方"取数,按某种规律运算,再把结果放到某个"地方"。这里"地方"是指存储器、I/O 接口等。因此,地址与数据是计算机中两个基本概念。由于计算机只存在"0"、"1"两种状态,因此在计算机中地址、数据都是二进制数表示。另外,数据存在着正数与负数、整数与小数,为了区别它们还必须产生用二进制数表示的编码系统。这样一来,在计算机中给出的一个二进制数到底是地址还是数据、是正数还是负数、是整数还是小数,常常让人跟花缭乱。本节着重介绍二进制数的编码系统及其特点,至于寻址问题将在第4章介绍。

### 1.2.1 数制

在日常生活中经常使用的是十进制数,由 0~9十个符号组成,按照逢十进一的规则运算。由于计算机只存在 "0"、"1"两种状态,故计算机中的数用二进制表示。二进制数只有 0 和 1 两个符号,按照逢二进一的规则运算。与二进制密切相关的是十六进制,它由 0~9、A~F 共 16 个符号组成,按照逢十六进一的规则运算。为了以示区别,二进制数以后级 "B"表示,十六进制数以后级 "H"表示。二进制数与十进制数、十六进制数与十进制数的关系如下:

$$[b_{n-1}b_{n-2}\cdots b_0 \cdot b_{-1}b_{-2}\cdots b_{-m}]_{\mathsf{B}} = b_{n-1} \times 2^{n-1} + b_{n-2} \times 2^{n-2} + \cdots + b_0 \times 2^0$$

$$+ b_{-1} \times 2^{-1} + b_{-2} \times 2^{-2} + \cdots + b_{-m} \times 2^{-m}$$

$$[h_{n-1}h_{n-2}\cdots h_0 \cdot h_{-1}h_{-2}\cdots h_{-m}]_{\mathsf{H}} = h_{n-1} \times 16^{n-1} + h_{n-2} \times 16^{n-2} + \cdots + h_0 \times 16^0$$

$$+ h_{-1} \times 16^{-1} + h_{-2} \times 16^{-2} + \cdots + h_{-m} \times 16^{-m}$$

例 1.1 将下列二进制数、十六进制数转换为十进制。

1011.

$$101_B = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-8}$$

= 11. 625

1011.

$$101_{H} = 1 \times 16^{3} + 0 \times 16^{2} + 1 \times 16^{1} + 1 \times 16^{0} + 1 \times 16^{-1} + 0 \times 16^{-2} + 1 \times 16^{-3}$$

= 4113.0627

由于 2<sup>4</sup>=16, 因此 1 位十六进制数可用 4 位二进制数表示, 它们之间的关系见表 1·1。这样一来, 二进制数与十六进制数的转换非常方便。

例 1.2 二进制数与十六进制数的转换。

计算机除了受 "0"、"1" 两种状态的限制外,还受到数据长度的限制。在计算机中数据总线的位数是有限的,一般有8位、16位或32位。用8位二进制数表示的数据称为一个字节,

可以表示  $0\sim255$  的无符号整数;用 16 位二进制数表示的数据称为一个字,可以表示  $0\sim65535$  的无符号整数;用 32 位二进制数表示的数据称为一个双字,可以表示  $0\sim2^{32}-1$  的无符号整数。一般情况下,用 n 位的二进制数表示无符号整数的范围是: $0\sim2^{n}-1$ 。由于数据位数的限制,在进行数据运算时要注意数据表示的范围、否则将会发生溢出错误。

| 十 进 制 | ナ六进制 | 二进制  | 十 进 制 | 十六进制 | 进制   |

|-------|------|------|-------|------|------|

| 0     | 0    | 0000 | 8     | 8    | 1000 |

| 1     | ı    | 0001 | 9     | 9    | 1001 |

| 2     | 2    | 0010 | 10    | A    | 1010 |

| 3     | 3    | 0011 | 11    | В    | 1011 |

| 4     | 4    | 0100 | 12    | C    | 1100 |

| 5     | 5    | 0101 | 13    | D    | 1101 |

| 6     | 6    | 0110 | 14    | E    | 1110 |

| 7     | 7    | 0111 | 15    | F    | 1111 |

表 1.1 十进制与二进制、十六进制的关系

除了要注意数据表示的范围外,还要关注数据的符号。数据有正、负两种,正好可用"0"、"1"、两种状态来表示,以"0"表示正数,以"1"表示负数。一般把符号位放在最高位,其余位表示数据。在计算机中,以这种格式表示的二进制数称为原码,n位的原码表示有符号整数的范围是: -2"-1~2"-1~1。

定义1(二进制原码):整数X用n位二进制原码表示,其规则如下:

- 1. 若  $X \ge 0$ , 它的最高位为 0, 其余位是 X 的二进制数;

- 2. 若 X < 0, 它的最高位为 1, 其余位是 |X| 的二进制数。

例 1.3 用二进制数表示无符号、有符号整数。

无符号整数:[0101 1101]<sub>B</sub>=93

$[1101 \ 1101]_{B} = 221$

有符号整数:[0101 1101],=93

$[1101 \ 1101]_{\mathbf{m}} = -93$

在计算机中,无符号整数的运算比较容易,因为一般情况下计算机中的加法器与乘法器都是按无符号整数设计的,这样一来只需注意数据的范围,不要发生溢出错误便可。对于有符号整数的运算就要麻烦一些,由于最高位是符号标志,如果直接参与运算,会带来不正确的结果。因此,对于有符号整数的运算分两步进行:先按规则运算符号位并寄存;然后屏蔽掉符号位,按无符号数进行运算,再把结果与寄存的符号位拼接成最后的结果。

可以看出,在计算机中直接进行有符号整数的运算是不方便的,有没有可能经过一定变换,使得有符号整数的运算能够一步完成?下面介绍的二进制补码就可以做到这一点。

### 1.2.2 补码与加、乘运算

1. 补码与整数加法 在计算机中加、乘运算是最基本的运算,对于有符号整数以及小数的加、乘运算能否有一套统一的编码系统来完成是一件非常有意义的事。下面首先从有符号整数的加法谈起,引人补码并同时介绍其特点,然后分别介绍补码形式的整数与小数的乘法运算。

前面说到,计算机的数据长度是有限的。对于8位计算机,超过2°就会溢出,这跟数学

中的同余(mod)运算是一样的,即

$$X = [X + 2^{8}] \mod 2^{8}$$

为了讨论方便、设X和Y是正整数、N是大于X和Y的正整数、那么

$$X + (-Y) = [N + X + (-Y)] \mod N$$

$$= [X + (N - Y)] \mod N$$

从上式可以看出,如果用 N-Y (这是大于 0 的数)代表 (-Y),则有符号的加法运算转换成了无符号的加法运算。下面给出二进制补码表示的定义:

定义 2 (二进制补码), 整数 X 用n 位二进制补码表示, 其规则如下:

- 1) 若 X≥0,它的原码就是它的补码;

- 2) 若 X < 0, 它的补码为  $2^n |X|$ 。

原码和补码都可以表示有符号数,它们之间的区别在于:对于原码表示,其最高位仅仅是一个符号标志,不能直接参与数据的加法运算,否则会引起错误的结果;对于补码表示,则不一样,其最高位既是符号标志,也是一位可以参与运算的数据。按二进制补码表示的数据,无论正数还是负数可以直接进行加法运算,但其结果按二进制补码解释。

例 1.4 设 n=8, X=66, Y=-24, 写出它们的原码和补码, 并求 X+Y=?

1)按原码方式直接相加,其结果是错误的。

$$[X]_{\mathbb{R}} = [0100 \ 0010]_{\mathbb{R}} \quad [Y]_{\mathbb{R}} = [1001 \ 1000]$$

$$[X]_{\mathbb{R}} + [Y]_{\mathbb{R}} = [0100 \ 0010]_{\mathbb{R}} + [1001 \ 1000]_{\mathbb{R}}$$

$$= [1101 \ 1010]_{\mathbb{R}} = -90$$

2) 按补码方式直接相加,其结果是正确的。

$$[X]_{**} = [0100\ 0010]_{**} \quad [Y]_{**} = 2^{8} - 24 = 232 = [1110\ 1000]_{**}$$

$$[X]_{**} + [Y]_{**} = [0100\ 0010]_{**} + [1110\ 1000]_{**}$$

$$= [1\ 0000\ 0000] + [0010\ 1010]_{**} \quad \text{mod} \quad 2^{8}$$

$$= [0010\ 1010]_{**} = 42$$

上面的讨论说明了采用二进制补码有益于有符号的加法运算,但是按定义 2 求负数的补码需要做一次减法,这与采用补码的初衷是相悖的,有无其它简易的方法求解补码呢?仔细的推敲可得到与定义 2 等价的另一种定义:

定义 3 (二进制补码):整数 X 用 n 位二进制补码表示,其规则如下:

- 1) 若  $X \ge 0$ , 它的原码就是它的补码;

- 2) 若 X < 0, 它的补码为: 其原码的符号位不变, 数据位求反加 1。

按照定义3可以很容易得到有符号整数的补码,从而避免了定义2求补码要做减法的困难。

2. 补码运算的溢出 要注意二进制补码表示也有一个数据范围的问题,n位二进制补码可以表示-2<sup>n-1</sup>~2<sup>n-1</sup>~1范围内的数。在做二进制补码加法的时候,要特别注意溢出的问题。下面先看一个例题。

例 1.5 按二进制补码求 X+Y=? 并注意符号位与数据的最高位的进位情况。

$$[X]_{*} = [0110 \ 1110]_{*} \quad [Y]_{*} = [0101 \ 1110]_{*}$$

从前两个算式看,最后的结果是不正确的,因为两个正数相加不可能为负数,两个负数相加也不可能为正数。引起这个结果的原因是相加的结果超出了8位二进制补码表示的范围,发生了溢出。所以二进制补码的溢出,不能只看最高位是否有进位,而需要看最高两位(符号位与数据最高位)的进位情况。如果最高两位都有进位或都无进位,则不发生溢出,否则将产生溢出。不少计算机的状态标志寄存器专门有一个溢出位 OV,就是为补码运算所设。

3. 数据扩展与符号扩展 在计算机的计算中,为了提高计算精度,常常需要用多字节来表示一个数,这就存在数据扩展的问题。对于无符号整数,这种扩展比较容易,在前面补 0 即可。对于有符号整数仅仅补 0 是不够的。下面以一个实例说明补码形式的数据扩展并总结出它的规律。

例 1.6 设

$$n=8$$

,  $X=66$ ,  $Y=-24$ , 写出它们的补码:

$$[X]_{\#} = [0100\ 0010]_{\#} \quad [Y]_{\#} = [1110\ 1000]_{\#}$$

设  $n=16$ ,  $X=66$ ,  $Y=-24$ , 写出它们的补码:

$$[X]_{\#} = [0000\ 0000\ 0100\ 0010]_{\#}$$

$$[Y]_{\#} = [1111\ 1111\ 1110\ 1000]_{\#}$$

仔细分析例 1.6 可以看出,采用二进制补码表示的数据扩展,实际上就是符号扩展,即正整数前面全部补 0,负整数前面全部补 1。正因为如此,在有的计算机中专门提供了符号扩展方式,就是为了方便实现二进制补码形式的数据扩展。

4. 整数补码的乘法 下面探讨二进制补码的乘法。设 $X \times Y \neq n$  位有符号的整数,其范

围为 $-2^{n-1}$ 到  $2^{n-1}-1$ , $N=2^n$ 。二进制补码的乘法有下面三种情况:

- X≥0,Y≥0。这与无符号乘法一样。

- X=0,Y<0。这是一种平凡的情况,按补码相乘的结果肯定是0。

- X>0, Y<0。用补码实现乘法的过程为:</li>

$$\{X \times (N-|Y|)\} \mod N = \{NX-N|Y|\} \mod N$$

$$= \{N(X-1) + (N-X|Y|)\} \mod N$$

$$= N-X|Y|$$

注意到整数 X>0,则  $X-1\ge0$ 。因此,上面的运算表明按照补码相乘其结果也是相应的补码。

X<0, Y<0。用补码实现乘法的过程为:</li>

$$\{(N-|X|)\times (N-|Y|)\} \mod N = \{N^2-N(|X|+|Y|)+|X||Y|\} \mod N$$

$$= \{N\{N-(|X|+|Y|)\}+XY\} \mod N$$

$$= XY$$

由于 $|X| \le 2^{n-1}$ , $|Y| \le 2^{n-1}$ ,所以  $N-(|X|+|Y|) \ge 0$ 。因此,对于二个负的整数按照补码相乘其结果也是相应的补码(正整数的补码是其本身)。

综上所述,按照二进制补码进行的有符号整数的乘法毋须关注它的符号,其结果按补码进行解释。在进行二进制乘法运算时有一点需要注意,二个n 位二进制整数相乘可以得到 2n 位二进制整数的乘积结果。为了得到正确的 2n 位二进制整数的乘积结果,需首先将n 位二进制补码的乘数和被乘数扩展到 2n 位,然后再按二进制补码的方式相乘,根据上面的讨论,其结果肯定是正确的。总的一句话,要得到 N 位二进制补码的乘积,其乘数与被乘数应为 N 位二进制补码。

例 1.7 设  $X=21=[0001\ 0101]_{\text{++}}, Y=-3=[1111\ 1101]_{\text{++}}, 求 XY=?$  若只需 8 位二进制乘积结果,则

所以  $XY = [1100\ 0001]_{*} = -63$

若需要 16 位二进制乘积结果,则先要将 X、Y 进行扩展,即

$X=21=\lceil 0000\ 0000\ 0001\ 0101 \rceil_{*}, Y=-3=\lceil 1111\ 1111\ 1111\ 1111\ 1101 \rceil_{*}$

所以 XY=[11111111 1100 0001]<sub>n</sub>=-63

5. 小数的补码与加、乘运算 前面较详细讨论了采用二进制补码的有符号整数的加、乘运算,那么对于有符号的小数,能否移植前面的结论?下面给出详细的讨论。

首先、有符号小数原码的表示可以从整数原码进行自然推广。即最高位为符号位为"0"表示正数,为"1"表示负数;其余位为数据位。不失一般性,设 n 位二进制小数由 m 位整数位(包括符号位)和 k 位小数位组成(n=m+k)。这种表示方式也成为  $Q_k$  方式。若 k=0,则退化为完全整数( $Q_0$ );若 m=1,则为完全小数,或称标准小数(若 n=16,为  $Q_{16}$ )。

例 1.8 用 8 位二进制原码表示下面的十进制数 (m=4, k=4):

5.

$$625 = [0101.1010]_{\overline{M}}$$

-3.  $25 = [1011.0100]_{\overline{M}}$

有符号小数补码的定义可以从整数二进制补码的定义进行推广。对于定义 3 可以完全照搬,即对于正数,其原码就是它的补码;对于负数,将其原码的符号位不变,其余位求反加 1。而对于定义 2 有如下自然的推广。

定义 4 (一般性的二进制补码): 设 x 是由 m 位整数位 (包括符号位) 和 k 位小数位组成的 n 位二进制数,n=m+k。它的补码表示如下:

- 1) 若  $x \ge 0$ ,它的原码就是它的补码;

- 2) 若 x < 0, 它的补码为  $2^{m} |x|$ .

例 1.9 用 8 位二进制补码表示下面的十进制数 (m=4, k=4)。

采用定义 3 求: 5.625=[0101.1010]\* -3.25=[1100.1100]\*

采用定义  $4 \bar{x}: -3.25 = 2^4 - [0011.0100]_B = [10000.0000]_B - [0011.0100]_B$

$$=[1100.1100]_{\#}$$

定义3和定义4都是二进制补码的一般性定义,它们是完全等效的,有兴趣的读者可自行证明。根据定义3或定义4给出的带小数二进制补码,其加法、乘法运算与整数补码的加法、乘法运算是否同样简单呢?答案是肯定的。

对于带小数的加法,首先要注意小数点位置要对齐,即需要相加的两个小数的格式要一致 (m 与 k 的值要一样),不然的话要通过移位操作使它们一致。另外,在计算机中并没有小数点的硬件设置,小数点的位置是一种"假想",也就是说计算机中的加法器(也包括乘法器)都是按无符号整数来运算的。基于这两点,下面简单推导有符号小数二进制补码加法实现的原理。

设 x、y 是由 m 位整数位(包括符号位)和 k 位小数位组成的 n (n=m+k) 位二进制数,取  $X=x2^k$ , $Y=y2^k$ ,即 X、Y 变为完全整数,也就是将小数点右移 k 位。按照前面讨论的结果知,完全整数可以采用补码形式直接相加;然后,将相加结果的小数点左移 k 位便是 x 与 y 相加的结果。不失一般性,设 x>0,y<0,则

$$[x+y]_{+} = [X+(2^{n}-|Y|)] \times 2^{-k} = [x2^{k}+(2^{m+k}-|y|)2^{k}] \times 2^{-k}$$

$$= [x+(2^{m}-|y|)]$$

这个推导说明,只要 x、y 的补码按照定义 3 或定义 4 给出,其加法可以直接相加。注意对于由 m 位整数位(包括符号位)和 k 位小数位组成的 n (n=m+k) 位二进制数所表示的范围是一 $2^{m-1}$  到  $2^{m-1}$  —  $2^{-k}$ ,超出此范围将发生溢出。

有符号小数的乘法实现原理与有符号小数的加法是类似的。思路都是先把它看成是完全整数(相当于将小数点右移 k 位), 然后按完全整数进行相乘, 最后再确定小数点的位置。如

果相乘的两个数据的小数位都是 k 位,则最后的结果要将小数点左移 2k 位;如果相乘两个数据的小数位分别是  $k_1$  位和  $k_2$  位(这一点与加法不同,两个数据可以有不同的数据格式),则最后的结果要将小数点左移  $k_1+k_2$  位。

不失一般性,设x>0由  $m_1$  位整数位(包括符号位)和  $k_1$  位小数位组成,y<0 由  $m_2$  位整数位(包括符号位)和  $k_2$  位小数位组成, $n=m_1+k_1=m_2+k_2$ 。取  $X=x2^{k_1}$ , $Y=y2^{k_2}$ ,那么

$$[x \times y]_{\mathbb{H}} = 2^{-(\lambda_1 + \lambda_2)} [X \times Y]_{\mathbb{H}} = [X \times (2^n - |Y|)] 2^{-(\lambda_1 + \lambda_2)}$$

$$= [x 2^{\lambda_1} \times (2^n - |y|) 2^{\lambda_2}] \times 2^{-(\lambda_1 + \lambda_2)}$$

$$= x \times (2^{m_2} - |y|)$$

例 1. 10 设  $x=5.25=[000101.01]_{\#}, y=-0.75=[111111.01]_{\#}, 求 xy=?$ 若只需 8 位二进制乘积结果,则

所以  $xy = [1100.0001]_{+} = -3.9375$

若需要 16 位二进制乘积结果,则先要将 x、y 进行扩展,即

$x=5.25=[0000\ 0000\ 0001\ 01.01]_{4}, y=-0.75=[11111111\ 1111\ 1111\ 111.01]_{4}$

所以  $xy = [1111111111111100 00.01]_{4} = -3.9375$

上面讨论了二进制补码的整数、小数与有符号数的加乘运算原理,可以看出采用二进制补码带来了许多便利。因此,在实际应用时应尽可能转换成二进制补码的形式存储数据。在 DSP 控制器中有一个 16 位×16 位的乘法器,其结果是 32 位。由于该乘法器自动实现乘数与被乘数的数据扩展(16 位到 32 位),因此不需要用户编程干预。

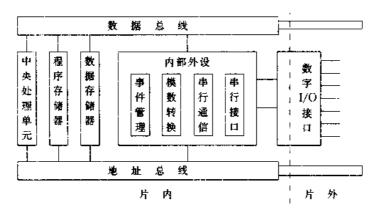

# 1.3 DSP 控制器的基本原理

无论是微处理器、单片机还是 DSP 控制器,它们的工作原理是基本一致的。不外乎要做的工作都是:从存储器、I/O 接口等地方取数,按某种规律运算,再把结果放到存储器、I/O 接口等地方。因此,在其工作过程中数据流与地址流占统治地位。为了实现数据流、地址流有序地管理和控制,采用数据总线和地址总线是一种最佳的结构方式。数据总线和地址总线就像两条高速公路,数据信息与地址信息分别在其上快速地流动。中央处理单元(CPU)、程序存储器、数据存储器和内部外设等功能模块分别挂接在数据总线和地址总线上。中央处理

单元是控制中心,由它指挥当前时刻谁可以占用数据总线或地址总线,同时它还可以进行有关的运算,程序存储器是物理芯片与人的交接面,由人编写程序指令并写入到程序存储器中,体现了人的意志,中央处理单元只能根据程序的流程进行指挥不能随意发挥;数据存储器用于记录工作过程中的原始数据、中间结果和最后结论;内部外设是集成在芯片内部的与外部世界进行信息交换的功能模块,一般包含 I/O、A/D、串行通信等。另外,数据总线和地址总线一般情况下都延伸到芯片外部(到引脚上)。图 1.1 说明了上述情况。

图 1.1 DSP 控制器的基本原理

一般的微处理器的数据总线和地址总线是单总线方式,相当于一辆车在只有一条道的高速公路上跑,这辆车分时地为大家服务。DSP 控制器与此不同,采用多总线方式,相当于是多条道的高速公路,这样一来多辆车可以同时在其上行驶,极大地加快了运行速度。这实质上是一种并行机制。

数据和地址是贯穿任何一种微处理器设计、编程的两个基本概念,特别是地址,它就是数据源、专用寄存器、I/O的代表。每一个存储器、寄存器都有地址,这个容易为大家接受。对于可编程的功能模块(片内的或片外的)它也有地址,有时让人费神。准确地说,对可编程的功能模块的操作,实际上是对它的寄存器(控制的、数据的等)进行操作,这些寄存器必须有唯一地址,否则会引起工作混乱。对于片内外设的功能模块各寄存器的地址是由芯片厂家确定的,应仔细查看手册,不可更改。片外设功能模块各寄存器的地址与所连接的外部地址总线有关,这是设计者一个重要的设计任务,即给每个功能模块分配地址,一旦完成设计做好印制电路也就被固定了下来。

当设计者明确了存储器地址空间、I/O 地址空间、片内或片外设功能模块各寄存器的地址后,程序设计的工作就有了一个明晰的轮廓,剩下的任务就是如何组织数据,采用什么控制律或算法,以何种流程来实现。

DSP 控制器在工作时要注意如下问题:

- ●加电后,中央处理单元自动从复位地址(0000H)取出首条指令。

- ●指令处理周期分为:取指令、指令译码、取操作数、执行指令四个阶段。

- ●---条指令执行完后,顺序处理下一条指令,除非遇到分支指令或中断响应。

- ●数据的地址由指令的寻址方式和相应的操作数确定,这一点非常重要。

- ●对外部世界的访问有两种方式:通过 I/O 端口或者特定的映射寄存器,前者使用 I/O 传送指令,后者使用存储器传送指令。

# 第2章 总体结构

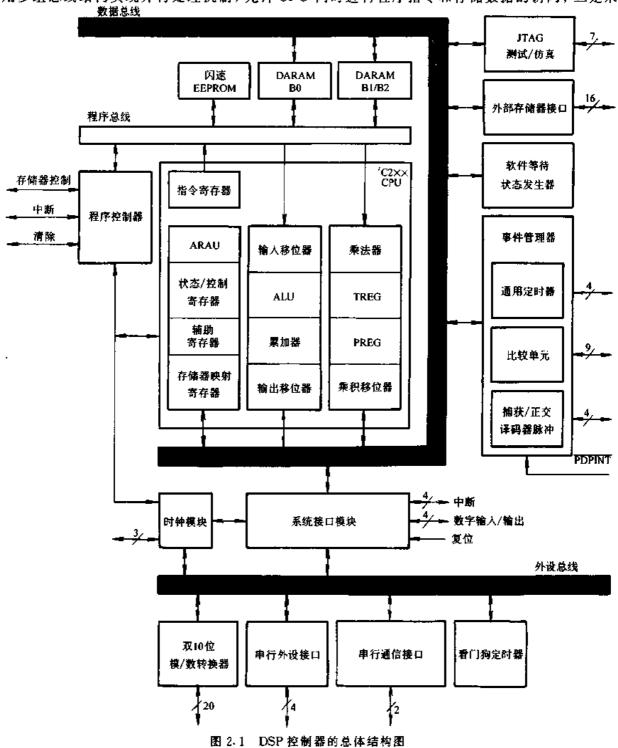

DSP 控制器是一款高性能的单片机。DSP 控制器的总体结构有许多独特的地方:一是采用多组总线结构实现并行处理机制,允许 CPU 同时进行程序指令和存储数据的访问;二是采

用独立的累加器和乘法器,使得复杂的乘法运算能快速进行;三是累加器和乘法器分别连接了比例移位器,使得许多复杂运算或者运算后的定标能在一条指令中完成;四是有丰富的寻址方式,可方便灵活的编程;五是有完善的片内外设,可以构成完整的单片系统。本章主要介绍 DSP 控制器的总体结构,包括总线结构、中央处理单元、存储器与 I/O 空间以及系统的复位。图 2.1 是 DSP 控制器的总体结构图。

### 2.1 总线结构

目前,在控制领域使用的各种微处理器芯片(各类 CPU、单片机等)的基本任务,就是从某个地方(内、外部存储器或外部接口)取得数据,经过算术或逻辑运算,然后放到相应的地方上。为了区别不同的数据源,需要给其赋予一个独立的地址。数据和地址是任何微处理器都要面对的两个基本要素。因此,在微处理器芯片中采用基于数据/地址总线的结构是最佳的选择。在总线上可以挂接中央算术逻辑单元(CALU)、存储器、定时器等功能模块。通过地址总线和某些控制信号线(与指令密切相关),使得在某一时刻仅仅让某个数据源占用数据总线。这样一来,在地址总线和控制总线的共同作用下,使得数据总线的数据得以有序的流动。

总线结构是计算机体系结构中最基本的结构,它提供了一种标准的接口方式。功能模块之间的信息交换,都可解释为"在什么地址存放数据"或"从什么地址取回数据"。数据与地址成为密不可分的一对伙伴。具备数据与地址接口方式的功能模块都可以挂接到数据/地址总线上。数据/地址总线是双向的,为了保证数据通畅流动,要在中央处理单元统一指挥下按节拍进行工作。

总线结构是各种微处理器芯片的总干道,它的性能(响应速度、位宽、负载能力等)在很大程度上决定了微处理器芯片的性能。为了提高处理速度,一方面可以通过新的工艺使得微处理器芯片能够采用更高频率的晶振以加快响应的速度;另一方面可以加宽数据总线(32位或 64位)以增加高精度复杂运算的指令。除此之外,加快处理速度的最佳方案是采用并行机制。一般情况下,总线的操作时序分为四个独立的阶段:取指令、指令译码、取操作数和执行指令,这四个阶段分别面向程序读、数据读和数据写。如果将数据/地址总线分开为三组数据/地址总线,分别对应程序读、数据读和数据写三种情况,这样一来就可以使总线操作时序的四个独立阶段并行处理,从而极大地加快微处理器芯片的处理速度。可以形象地理解,单总线方式就像是一辆车在只有一条道的高速公路上跑;而多组总线方式就像是多辆车在多条道的高速公路上跑。后者的运行速度和效率肯定要超过前者。

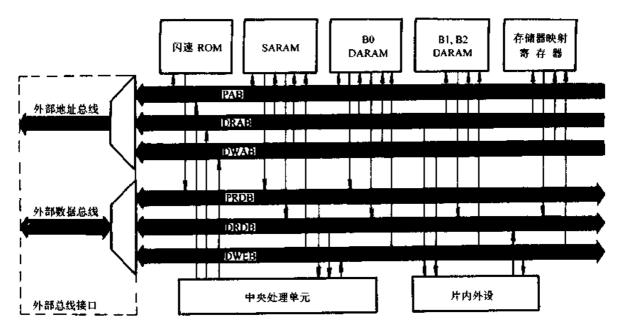

DSP 控制器就是采用了多组总线的结构,图 2.2 是 DSP 控制器的总线结构图。其中内部地址总线分为了三条总线:

- ●程序读地址总线 (PAB),提供读程序的地址;

- ●数据读地址总线 (DRAB),提供读数据存储器的地址;

- ●数据写地址总线 (DWAB), 提供写数据存储器的地址。

内部数据总线也对应分为三条总线:

- ●程序读数据总线 (PRDB),将指令代码中的立即数以及表信息传送到 CPU;

- ●数据读数据总线 (DRDB), 将数据存储器的数据传送到 CPU;

- ●数据写数据总线 (DWDB), 将处理后的数据传送到数据存储器和程序存储器。

图 2.2 DSP 控制器的总线结构图

外部数据/地址总线仍为单一形式,这使得众多的外围芯片可与其兼容。

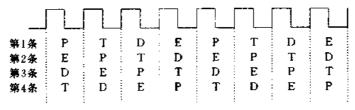

每条指令的执行过程可以分为四个阶段:取指令(P)、指令译码(T)、取操作数(D)和执行指令(E)。由于 DSP 控制器采用了多组总线的结构,这将允许 CPU 同时进行程序指令和存储数据的访问,因而在其内部可以实现四级逻辑流水线,如图 2.3 所示。在某一时刻,第一条流水线上在做取指令操作时,第二条流水线可同时进行上一条指令的指令译码的操作,第三条流水线可同时进行再上一条指令的取操作数的操作,第四条流水线可同时进行再上一条指令的执行指令的操作。由于这四种操作在同一时刻是分别使用内部的六条总线,因此不会发生冲突,就像多辆车在多条道的高速公路上行驶一样,从而实现了一种并行处理的机制。

图 2.3 四级逻辑流水线

这种并行机制可使得 4 条指令同时在一个周期内处于激活状态,而在任一周期都有执行指令 (E) 的操作,就好像一个周期就可以完成一条指令。

四级流水线是逻辑上的,大部分情况下对用户来说也是不可见的。在下面两种情况下,四级流水线将会暂停:

- ●紧跟在修改全局存储器分配寄存器(GREG)后的单字单周期指令使用先前的全局映射。

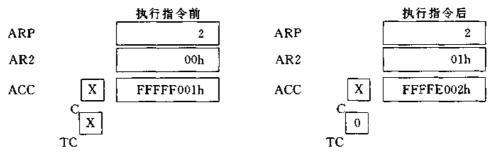

- NORM 指令修改辅助寄存器指针 (ARP) 而且在流水线执行阶段要使用修改后 ARP 指出的那个寄存器,如果后面两个指令字在执行 NORM 前会改变 ARP 的值或者是辅助寄存器的值,这就会使 NORM 使用错误的辅助寄存器值,并使后续指令使用错误的 ARP 值。

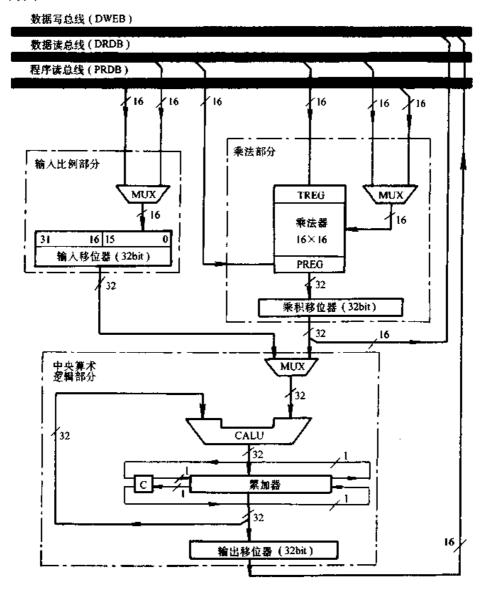

# 2.2 中央处理单元

中央处理单元(CPU)是挂接在总线上的核心模块,它的任务是从程序读数据总线或数据读数据总线上获取数据,经过加、乘、移位等算术逻辑运算,再经数据写数据总线将结果送出,如图 2.4 所示。中央处理单元分为三个部分:

- ●輸入比例部分。

- ●中央算术逻辑部分。

- ●乘法部分。

图 2.4 中央处理单元

输入比例部分是将程序读数据总线或数据读数据总线上的 16 位数据与 32 位的中央算术逻辑单元 (CALU) 的数据对齐;中央算术逻辑部分完成加、减、移位等算术逻辑运算;乘法部分实现 16×16 的乘法运算。下面分别加以介绍。

### 2.2.1 输入比例部分

由于程序读数据总线或数据读数据总线是 16 位, 而中央算术逻辑单元是 32 位。为了使程序读数据总线或数据读数据总线上的数据能正确地参与到中央算术逻辑单元中运算, 需要对程序读数据总线或数据读数据总线上的数据进行移位以及扩展,以便与 32 位中央算术逻辑单元中的数据对齐。输入移位器进行的操作不需要 CPU 时钟开销。

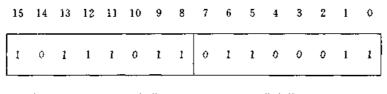

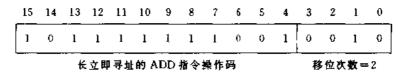

16 位的程序读数据总线或数据读数据总线上的数据信号通过多路转换器接至 32 位的输入移位器的输入端,程序读数据总线上的数据是指令操作数给出的常数值(立即寻址),数据读数据总线上的数据是指令操作所需引用的数据存储单元中的数值(直接寻址、间接寻址),如图 2.4 所示。

输入移位器可将输入值左移 0~16 位,移位次数可由两种来源获得:

- ●指令字中的常数。把移位次数放在指令字中,允许用户为程序代码使用特定的数据比例 (左移1次相当于乘2)。

- ●临时寄存器 (TREG) 的低 4 位。根据 TREG 的值移位,允许动态调整数据的比例系数,从而适应不同的系统性能。

另外,输入移位器也可以进行符号扩展。在微处理器中常常需要进行有符号数的运算,有符号数常以二进制补码来表示。因此,对于 16 位的有符号数送人到 32 位中央算术逻辑单元时,需要进行符号扩展(参见 1.2.2)。DSP 控制器中状态寄存器 ST1 的第 10 位是符号扩展模式位(SXM)。若 SXM=0,则不进行符号扩展;若 SXM=1,则进行符号扩展。

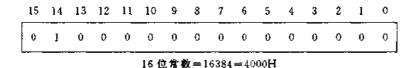

- ●当 SXM=0 时,输入移位器对输入值左移后,其低端中未使用的 LSB 填 0,高端未使用的 MSB 填 0。

- ●当 SXM=1 时,移位时需要进行符号扩展。若输入值为正数,高端未使用的 MSB 填 0,低端中未使用的 LSB 填 0;若输入值为负数,高端未使用的 MSB 填 1,而低端中未使用的 LSB 仍填 0。

### 2.2.2 中央算术逻辑部分

中央算术逻辑部分含有:

- 32 位的中央算术逻辑单元 (CALU);

- 32 位的累加器 (ACC);

- 32 位输出移位器。

中央算术逻辑单元有两个输入:一个输入总是来自累加器(所有的加减法指令都隐含累加器作为一个操作数);另一个输入来自输入移位器的输出或者乘积移位器的输出。中央算术逻辑单元可实现加减算术运算、与或等逻辑运算和位测试等功能;累加器接收中央算术逻辑单元的输出,可与进位位(C)一起进行移位操作,ACCH和ACCL分别是累加器的高位字和低位字。

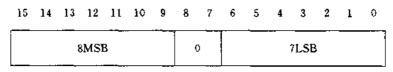

输出移位器把累加器的内容拷贝过来,并可对其高位字或低位字进行移位操作,然后送到 16 位的数据写数据总线上,进入到数据存储器中。输出移位器可以左移 0~7 位,移位时高位丢失,低位补 0。然后经指令 SACH 或 SACL 将移位器中的高位字或低位字保存到数据存储器,累加器的内容保持不变。

### 2.2.3 乘法部分

DSP 控制器含有一个  $16 \times 16 \times 16$  位的硬件乘法器,可在一个周期内完成有符号或无符号数乘法,乘积为 32 位。如图 2.4 所示,乘法部分包括:

- 16 位的临时寄存器 (TREG), 它含有一个乘数;

- ●乘法器,它把临时寄存器的值与来自数据存储器或程序存储器的被乘数相乘;

- 32 位的乘积寄存器 (PREG), 它接收相乘运算的结果;

- ●乘积移位器,使乘积寄存器的值在送到中央算术逻辑单元或数据存储器前进行移位定标。

乘法器接收两个 16 位的输入:一个输入(乘数)总是来自临时寄存器 TREG,在乘法之前把数据读数据总线的值加载到临时寄存器;另一输入(被乘数)来自数据存储器或程序存储器。

乘积移位器可进行四种形式的移位,由状态寄存器 ST1 中的乘积移位模式位 (PM)确定,如表 2.1 所示。乘积移位器可把乘积结果送到中央算术逻辑单元或者经指令 SPH (SPL) 将乘积移位器的高位字 (低位字) 送到数据存储器。

| PM | 移位         | 说明                                                    |

|----|------------|-------------------------------------------------------|

| 00 | 不移         | 乘积送到 CLAU 或数据写数据总线,不移位                                |

| 01 | 左移1位       | 移去二进制补码乘法产生的额外符号位、产生 $Q_{31}$ 格式的乘积                   |

| 10 | 左移 4 位     | 移去 16 位×13 位(常数)二进制补码乘法产生的额外 4 位符号位,产生 Q31格式的乘积       |

|    | + ** * * * | 把乘积定标,使最多作 128 次乘法累加而不使累加器溢出。不论 STt 中 SXM 为何值, 右移总是要进 |

| 11 | 右移 6 位<br> | 行符号扩展                                                 |

表 2.1 乘积移位器中乘积移位模式

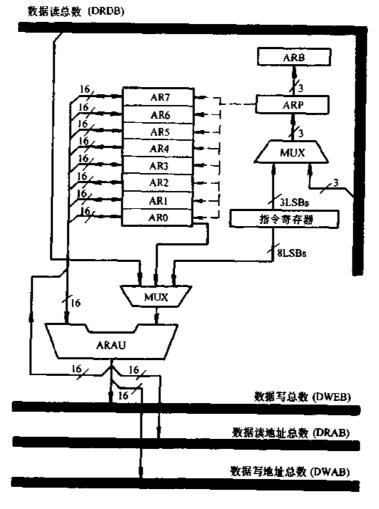

# 2.3 辅助寄存器算术单元

中央处理单元 (CPU) 还有一个与中央算术逻辑单元 (CALU) 无关的辅助寄存器算术单元 (ARAU)。它的主要功能是与中央算术逻辑单元中进行的操作并行地实现对 8 个辅助寄存器 (AR0~AR7) 的算术运算,如图 2.5 所示。

DSP 控制器的指令系统提供了丰富、灵活、有效的间接寻址方式的指令。这些间接寻址方式由 8 个辅助寄存器 (AR0~AR7) 来实现。当前时刻由哪个辅助寄存器进行间接寻址取决于状态寄存器 ST0 中的辅助寄存器指针 (ARP),利用 MAR、LST 指令可以修改辅助寄存器指针的值。辅助寄存器指针所指出的寄存器称为当前辅助寄存器或当前 AR。在处理一条间接寻址的指令时,当前辅助寄存器的内容用作访问数据存储器的地址。如果指令需要从数据存储器读出,辅助寄存器算术单元(ARAU)就把这个地址送到数据读地址总线(DRAB)。如果指令要向数据存储器写入,则将地址送到数据写地址总线(DWAB)。

辅助寄存器算术单元(ARAU)完成以下运算:

- ●将辅助寄存器的内容增、减 1,或者增、减一个变址量(取决于间接寻址的指令)。

- ●使輔助寄存器的内容增、减一常数(ADRK、SBRK 指令), 该常数值是指令字的低 8 位。

- ●把 ARO 的内容与当前 AR 的内容进行比较 (CMPR 指令),并把结果经数据写数据总线 (DWDB) 放入到状态寄存器 ST1 的测试/控制位 (TC)。

注:Q31格式是 32 位有符号小数的标准格式,即最高位是符号位,小数点紧接其后。可参见 1.2.2。

图 2.5 辅助寄存器算术单元

通常,辅助寄存器算术单元在流水线的译码阶段进行它的算术运算。这就能在下条指令译码之前产生地址。有一个例外情况,就是在处理 NORM 指令时,在流水线的执行阶段修改辅助寄存器或辅助寄存器指针。

除进行间接寻址外,辅助寄存器还有其它用途。例如,

- ●通过 CMPR 指令,使辅助寄存器支持条件分支、调用和返回。

- ●用辅助寄存器作暂存单元,利用 LAR 指令将数值加载到该寄存器,再用 SAR 指令把AR 值保存到数据存储器。

- ●利用辅助寄存器做软件计数器,按需要对其加、减。

# 2.4 状态寄存器 ST0 和 ST1

DSP 控制器有两个状态寄存器——ST0 和 ST1,它们含有状态和控制位。状态寄存器 ST0 和 ST1 的内容可以保存到数据存储器 (SST 指令)也可以从数据存储器中加载 (LST 指令)。因此,可以保存和恢复子程序的机器状态。

状态寄存器 ST0 和 ST1 中有很多位可用 SETC 和 CLRC 指令单独置 1 和清 0。例如,利用 SETC SXM 指令将符号扩展模式位置 1,而 CLRC SXM 指令则将其消 0。表 2.2 示出了状态寄存器 ST0 和 ST1 各位的定义。其中有些位是保留的,读出时为逻辑 1。表 2.3 是各位的

### 详细说明。

表 2.2 状态寄存器 STO 和 ST1

| 寄存器 | 位 数  |      |      |      |      |      |             |      |

|-----|------|------|------|------|------|------|-------------|------|

|     | 15   | 14   | 13   | 12   | 11   | 10   | 9           | 8-0  |

| ST0 | ARP  |      |      | ov   | оум  |      | INTM        | DP   |

|     |      | RW-x |      | RW-0 | RW-x | 1    | RW-1        | RW-x |

|     | 15   | 14   | 13   | 12   | 11   | 10   | 9           | 8    |

|     |      | ARB  |      | CNF  | TC   | SXM  | c ·         |      |

| CT. | RW-x |      |      | RW-0 | ŔW-x | RW-1 | RW-1        | 1    |

| ST1 | 7    | 6    | 5    | 4    | 3    | 2    | 1           | 0    |

|     |      |      | XF   | _    |      | PM   |             |      |

|     | 1 1  | RW-  | RW-1 | 1    | 1    | RV   | <b>V</b> -0 |      |

注:R——可读;W----可写;x——复位时为任意值;0——复位时为 0;1——复位时为 1。(以下同)

表 2.3 状态寄存器 STO 和 ST1 各位的定义与说明

| 名称   | 说 明                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARP  | 辅助寄存器指针。该指针用于选择间接寻址中使用的辅助寄存器 AR。可用 LST、MAR 指令修改它的值                                                                                                                                        |

| ARB  | 输助寄存器指针缓存器。除 LST 指令外,每当加载 ARP 时,ARP 原来的值就拷贝到 ARB 中。当用 LST 加载ARB 时,同样的值也拷贝到 ARP 中                                                                                                          |

| c    | 进位位。如果相加结果产生进位,该位置1,否则清0;如果减法结果产生借位,该位清0,否则置1。但是移位16位的 ADD 和 SUB 指令除外,这时 ADD 指令只在进位时使 C 置 1,SUB 只在借位时使 C 清 0,否则不影响 C。复位时 C 为 1                                                            |

| CNF  | 片内 DARAM 配置位。该位决定可重新配置的双口 RAM 块映射到数据空间还是程序空间。CNF 为 0 则配置到数据空间,CNF 为 1 配置到程序空间。SETC CNF、CLRC CNF、LSF 指令可以修改 CNF。复位时 CNF 为 0                                                                |

| DP   | 数据页面指针                                                                                                                                                                                    |

| INTM | 中断总屏蔽位。INTM 为 0 允许没有屏蔽的中断使能,INTM 为 1 则禁止所有可屏蔽中断。LST 指令不影响INTM。该位对非屏蔽中断 RS、NMI 和软件中断不起作用                                                                                                   |

| ov   | 溢出标志,进行补码运算时,数据超出范围将发生溢出,该位置1。复位或LST、(无)溢出条件分支指令将使该位清 0                                                                                                                                   |

| OVM  | 溢出模式位。OVM 为 0,不对溢出结果进行调整;OVM 为 1,对溢出结果进行调整,正溢出时累加器的结果调整 为 7FFF FFFFH,负溢出时累加器的结果调整为 8000 0000H                                                                                             |

| PM   | <ul> <li>乘积移位模式。PM 决定乘积结果在送出前怎样进行移位</li> <li>PM=00 不移位</li> <li>PM=01 左移 1位,低位填 0</li> <li>PM=10 左移 4位,低位填 0</li> <li>PM=11 右移 6位,进行符号扩展</li> <li>复位时 PM 清 0。SPM、LST 指令可以修改 PM</li> </ul> |

| SXM  | 符号扩展模式位。SXM 为 ① 不进行符号扩展;SXM 为 1 进行符号扩展                                                                                                                                                    |

| тс   | 测试/控制标志位。如果 BIT 或 BITT 测试结果为 1、CMPB 测试当前 AR 和 AR0 的比较条件成立、NOMR 测试<br>累加器最高 2 位异或结果为 1,将使 TC 置 1                                                                                           |

| XF   | XF 引脚状态位。复位时该位为 1。SET XF、CLR XF、LST 指令都可以修改 XF                                                                                                                                            |

|      |                                                                                                                                                                                           |

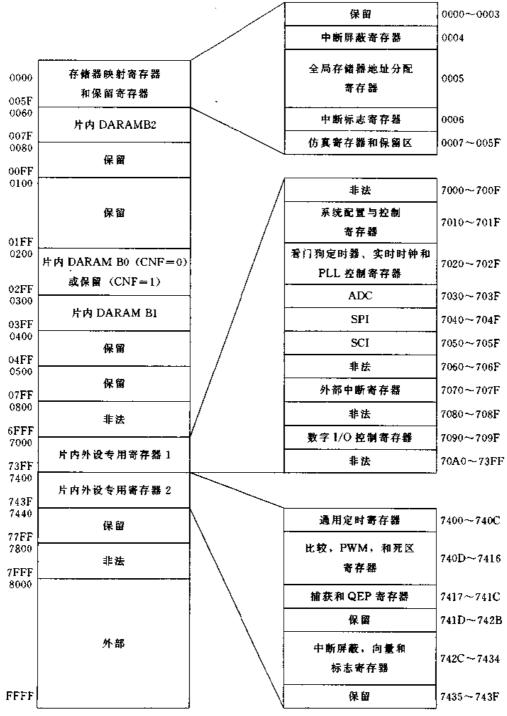

### 2.5 存储器与 I/O 空间

存储器结构有两大类:冯诺曼结构 (Von Neumann) 和哈佛结构 (Harvard)。前者将程序与数据合用一个存储空间,通过地址分段来存放程序与数据,像 Intel 8086 系列。后者将程序存储空间与数据存储空间分离开来,二者是不同的物理存储器,可以拥有相同的地址,通过不同的控制线 (读、写、片选等信号)来对它们进行访问,像 Intel 8051 系列。一般情况下,控制系统需要的程序存储容量较大而数据存储容量较小。这样一来,采用哈佛结构就可以单独将小容量的数据存储器以高速的 RAM 形式实现并集成到芯片内,以加快数据处理的速度。目前,大部分单片机和 DSP 控制器都采用哈佛结构。

I/O 端口与存储器一样,都可看作为数据源,从逻辑上讲二者没有本质的差异。有的微处理器芯片,其存储空间与 I/O 空间是相互分离的,可以拥有相同的地址,它们的访问通过控制线来区分(对应不同类型的指令),像 Intel 8086 系列;有的微处理器芯片,其存储空间与 I/O 空间是同一个地址空间,也就是把 I/O 空间映射到存储空间,二者通过地址来区分,这样一来对存储器和 I/O 端口的访问使用同类型的指令,像 Intel 8051 系列。

DSP 控制器采用独立的程序存储器、数据存储器和 I/O 空间,即它们可以有相同的地址,而它们的访问通过控制线来区分。除此之外,数据存储器还分为局部数据存储器和全局数据存储器,这二者也可共用相同的地址空间,它们的访问除了通过不同的控制线来区分以外,还受全局存储器分配寄存器(GREG)的控制。

DSP 控制器使用 16 位的地址总线,可访问的四种独立的选择空间是(共 224K 字):

- 64K 字程序存储器空间,包含要执行的指令及程序执行时使用的数据。

- 64K 字局部数据存储器空间,保存指令使用的数据。

- 32K 字全局数据存储器空间,保存与其它处理器共用的数据,或者作为一个附加的数据空间。局部数据空间中的高 32K 字地址 (8000h~FFFFh)可用作全局数据空间。局部数据存储器与全局数据存储器可以是两个不同的物理存储器,通过修改全局存储器分配寄存器(GREG)的内容来控制当前使用何种数据存储器。但全局数据寄存器的最大空间是 32K 字(8000h~FFFFh)。

- 64K 字的 I/O 空间、用于外设接口、包括一些片内外设的寄存器。

### 2.5.1 与外部存储器和 I/O 空间接口的信号

由于 DSP 控制器四种独立选择空间都占用相同的 16 位的地址空间,因此对它们的访问必须通过控制线来区分。表 2. 4 描述了与外部存储器和 I/O 空间接口的信号,这些信号主要有四类:

- ●外部数据/地址总线, D0~D15 是数据总线, A0~A15 是地址总线。

- ●片选信号线,外部器件利用这些信号来区分是内部访问还是外部访问?是访问程序存储空间、局部数据空间、全局数据空间还是 I/O 空间?

- ●读/写信号,这些信号向外部器件指出数据传送的方向。

- ●请求/控制信号,通过这些信号可实现一些特殊操作,例如,存储器直接访问方式的实现。

| 引力            | 说 明                                        |

|---------------|--------------------------------------------|

| A15-A0        | 16 条外部地址总线,可寻址 64K 字的外部存储器或 1/() 空间        |

| D15-D0        | 16 条双向外部数据总线                               |

| <del>DS</del> | 数据存储器选择引脚。当执行访问外部(局部或全局)数据存储器指令时该引脚有效      |

| BR            | 总线请求引脚。当执行访问外部全局数据存储器指令时该引脚有效              |

| PS            | 程序存储器选择引脚。当从外部程序存储器取指令时该引脚有效               |

| ĪS            | I/O 空间选择引脚,当执行 I/O 指令时该引脚有效                |

| STRB          | 外部访问有效选通引牌。当访问外部程序、数据或 I/O 时该引脚有效          |

| R/W           | 读/写引脚                                      |

| ₹/w           | R/W 引脚的逆                                   |

| WE            | 写允许引脚。发给外部程序、数据或 I/O,请求允许对它们进行写操作          |

| MD/MC         | 微处理器/微计算机模式引脚。该引脚为高电平,器件处于微处理器模式,从外部程序存储器取 |

| MP/MC         | 复位向量;该引脚为低电平,器件处于微计算机模式,从片内程序存储器取复位向量      |

| READY         | 外围设备就绪引脚。当该引脚被驱动为低时,CPU处在等待状态,直到该引脚为高      |

|               | A15-A0 D15-D0 DS BR PS IS STRB R/W K/W WE  |

表 2.4 与外部存储器和 I/O 空间接口的信号

### 2.5.2 程序存储器

程序存储器的配置如图 2.6 所示。DSP 控制器可以使用片内程序存储器,也可以使用片外程序存储器,由引脚  $MP/\overline{MC}$ 央定。当  $MP/\overline{MC}=0$  时,使用片内程序存储器,当  $MP/\overline{MC}=1$

|                 | 程序空间                    |      | 程序空间                  |               |                   |

|-----------------|-------------------------|------|-----------------------|---------------|-------------------|

|                 | $(MP/\overline{MC}=1)$  |      | $(MP/\overline{MC}=0$ |               |                   |

| ×               | 微处理器模式)                 | Hex  | 微计算机模式)               | Hex           | 数据空间              |

| 00              | 中断                      | 0000 | 中断                    | 0000          | 专用寄存器             |

| 3F              | (外部)                    | 003F | (片内)                  | 005F          | 和保留区              |

| 10              |                         | 0040 | 片内 ROM                | 0060          | -                 |

|                 | 1                       |      | (内無 EEPROM)           |               | 片内 DARAM B2       |

|                 |                         | 3FFF | (8×2K)                | 007F<br>0080  |                   |

|                 | 外部                      | 4000 |                       | 00 <b>F</b> F | 保留                |

| 1               |                         |      | 外部                    | 0100          |                   |

| FF              |                         | FDFF | 1                     |               | 保留                |

| 00              | 片内 DARAM B0             | FE00 | 片内 DARAM BO           | 01FF<br>0200  | 片内 DARAM Bo       |

|                 | (CNF=1)或                |      | (CNF=1)或              |               | (CNF=0)或          |

| FF              | 外部(CN=0)                | FEFF | 外部(CN=0)              | 02FF          | 保留(CN=1)          |

| 00 [            | 保留                      | FF00 | 保留                    | 0300          |                   |

| FF              | <b>休日</b>               | FFFF | 体 母                   |               | 片内 DARAM BI       |

|                 |                         |      |                       | 03FF          |                   |

|                 |                         |      |                       | 0400          | 保留                |

|                 |                         |      |                       | 04FF<br>0500  | 保留                |

| ×               | 1/0 空间                  |      |                       | 07FF<br>0800  | 非法                |

| <sup>90</sup> [ | 外部                      |      |                       | 6FFF<br>7000  | 片内外设专用            |

| FF              |                         |      |                       | 7000          | (存儀器映射)寄存         |

| 00              | 保留                      |      |                       |               | 器 ADC、SCI、SPI,1/O |

| FE L            | 等待状态发生器                 |      |                       | 743F          | 中断、事件管理模块         |

|                 | 的控制寄存器                  |      |                       | 7440<br>77FF  | 保留                |

| L               | मन रक्ता भाग पर प्राप्त |      |                       | 7755          | 非法                |

|                 |                         |      |                       | 7FFF<br>8000  | 外部                |

图 2.6 程序存储器的配置

时,使用片外程序存储器。一般情况下,片内程序存储器的访问速度比片外程序存储器速度快,而且比片外程序存储器功耗低。采用片外程序存储器操作的优点是可访问更大的地址空间 (64K 字)。

程序存储器的地址分配:

- 0000h~003Fh:用于存储中断入口地址。当有中断请求信号时,CPU 从这个地方取中断服务子程序的人口。0000h 是系统复位向量地址,任何程序都得从此开始运行,所以一般在此安排一条分支跳转指令,让 CPU 转入到用户主程序的入口处。此块地址与中断服务有关,因此这个地方最好不要安排其它的程序指令。

- 0040h~FDFFh:用户程序区。根据不同的型号,可以有 4/8/16/32K 字的片内 FLASH/ROM; 0/1/2/4/8/16K 字的单口存储器 SARAM; 其余地址空间要使用的话,需要外扩。

- ●FE00h~FFFFh,这是一个双口存储器 DARAM 区 (B0),可以配置给程序存储器,也

可以配置给数据存储器,由状态寄存器 ST1 的 CNF 位决定。CNF=0,配置给数据存储器;CNF=1,配置给程序存储器。复位时 CNF=0。

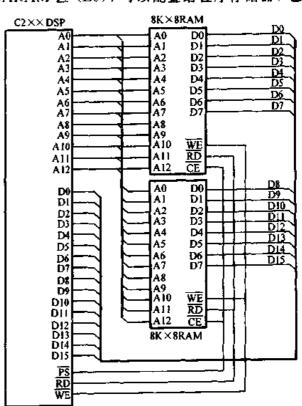

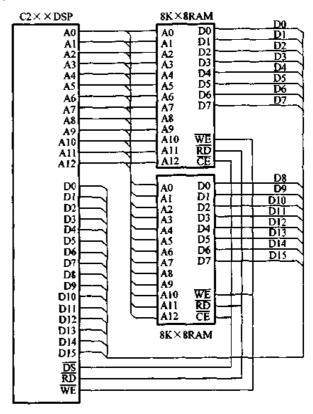

如果片內程序存储器不够用或不能用(片内ROM需要厂家写人),就需要外扩程序存储器。图 2.7 是 DSP 控制器与外部程序存储器。图 2.7 是 DSP 控制器与外部程序存储器接口的一个例子。图中利用两片 8K×8位 EEPROM 构成 8K×16 位的程序存储器。外部程序存储器线、地址线与 DSP 控制器访问片内程序存储器时,信号 PS和STRB 处于高阻状态; DSP 控制器访问外部程序存储器的片类证明外部总线被激活,信号 PS和STRB有效,此时表明外部总线证用于程序存储器。因此,可以用信号 PS作为外部程序存储器。因此,可以用信号 PS作为外部程序存储器的片选信号。如果还需扩展多片外部程序存储器的片选信号。DSP 控制器

图 2.7 外扩程序存储器

的处理速度非常快,在外扩程序存储器时必需考虑其响应时间是否与 DSP 控制器匹配。若使用较慢的存储器,则需插入等待状态以匹配二者的速度。插入等待状态有两种方法,一是利用片内等待状态发生器在访问周期中自动插入一个等待状态;二是在外部产生等待逻辑,并将其连接到 DSP 控制器的引脚 READY 上。当信号 READY 为低时,DSP 控制器处于等待状态;当信号 READY 为高时,DSP 控制器处于工作状态。采用第二种方法可以产生一个以上的等待状态,其等待的时间由外部等待逻辑发生器控制。

### 2.5.3 局部数据存储器

局部数据存储器分为片内数据存储器和片外数据存储器,其配置如图 2.8 所示。其中:

- 0000h~005Fh: 专用寄存器区。这个区间的地址由 DSP 控制器使用,安排了中断屏蔽寄存器、全局存储器分配寄存器、中断标志寄存器等。

- 0060h~007Fh: 32 个字的双口存储器 DARAM (B2), 用户数据区。

- · 0080h~00FFh. 保留。

- 0100h~02FFh: 256/512 个字的双口存储器 DARAM (B0),只当 CNF=0 才可作为用户数据区。

- 0300h~04FFh, 256/512 个字的双口存储器 DARAM (B1), 用户数据区。

图 2.8 局部数据存储器配置

- 0500h~07FFh: 保留。

- 0800h~6FFFh: 1/2/4/8/16K 字的单口存储器 SARAM, 用户数据区。

- 7000h~743Fh: 片內外设控制、数据等寄存器、是给 DSP 控制器用的专用寄存器区,可`参见附表。

- 7440h~7FFFh. 保留。

- ●8000h~FFFFh: 给片外局部数据存储器使用。

局部数据存储器的寻址范围是 64K 字。DSP 控制器的指令系统对数据存储器的寻址可以 16 位的物理地址进行访问(例如,间接寻址方式),也可以按页进行访问(例如,直接寻址方式)。

64K字的局部数据空间分成 512 个数据页(占用 9 位高地址位),每个数据页有 128 个字(占用 7 位低地址位),如表 2.5 所示。状态寄存器 STO 中 9 位数据页面指针 DP 的值确定当前使用哪个数据页。当前数据页中的每一个字则由 7 位偏移量来指定(含在指令中)。因此、在采用直接寻址方式访问数据存储器时,不但要指定数据页面(确定 DP 的值),还要指定偏移量(由指令确定)。为了加快数据的访问速度,最好把同类的数据放在同一数据页中。

表 2.5 局部数据存储器的地址分配与数据页

| DP值         | 编移量      | 数据存储器             |  |  |

|-------------|----------|-------------------|--|--|

| 0000 0000 0 | 000 0000 |                   |  |  |

| ;           | ;        | 页 0,0000h~007Fh   |  |  |

| 0000 0000 0 | 111 1111 | į                 |  |  |

| 0000 0000 1 | 000 0000 |                   |  |  |

| :           | :        | 页 1:0080h~00FFh   |  |  |

| 0000 0000 1 | 111 1111 |                   |  |  |

| 0000 0001 0 | 000 0000 |                   |  |  |

| :           | :        | 页 2:0100h~017Fh   |  |  |

| 0000 0001 0 | 111 1111 |                   |  |  |

| :           | :        | :                 |  |  |

| 1111 1111 1 | 000 0000 |                   |  |  |

| i           | :        | 页 511.FF80h~FFFFh |  |  |

| 1111 1111 1 | 111 1111 |                   |  |  |

图 2.9 外扩局部数据存储器

如果供用户使用的片内数据存储器 BO、B1 和 B2 不够用,则需外扩数据存储器。DSP 控制器在访问片内数据存储器时,信号 $\overline{DS}$ 和 $\overline{STRB}$ 处于高阻状态。仅当 DSP 控制器访问映射至外部存储器的地址范围(8000h~FFFFh)时,信号 $\overline{DS}$ 和 $\overline{STRB}$ 处于有效状态,表明数据存储器在使用外部总线。因此,可以用信号 $\overline{DS}$ 作为外部局部数据存储器的片选信号。图 2.9 是外扩局部数据存储器的例子,图中用两片  $16K\times 8$  位的 RAM 构成  $16K\times 16$  位字的 RAM。若还

有多片外部数据存储器要连,可以用高位地址线经译码后与信号DS一起构成外部局部数据存储器的片选信号。

为加快接口速度,可选用快速外部存储器。若不要求快速访问存储器,可用 READY 信号或片内等待状态发生器来建立等待状态以便和低速外部存储器接口,这和使用慢速程序存储器时采用的方法类似。

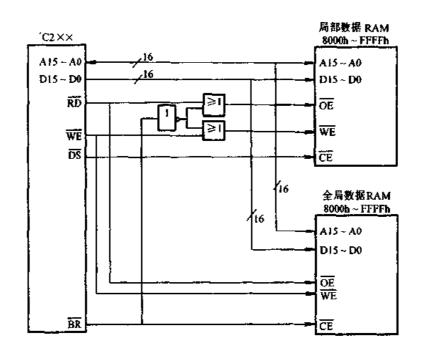

### 2.5.4 全局数据存储器

DSP 控制器除了局部数据存储器外,还有一个全局数据存储器,用于保存与其它处理器共用的数据,或者作为一个附加的数据空间。全局数据存储器的最大寻址空间是 32K 字 (8000h~FFFFh),它与局部数据存储器可以是同一个物理存储器,也可以是两个不同的物理存储器。

如果是同一个物理存储器,二者通过地址就可以区分,其地址范围由全局存储器分配寄存器 (GREG) 来指定,如表 2.6 所示。全局存储器分配寄存器 (GREG) 确定全局数据存储器空间的大小,范围在 256 到 32K 字之间。全局存储器分配寄存器的地址是 0005h、只使用低 8 位。切记只能选择表 2.6 所列出的 GREG 值,其它值会使存储器映射分成碎片。

| GREG 的值             | 局部一存储器            | 全局存储器             |

|---------------------|-------------------|-------------------|

| ×××× ×××× 0000 0000 | 0000h~FFFFh 65356 | 0                 |

| ×××× ×××× 1000 0000 | 0000h~7FFFh 32768 | 8000h~FFFFh 32768 |

| ×××× ××× 1100 0000  | 0000h~BFFFh 49152 | C000h~FFFFh 16384 |

| ×××× ××× 1110 0000  | 0000h∼DFFFh 57344 | E000h~FFFFh 8192  |

| ×××× ×××× 1111 0000 | 0000h~EFFFh 61440 | F000h~FFFFh 4096  |

| ×××× ××× 1111 1000  | 0000h~F7FFh 63488 | F800h~FFFFh 2048  |

| ×××× ×××× 1111 1100 | 0000h~FBFFh 64512 | FC00h~FFFFh 1024  |

| ×××× ××× 1111 1110  | 0000h~FDFFh 65024 | FE00h~FFFFh 512   |

| ×××× ×××× 1111 1111 | 0000h~FEFFh 65280 | FF00h~FFFFh 256   |

表 2.6 全局存储器分配寄存器(GREG)

如果不是同一个物理存储器,二者的地址空间将会有重叠的部分,特别是当局部数据存储空间需要 64K 字,全局数据存储空间需要 32K 字时,二者的高 32K 字地址空间 (8000h~FFFFh) 将完全重叠。这个时候,要区分局部数据空间和全局数据空间的访问,光靠全局存

储器分配寄存器 (GREG) 来指定地址范围就不行了,需要加上总线请求信号 $\overline{BR}$ ,如图 2.10 所示。当 DSP 控制器访问全局数据空间时,信号 $\overline{BR}$ 将被置为有效,因此可用它作为全局数据存储器的片选信号。

在局部数据存储器和全局数据存储器是两个不同的物理存储器的情况下进行数据访问时,要根据当前是访问局部数据空间还是全局数据空间,进行修改全局存储器分配寄存器 (GREG) 的值。当进行全局数据空间访问时,要先将全局存储器分配寄存器 (GREG) 的值修改到与实际的全局数据存储器的物理地址范围一致;当进行局部数据空间访问时,要先将全局存储器分配寄存器 (GREG) 的值清零,此时总线请求信号 $\overline{BR}$ 将失效,而数据存储器选择信号 $\overline{DS}$ 会有效,从而保证当前访问的是局部数据空间。

图 2.10 外扩局部和全局数据存储器

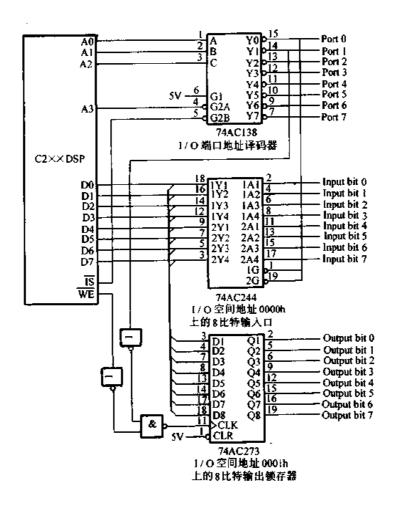

### 2.5.5 I/O 空间

DSP 控制的 I/O 空间可寻址 64K 字,由三部分组成:

- 0000h~FEFFh 用于访问片外外设。

- FF00h~FFFEh 保留。

- FFFFh, 映射为等待状态发生器的控制寄存器。

所有 I/O 空间 (外部 I/O 端口和片内 I/O 寄存器) 都可用 IN 和 OUT 指令访问。当执行 IN 或 OUT 指令时,信号IS将变成有效,因此可用信号IS作为外围 I/O 设备的片选信号。访问外部并行 I/O 端口与访问程序、数据存储器复用相同的地址和数据总线。数据总线宽度为 16 位,若使用 8 位的外设,既可使用高 8 位数据总线也可使用低 8 位数据总线,以适应特定应用的需要。图 2.11 是一个 16 位 I/O 端口接口电路。需指出,若所用 I/O 端口很少,那么译码部分可以简化。

图 2.11 16 位 I/O 端口接口电路

# 2.6 程序控制

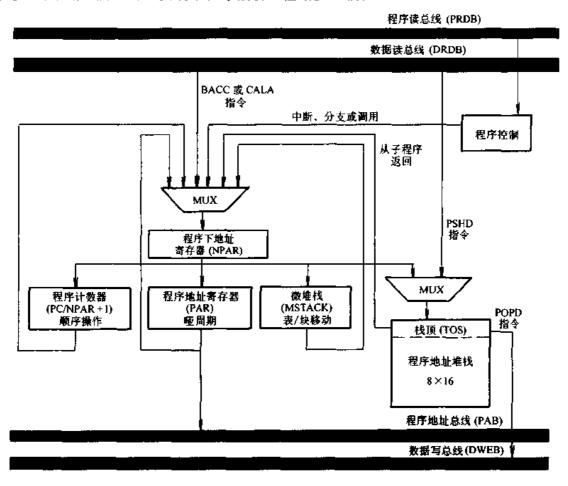

通常程序的流程是顺序的,在程序地址指针的指挥下按节拍进行工作。DSP 控制器的程序地址的产生如图 2·12 所示。

16 位的程序计数器 PC 是程序地址产生的核心部分, PC 也称为程序地址指针。系统复位时由内部硬件逻辑将 PC 置为 0000h(复位中断向量)。PC 的内容经程序地址寄存器(PAR)驱动程序地址总线(PAB),使得中央处理单元 CPU 获得当前的指令。当前指令被装入指令寄存器后, PC 的内容加 1, 为下一个地址作准备。PC 的内容决定了 CPU 下次取指的地点。

程序的流程一般是顺序的,但也存在跳变。引起程序跳变有下面一些情况。

- ●分支跳转指令。

- ●子程序调用。

- ●软、硬件中断。

- ●块传送或表传送。

如果遇到分支跳转指令,硬件逻辑会把指令中的跳转地址(立即数或累加器的低 16 位)加载到 PC,从而保证分支跳转到指定的地址上。

如果遇到的是子程序调用指令,不但需要考虑 PC 转移到子程序的人口上,而且还要考虑

到调用完后 PC 的返回。因此,首先要将返回(断点)地址,即当前调用的下一条指令地址保护起来,称为现场保护。程序地址产生模块中的8级硬件堆栈就是为此而设,这个堆栈采用先进后出、后进先出的策略。当 CPU 执行子程序调用指令时,首先自动地将返回地址压入堆栈;然后再将子程序的入口地址(含在调用指令中的长立即数或累加器的低16位)加载到 PC, CPU 转而运行子程序的指令;当碰到返回指令 RET, CPU 自动地将当前栈顶内容(返回地址)弹到 PC,从而恢复原来的断点程序继续运行。由于硬件堆栈有8级,而且采用先进后出、后进先出的策略,所以可以实现子程序嵌套,但最多8级。

图 2.12 DSP 控制器的程序地址的产生

如果是发生软、硬件中断,与子程序调用完全类似,同样需要考虑 PC 的转移与返回。在中断情况下,需要把当前中断处的指令执行完,并把返回地址(下一条指令的地址)压入堆栈;由内部硬件逻辑把中断服务子程序的人口中断向量(这个中断向量是 DSP 控制器规定的)加载到 PC 中;当碰到中断服务子程序的返回指令 RET 时,CPU 自动地将当前栈顶内容(返回地址)弹到 PC,从而恢复原来的断点程序继续运行。中断和子程序都可以嵌套,但一起不能超过 8 级。

如果进行块传送或表传送,即执行 BLDD、BLPD、MAC、MACD、TBLR 和 TBLW 指令,由于需要利用 PC 使源(目的)操作地址增 1,因此与调用子程序指令一样在执行指令之前要保护返回地址。由于块传送或表传送是单独的指令,不可能含 RET 指令在其中。因此,块传送或表传送的返回地址不能用 8 级硬件堆栈来保护。为了解决这个问题,在程序地址产

生模块中设计了一个 16 位宽、1 级深的微堆栈 (MSTACK),用这个微堆栈来保护这个返回地址 (块传送或表传送指令的下一条指令的地址)。当块传送或表传送指令执行完后,硬件逻辑自动地将微堆栈的内容弹到 PC 中。与硬件堆栈不同,不能用 PUSH、POP 等指令对微堆栈进行操作,只有程序地址产生逻辑能够使用微堆栈,而且微堆栈的操作是不可见的。

### 2.7 时钟源模块

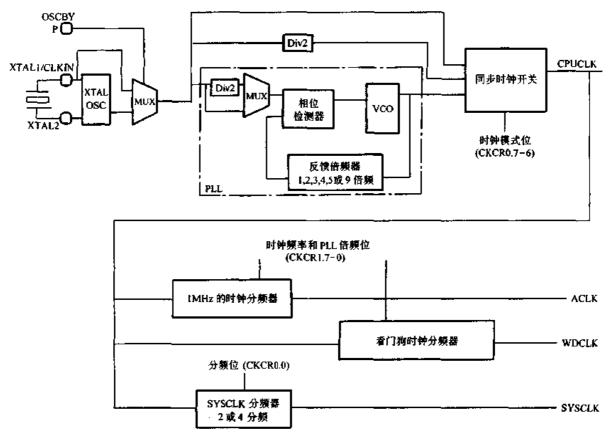

DSP 控制器的时钟源模块采用锁相环 (PLL) 技术,可以对外部振荡频率进行倍频,得到非常稳定的内部时钟。图 2.13 是时钟源模块的结构示意图。

图 2.13 时钟源模块的结构示意图

与时钟源模块相关的外部引脚:

- ●OSCBYP: 振荡器的旁路引脚。如果要使用 DSP 控制器的内部振荡器,必须外接晶振,此时该引脚接高电平;如果直接使用外部振荡器,就要将内部振荡器旁路,此时该引脚接低电平。外接晶振和外部振荡器统称为外部时钟。

- XTAL1/CLKIN: 当使用内部振荡器时,该引脚接外部晶振;当使用外部振荡器时,该引脚接外部振荡器的输出。外部晶振的频率可以是 2、4、6、8MHz,外部振荡器的输出的频率可在 2~32MHz 之间。

- ◆XTAL2:接外部晶振的另一端。如果采用外部振荡器,该引脚不使用。 在时钟源模块内产生四种时钟:

- CPUCLK, CPU 时钟,供 CPU 及总线使用,也称为机器时钟,它的周期称为 CPU (机器)周期。该时钟可以是外部时钟的 1、1.5、2、2.5、3、4、4.5、5、9 倍。

- ●SYSCLK: 它是 CPU 时钟的 2 分频或 4 分频, 为 DSP 控制器的片内外设服务。

- ACLK: 这个时钟专为 DSP 控制器中的模拟模块服务,无论外部时钟频率怎样,它的正常频率都是(1+10%) MHz。

- WDCLK: 为看门狗和实时时钟模块提供时钟, 与 ACLK 一样, 无论外部时钟频率怎样, 它的正常频率约为 16384Hz, 其占空比为 25%。

DSP 控制器的时钟源模块是可编程的,与它相关的两个寄存器是 CKCR0 和 CKCR1,它们各位的组成如表 2.7 所示,每位的定义及说明见表 2.8 和表 2.9。

| 地址    | 寄存器           | 位 数    |        |         |         |        |        |         |        |

|-------|---------------|--------|--------|---------|---------|--------|--------|---------|--------|

|       |               | 7      | 6      | 5       | 4       | 3      | 2      | 1       | 0      |

| 702Bh | CKCR0         | CLKMD1 | CLKMD0 | PLLOCKI | PLLOCK0 | PLLPM1 | PLLPMO | ACLKENA | PLLPS  |

|       |               | RW-x   | RW-x   | R-x     | R-x     | RW-0   | RW-0   | RW-x    | RW-0   |

|       | ·· <u>-</u> . | 7      | 6      | . 5     | 4       | 3      | 2      | . 1 .   | 0      |

| 702Dh | CKCRI         | CKINF3 | CKINF2 | CKINFI  | CKINF0  | PLLDIV | PLLFB2 | PLLFB1  | PLLFB0 |

|       |               | RW-x   | RW-x   | RW-x    | RW-x    | RW-x   | RW-x   | RW-x    | RW-x   |

表 2.7 时钟控制寄存器 CKCR0 和 CKCR1

表 2.8 时钟控制寄存器 CKCR0 各位定义与说明

| 位           | 定        | 义      | 说                      | 明                      |  |  |

|-------------|----------|--------|------------------------|------------------------|--|--|

| · · · · · · | CLKMDI   | CLKMD0 | CPU 时钟(CPUCLK)来源方式     |                        |  |  |

|             | 0        | 0      | CLKIN/2,外部頻率的 2 分頻     | <u></u>                |  |  |

| Bits 7-6    | 0        | 1      | CLKIN,直接使用外部頻率         |                        |  |  |

|             | 1        | 0      | PLL,经过 PLL 电路(可倍频)     |                        |  |  |

|             | 1        | 1      | PLL,经过 PLL 电路(可倍频)     |                        |  |  |

| Div. 6      | PLI OCKI | 0      | 只读,使用 PLL 电路           | D1 r + B4 44 Av F72 (A |  |  |

| Bits5       | PLLOCKI  | 1      | 只读,未使用 PLL 电路          | PLL 电路的使用状态            |  |  |

|             |          | 0      |                        |                        |  |  |

| Bits4       | PLLOCK0  | 1      | ── 只读,用于系统测试<br>│      |                        |  |  |

|             | PLLPM1   | PLLPM0 | 执行空闲指令后,4种时钟的状         | 汉                      |  |  |

|             | 0        | 0      | CPUCLK 停               |                        |  |  |

| Bits3-2     | 0        | 1      | CPUCLK、SYSCLK、ACLK 停   |                        |  |  |

|             | 1        | 0      | CPUCLK、SYSCLK、ACLK 停   | PLL 停                  |  |  |

|             | I        | 1      | 全停                     |                        |  |  |

|             |          | 0      | 停止 ACLK                |                        |  |  |

| Bits1       | ACLKENA  | 1      | 使能 ACLK                |                        |  |  |

| Div. o      | 21.1.70  | 0      | SYSCLK 取 CPUCLK 的 4 分別 | ·                      |  |  |

| Bits0       | PLLPS    | 1      | SYSCLK 取 CPUCLK 的 2 分頻 |                        |  |  |

表 2.9 时钟控制寄存器 CKCR1 各位定义与说明

| 位        |        | 定        | . 义    | 说明            |                   |

|----------|--------|----------|--------|---------------|-------------------|

|          | CKINF3 | CKINF2   | CKINFI | CKINF0        | 外部頻率的选择<br>单位:MHz |

| [        | 0      | 0        | 0      | 0             | 32                |

|          | 0      | 0        | 0      | 1             | 30                |

| Ī        | 0      | 0        | 1      | 0             | 28                |

|          | 0      | 0        | 1      | 1             | 26                |

|          | 0      | 1        | 0      | 0             | 24                |

|          | 0      | 1        | 0      | 1             | 22                |

|          | 0      | 1        | 1      | 0             | 20                |

| Bits 7-4 | 0      | . 1      | 1      | 1             | 18                |

| Ì        | 1      | 0        | 0      | 0             | 16                |

| Ī        | ]      | 0        | 0      | 1             | 14                |

|          | 1      | 0        | 1      | 0             | 12                |

| Ī        | 1      | 0        | 1      | 1             | 10                |

| ļ        | 1      | 1        | 0      | 0             | 8                 |

|          | 1      | 1        | 0      | 1             | 6                 |

|          | 1      | 1        | 1      | 0             | 4                 |

| ļ        | 1      | 1        | 1      | 1             | 2                 |

|          |        |          |        | 0             | PLL 输入不经 2 分頻     |

| Bits3    | PLL    | .DIV     |        | PLL 输入经过 2 分频 |                   |

| -        | PLLFB2 | I        | PLLFB1 | PLLFB0        | PLL 倍频率           |

|          | 0      |          | 0      | 0             | 1                 |

|          | 0      |          | 0      | 1             | 2                 |

|          | 0      | <u> </u> | 1      | 0             | 3                 |

| Bits 2-0 | 0      |          | 1      | 1             | 4                 |

|          | 1      |          | 0      | 0             | 5                 |

|          | 1      |          | 0      | 1             | 9                 |

|          | 1      | "        | 1      | 0             | 1                 |

| ľ        | 1      |          | 1      | 1             | 1                 |

CPU 时钟是 DSP 控制器最重要的时钟源。它可以直接取自外部时钟或它的 2 分频,也可以由 PLL 电路对外部时钟进行倍频得到,这一切由时钟控制寄存器 CKCR0 的 CLKMD1:0 决定。采用 PLL 电路进行倍频时,其倍频系数由时钟控制寄存器 CKCR1 的 PLLFB2:0 设置。考虑到 PLL 电路的输入可先进行 2 分频(取决时钟控制寄存器 CKCR0 的 PLLDIV 位),因此 CPU 时钟可以是外部时钟的 1、1.5、2、2.5、3、4、4.5、5、9 倍。

设外部晶振或外部时钟的频率为  $F_x$ , CPU 时钟(机器时钟)的频率为  $F_c$ 。它们之间的

关系为:

$$F_{c} = \begin{cases} F_{x}/2 & \text{若 CLKMD1}: 0 = 00 \\ F_{x} & \text{若 CLKMD1}: 0 = 01 \\ F_{x} \times (\text{PLL 倍频率})/2^{\text{PLLDIV}} & \text{若 CLKMD1}: 0 = 10 或 11 \end{cases}$$

(2.1)

SYSCLK 时钟是为挂接在片内外设总线上各功能模块服务的,它是 CPU 时钟的 2 分频或 4 分频,由时钟控制寄存器 CKCR0 的 PLLPS 决定。

ACLK 时钟专为片内模拟外设服务。当不需要使用该时钟时,可通过时钟控制寄存器 CKCR0 的 ACLKENV 位将其关闭,以减少能量消耗和电磁辐射(1MHz)。DSP 控制器加电复位时,该时钟处于关闭状态。ACLK 时钟频率在 1MHz 左右,不随外部时钟频率变化,但外部时钟频率的选择必须符合时钟控制寄存器 CKCR1 的 CKINF3:0 的要求。如果 CPU 时钟频率的兆赫数是奇数的话,ACLK 时钟频率实际上是 0.5MHz。

WDCLK 时钟为 DSP 控制器的看门狗与实时时钟模块提供时钟源。它的产生办法与ACLK时钟类似。大约送出 16kHz 左右的时钟信号。如果外部时钟 CLKIN 的频率是 2Hz 的乘方,则 WDCLK 的频率为 16384Hz。如果外部时钟 CLKIN 的频率正好是 4MHz 或其倍数,则 WDCLK 的频率为 15625Hz。如果想增加 WDCLK 的频率,可以采取将时钟控制寄存器 CK-CR1 的 CKINF3:0 设为不正确的值来实现,例如外部时钟 CLKIN 的频率为 4.194304MHz,但将 CKINF3:0 设为 1111 (2MHz),此时 WDCLK 的频率将为 32768Hz。这不是一个很好的办法,因为它会影响到 ACLK 的频率。

DSP 控制器加电复位时,锁相环电路 PLL 未被使用(CLKMD=00),CPU 时钟为外部时钟的 2 分頻,且 PLLF2:0=000,PLLDIV=0。如果要使用锁相环电路 PLL,则要设置 PLLF2:0 和 PLLDIV,并置 CLKMD1=1,经过  $100\mu$ s 的延迟,锁相环电路 PLL 被加电开始工作。在这段时间若要阻止某些代码执行,可通过读取 PLL 的状态(PLLOCK1)来编程实现。如果在运行过程中修改 PLL 的倍率(PLLF2:0 和 PLLDIV),它不能马上见效。需要先将 CLKMD1 清 0,然后接着置 1,这样新的倍率值就被写入到锁相环电路 PLL 中。

与系统时钟源模块紧密相关的是系统空闲功能的实现。在系统空闲时,可以将某些时钟源停止,以节省能量。当需要时,再将其唤醒。在当今环保要求越来越高的情况下,这一点是非常有意义和重要的。DSP 控制器有四种空闲方式,由时钟控制寄存器 CKCRO 的PLLPM1: 0 来设置,参见表 2.10。当空闲指令 (IDLE) 被执行时,DSP 控制器将处于PLLPM1: 0 规定的某种空闲方式下。

| 方式    | PLLP<br>M1:0 | Mem _<br>Domain | Sys _ Do | DCL<br>K | PLL<br>状态 | 振荡器<br>状态 | 电源消耗   | 退 出 条 件                                          |

|-------|--------------|-----------------|----------|----------|-----------|-----------|--------|--------------------------------------------------|

| 正常    | ××           | On              | On       | On       | On        | On        | >40mA  |                                                  |

| IDELI | 00           | Off             | On       | On       | Оп        | On        | 约 15mA | RS、NMI、看门狗中断、任何<br>未屏蔽的中断                        |

| IDEL2 | 01           | Off             | Off      | On       | On        | On        | ,约 4mA | RS、NMI、看门狗中断、任何<br>未屏蔽的外部中断、未使用<br>SYSCLK的片内外设中断 |

表 2.10 系统空闲方式

| 方式                 | PLLP<br>M1:0 | Mem _<br>Domain | Sys_Do | DCL<br>K | PLL<br>状态 | 振荡器 | 电源消耗  | 退出条件                                                       |

|--------------------|--------------|-----------------|--------|----------|-----------|-----|-------|------------------------------------------------------------|

| PLL<br>掉电<br>(PPD) | 10           | Off             | Off    | On       | Off       | On  | 约 ]mA | RS、NMI、看门狗中断、任何<br>未 屏 蔽 的 外 都 中 断、未 使 用<br>SYSCLK 的片内外设中断 |

| 振荡器<br>掉电<br>(OPD) | 11           | Off             | Off    | Off      | Off       | Off | <30μA | RS、NMI、任何未屏蔽的外部中断、未使用 SYSCLK 的片内外设中断                       |

表 2.10 中的存储时钟域 (Mem\_Domain) 是指用在除了中断寄存器以外的存储器、寄存器的 CPUCLK, 系统时钟域 (SYS\_Domain) 是指 CPUCLK、SYSCLK、ACLK 三种时钟源, 它包含了存储时钟域和中断寄存器用的 CPUCLK。唤醒中断包含各种片内、片外中断。

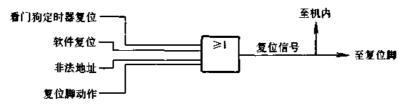

### 2.8 系统复位

有六种信号可使 DSP 控制器复位:

- ●电源复位:由引脚PORESET引起。该引脚产生一个由低到高的电平变化,将产生复位信号。为了可靠复位,其低电平有效时间至少需要6个CPU时钟周期。

- ●复位引脚RS:该引脚是 I/O 类型的,当作为输入引脚时,其作用与引脚PORESET相同: 当作为输出引脚时,可将 DSP 控制器的复位信号送给其它的器件。

- ●软件复位: 将系统控制寄存器 STSCR 的 RESET0 清 0 或 RESET1 置 1, 将产生复位信号(见表 2.11~表 2.13)。

- ●非法地址:如果在程序运行过程中,出现了非法地址,将产生复位信号。

- ●看门狗定时器溢出:看门狗是为了监控系统运行状况而设。当系统运行出现故障时,通过看门狗定时器溢出产生复位信号,使系统重新开始。

- ●欠电压复位: 这与 DSP 控制器的型号有关。当内嵌了欠电压检测电路时,如果发生欠电压,将产生复位信号。

系统复位见图 2.14。

图 2.14 系统复位

复位信号实际上是一个不可屏蔽的中断。当系统收到复位信号后,将复位中断向量 0000H 加载到程序计数器 PC 中。一般情况下,该处设有一条分支指令,以跳转到主程序人口上。系统复位后:

- ●CNF=0,双口存储器 DARAM (B0) 分配给数据空间。

- ●INTM=1,禁止可屏蔽中断。

- ●系统状态: OV=0, XF=1, SXM=1, PM=00, C=1。

- ●全局存储器分配寄存器 GREG=×××××××× 000000000。

- ●重复计数器 RPTC=0。

- ●等待状态的周期设为最大。

表 2-11 系统控制寄存器(SYSCR)和系统状态寄存器(SYSSR)的组成

| 地址    | 寄存器   |                |          |               | 位        | 数        |          |          |          |

|-------|-------|----------------|----------|---------------|----------|----------|----------|----------|----------|

|       |       | 15             | 14       | 13            | 12       | 11       | 10       | 9        | 8        |

| 70]8h |       | RESET1         | RESET0   | Reserved      | Reserved | Reserved | Reserved | Reserved | Reserved |

|       | ayean | R/ <b>W</b> -0 | R/W-1    | -             |          |          |          |          |          |

|       | SYSCR | 7              | 6        | 5             | 4        | 3        | 2        | 1        | 0        |

|       |       | CLKSRC1        | CLKSRC0  | Reserved      | Reserved | Reserved | Reserved | Reserved | Reserved |

|       |       | R/W-1          | R/W-1    |               |          |          |          |          |          |

| ·     | SYSSR | 15             | 14       | 13            | 12       | 11       | 10       | 9        | 8        |

|       |       | PORST          | Reserved | Reserved      | ILLADR   | Reserved | SWRST    | WDRST    | Reserved |

| 701Ah |       | R/C-x          |          | <del></del> - | R/C-x    |          | R/C-x    | R/C-x    |          |

|       |       | 7              | 6        | 5             | 4        | 3        | 2        | 1        | 0        |

|       |       | Reserved       | Reserved | нро           | Reserved | VCCAOR   | Reserved | Reserved | VECRD    |

|       |       |                |          | R/C-1         |          | R-1      |          |          | R-0      |

表 2-12 系统控制寄存器(SYSCR)各位定义与说明

| 位         | 定       | 义       | 说 明           |

|-----------|---------|---------|---------------|

|           | RESET1  | RESET0  | 软件复位,两位要同时写   |

|           | 0       | 0       | 系统复位          |

| Bits15-14 | 0       | 1       | 无效            |

|           | 1       | 0       | 系统复位          |

|           | 1       | 1       | 系统复位          |

| Bits 13-8 | 保       |         |               |

|           | CLKSRC1 | CLKSRC0 | 引脚 CLKOUT 的功能 |

|           | 0       | 0       | 数字 I/O        |

| Bits7-6   | 0       | 1       | 输出 WDCLK      |

|           | 1       | 0       | 輸出 SYSCLK     |

|           | 1       | 1       | 输出 CPUCLK     |

| Bits5-0   | 保       |         |               |

表 2.13 系统状态寄存器(SYSSR)各位定义与说明

| 位         | 定     | 义   |   | 说 明      |

|-----------|-------|-----|---|----------|

| Bits15    | PORST |     | 0 | 没有电源复位   |

| Dits13    | roksi |     | 1 | 由电源引起了复位 |

| Bits14-13 | 伤     | 1 留 |   |          |

(续)

| 位       | 定      | 义 | 说 明                  |

|---------|--------|---|----------------------|

| Bits 12 | ILLADR | 0 | 没有非法地址复位             |

| Dittal  | ILLADR | 1 | 由非法地址引起了复位           |

| Bits11  | 保      | 留 |                      |

| Bits 10 | CWDCT  | 0 | 没有软件复位               |

| DITSTO  | SWRST  | 1 | 由软件引起了复位             |

| Bits9   | WINDOT | 0 | 没有看门狗复位              |

| Ditsa   | WDRST  | 1 | 由看门狗引起了复位            |

| Bits8-6 | 保      | 留 |                      |

| Bits5   | HPO    | 0 | 正常模式                 |

| Ditsa   | nro    | 1 | FLASH 存储器编程模式        |

| Bits4   | 保      | 留 |                      |

| Bits3   | VCCAOR | 0 | VCCA 自动调节            |

| DIISŞ   | (欠压检测) | 1 | VCCA 不调节             |

| Bits2-1 | 保      | 留 |                      |

| Bits0   | VECRD  | 0 | 系统中断向量寄存器 SYSIVR 空   |

| Ditsv   | VECKD  | 1 | 系统中断向量寄存器 SYSIVR 已写。 |

# 第3章 片内外设

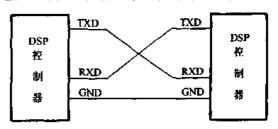

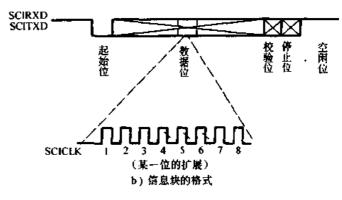

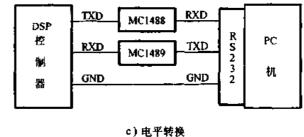

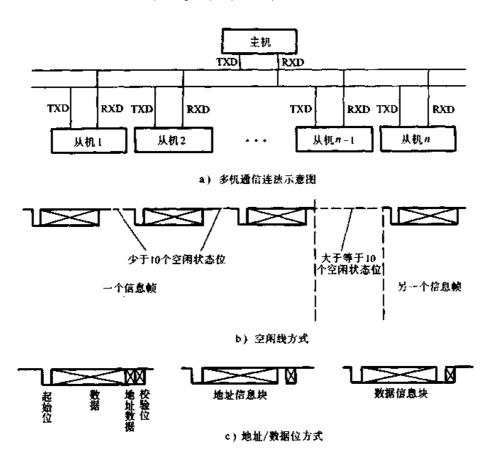

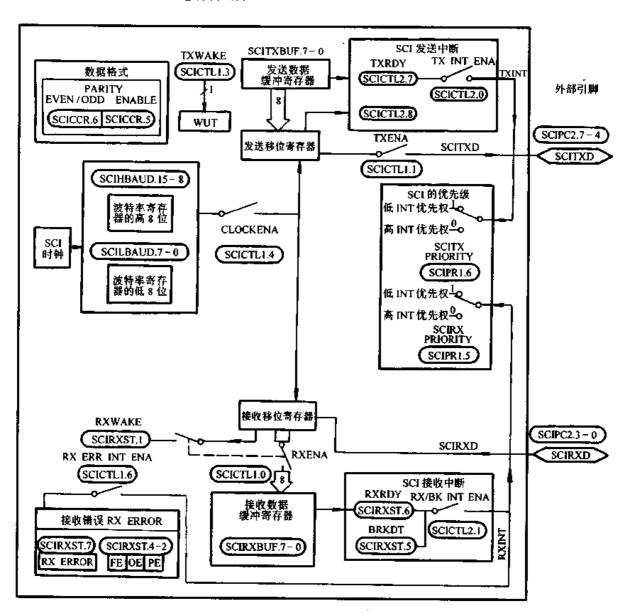

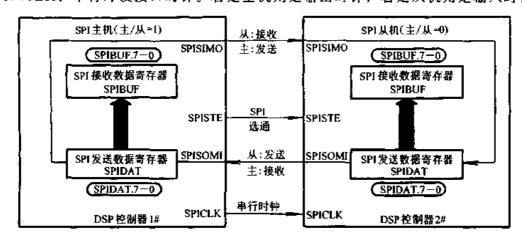

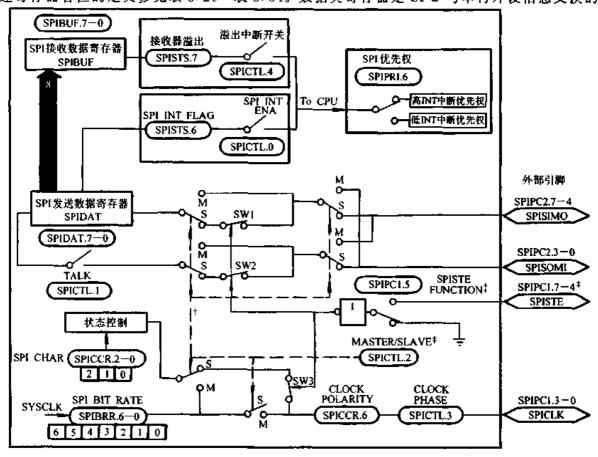

DSP 控制器是一个单片系统,除了有中央处理单元,还有片内程序存储器、数据存储器以及片内外设。片内外设包括事件管理模块(EV)、A/D 转换模块(ADC)、串行通信模块(SCI)、串行外设接口模块(SPI)、中断管理系统和系统监视模块。事件管理模块(EV)含有通用定时器、比较器、PWM 发生器、捕获器。A/D 转换模块(ADC)包含两个 8 通道 10 位的 A/D 转换器,实现模拟量到数字量的转换。串行通信接口模块(SCI)是一个标准的串行异步数字通信接口模块,可以实现半双工或双工的通信,通信速率可达 625kbps。串行外设接口模块(SPI)实际上是提供了一个高速同步串行总线,实现与带有 SPI 接口芯片的连接。目前,设备小型化的要求越来越强烈,为了减少引脚线缩小芯片尺寸,采用 SPI 接口的芯片越来越多,因此 DSP 控制器提供 SPI 接口为工程应用系统带来了便利。中断管理系统负责处理 DSP 内核中断、片内外设以及外部引脚中断的响应过程。系统监视模块由看门狗和实时中断定时器组成,负责监视 DSP 控制器的软件、硬件运行状况。一旦系统出现故障,可在一定时间内复位或恢复到定制的状态。

# 3.1 事件管理模块

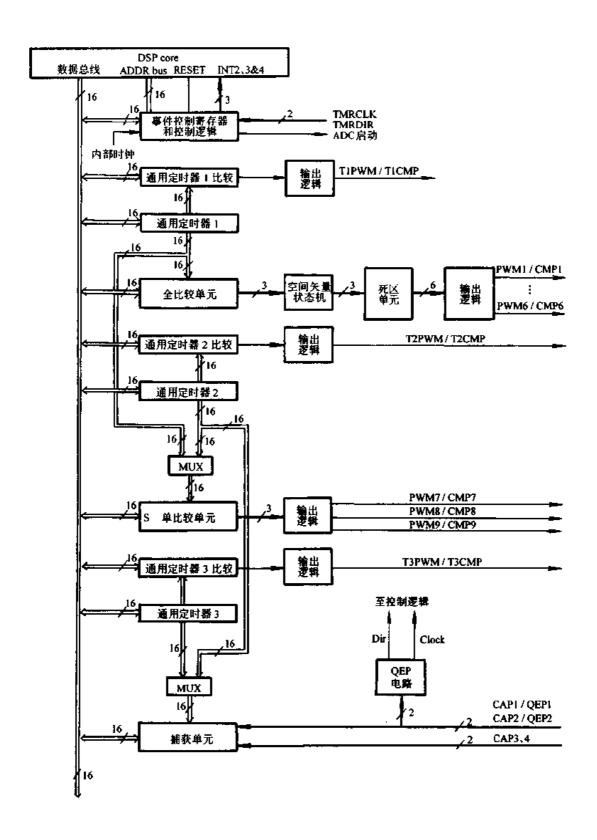

在微机控制系统中,两类事件是非常重要的,一类是与时间有关的事件,另一类是外部中断事件。一个控制程序是否优良,与这两类事件使用好坏有着直接的关系。在控制程序中,经常采用定时采样、定时显示、定时轮询等方式,以及要求输出各种各样的控制波形,这些都需要通过与时间有关的事件来完成。此外,通过对时间分片还可以实现多进程的控制方式。中断是微机控制系统另一种非常好的控制方式,因为只是在有中断请求时,CPU 才可能去对它服务,这样一来就可以不用软件轮询的方式来访问外设接口,从而节约软件开销,简化程序结构。DSP 控制器的事件管理模块主要涉及与时间有关的事件。

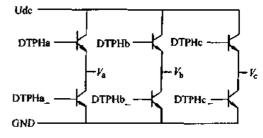

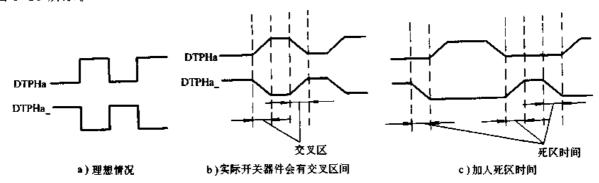

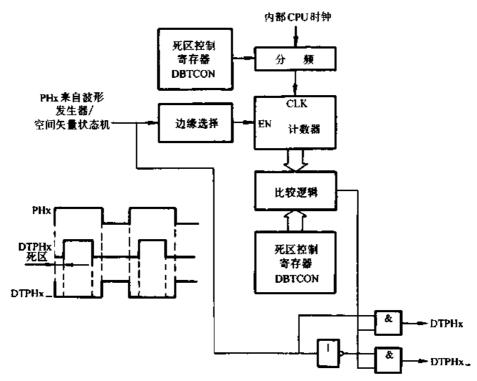

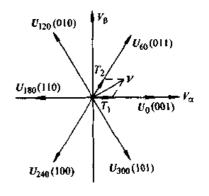

图 3.1 是 DSP 控制器事件管理模块的结构示意图。它由 3 个通用定时器、6 个全比较单元、3 个单比较单元、4 个捕获单元、2 个正交编码脉冲电路组成。表 3.1 列出了与事件管理模块相关的引脚说明。

一般情况下,每个单元模块都有多种功能或多种工作方式,它的功能实现是由相关的寄存器和引脚完成。寄存器分为两大类:控制类寄存器和数据类寄存器。当前具体使用哪种功能或哪种工作方式由它的控制类寄存器来规定。因此,在使用某种功能模块之前需要对它的控制类寄存器进行初始化。这种模块也称为可编程模块。从用户编程的角度来看,使用某种功能模块实际上就是对它的控制类寄存器或数据类寄存器进行读写,而对应的引脚变化或其它的物理过程是模块自身完成的。因此,对于寄存器的地址以及每位含义的了解是至关重要的。

图 3.1 DSP 控制器事件管理模块的结构示意图

| 引力          | 说 明                  | 引脚          | 说明                   |

|-------------|----------------------|-------------|----------------------|

| CARL OFF    | 捕获单元1的输入/正交编码脉冲      | PWM5/CMP5   | 全比较单元 3 的比较/PWM 输出 1 |

| CAP1/QEP1   | 电路1的输入               | PWM6/CMP6   | 全比较单元 3 的比较/PWM 输出 2 |

| CA Da (OFDa | 捕获单元 2 的输入/正交编码脉冲    | PWM7/CMP7   | 单比较单元1的比较/PWM 输出     |

| CAP2/QEP2   | 电路2的输入               | PWM8/CMP8   | 单比较单元 2 的比较/PWM 输出   |

| CAP3        | 捕获单元 3 的输入           | PWM9/CMP9   | 单比较单元 3 的比较/PWM 输出   |

| CAP4        | 捕获单元 4 的输入           | T1PWM/T1CMP | 通用定时器 1 的比较/PWM 输出   |

| PWM1/CMP1   | 全比较单元 1 的比较/PWM 输出 1 | T2PWM/T2CMP | 通用定时器 2 的比较/PWM 输出   |

| PWM2/CMP2   | 全比较单元 1 的比较/PWM 输出 2 | ТЗРWМ/ТЗСМР | 通用定时器 3 的比较/PWM 输出   |

| PWM3/CMP3   | 全比较单元 2 的比较/PWM 输出 1 | TMRCLK      | 通用定时器外部时钟输入          |

| PWM4/CMP4   | 全比较单元 2 的比较/PWM 输出 2 | TMRDIR      | 通用定时器外部计数方向输入        |

表 3.1 事件管理模块的相关引脚的说明

### 3.1.1 通用定时器

定时器是最常用的外围设备,它的核心是计数器。DSP 控制器的三个通用定时器都采用 16 位的计数器,它们的计数范围是 0~65535 个脉冲。计数脉冲可以由内部时钟经分频产生,也可以由外部引脚时钟提供。计数方向可以是增计数也可以是减计数。定时器内设有周期寄存器和比较寄存器。定时器除了产生上溢(增计数时)、下溢(减计数时)事件外,当计数值与周期寄存器的值或比较寄存器的值相等时,还会产生周期匹配或比较匹配两种事件。如果开启了比较输出功能,这些事件还将引起输出引脚的电平变化。所以,DSP 控制器的通用定时器为控制系统的各种应用提供了设计上的便利。图 3.2 是通用定时器的结构示意图。

与通用定时器相关的引脚(x=1,2,3,下同):

- TMRDIR:用于确定通用定时器计数增/减方式,高电平为增计数,低电平为减计数。

- ●TMRCLK:外部引脚时钟,最大频率是 CPU 时钟频率的 1/4。

- TxPWM/TxCMP. 通用定时器输出引脚。在通用定时器的比较输出操作被开启时,该引脚才起作用,否则处于高阻状态。

- ADC \_ Start: A/D 转换的启动信号。当定时时间到了时,自动发出这个启动信号。 与通用定时器相关的寄存器:

- TxCNT (Count): 16 位计数寄存器,可读写。

- TxCMPR (Compare): 16 位定时比较寄存器,存放待比较的值,可读写,双缓冲结构。 当计数寄存器的计数值与定时比较寄存器的值相等时将产生比较匹配事件。

- ●TxPR (Period): 16 位定时周期寄存器,存放周期值,可读写,双缓冲结构。当计数寄存器的计数值与定时周期寄存器的值相等时将产生周期匹配事件。

- TxCON (Control): 16 位定时控制寄存器,可读写,决定操作模式、时钟选择、分频系数预定标因子以及对定时比较寄存器和定时周期寄存器的控制。

- ◆ GPTCON (GP Control), 16 位通用定时控制寄存器,可读写,主要规定由哪种定时事件启动 A/D 转换,同时也可决定四种定时事件的优先级。

对可编程功能模块(芯片)的操作,实际上就是对它的寄存器进行读写。上述五个通用

定时器相关寄存器的地址见附表 B。计数寄存器 TxCNT 是通用定时器的核心,它记录输入给它的脉冲数。计数脉冲可由内部引脚时钟提供也可由外部时钟提供,其时钟的选择及分频系数由定时控制寄存器 TxCON 相应位决定。当计数寄存器的值达到 FFFFh 时将产生上溢事件,当计数寄存器的值达到 0000h 时将产生下溢事件,并分别在中断标志寄存器 EVIFRA 和 EVIFRB 中的 TxOFINT 位和 TxUFINT 位上产生置位。

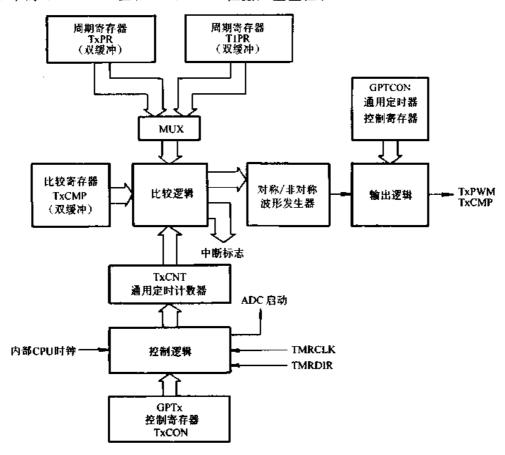

图 3.2 通用定时器的结构示意图

定时比较寄存器 TxCMPR 存放待比较的值,它是双缓冲结构,分为缓冲寄存器和工作寄存器。定时比较缓冲寄存器可在任何时候进行读写。但是,定时比较缓冲寄存器的内容什么时候装载到它的工作寄存器,取决于定时控制寄存器 TxCON 的设置,参见表 3.3。计数寄存器的值不断与定时比较工作寄存器的值进行比较,一旦相等就产生比较匹配事件,在中断标志寄存器 EVIFRA 和 EVIFRB 中的 TxCINT 位上产生置位,同时还会给出相应的 A/D 转换启动信号(取决于通用定时控制寄存器 GPTCON 的 TxADC1:0 的设置),在通用定时器的比较输出操作被开启时(由定时控制寄存器 TxCON 的 TECMPR 和通用定时控制寄存器 GPTCON 的 TCOMPOE 来设置),还将使引脚 TxPWM/TxCMP 产生跳变。

定时周期寄存器 TxCPR 与定时比较寄存器 TxCMPR 相类似,它存放周期值,也是双缓冲结构,分为缓冲寄存器和工作寄存器,可在任何时候对它的缓冲寄存器进行读写。定时周期缓冲寄存器的内容装载到它的工作寄存器,只能在计数寄存器的值为 0 时进行。计数寄存器的值不断与定时周期工作寄存器的值进行比较,一旦相等就产生周期匹配事件,在中断标志寄存器 EVIFRA 和 EVIFRB 中的 TxPINT 位上产生置位。在连续计数模式下,有了定时周

期寄存器就可以产生连续的周期信号,再通过定时比较寄存器控制脉宽,就可以产生任意调制的 PWM 波形。

定时控制寄存器 TxCON 和通用定时控制寄存器 GPTCON 决定了通用定时器的工作方式,在使用通用定时器前必须对它们进行初始化。16 位定时控制寄存器 TxCON 各位组成如表 3.2 所示,各位的定义与说明见表 3.3。16 位通用定时控制寄存器 GPTCON 各位组成如表 3.2 所示,各位的定义与说明见表 3.4。定时控制寄存器 TxCON 主要决定通用定时器的计数模式、分频系数、时钟选择、定时比较寄存器重装载条件、定时器比较输出操作的使能、定时器的开启与关闭等。通用定时控制寄存器 GPTCON 主要决定由哪个定时器的何种事件来启动 A/D 转换以及三个定时器比较输出的极性。

| 地址                      | 寄存器               |              |             |              | 位           | 数           |       |             |              |

|-------------------------|-------------------|--------------|-------------|--------------|-------------|-------------|-------|-------------|--------------|

|                         |                   | 15           | 14          | 13           | 12          | 11          | 10    | 9           | 8-7          |

|                         |                   | T3STAT       | T2STAT      | TISTAT       | Т3Т(        | DAC         | T2T0  | ODAC        | TITODAC      |

| 7400h                   | 0.000000          | R-1          | R-1         | R-1          | RV          | <b>V</b> -0 | RY    | <b>W</b> -0 | RW-0         |

|                         | GPTCON            |              | 6           | 5            | 4           | 3           | 2     | 1           | 0            |

|                         |                   | тсомрое      |             | T31          | PIN         | Т21         | PIN   | T1          | PIN          |

|                         |                   | RV           | <b>W</b> -0 | RV           | <b>V</b> -0 | RW          | 7-0   | RV          | <b>V</b> -0  |

| 7404h<br>7408h<br>740Ch | TxCON (x=1, 2, 3) | 15           | 14          | 13           | 12          | 11          | 10    | 9           | 8            |

|                         |                   | Free         | Soft        | TMODE2       | TMODE1      | TMODE0      | TPS2  | TPS1        | TPS0         |

|                         |                   | <b>R₩</b> -0 | RW-0        | <b>RW</b> -0 | RW-0        | RW-0        | RW-0  | RW-0        | RW-0         |

|                         |                   | 7            | 6           | 5            | 4           | 3           | 2     | 1           | 0            |

| 740011                  |                   | TSWT1        | TENABLE     | TCLKS1       | TCLKS0      | TCLD1       | TCLD0 | TECMPR      | SELTIPR      |

|                         |                   | RW-0         | RW-0        | RW-0         | RW-0        | RW-0        | RW-0  | RW-0        | <b>RW</b> -0 |

表 3.2 定时控制寄存器和通用定时控制寄存器

| 表 3.3 定时控制器 | TxCON | 的定义与说明 |

|-------------|-------|--------|

|-------------|-------|--------|

| 位        | ភ      | È 3    | ×      | 说              |

|----------|--------|--------|--------|----------------|

|          | Free   |        | soft   | 仿真控制           |

|          | 0      |        | 0      | 仿真悬挂时立即停止      |

| Bit15-14 | 0      |        | 1      | 仿真悬挂时完成当前周期后停止 |

|          | 1      |        | 0      | 不受仿真悬挂的影响      |

|          | 1      |        | 1      | 不受仿真悬挂的影响      |

|          | TMode2 | TMode1 | TMode0 | 计数模式           |

|          | 0      | 0      | 0      | 模式 0: 停止/保持    |

|          | 0      | 0      | 1      | 模式 1; 单增计数     |

|          | 0      | 1      | 0      | 模式 2: 连续增计数    |

| Bit13-11 | 0      | 1      | 1      | 模式 3: 定向增/减计数  |

|          | 1      | 0      | 0      | 模式 4; 单增/减计数   |

|          | 1      | 0      | 1      | 模式 5:连续增/藏计数   |

|          | 1      | 1      | 0      | 保留             |

|          | 1      | 1      | 1      | 保留             |

|          |          |                  |                                       |                                  |                            |                                       | (狭)              |

|----------|----------|------------------|---------------------------------------|----------------------------------|----------------------------|---------------------------------------|------------------|

| 垃        |          | <del></del>      | 义                                     |                                  | 说                          | 明                                     |                  |

|          | TPS2     | TPS1             | TPS0                                  | 分頻系数 (F <sub>c</sub> 是)          | CPU 时钟频率)                  |                                       |                  |

|          | 0        | 0                | 0                                     | F <sub>c</sub> /1                | <u> </u>                   |                                       |                  |

|          | 0        | 0                | 1                                     | F <sub>c</sub> /2                |                            | <u> </u>                              |                  |

|          | 0        | 1                | 0                                     | $F_c/4$                          |                            | · · · · · · · · · · · · · · · · · · · | · ···            |

| Bit 10-8 | 0        | 1                | 1                                     | $F_c/8$                          |                            |                                       |                  |

|          | 1        | 0                | 0                                     | $F_c/16$                         |                            |                                       |                  |

|          | 1        | _0               | 1                                     | $F_{\epsilon}/32$                |                            |                                       |                  |

|          | 11       | 1                |                                       | Fc/64                            |                            |                                       |                  |

|          | 1        | 1                | 1                                     | $F_c/128$                        |                            |                                       |                  |

| Bit 7    | т        | SWT1             | 0                                     | 使用自己的使能位                         | Ì                          |                                       |                  |

|          | (对 T1    | CON 无效)<br>      | 1                                     | 以 TICON 的 TE                     | nable 位作为使能位               | Ì                                     |                  |

| Bit 6    | т        | enable           | 0                                     | 停止计数,保持原                         |                            |                                       |                  |

|          | <u> </u> |                  | 1                                     | 使能 (启动) 计数                       | <b>x</b>                   |                                       |                  |

|          | TCL      | .KSI             | TCLKS0                                | 时钟选择                             |                            |                                       |                  |

|          |          | 0                | 0                                     | 内部时钟                             |                            |                                       |                  |

|          |          | o                | 1                                     | 外部时钟                             |                            |                                       |                  |

| Bit5-4   | 1        | 1                | 0                                     | 仅用于 T3CON,<br>作为定时器 3 的时间<br>时无效 | 此时通用定时器 2<br>中源。该位对于 T10   |                                       |                  |

| •        | ]        | 1                | ī                                     | 仅用于 T2CON 和<br>位对于 T1CON 以及      | 1T3CON,此时使用<br>SELT1PR=1时: |                                       | 格作为时 <b>钟源</b> 。 |

|          | TC       | LDI              | TCLD0                                 | 定时比较寄存器物                         | 复载条件                       |                                       |                  |

|          |          | 0                | 0                                     | 计数寄存器值为(                         | )                          |                                       |                  |

| Bit3-2   | ,        | 0                | 1                                     | 计数寄存器值为(                         | ) 或等于定时周期智                 | 寄存器的值                                 |                  |

|          | 1        | 1                | 0                                     | 立即                               |                            |                                       |                  |

|          |          | 1                | 1                                     | 保留                               |                            |                                       |                  |

| Bit 1    | 1        | ECMPR            | 0                                     | 关闭比较操作                           |                            |                                       |                  |

|          | (定时      | 比较使能)            | 1                                     | 使能比较操作                           |                            | <u></u>                               |                  |

| BitO     | SE       | LTIPR            | 0                                     | 使用自己的周期者                         | 8存器                        | <u></u> -                             |                  |

|          | (选择》     | 前期寄存器)<br>—————— | 1                                     | 以TIPR作为自己                        | 的周期寄存器                     | <u> </u>                              |                  |

|          |          | į                | 庚3.4 通月                               | 定时控制器 GPTC                       | ON 的定义与说                   | 明                                     |                  |

| 位        |          | 定                | · · · · · · · · · · · · · · · · · · · |                                  | 说                          | 明                                     |                  |

| p)       |          | T3STAT           |                                       | 通用定                              | 时器 3 采用减计数                 | (模式                                   | ·                |

| Bits 15  | ·        | (只读)             |                                       | 通用定                              | 时器 3 采用增计数                 | (模式                                   |                  |

| T)' -    | ,        | T2STAT           |                                       | 通用定                              | 时器 2 采用减计数                 | <br>(模式                               |                  |

| Bits14   | *        | (只读)             |                                       | 通用定                              | 时器 2 采用增计数                 | 模式                                    |                  |

|          |          |                  | _ — -                                 | · — ·                            |                            | <del></del>                           |                  |

| 位          | 定       | 义      | 说明                   |

|------------|---------|--------|----------------------|

| Bits13     | TISTAT  | 0      | 通用定时器 1 采用减计数模式      |

| DITS13     | (只读)    | 1      | 通用定时器 1 采用增计数模式      |

|            | T3ADC1  | T3ADC0 | 由通用定时器 3 的事件启动 A/D   |

|            | 0       | 0      | 不启动                  |

| Bits12-11  | 0       | 1      | 下溢出                  |

|            | 1       | 0      | 周朔匹配                 |

|            | 1       | 1      | 比较匹配                 |

|            | T2ADC1  | T2ADC0 | 由通用定时器 2 的事件启动 A/D   |

|            | 0       | 0      | 不启动                  |

| Bits10-9   | 0       | 1      | 下溢出                  |

|            | 1       | 0      | 周期匹配                 |

| · <u> </u> | 1       | 1      | 比较匹配                 |

|            | T1ADC1  | T1ADC0 | 由通用定时器 1.的事件启动 A/D   |

|            | 0       | 0      | 不启动                  |

| Bits8-7    | 0       | 1      | 下溢出                  |

|            | 1       | 0      | 周期匹配                 |

|            | 1       | 1      | 比较匹配                 |

|            | TOOLODO | 0      | 关闭三个通用定时器的比较输出       |

| Bits6      | тсомРое | 1      | 使能 (开启) 三个通用定时器的比较输出 |

|            | T3PIN1  | T3PIN0 | 通用定时器 3 比较輸出引脚的极性    |

|            | 0       | 0      | 强迫低                  |

| Bits5-4    | 0       | 1      | 低有效                  |

|            | i       | 0      | 高有效                  |

|            | 1       | 1      | 張迫高                  |

|            | T2PIN1  | T2PIN0 | 通用定时器 2 比较输出引脚的极性    |

|            | 0       | 0      | 强迫低                  |

| Bits3-2    | 0       | 1      | 低有效                  |

|            | 1       | 0      | 高有效                  |

|            | 1       | 1      | <b>强迫高</b>           |

|            | TIPINI  | T1PIN0 | 通用定时器 1 比较輸出引脚的极性    |

|            | 0       | 0      | 强迫低                  |

| Bits1-0    | 0       | 1      | 低有效                  |

|            | 1       | 0      | 高有效                  |

|            | 1       |        | <u> </u>             |

设 F, 是 CPU (机器) 时钟的频率,则定时时间 T 的计算公式为:

式中分频系数按 TxCON 中的 TPS2:1:0 取值,脉冲数与定时周期寄存器的值或定时比较寄存器的值有关, $F_c$ 的计算参照 2.7。

每个通用定时器有6种计数模式;

- ●停止/保持模式。

- ●单增计数模式。

- ●连续增计数模式。

- ●定向增/减计数模式。

- ●单增/减计数模式。

- ●连续增/减计数模式。

下面先讨论通用定时器 6 种计数模式的基本功能,即"定时"功能;然后讨论通用定时器的比较输出功能与 PWM 调制技术的实现方法。

- 1. 模式 0: 停止/保持 在这种模式下,通用定时器停止操作并保持当前状态,计数寄存器、比较输出和分频系数都保持不变。

- 2. 模式 1: 单增计数模式 在这种模式下,通用定时器的计数寄存器记录输入时钟的脉冲个数,直到计数寄存器的值与周期寄存器的值匹配为止。发生周期匹配后将继续完成下述工作:

- ●匹配之后的下一个输入时钟的上升沿,计数寄存器复位为零并且定时控制寄存器 Tx-CON 的使能位 Tenable 被清 0, 停止计数操作;

- ●匹配之后的下一个 CPU 时钟周期,周期匹配中断标志置位,如果通用控制寄存器 GPT-CON 规定该定时器的周期匹配事件启动 A/D 转换器,那么在设置周期匹配中断标志的同时,发送 A/D 转换器启动信号;

- ●匹配之后的下两个 CPU 时钟周期,定时器的下溢中断标志置位,如果通用控制寄存器

GPTCON 规定该定时器的下溢事件启动 A/D 转换器,那么在设置下溢中断标志的同时,发送 A/D 转换器启动信号。

图 3.3 反映了通用定时器单增计数模式下的工作过程。

如果计数寄存器的初始值大于周期寄存器的值,计数寄存器首先从初始值计数到 FFFFh,并产生上溢中断标志;然后复位为零,再重新计数至与周期寄存器的值匹配,周期匹配之后的工作与前面所述一致。

如果计数寄存器的初始值等于周期寄存器的值,定时器将立即产生周期匹配,其后的工作同前所述。

在单增计数模式下,计数方向始终是增,引脚

图 3.3 通用定时器单增计数模式 下的工作过程

TMRDIR 不起作用,通用控制寄存器 GPTCON 中计数方向指示位 TxSATA 是 1。一个单增计数周期所计的脉冲数为 (TxPR+1)。在该模式下,如果要产生连续的定时事件,就要在发生周期匹配后,通过软件使定时控制寄存器 TxCON 的使能位 Tenable 置 1,重新开始下一次的计数操作。

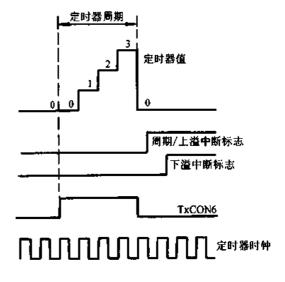

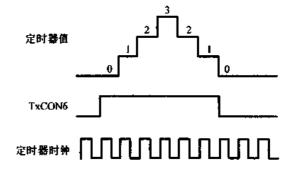

3. 模式 2: 连续增计数模式 单增计数模式的连续重复就是连续增计数模式。在这种模式下, 计数寄存器不断计数, 并与定时周期寄存器进行匹配, 一旦匹配就像单增计数模式一样对相应的中断标志进行置位, 计数寄存器复位为 0, 然后重新开始下一次计数周期。每个计数周期的脉冲数为 TxPR+1。图 3.4 反映了通用定时器连续增计数模式下的工作过程。

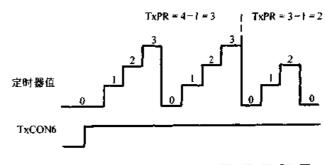

在连续增计数模式下,可以改变定时周期寄存器的值,以得到不同的周期信号。但要记住,对定时周期寄存器值的修改是对它的缓冲寄存器进行的,要将它装载到工作寄存器需在计数寄存器复位为 0 的时刻,这个装载是自动完成的。

连续增计数模式下的周期匹配、下 溢和上溢中断标志的置位,以及对 A/D 转换的启动操作都与单增计数模式下相

定时器时钟几几几几几几几几几几几

图 3.4 通用定时器连续增计数模式下的工作过程

同。在连续增计数模式下,引脚 TMRDIR 同样不起作用。通用定时器的连续增计数模式特别适用于产生边沿触发或异步 PWM 波形,以及实现定时采样、定时显示、定时轮寻等控制方式。

4. 模式 3: 定向增/减计数模式 在定向增/减计数模式下,由引脚 TMRDIR 来规定是增计数还是减计数。当引脚 TMRDIR 为高电平时,计数寄存器进行增计数;当引脚 TMRDIR 为低电平时,计数寄存器进行减计数。定向增/减计数模式特别适用于位置控制,如步进马达的控制、伺服控制等。以增计数代表前进方向,以减计数代表后退方向,以脉冲数表示位移量,这样一来就完全决定了位置的状况。

对于通用定时器 1 和通用定时器 3, 其定向增/减计数模式的操作有如下特点:

- ●只要引脚 TMRDIR 为低电平, 计数寄存器的值不断减 1, 并与 0000h 进行比较, 一旦 匹配即产生下溢出事件。随后, 计数寄存器保持原值。

- ●只要引脚 TMRDIR 为高电平而且计数寄存器的初始值小于或等于定时周期寄存器的值,计数寄存器的值不断增 1,并与定时周期寄存器的值进行比较。一旦与定时周期寄存器的值发生匹配,将产生周期匹配事件。随后,计数寄存器保持原值。

- ◆只要引脚 TMRDIR 为高电平而且计数寄存器的初始值大于定时周期寄存器的值,计数寄存器的值不断增 1,并与 FFFFh 进行比较。一旦与 FFFFh 发生匹配,将产生上溢事件。随后,计数寄存器保持原值。

- ●引脚 TMRDIR 电平改变引起计数方向的改变需要延迟两个 CPU 时钟周期。引脚 TM-RDIR 的电平状态会在通用定时控制寄存器 GPTCON 中的方向指示位 TxSATA 得到反映、1表示增计数; 0表示减计数。

- ●由于是由引脚 TMRDIR 来规定当前是增计数还是减计数。因此,当引脚 TMRDIR 为高

电平而且计数寄存器的值还未达到定时周期寄存器的值或 FFFFh 时,将引脚 TMRDIR 变为低电平,这时将进行减计数,定时器将不会发生周期匹配或上溢出事件。类似的道理,也有可能不发生下溢出事件。

●周期匹配、下溢和上溢所产生的中断标志,以及相关的操作都与单增计数模式相同。

通用定时器 2 的定向增/减计数模式工作过程与通用定时器 1 或通用定时器 3 的定向增/减计数模式的基本一样。只是在增计数过程中,当与定时周期寄存器的值发生匹配后(产生周期匹配事件),若引脚 TMRDIR 仍为高电平,将还会继续进行增计数,不在定时周期寄存器的值上停留。因此,通用定时器 2 的定向增/减计数模式工作过程是在上溢与下溢之间滚动。这样设计通用定时器 2 的定向增/减计数模式工作过程,主要是为了适应正交编码脉冲电路的工作(参见 3. 1. 4)。图 3. 5 反映了通用定时器定向增减计数模式的工作过程。

图 3.5 通用定时器定向增减计数模式的工作过程

5. 模式 4: 单增/减计数模式 在这种模式下,通用定时器的计数寄存器由初始值增计数至定时周期寄存器的值,然后改变计数方向进行减计数至 0 为止。当计数至 0 时,定时控制寄存器 TxCON 的使能位 Tenable 被清 0,停止计数操作,保持当前状态。

如果计数寄存器的初始值大于定时周期寄存器的值时,计数寄存器先计数至 FFFFh 再复位为 0,然后由 0 增计数至定时周期寄存器的值,然后改变计数方向进行减计数至 0 为止。

周期匹配、下溢和上溢所产生的中断标志,以及相关的操作都与单增计数模式相同,并且引脚 TMRDIR 不起作用。如果计数寄存器的初始值为 0,则其计数周期为 2× (TxPR) 个时钟周期。在完成一次单增/减计数过程后,可通过软件使定时控制寄存器 TxCON 的使能位置位 Tenable 置 1,重新开始下一次的单增/减计数模式的工作过程。

图 3.6 通用定时器单增/减计数模式的工作过程

6. 模式 5; 连续增/减计数模式 单增/减计

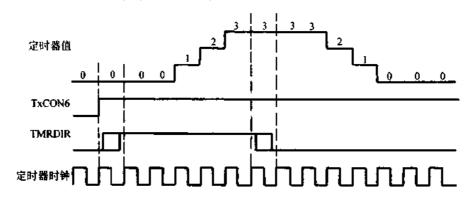

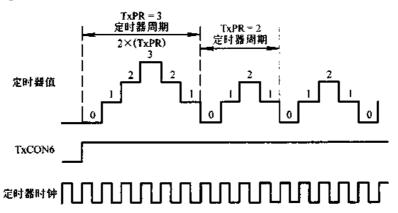

数模式的重复操作就是连续增/减计数模式。在这种操作模式下,一旦计数开始无需软件或硬件干涉,计数寄存器从 0 增计数到定时周期寄存器值,然后减计数至 0,周而复始。在循环计数的过程中,可以改变定时周期寄存器的值,但需到计数寄存器为 0 时才会生效。定时器周期是 2× (TxPR) 个输入时钟周期。

如果计数寄存器最开始的值大于定时周期寄存器的值,则先计数至 FFFFh,然后溢出到 0,再周而复始地从 0 到定时周期寄存器值再到 0。如果计数寄存器最开始的值等于定时周期寄存器的值,则先减计数至 0,再周而复始地从 0 到定时周期寄存器值再到 0。

在循环计数的过程中,产生周期匹配、上溢、下溢等中断标志,以及相关的操作与单增 计数模式一样。在该模式下,引脚 TMRDIR 不起作用。图 3.7 反映了通用定时器连续增/减 计数模式的工作过程。

图 3.7 通用定时器连续增/减计数模式的工作过程

连续增/减计数模式适用于产生对称的PWM 波形,该波形广泛应用于运动控制系统和电力电子等电器设备中。

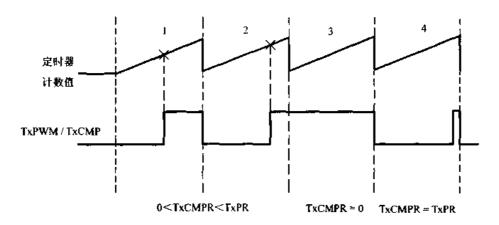

7. 调制技术的基本实现原理 前面讨论了通用定时器六种计数模式,它的最基本的功能是产生 "定时"事件,通过改变定时周期寄存器的值可以得到不同的定时时间,除了周期匹配这种 "定时"事件外,还有上溢、下溢事件可利用。这一些都比普通的微处理器的通用定时器的功能要强。但是,对于 DSP 控制器上述功能仅仅是其中的一部分。由于 DSP 控制器的通用定时器都有一个相关的比较寄存器 TxCMPR 和一个输出引脚 TxPWM/TxCMP,因此可以利用它们做成波形发生器。

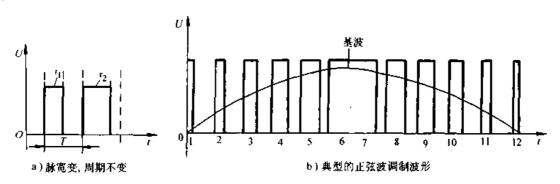

在数字控制系统中,无论采用什么样的控制方案、最终都需要将数字的控制策略转化成模拟信号以控制外部对象。由于目前大部分功率器件都是开关型器件,因此这种转化过程最常用的一种方法就是采用脉宽调制(PWM)技术,将数字量调制成满足控制策略的各种波形、最后施加到被控对象上。调制技术的核心就是产生周期不变但脉宽可变的信号。周期不变意味着以同样的调制频率工作,脉宽可变意味着可以得到不同的波形。脉宽应该以一种什么规律变化才能得到满足控制策略的波形,这不是本书要讨论的问题(有兴趣的读者可参考有关控制方面的书籍),本书假定已得到脉宽变化的规律,问题是怎样去实现它?

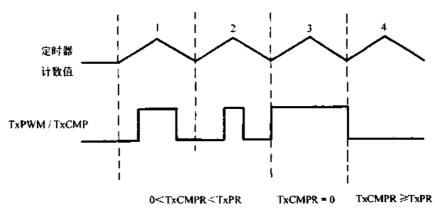

从前面简单的叙述知,调制波形是一系列周期信号,但每个周期中的脉宽是不同的。为了产生这种波形,可以想像需要两种事件:周期匹配与比较匹配。周期匹配保证调制波形的周期不变,比较匹配产生不同的脉宽。因此,根据调制频率来设置定时周期寄存器的值;根据已得到的脉宽变化规律在每个周期内修改定时比较寄存器的值,以得到不同的脉宽。图 3.8 是调制技术的原理图。

前面探讨了调制技术实现的原理,下面具体研究 DSP 控制器的通用定时器是怎样产生调制波形的。要从通用定时器的输出引脚 TxPWM/TxCMP 产生输出信号,必须首先将定时控

制寄存器 TxCON 的 TECMPR 位置 1.以及通用定时控制寄存器 GPTCON 的 TCOMPOE 位置 1.使能(开启)通用定时器的比较输出操作。另外、要对通用定时控制寄存器 GPTCON 的 TxPIN1 和 TxPIN0 进行设置,以规定当发生比较匹配事件时引脚 TxPWM/TxCMP 应处于何种极性(参见表 3.4)。

图 3.8 调制技术的原理图

通用定时器的定时比较寄存器 TxCMPR 是一个有特殊意义的寄存器,无论在何种计数模式下,计数寄存器的值总是与定时比较寄存器的值进行比较,当它们相等时,便发生比较匹配事件,并且产生以下相关操作:

- ●在匹配后的 2 个 CPU 时钟,将中断标志寄存器 EVIFRA 和 EVIFRB 中的比较中断标志位 TxCINT 置位。

- ●如果通用定时器不处于定向增/减计数模式,并且定时控制寄存器 TxCON 的 TECMPR 位置 1,那么在匹配后的一个 CPU 时钟周期,根据通用定时控制寄存器 GPTCON 的 TxPIN1 和 TxPIN0 设置的情况,相关的引脚 TxPWM/TxCMP 上将发生跳变。如果 TxPIN1 和 TxPIN0 设置为"低有效",则在比较匹配发生前引脚 TxPWM/TxCMP 为高电平(无效),发生比较匹配后引脚 TxPWM/TxCMP 跳变为低电平(有效);如果设置为"高有效",其结果与"低有效"相反;如果设置为"强制低",则无论比较匹配发生前引脚 TxPWM/TxCMP 是何种电平,发生比较匹配后引脚 TxPWM/TxCMP 都被强制为低电平;如果设置为"强制高",其结果与"强制低"相反。

- ●如果通用定时控制寄存器 GPTCON 的 TxADC1 和 TxADC0 位允许比较匹配事件启动 A/D 转换,那么当比较中断标志位置位的同时将产生 A/D 转换的启动信号。

- ●如果比较中断标志未被屏蔽,且同组中没有其它更高优先级的中断被挂起,则由比较中断标志产生的中断请求被送至 CPU。

- ●如果通用定时器处于连续计数模式,则引脚 TxPWM/TxCMP 输出连续的信号;如果通用定时器处于单计数模式,则引脚 TxPWM/TxCMP 只发生一次跳变。

出现下列情况时,通用定时器的输出引脚 TxPWM/TxCMP 被置成高阻状态:

- ●通用定时控制寄存器 GPTCON 的 TCOMPOE 位被置为 0;

- ●引脚 PDPINT (电源保护中断) 置为低电平且该中断未屏蔽;

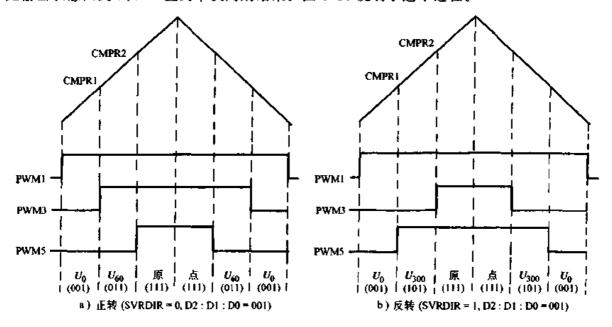

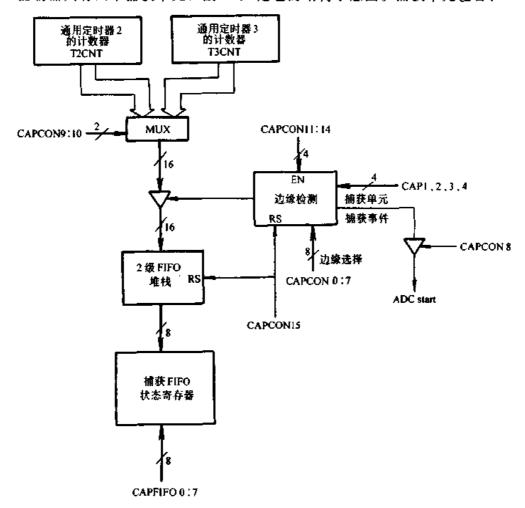

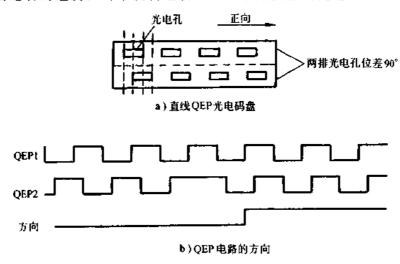

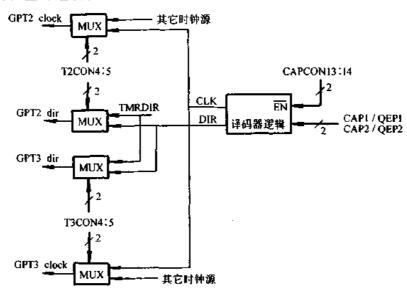

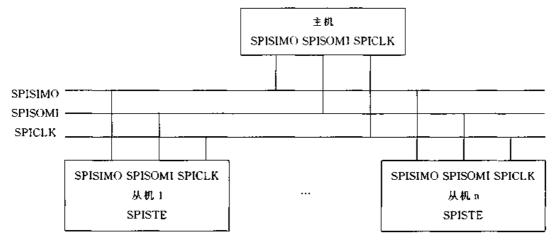

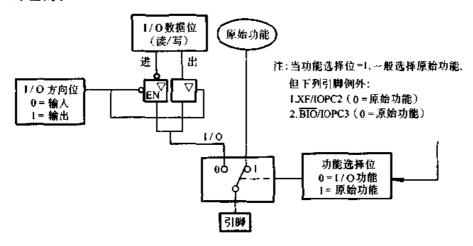

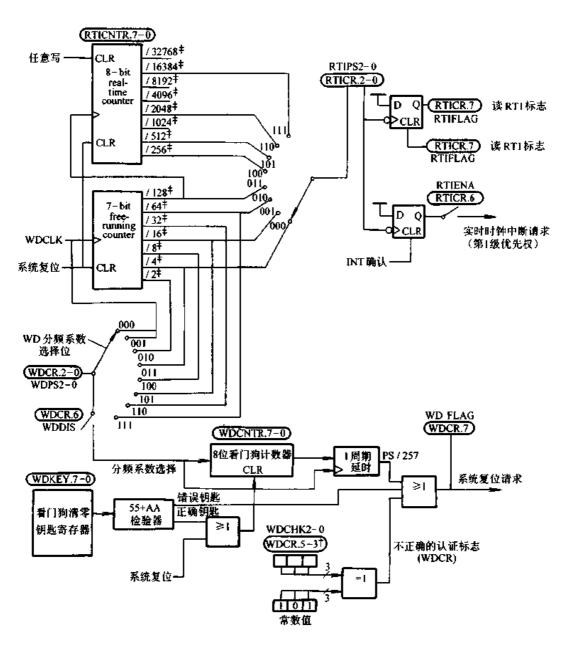

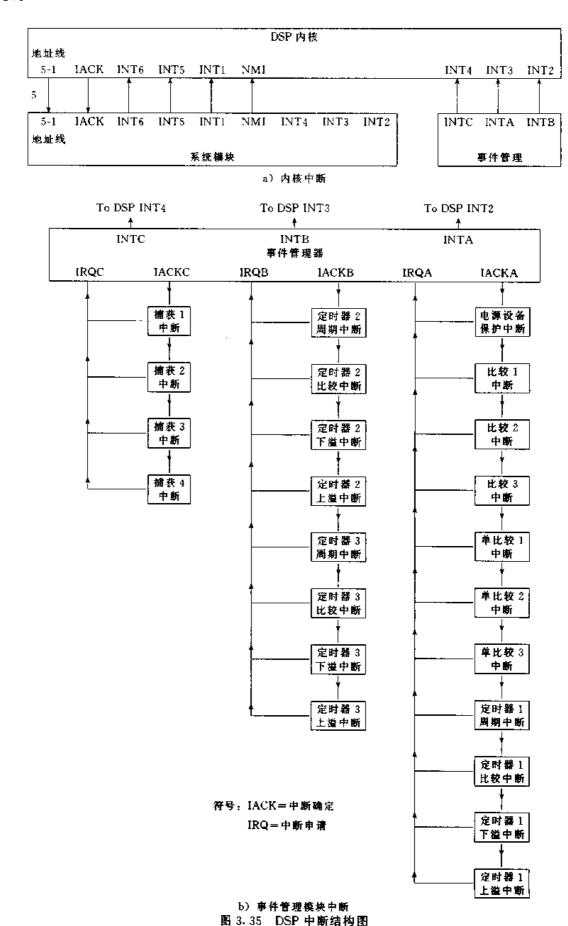

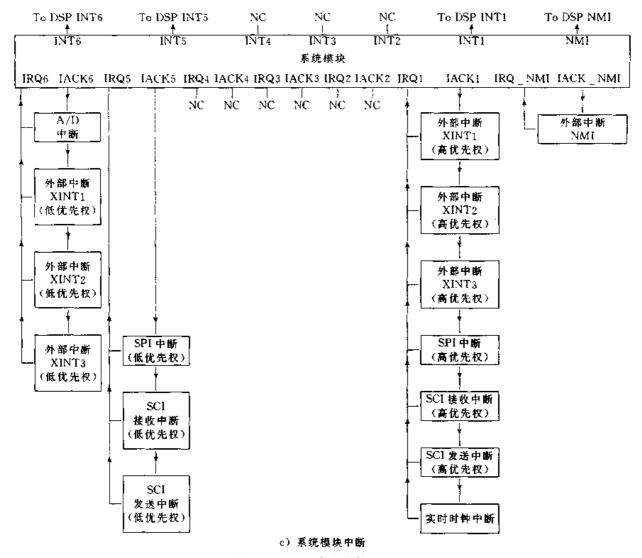

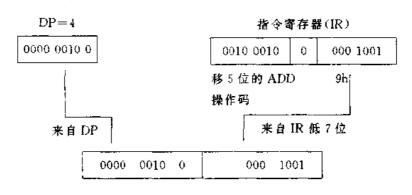

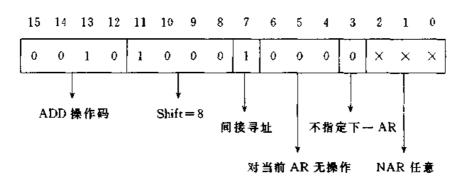

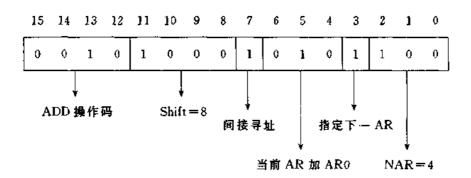

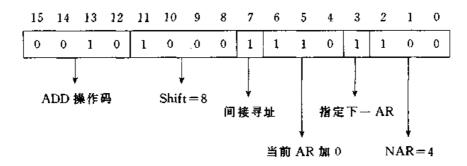

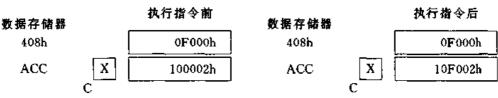

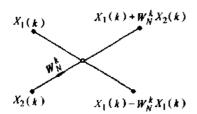

- ●系统复位。