## Data International Co., Ltd.

## APPROVAL SHEET

| Customer    | : |               |

|-------------|---|---------------|

| Part Name   | : | LCD MODULE    |

| Model No.   | : | DG-12864-S2RB |

| Drawing No. | : |               |

| Approved by | : |               |

| Date        | : |               |

| Approved | Checked | Prepared     | Sheet Code: |

|----------|---------|--------------|-------------|

|          |         | Jia-Huei Liu | 3115100050  |

5F, No. 25, Lane, 169, Kang-Ning Street., His Chin Chen, Taipei Hsien, Taiwan (R.O.C.)

Tel: 886-2-26950959

Fax: 886-2-26958620

## **CONTENTS**

| 1. | SCO | PE                                               | <br>3  |

|----|-----|--------------------------------------------------|--------|

| 2. | PRO | DUCT SPECIFICATIONS                              | <br>3  |

|    | 2.1 | General                                          | <br>3  |

|    | 2.2 | Mechanical Characteristics                       | <br>3  |

|    | 2.3 | Absolute Maximum Ratings                         | <br>4  |

|    | 2.4 | Electrical Characteristics                       | <br>4  |

|    | 2.5 | Optical Characteristics Absolute maximum ratings | <br>5  |

|    | 2.6 | Optical Characteristics                          | <br>5  |

| 3. | REL | IABILITY                                         | <br>8  |

| 4. | OPE | RATING INSTRUCTIONS                              | <br>9  |

|    | 4.1 | Input signal Function                            | <br>9  |

|    | 4.2 | Circuit Block Diagram                            | <br>10 |

|    | 4.3 | Voltage Generator Circuit                        | <br>11 |

|    | 4.4 | Timing Characteristics                           | <br>12 |

|    | 4.5 | Operating Principles & Methods                   | <br>14 |

|    | 4.6 | Display control instruction                      | <br>16 |

|    | 4.7 | Application circuit                              | <br>18 |

| 5. | NOT | ES                                               | <br>21 |

| 6. | OPE | RATION PRECAUTIONS                               | <br>21 |

| 7. | LCM | I DIMENSIONS                                     | <br>22 |

DATA VISION 00/02/11 2 / 22

### 1. SCOPE

This specification covers the engineering requirements for the DG-12864-S2RB liquid crystal module.

### 2. PRODUCT SPECIFICATIONS

#### 2.1 General

- $128 \times 64$  dot matrix LCD

- STN (Gray), Positive mode LCD panel

- Reflective, Normal temperature type

- 6 o'clock

- Multiplexing driving: 1/64duty, 1/9bias

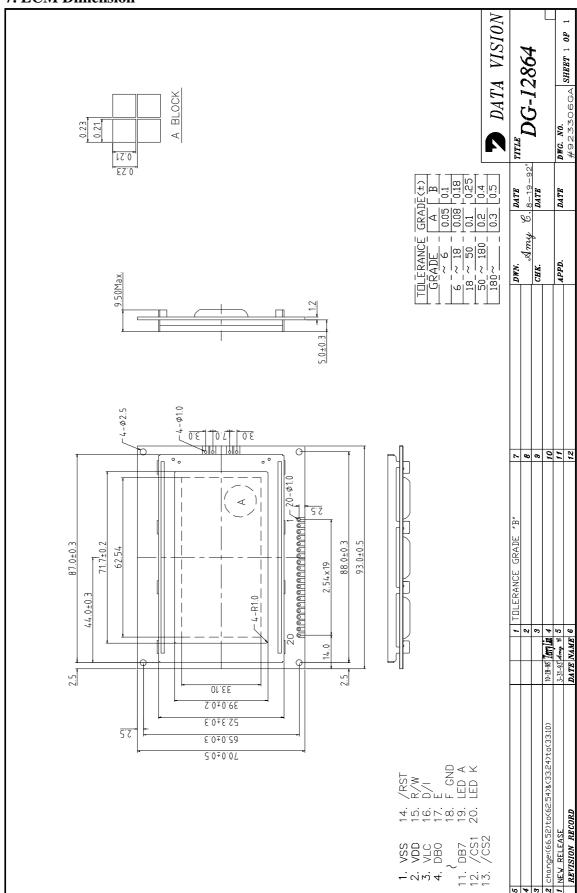

#### 2.2 Mechanical Characteristics

| Item                                                      | Characteristic                     |

|-----------------------------------------------------------|------------------------------------|

| Dot configuration                                         | 128 × 64                           |

| Dot dimensions(mm)                                        | $0.21 \times 0.21$                 |

| Dot spacing (mm)                                          | 0.02                               |

| Module dimensions (Horizontal × Vertical × Thickness, mm) | $93.0 \times 70.0 \times 9.5$ max. |

| Viewing area (Horizontal × Vertical, mm)                  | $71.7 \times 39.0$                 |

| Active area (Horizontal × Vertical, mm)                   | 62.54 × 33.10                      |

DATA VISION 00/02/11 3 / 22

### 2.3 Absolute Maximum Ratings (Without LED back-light)

#### **MAXIMUM ABSOLUTE LIMIT**

| Characteristic        | Symbol           | Value                                      | Unit | Note |

|-----------------------|------------------|--------------------------------------------|------|------|

| Operating Voltage     | $V_{DD}$         | -0.3~+7.0                                  | V    | *1   |

| Supply Voltage        | $V_{EE}$         | V <sub>DD</sub> -19.0~V <sub>DD</sub> +0.3 | V    | *4   |

| Driver Supply Voltage | V <sub>B</sub>   | -0.3~V <sub>DD</sub> +0.3                  | V    | *1,2 |

|                       | $V_{LCD}$        | V <sub>EE</sub> -0.3~V <sub>DD</sub> +0.3  | V    | *3,4 |

| Operating Temperature | T <sub>OPR</sub> | -30~+85                                    | °C   | -    |

| Storage Temperature   | T <sub>STG</sub> | -55~+125                                   | °C   | -    |

## 2.4 Electrical Characteristics (Without LED back-light)

#### **ELECTRICAL CHARACTERISTICS**

DC Characteristics ( $V_{DD}$ =+5V ±10%,  $V_{SS}$ =0V,  $|V_{DD}$ -V<sub>EE</sub> |=8~17V,  $T_a$ = -30 ~ +85°C)

| Char      | acteristic             | Symbol           | condition                                                         | Min                  | Тур | Max                | Unit | Note |

|-----------|------------------------|------------------|-------------------------------------------------------------------|----------------------|-----|--------------------|------|------|

| Input     | High                   | V <sub>IH</sub>  | -                                                                 | $0.7V_{DD}$          | -   | $V_{DD}$           | V    | *1   |

| Voltage   | Low                    | V <sub>IL</sub>  |                                                                   | V <sub>SS</sub>      | -   | 0.3V <sub>DD</sub> | ]    |      |

| Output    | High                   | V <sub>OH</sub>  | I <sub>OH</sub> =-0.4 mA                                          | V <sub>DD</sub> -0.4 | -   | -                  | V    | *2   |

| Voltage   | Low                    | V <sub>OL</sub>  | I <sub>OL</sub> =0.4 mA                                           | -                    | -   | 0.4                |      |      |

| Input Lea | akage Current          | I <sub>LKG</sub> | $V_{IN}=V_{DD}\sim V_{SS}$                                        | -1.0                 | -   | 1.0                | μΑ   | *1   |

| OSC       | Frequency              | f <sub>osc</sub> | Rf=47 k $\Omega$ ± 2%<br>Cf=20pf ± 5%                             | 315                  | 450 | 585                | KHz  |      |

|           | tesistance<br>/div-Ci) | R <sub>ON</sub>  | V <sub>DD</sub> -V <sub>EE</sub> =17V<br>Load current =<br>±150µA | -                    | -   | 1.5                | kΩ   |      |

| Opera     | ting Current           | I <sub>DD1</sub> | Master mode<br>1/128 Duty                                         | -                    | -   | 1.0                | mA   | *3   |

|           |                        | I <sub>DD2</sub> | Slave mode<br>1/128 Duty                                          | -                    | -   | 200                | μА   | *4   |

| Supp      | ly Current             | I <sub>EE</sub>  | Master mode<br>1/128 Duty                                         | -                    | -   | 100                |      | *5   |

| Op        | perating               | f <sub>op1</sub> | Master mode<br>External clock                                     | 50                   | -   | 600                | KHz  |      |

| Fre       | equency                | f <sub>op2</sub> | Slave mode                                                        | 0.5                  | -   | 1500               | 1    |      |

<sup>\*1.</sup> Applies to input terminals FS, DS1, DS2, CR, SHL, MS and PCLK2 and I/O terminals DIO1, DIO2, M and CL2 in the input state.

DATA VISION 00/02/11 4 / 22

<sup>\*2.</sup> Applies to output terminals CLK1, CLK2 and FRM and I/O terminals DIO1, DIO2, M and CL2 in the output state.

<sup>\*3.</sup> This value is specified at about the current flowing through V<sub>SS</sub>. Internal oscillation circuit: Rf=47 kΩ, Cf=20 pF

Each terminal of DS1, DS2, FS, SHL and MS is connected to VDD and out is no load.

<sup>\*4.</sup> This value is specified at about the current flowing through V<sub>SS</sub>. Each terminal of DS1, DS2, FS, SHL, PCLK2 and CR is connected to V<sub>DD</sub>, and MS is connected to V<sub>SS</sub> CL2, M, DIO1 is external clock.

<sup>\*5.</sup> This value is specified at about the current flowing through V<sub>EE</sub>. Don't connect to V<sub>LCD</sub> (V1~V5).

## 2.5 Optical Characteristics Absolute maximum ratings

| Item                        | Symbol | Rating | Unit |

|-----------------------------|--------|--------|------|

| Applied voltage AC          | VAC    | 15     | V    |

| Operating temperature range | Тор    | 0~50   | °C   |

| Storage temperature range   | Tst    | -20~60 | °C   |

## 2.6 Optical Characteristics

1/64 duty, 1/9 bias

| Item            | Symbol          | Temp. | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|-------|------|------|------|------|

|                 |                 | 0°C   | 12.1 | 12.8 | 13.5 |      |

| Driving voltage | Vop             | 25 °C | 11.3 | 12.0 | 12.7 | V    |

| voltage         |                 | 50°C  | 10.4 | 11.1 | 11.8 |      |

| Contrast        | K               | θ=0°  | 2    | 2.7  |      |      |

| Contrast        | IX.             | φ=0°  | 2    | 2.7  |      |      |

| Frame freq.     | fF              |       |      | 70   |      | Hz   |

| Viewing         | $\theta_1$      |       | -35  |      | 40   | deg. |

| angle*          | $\theta_2$      | 25°C  | -35  |      | 35   | ucg. |

| Response        | t <sub>on</sub> | 25°C  |      | 140  | 210  | ms   |

| time            | $t_{\rm off}$   | 23 C  |      | 220  | 330  | 1115 |

DATA VISION 00/02/11 5 / 22

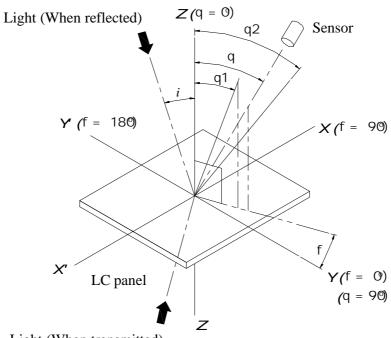

## 2.6.1 Definition of optical characteristics

\* Definition of angles  $\phi$  and  $\theta$

## Light (When transmitted)

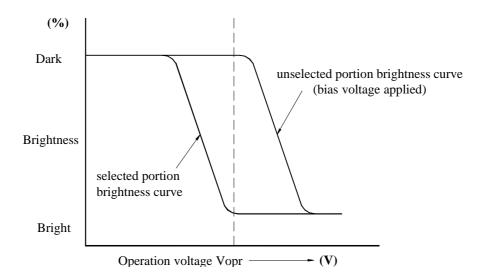

### \*Definition of contrast C

$$C = \frac{B1}{B2} = \frac{\text{Brightness of selected portion}}{\text{Brightness of unselected portion}}$$

DATA VISION 00/02/11 6 / 22

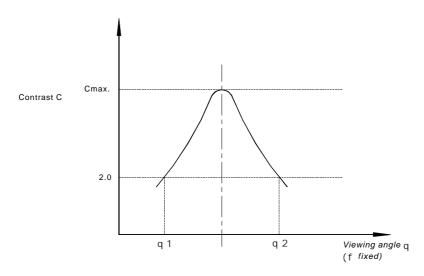

## \* Definition of viewing angles $\theta 1$ and $\theta 2$

Note : Optimum vision with the naked eye and viewing angle  $\theta$  at Cmax above are not always the same.

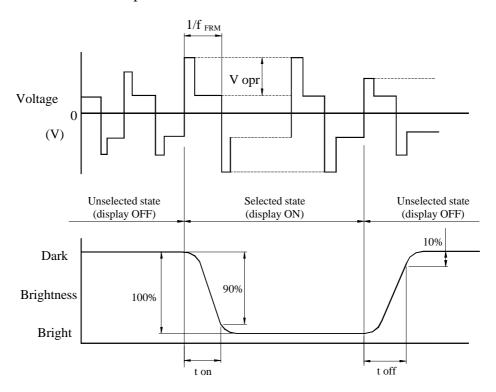

## \* Definition of response time

Vopr : Operating voltage (V) ton : Response time (rsie) (ms)

fFRM : Frame frequency (Hz) toff : Response time (fall) (ms)

DATA VISION 00/02/11 7 / 22

### 3. RELIABILITY

### 3.1 Reliability

| Test item                                  | Test condition                                                                                        | Evaluation and assessment                       |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Operation at high temperature and humidity | 40°C±2°C<br>90%RH for 500hours                                                                        | No abnormalities in functions* and appearance** |

| Operation at high temperature              | 60°C±2°C for 500 hours                                                                                | No abnormalities in functions* and appearance** |

| Heat shock                                 | -20± ~ +60 °C Left for 1<br>hour at each temperature,<br>transition time 5 min,<br>repeated 10times   | No abnormalities in functions* and appearance** |

| Low temperature                            | -20±2 °C for 500 hours                                                                                | No abnormalities in functions* and appearance** |

| Vibration                                  | Sweep for 1 min at 10 Hz,<br>55Hz, 10Hz, amplitude<br>1.5mm 2 hrs each in the<br>X,Y and Z directions | No abnormalities in functions* and appearance** |

| Drop shock                                 | Dropped onto a board from a height of 10cm                                                            | No abnormalities in functions* and appearance** |

<sup>\*</sup> dissipation current, contrast and display functions

## 3.2 Liquid crystal panel service life

100,000 hours minimum at 25 °C±10 °C

- 3.3 definition of panel service life

- Contrast becomes 30% of initial value

- Current consumption becomes three times higher than initial value

- Remarkable alignment deterioration occurs in LCK cell layer

- Unusual operation occurs in display functions

DATA VISION 00/02/11 8 / 22

<sup>\*\*</sup> Polarizing filter deterioration, other appearance defects

## 4. OPERATING INSTRUCTIONS

## 4.1 Input signal Function

| NO.  | Symbol  | Function                           |  |  |  |

|------|---------|------------------------------------|--|--|--|

| 1    | VSS     | Ground (0V)                        |  |  |  |

| 2    | VDD     | Power supply for Logic circuit (+) |  |  |  |

| 3    | V0      | Power supply for LCD               |  |  |  |

| 4    | RS      | H: Instruction L: Data             |  |  |  |

| 5    | R/W     | Read/Write                         |  |  |  |

| 6    | Е       | Enable Signal                      |  |  |  |

| 7-14 | DB0-DB7 | Data Bus Line                      |  |  |  |

| 15   | CS1     | Chip Selection For IC1             |  |  |  |

| 16   | CS2     | Chip Selection For IC2             |  |  |  |

| 17   | /RES    | Reset Active "L"                   |  |  |  |

| 18   | VEE     | Power supply for LCD (0V)          |  |  |  |

| 19   | LED 1   | Power supply for LED               |  |  |  |

| 20   | LED 2   | Power supply for LED               |  |  |  |

DATA VISION 00/02/11 9 / 22

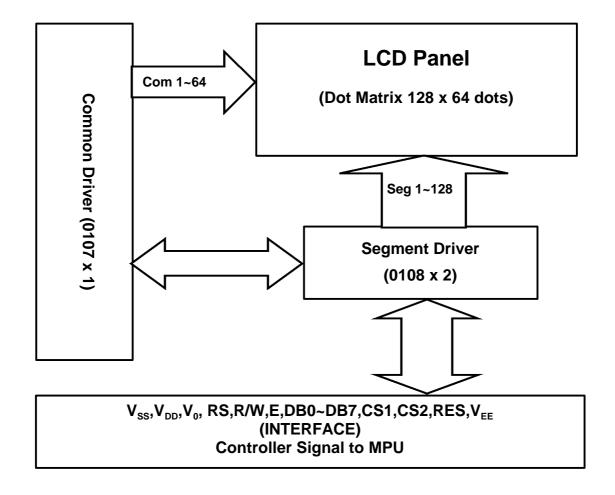

## 4.2 Circuit Block Diagram

DATA VISION 00/02/11 10 / 22

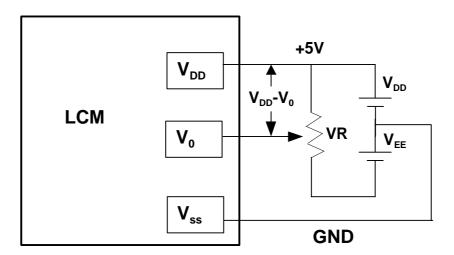

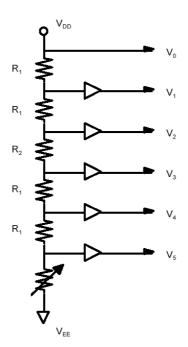

## 4.3 Voltage Generator Circuit

## **Power Supply Circuit Diagram**

$V_{DD}$  -  $V_0$  : LCD Driving Voltage VR : 10K~20K

11 / 22 DATA VISION 00/02/11

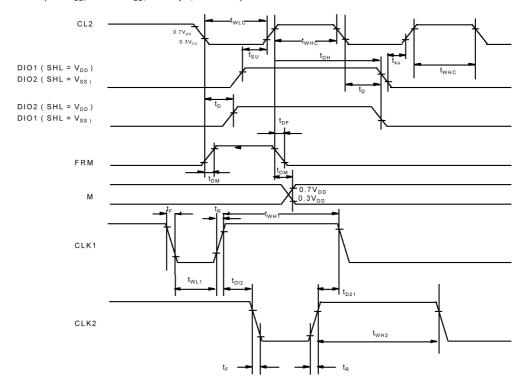

## 4.4 Timing Characteristics

AC Characteristics (VDD=5V ±10%, Ta=-30°C~+85°C)

1. Master mode (MS=V<sub>DD</sub>, PCLK2=V<sub>DD</sub>, Cf=20 pF, Rf=47 k $\Omega$ )

| Characteristic             | Symbol                         | Min  | Тур | Max | Unit |

|----------------------------|--------------------------------|------|-----|-----|------|

| Data Setup Time            | t <sub>SU</sub>                | 20   | -   | -   |      |

| Data Hold Time             | t <sub>DH</sub>                | 40   | -   | -   |      |

| Data Delay Time            | t <sub>D</sub>                 | 5    | -   | -   |      |

| FRM Delay Time             | t <sub>DF</sub>                | -2   | -   | 2   | μs   |

| M Delay Time               | t <sub>DM</sub>                | -2   | -   | 2   | ]    |

| CL2 Low Level Width        | t <sub>WLC</sub>               | 35   | -   | -   |      |

| CL2 High Level Width       | t <sub>WHC</sub>               | 35   | -   | -   |      |

| CLK1 Low Level Width       | t <sub>WL1</sub>               | 700  | -   | -   |      |

| CLK2 Low Level Width       | t <sub>WL2</sub>               | 700  | -   | -   | 1    |

| CLK1 High Level Width      | t <sub>WH1</sub>               | 2100 | -   | -   |      |

| CLK2 High Level Width      | t <sub>WH2</sub>               | 2100 | -   | -   | ns   |

| CLK1-CLK2 Phase Difference | t <sub>D12</sub>               | 700  | -   | -   | ]    |

| CLK2-CLK1 Phase Difference | t <sub>D21</sub>               | 700  | -   | -   | ]    |

| CLK1, CLK2 Rise/Fall Time  | t <sub>R</sub> /t <sub>F</sub> | -    | -   | 150 |      |

DATA VISION 00/02/11 12 / 22

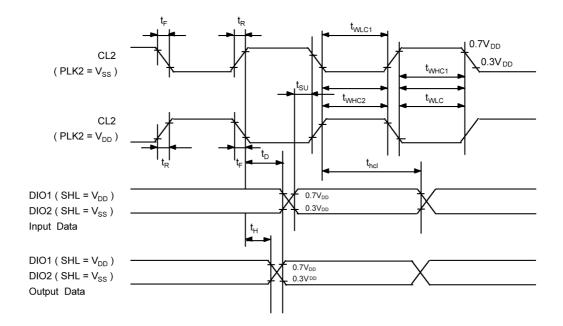

### 2. Slave mode (MS=V<sub>SS</sub>)

| Characteristics       | Symbol                         | Min | Тур | Max | Unit | Note                  |

|-----------------------|--------------------------------|-----|-----|-----|------|-----------------------|

| CL2 Low Level Width   | t <sub>WLC1</sub>              | 450 | -   | -   | ns   | PCLK2=V <sub>SS</sub> |

| CL2 High Level Width  | t <sub>WHC1</sub>              | 150 | -   | -   | ns   | PCLK2=V <sub>SS</sub> |

| CL2 Low Level Width   | t <sub>WLC2</sub>              | 150 | -   | -   | ns   | PCLK2=V <sub>DD</sub> |

| CL2 High Level Width  | t <sub>WHL</sub>               | 450 | -   | -   | ns   | PCLK2=V <sub>DD</sub> |

| Data Setup Time       | t <sub>SU</sub>                | 100 | -   | -   | ns   |                       |

| Data Hold Time        | t <sub>DH</sub>                | 100 | -   | -   | ns   |                       |

| Data Delay Time       | t <sub>D</sub>                 | -   | -   | 200 | ns   | *1                    |

| Output Data Hold Time | t <sub>H</sub>                 | 10  | -   | -   | ns   |                       |

| CL2 Rise/Fall Time    | t <sub>R</sub> /t <sub>F</sub> | -   | -   | 30  | ns   |                       |

DATA VISION 00/02/11 13 / 22

#### 4.5 Operating Principles & Methods

#### **OPERATING PRINCIPLES & METHODS**

#### 1. I/O Buffer

Input buffer controls the status between the enable and disable of chip. Unless the CS1B to CS3 is in active mode, Input or output of data and instruction does not execute. Therefore internal state is not change. But RSTB and ADC can operate regardless CS1B-CS3.

#### 2. Input register

Input register is provided to interface with MPU which is different operating frequency. Input register stores the data temporarily before writing it into display RAM.

When CS1B to CS3 are in the active mode, R/W and RS select the input register. The data from MPU is written into input register. Then Writing it into display RAM. Data latched for falling of the E signal and write automatically into the display data RAM by internal operation.

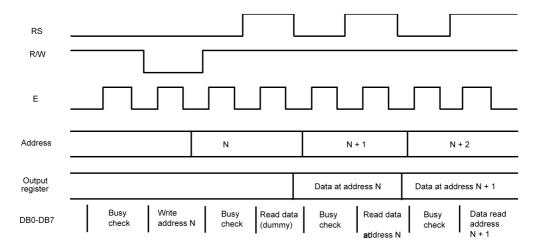

#### 3. Output register

Output register stores the data temporarily from display data RAM when CS1B, CS2B and CS3 are in active mode and R/W a RS=H, stored data in display data RAM is latched in output register. When CS1B to CS3 is in active mode and R/W=H, RS=L, status data (busy check) can read out.

To read the contents of display data RAM, twice access of read instruction is needed. In first access, data in display data RAM is latched into output register. In second access, MPU can read data which is latched. That is, to read the data in display data RAM, it needs dummy read. But status read is not needed dummy read.

| RS | R/W | Function                                             |

|----|-----|------------------------------------------------------|

| L  | L   | Instruction                                          |

|    | Н   | Status read (busy check)                             |

| Н  | L   | Data write (from input register to display data RAM) |

|    | Н   | Data read (from display data RAM to output register) |

#### 4. Reset

The system can be initialized by setting RSTB terminal at low level when turning power on, receiving instruction from MPU When RSTB becomes low, following procedure is occurred.

- 1. Display off

- 2. Display start line register become set by 0.(Z-address 0)

While RSTB is low, No instruction except status read can be accepted. Therefore, execute other instructions after making sure that DB4=0 (clear RSTB) and DB7=0 (ready) by status read instruction.

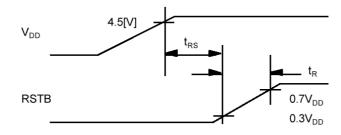

The Conditions of power supply at initial power up are shown in table 1.

Table 1. Power Supply Initial Conditions

| Item       | Symbol          | Min | Тур | Max | Unit |

|------------|-----------------|-----|-----|-----|------|

| Reset Time | t <sub>RS</sub> | 1.0 | -   | -   | us   |

| Rise Time  | t <sub>R</sub>  | 1   | 1   | 200 | ns   |

DATA VISION 00/02/11 14 / 22

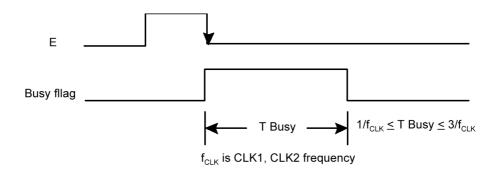

#### 5. Busy flag

Busy flag indicates that KS0108B is operating or no operating. When busy flag is high, KS0108B is in internal operating. When busy flag is low, KS0108B can accept the data or instruction. DB7 indicates busy flag of the KS0108B.

**Busy Check**

**Busy Flag**

DATA VISION 00/02/11 15 / 22

#### 6. Display On/Off Flip - Flop

The display on/off flip-flop makes on/off the liquid crystal display. When flip-flop is reset (logical low), selective voltage or non selective voltage appears on segment output terminals. When flip-flop is set (logic high), non selective voltage appears on segment output terminals regardless of display RAM data.

The display on/off flip-flop can changes status by instruction. The display data at all segment disappear while RSTB is low. The status of the flip-flop is output to DB5 by status read instruction.

The display on/off flip-flop synchronized by CL signal.

#### 7. X Page Register

X page register designates pages of the internal display data RAM. Count function is not available. An address is set by instruction.

#### 8. Y address counter

Y address counter designates address of the internal display data RAM. An address is set by instruction and is increased by 1 automatically by read or write operations of display data.

#### 9. Display Data RAM

Display data RAM stores a display data for liquid crystal display. To indicate on state dot matrix of liquid crystal display, write data 1. The other way, off state, writes 0.

Display data RAM address and segment output can be controlled by ADC signal.

ADC=H⇒ Y-address 0:S1 ~ Y address 63:S64

ADC=L⇒ Y-address 0:S64 ~ Y address 63:S1

ADC terminal connect the V<sub>DD</sub> or V<sub>SS</sub>.

#### 10. Display Start Line Register

The display start line register indicates of display data RAM to display top line of liquid crystal display.

Bit data (DB<0:5>) of the display start line set instruction is latched in display start line register. Latched data is transferred to the Z address counter while FRM is high, presetting the Z address counter.

It is used for scrolling of the liquid crystal display screen.

#### 4.6 Display control instruction

The display control instructions control the internal state of the KS0108B. Instruction is received from MPU to KS0108B for the display control. The following table shows various instructions.

| Instruction                          | RS | R/W | DB7  | DB6       | DB5         | DB4                   | DB3    | DB2                     | DB1                                                                                                                          | DB0 | Function                                                                                                |

|--------------------------------------|----|-----|------|-----------|-------------|-----------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------|

| Display ON/OFF                       | ١  | L   | L    | L         | Н           | Н                     | Н      | Н                       | Н                                                                                                                            | L/H | Controls the display on or off. Internal status and display RAM data is not affected. L:OFF, H:ON       |

| Set Address<br>(Y address)           | L  | L   | L    | Н         |             | Υa                    | ddress | (0~63)                  |                                                                                                                              |     | Sets the Y address in the Y address counter.                                                            |

| Set Page<br>( X address)             | L  | L   | Η    | L         | Н           | Н                     | Н      |                         | Page (0~7)                                                                                                                   |     | Sets the X address at the X address register.                                                           |

| Display Start<br>Line<br>(Z address) | _ا | L   | Н    | Н         |             |                       | . ,    | splay start line (0~63) |                                                                                                                              |     | Indicates the display data RAM displayed at the top of the screen.                                      |

| Status Read                          |    | Ι   | BUSY | L         | 0 N / 0 F F | R<br>E<br>S<br>E<br>T | L      | L                       | L                                                                                                                            | L   | Read status. BUSY L: Ready H: In operation ON/OFF L: Display ON H: Display OFF RESET L: Normal H: Reset |

| Write Display<br>Data                | Н  | L   |      |           | Write Data  |                       |        |                         | Writes data (DB0:7) into<br>display data RAM. After<br>writing instruction, Y<br>address is increased by<br>1 automatically. |     |                                                                                                         |

| Read Display<br>Data                 | Н  | Н   |      | Read Data |             |                       |        |                         | Reads data (DB0:7) from display data RAM to the data bus.                                                                    |     |                                                                                                         |

DATA VISION 00/02/11 16 / 22

#### 1. Display On/Off

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | D   |

The display data appears when D is 1 and disappears when D is 0.

Though the data is not on the screen with D=0, it remains in the display data RAM.

Therefore, you can make it appear by changing D=0 into D=1.

#### 2. Set Address (Y Address)

| S | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0 | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Y address (AC0 ~ AC5) of the display data RAM is set in the Y address counter.

An address is set by instruction and increased by 1 automatically by read or write operations of display data.

#### 3. Set Page (X Address)

|   | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ſ | 0  | 0   | 1   | 0   | 1   | 1   | 1   | AC2 | AC1 | AC0 |

X address(AC0 ~ AC2) of the display data RAM is set in the X address register.

Writing or reading to or from MPU is executed in this specified page until the next page is set.

#### 4. Display Start Line (Z Address)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Z address (AC0  $\sim$  AC5) of the display data RAM is set in the display start line register and displayed at the top of the screen.

When the display duty cycle is 1/64 or others(1/32 ~ 1/64), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed.

#### 5. Status Read

| RS | R/W | DB7  | DB6 | DB5    | DB4   | DB3 | DB2 | DB1 | DB0 |   |

|----|-----|------|-----|--------|-------|-----|-----|-----|-----|---|

| 1  | 0   | BUSY | 0   | ON/OFF | RESET | 0   | 0   | 0   | 0   | ٦ |

#### BUSY

When BUSY is 1, the Chip is executing internal operation and no instructions are accepted.

When BUSY is 0, the Chip is ready to accept any instructions.

#### ON/OFF

When ON/OFF is 1, the display is on.

When ON/OFF is 0, the display is off.

#### RESET

When RESET is 1, the system is being initialized.

In this condition, no instructions except status read can be accepted.

When RESET is 0, initializing has finished and the system is in the usual operation condition.

#### 6. Write Display Data

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Writes data (D0 ~ D7) into the display data RAM.

After writing instruction, Y address is increased by 1 automatically.

#### 7. Read Display Data

|   | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Г | 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Reads data (D0 ~ D7) from the display data RAM.

After reading instruction, Y address is increased by 1 automatically.

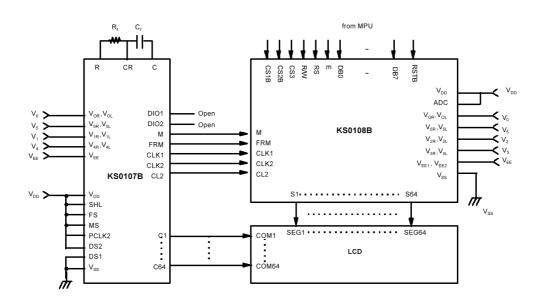

## 4.7 Application circuit

### **APPLICATION CIRCUIT**

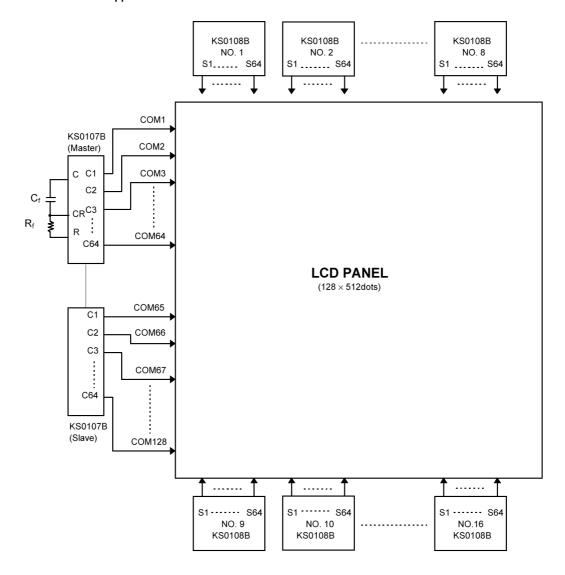

1.1/64 duty common driver(KS0107B) interface circuit

DATA VISION 00/02/11 18 / 22

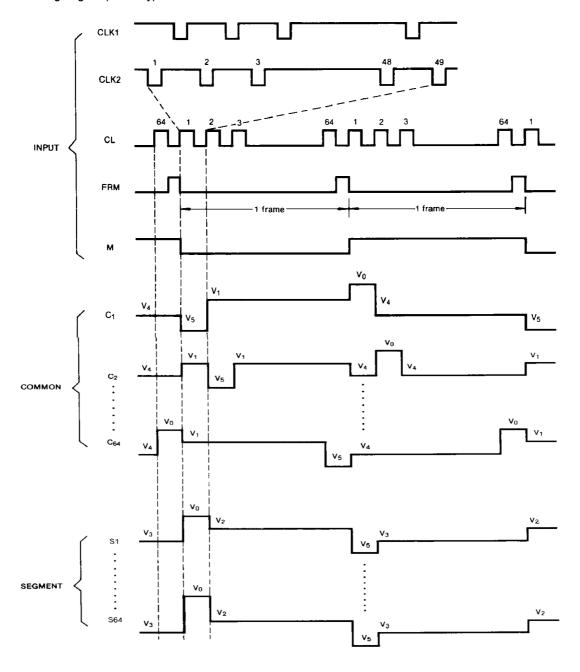

### 2. Timing diagram (1/64 duty)

DATA VISION 00/02/11 19 / 22

#### 3. LCD Panel interface application circuit

DATA VISION 00/02/11 20 / 22

#### 5. NOTES

#### <u>Safety</u>

• If the LCD panel breaks, be careful not to get the liquid crystal in your mouth. If the liquid crystal touches your skin or clothes, wash it off immediately using soap and plenty of water.

#### **Handling**

- Avoid static electricity as this can damage the CMOS LSI.

- The LCD panel is plate glass; do not hit or crush it.

- Do not remove the panel or frame from the module.

- The polarizing plate of the display is very fragile; handle it very carefully

#### Mounting and Design

- Mount the module by using the specified mounting part and holes.

- To protect the module from external pressure, leave a small gap by placing transparent plates (e.g. acrylic or glass) on the display surface, frame, and polarizing plate

- Design the system so that no input signal is given unless the power-supply voltage is applied.

- Keep the module dry. Avoid condensation, otherwise the transparent electrodes may break.

#### **Storage**

- Store the module in a dark place where the temperature is 25 °C±10 °C and the humidity below 65% RH.

- Do not store the module near organic solvents or corrosive gases.

- Do not crush, shake, or jolt the module (including accessories).

#### Cleaning

- Do not wipe the polarizing plate with a dry cloth, as it may scratch the surface.

- Wipe the module gently with soft cloth soaked with a petroleum benzine.

- Do not use ketonic solvents (ketone and acetoe) or aromatic solvents (toluene and xylene), as they may damage the polarizing plate.

#### 6. OPERATION PRECAUTIONS

Any changes that need to be made in this specification or any problems arising from it will be dealt with quickly by discussion between both companies.

DATA VISION 00/02/11 21 / 22

### 7. LCM Dimension

DATA VISION 00/02/11 22 / 22