|     | 目 录                          |

|-----|------------------------------|

| 第一  | 章 数字信号处理器发展概述                |

| 1.1 | 第一代 DSP ······(1)            |

| 1.2 | 第二代 DSP(2)                   |

| 1.3 | 第三代 DSP 及 DSP 的发展动向(3)       |

| 第二  | 章 TMS32010 系列处理器(5)          |

| 2.1 | TMS32010 概述                  |

| 2.2 | TMS32010 的硬件结构               |

| 2.3 | 寻址方式和指令系统 (13)               |

| 2.4 | TMS32010 程序设计(17)            |

| 2.5 | TMS32010 外部电路设计(24)          |

| 第三  | 章 TMS32020 系列信号处理器(36)       |

| 3.1 | TMS32020 概述                  |

| 3.2 | TMS32020 硬件结构                |

| 3.3 | TMS32020 的指令系统               |

| 3.4 | TMS32020 与外部设备接口             |

| 3.5 | TMS320C20 汇编程序设计 (61)        |

| 3.6 | TMS320C25 处理器 ······ (67)    |

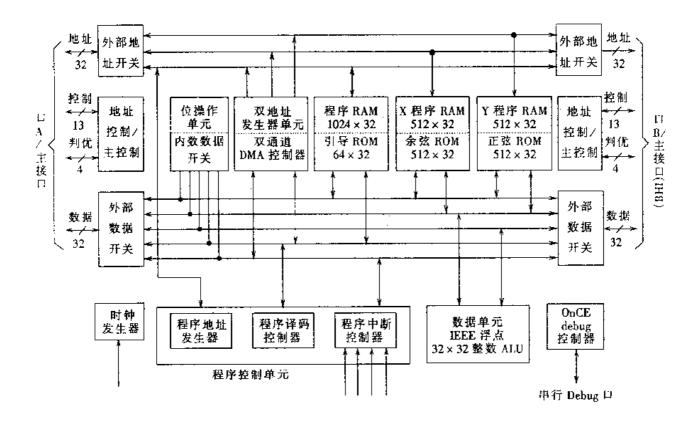

| 第四: | 章 TMS320C50 及其它常用 DSP(80)    |

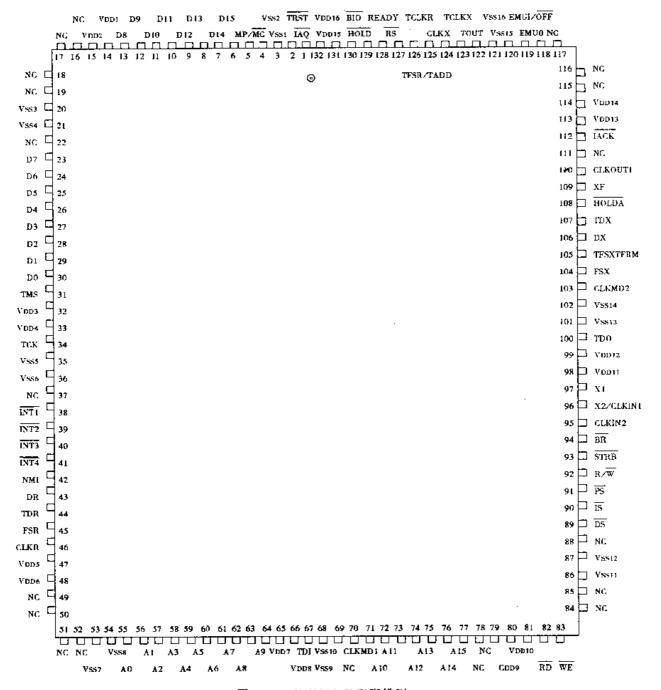

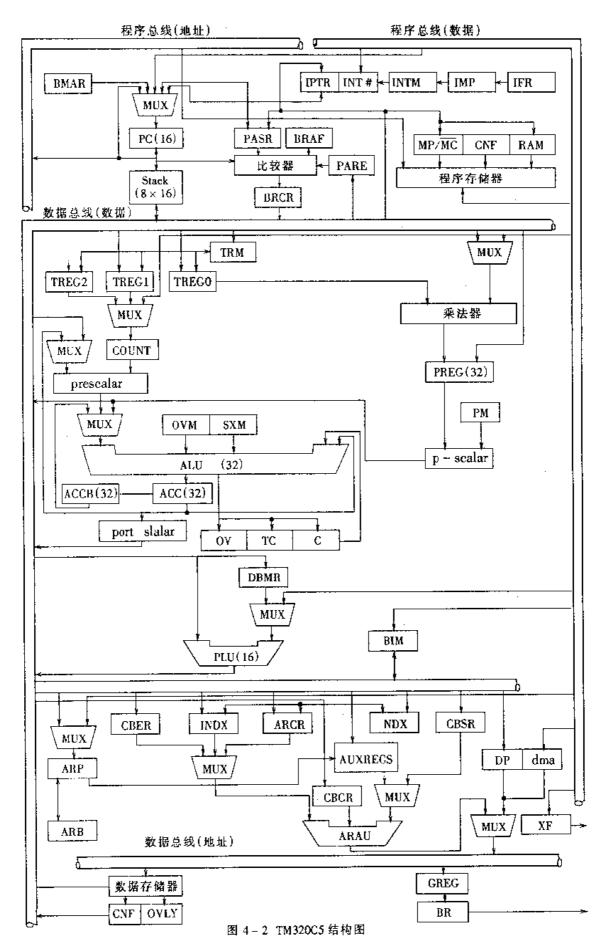

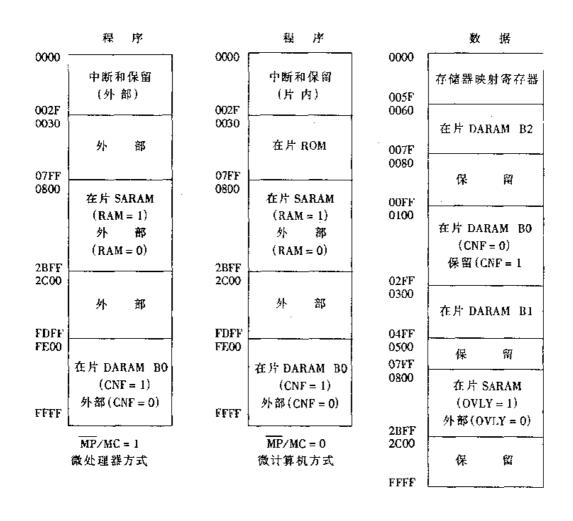

| 4.1 | TMS320C5X 处理器 ······ (80)    |

| 4.2 | μPD77230 处理器 ·······(96)     |

| 4.3 | 其它数字信号处理器简介                  |

| 第五: | 章 TMS320C30 与'C40 处理器(130)   |

|     | TMS320C30 处理器(130)           |

| 5.2 | TMS320C40 处理器 ····· (159)    |

| 第六: | 章 数字信号处理器的应用                 |

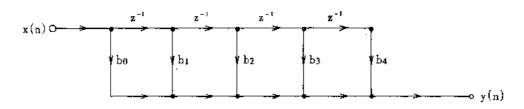

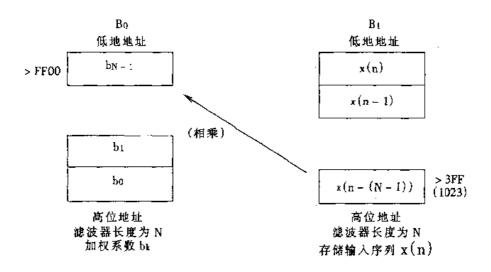

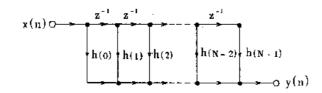

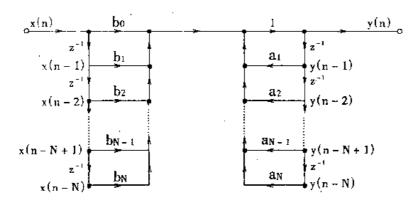

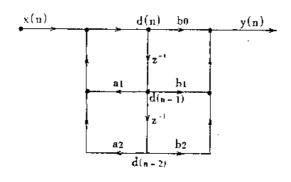

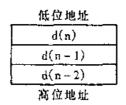

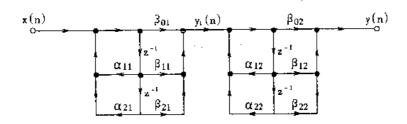

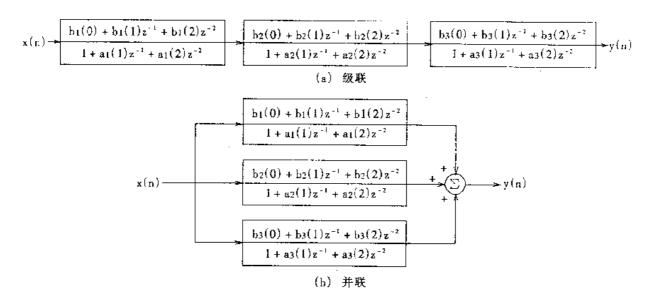

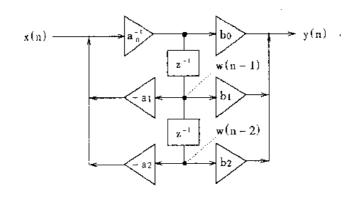

| 6.1 | 数字滤波器                        |

|     | 采用 TMS320C25 实现 FFT          |

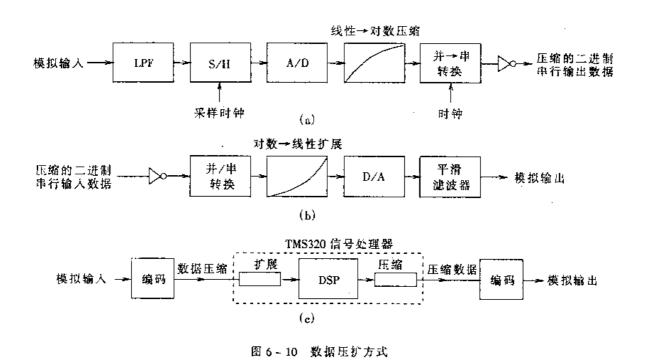

|     | 数据压扩 (187)                   |

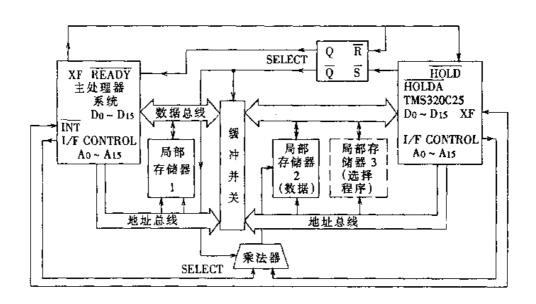

| 6.4 | 双 DSP 实时数字相关处理系统 ······(194) |

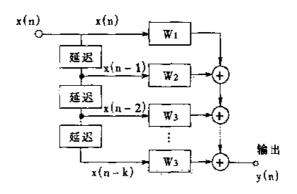

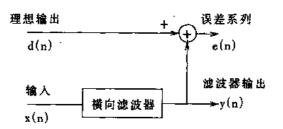

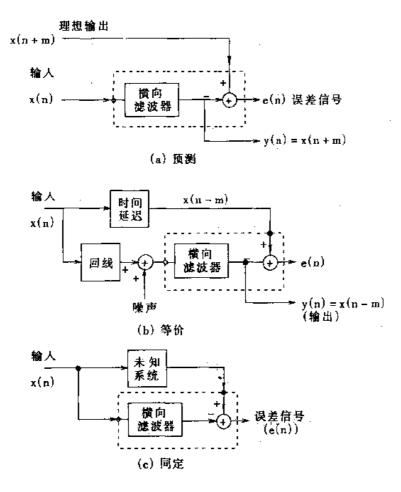

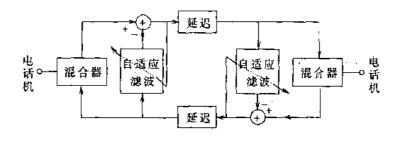

| 6.5   | 自适应滤波器及用 TMS32020 实现                                    | (202) |

|-------|---------------------------------------------------------|-------|

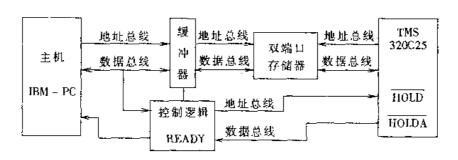

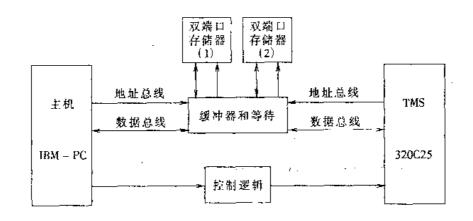

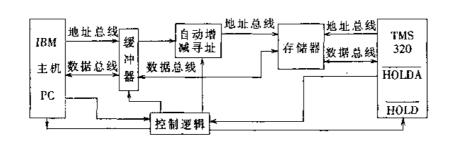

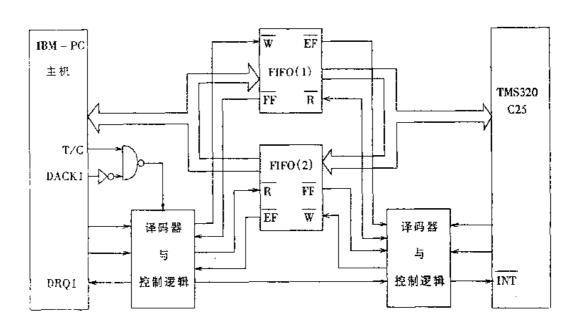

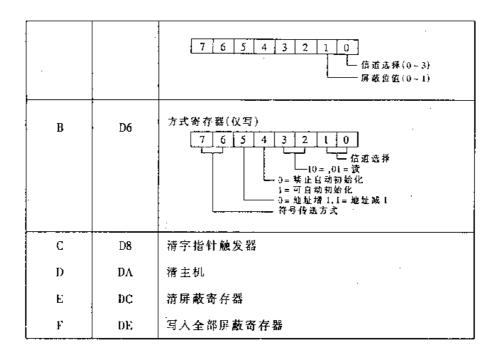

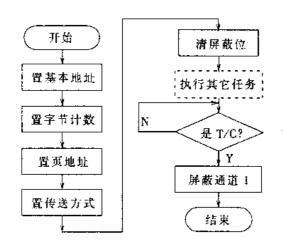

| 6.6   | PC 和 DSP 之间的 DMA 通信 ··································· | (206) |

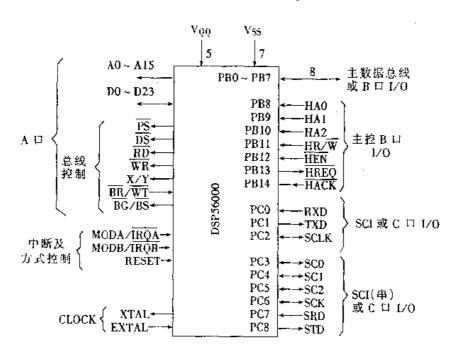

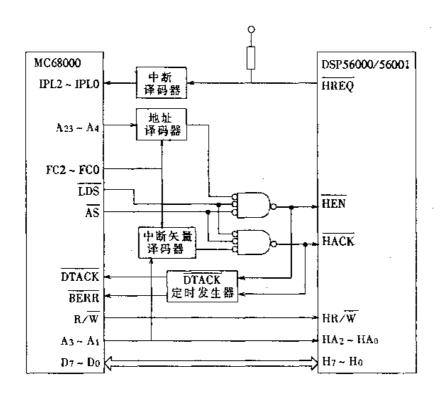

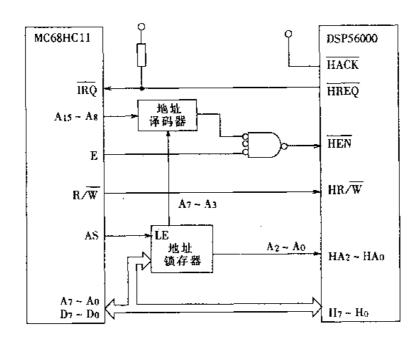

| 6.7 - | DSP56000/DSP56001 PID 控制系统 ······                       | (212) |

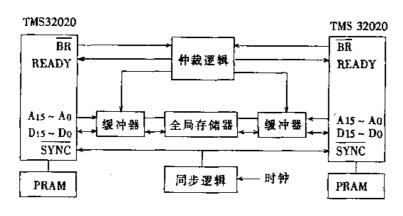

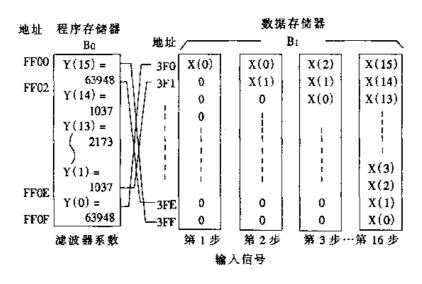

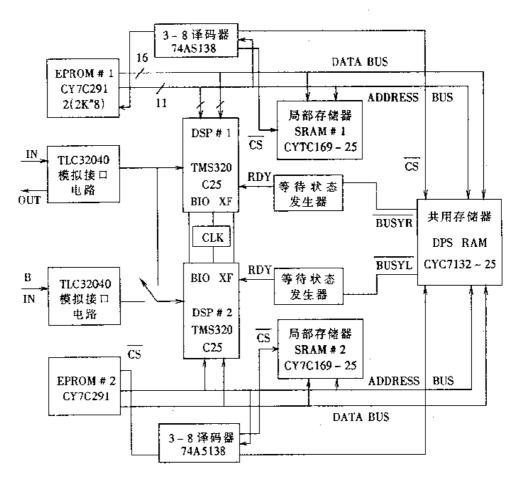

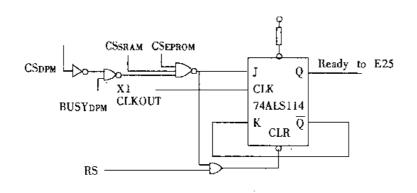

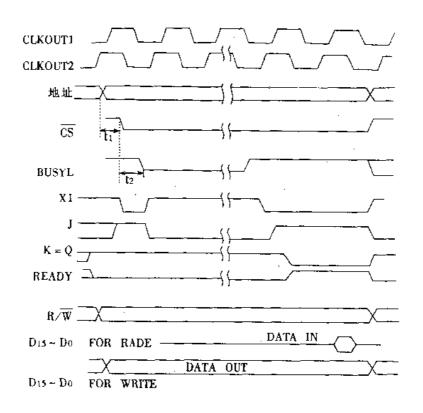

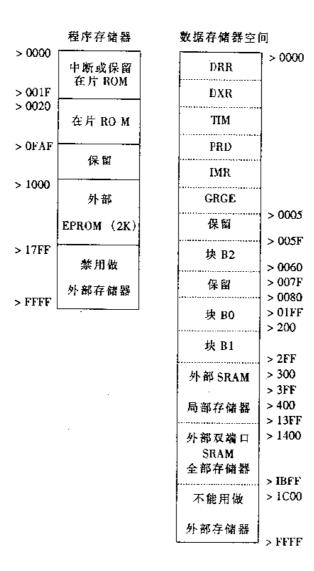

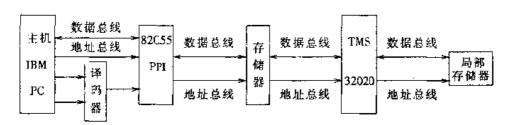

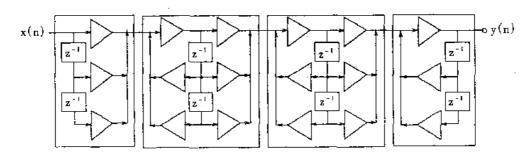

| 6.8   | 并行实时数字信号处理系统                                            | (218) |

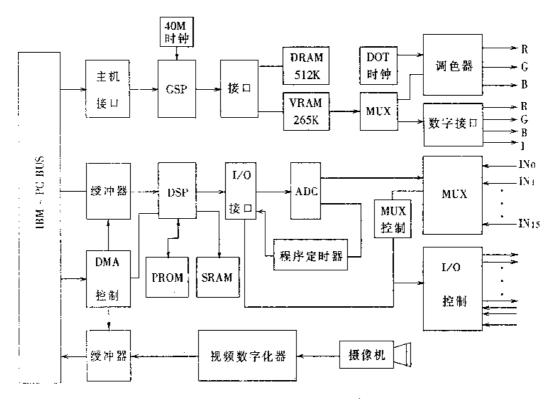

| 6.9   | SIMD 多 DSP 图象处理系统 ····································  | (224) |

|       |                                                         |       |

| 附录    | TMS320 系列指令系统 ····································      | (230) |

# 第一章 数字信号处理器发展概述

数字信号处理中的卷积、相关、窗口及FFT等,都是频繁进行大量数据的乘法和加法运算。通用微处理器(例如,8086、68000等)因适用目的不同,在运算速度上难以适应信号实时处理的要求。随着大规模集成技术的发展,开发了一种集成有高速度乘法器硬件、能够快速进行乘法和加法运算、适用于高速数字信号处理的单芯片大规模集成电路,这就是数字信号处理器(DSP)。近年来,DSP在功能、处理速度和处理能力方面,都取得了划时代的突破,并广泛应用在数据通信、语声信号处理、智能化仪器、自动控制等技术领域中,展示了其独特的应用潜力。

### 1.1 第一代 DSP

早期的 DSP 器件是 1979 年 Intel 公司开发的 2920 和 AMI 公司的 S2811。但典型 DSP 还是 1980 年 NEC 公司开发的 μPD7720 和 Bell 研究所开发的 DSP20。由于 DSP 器件在数字信号处理中展示了独特的优点,随之于 1982 年日立公司开发了 61810, TI 公司开发了 TMS32010 等 DSP 器件。这个时期开发的 DSP 器件,称为第一代 DSP,其主要指标如表 1-1 所示。

| 型号       | μΡD7720                 | TMS32010   | UD61810         | MB8764      |

|----------|-------------------------|------------|-----------------|-------------|

| 项目       | (NEC)                   | (17)       | (日立)            | (富士通)       |

| 硬件工艺     | NMOS                    | NMOS       | CMOS            | CMOS        |

| 引脚数      | 28(DIP)                 | 40(DIP)    | 40(DIP)         | 88(PGA)     |

| 命令周期     | 250ns                   | 200ns      | 250ns           | 100ns       |

| 数据字长     | 16 位                    | 16 位       | 16 位            | 16 位        |

| 在片程序存储器  | 512×23 位                | 1.5K×16 位  | 512 × 22 位      | 1K×24 位     |

|          |                         | 可外接扩至 4K 字 |                 |             |

| 在片数据 ROM | 512×13 位                | 与程序 ROM 并用 | 128×16 位        | 与程序 ROM 并用  |

| 在片数据 RAM | 128×16 位                | 144×16 位   | 200×16 位        | 256×16 位    |

| 乘法器      | 16 × 16 <del>→</del> 31 | 16 × 16→32 | (12+4) × (12+4) | 16 × 16-+26 |

| 输入输出     | 总线 8 位                  | 总线 16 位    | 总线 16 位         | 总线 16 位     |

| 1/0接口    | 串行 1/0                  | 16位1/0     | 串行 I/O          | 16 位 1/0    |

表 1-1 第一代 DSP

第一代 DSP 的构成特点为:

- (1)片装乘法器硬件,具有将乘法器和累加器以流水线方式连接的总线,能高速进行连续的乘法和累加运算;

- (2)采用哈佛结构,数据总线和程序总线分离,可同时进行指令的读取和数据运算;

- (3)在片程序存储器和数据存储器:

- (4)备有与 A/D、D/A 变换器等外围设备相接的接口,乘法器和累加器的位数在 16 位以上,能实现高精度的数据运算;

- (5)指令基本上在一个机器周期内进行处理;

(6)可进行数据的浮动小数点运算,动态范围大。

表 1 – 2 为  $\mu$ PD7720 和通用 8086 微处理器运算性能比较。从表中可以看到:  $\mu$ PD7720 和 8086 虽采用相同的 MOS 工艺和时钟,但同样完成 16 节 FIR 数字滤波器的运算,  $\mu$ PD7720 要比 8086 快几倍。

| 型 号          | μ₹D7720 | 8086     |

|--------------|---------|----------|

| 制造技术         | NMOS    | NMOS     |

| 时钟           | 8MHz    | 8MHz     |

| 元件数          | 40000   | 24000    |

| 机器周期         | 250ns   | 最小 250ns |

| 16 节 FIR 滤波器 | 50μs    | 270μs    |

表 1-2 μPD7720 和 8086 性能比较

### 1.2 第二代 DSP

1985 年 TI 公司开发的 TMS32020,1986 年日本 NEC 公司开发的 μPD77230 等通用 DSP, 与第一代 DSP 相比, 在功能上、速度上及内存容量方面, 都取得了划时代的突破;

- (1)运算速度更高,机器周期减少到 100ns,运算能力达 8~40MFLOPS:

- (2)和大型计算机一样,能进行32位的浮点运算,运算精度更高;

- (3) 片装大容量数据存储器和程序存储器,并大大扩展外部存储器空间(达 64K);

- (4)强化和完善了指令功能及寻址方式。

表 1-3 为第二代 DSP 性能一览表。表 1-4 是第二代 DSP 典型器件  $\mu$ PD77230 处理能力测试结果。

| 型号       | TMS32020/C25<br>(T1) | μPD77230<br>(NEC) | ADSP2100<br>(AD) | DSP56000<br>(MOTOROLA) |

|----------|----------------------|-------------------|------------------|------------------------|

| 机器周期     | 200/100ns            | 150ns             | 125ns            | 97.6ns                 |

| 乘·加执行时间  | 200ns/100ns          | 150ns             | 125ns            | 97.6ns                 |

| 数据字长     | 16 ∯                 | 32 位浮点            | 16 位             | 24 चि                  |

| 指令字长     | 16 位.                | 32 位              | 24 位             | 24 位                   |

| 在片程序 ROM | - /4K学               | 2 <b>K</b> 字      | -                | 2 <b>K</b> 字           |

| 在片程序 RAM | 256 字                | _                 | — 16字 (CACHE)    |                        |

| 在片数据 ROM | 与程序 ROM 并用           | 1K 宇              | _                | 512 字                  |

| 在片数据 RAM | 544 字                | 1K 字              | _                | 512 字                  |

| 程序存储器空间  | 64K 字                | 4K 字              | 16K 字            | 64K 字                  |

| 数据存储器空间  | 64K 字                | 8K 字              | 32K 字            | 128K 字                 |

| ALU      | 32 位                 | 55 位              | 16 位             | 56 位                   |

| ACC      | 32 位                 | 55 位              | 40 位             | 56 位                   |

表 1 - 3 第二代 DSP

| 输入·输出接口  | 16 位并行串行  | 32 位并行串行 | 存储器屏蔽 | 24 位可编程 |

|----------|-----------|----------|-------|---------|

| DMA 接口 , | 有         | 无        | 有     | 有       |

| 制造技术     | NMOS/CMOS | CMOS     | CMOS  | CMOS    |

| 消耗功率     | 1.2W/0.6W | 0.8W     | 0.5W  | < 1.0W  |

| 开发年月     | 1985/1988 | 1986     | 1986  | 1987    |

表 1-4 µPD77230 运算能力测试

| [        | 除算         | 4.8µs  |

|----------|------------|--------|

| <b>'</b> | 平方根        | 9. Oµs |

| 数值运算     | sin        | 10.8µs |

|          | C08        | 10.8μs |

|          | ATAN       | 40µs   |

|          | 2 节 FIR    | 0.9μs  |

|          | 32 节 FIR   | 5.25µs |

| 数字信号处理   | 32 点 FFT   | 150µs  |

|          | 512 点 FFT  | 4.7ms  |

| i        | 1024 点 FFT | 12.3ms |

# 1.3 第三代 DSP 及 DSP 的发展动向

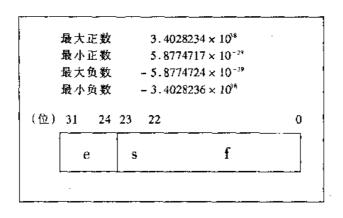

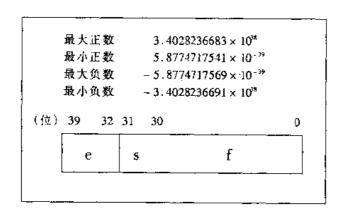

从1980年第一代 DSP 付诸实用,随着半导体集成电路技术的急速发展和高速实时信号处理技术的需求,在短短的十几年中,单片数字信号处理器取得了划时代的发展。1987年, T1 公司开发出高速、高性能、高内存、并且可使用高级语言的第三代数据字信号处理器 TMS320C30, 1991年,又推出了支持 32 位浮点运算的、速为 275MIPS、具有 340MB/秒数据 传输能力的、真正支持并行操作并与 TMS320C30 原代码兼容的 TMS320C40。表 1-5 为近年来开发的 32 位浮点数信号处理器功能一览表;

表 1-5 最新 32 位浮点 DSP

| 型号项目      | TMS320C30<br>(TI) | DSP96002<br>(摩托罗拉) | ZR34325<br>(ZORAN) | μΡD77240<br>(NEC) | MB86232<br>(富士通) | DSP32C<br>(AT&T) |

|-----------|-------------------|--------------------|--------------------|-------------------|------------------|------------------|

| 指令周期      | 60ns              | 60ns               | 80ns               | 90ns              | 75лв             | 60ns             |

| 浮点形式      | 2的补码              | IEEE               | IEEE               | 2的补码              | IEEE             |                  |

| 存储器<br>空间 | 16M 字             | 12G 字              | 16M 字              | 16M字              | 1M字              | 4M 字             |

| 在片 RAM    | 2 × 1K            | 3 x 512            | 2 × 64             | 2 × 512           | 512              | 1K/1536          |

| 在片 ROM    | 4K                | 2 × 512            | 256                | 2K + 1K           | 1 K              | 2K               |

| 在片高速      | 64                | <u> </u>           | 4                  |                   | <del>-</del> -   | _                |

| ALU       | 32E8              | 32E11              | 44 位               | 47E8              | 24E8             | 32E8             |

| 中 断 (内/外) | 7/4               | 0/3                | 22/1               |                   | /4               | /3               |

|     | DMA   | DMA   | DMA   | 输入 2 位 | DMA PIO | PIO   |

|-----|-------|-------|-------|--------|---------|-------|

| 1/0 | SIO×2 |       |       | 输出2位   | SIO × 2 | i     |

|     | 定时器×2 |       |       | •      | 定时器     |       |

| 封 装 | 181 端 | 195 端 | 84 端  | 132 端  | 208 端   | 195 端 |

|     | PGA   | PGA   | PGA   | PGA    | PGA     | PGA   |

| 功耗  | < 1 W | < 1 W | < 1 W | <2.3W  | < i W   | < 1W  |

由表 1-5 中可看出,在短短的几年中,通用 DSP 的发展取得了划时代的突破。人们期待着性能更高、运算速度更快的新 DSP 产品。从其开发动向来看,为满足复杂信号处理的需要,例如:运动图像处理、连续发声非特定说话人语音识别等,高速化、高性能化、片装存储器大容量化仍然是 DSP 的开发方向。近年来开发的 DSP,大多采用 32 位浮点运算机构,具有和大型计算机相同的浮点运算能力和精度,更加适合于数字信号处理的要求。

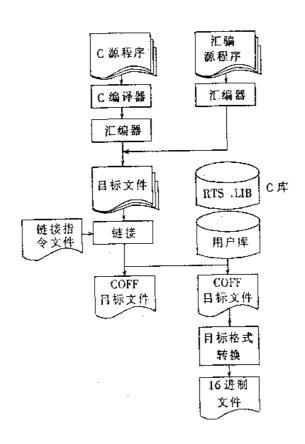

- (1) 浮点运算的 DSP 容易导入高级计算机语言。采用高级语言能缩短程序的开发时间,提高开发效益,因此,用于数字信号处理器的高级语言研究正蓬勃展开。使用高级语言,已成为第三代 DSP 的重要特征。

- (2) 目前使用的 DSP 其浮点数据的表示格式有两种,一是 2 的补码形式,另一种是 IEEE 格式,为便于 DSP 和高档微计算机相匹配以构成实用系统,采用 IEEE 格式将为主流。

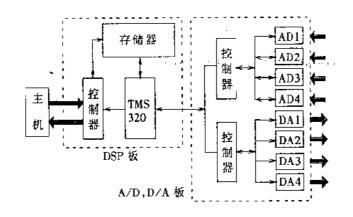

为充分发挥一般 CPU 所不具有的 DSP 的长处,扩大 DSP 的应用范围,各厂家均致力于 开发和完善 DSP 支援系统,特别是软件开发支援系统。值得指出的是,最近国外已研究出 利用通用微型计算机和 DSP 板组成的 DSP 开发系统。这个系统主机侧使用高级语言 C, PAS-CAL, DSP 板侧采用汇编语言,用微计算机开发 DSP 软件,直接生成目标代码。如果再配置 A/D、D/A 板,则可构成一个比较完善数字信号处理系统,完成数字滤波器设计、图像处 理、声音处理等。由于这种 DSP 开发系统的硬件成本远远低于 DSP 的专用开发支持系统, 特别是随着通用 32 位徽型计算机的普及,可用最小的开发成本获得最大的开发效益,因而 有可能成为当前 DSP 应用软件开发系统的主流。

# 第二章 TMS32010 系列处理器

### 2.1 TMS32010 概述

TMS32010 是 1983 年开发的第一代数字信号处理器。TMS32010 采用 2. 4 μmNMOS 工艺,使用单 + 5V 电源,时钟为 20MHz,片内带有时钟电路,指令周期为 200ns。片内数据 RAM为 144 字,片外程序存储器可扩展到 4K 字。

TMS32010 在运算中采用带符号的 2 的补码定点运算,并且有一个 32 位累加器/算术逻辑单元。除了用于信号定标的 0~15 位定标移位器外,还有一个对累加器输出进行 0、1、4 位移位的行数据移位器。TMS32010 有 8 个输入口和 8 个输出口,允许 40 兆位/秒速率的 16 位双向数据传送。它的中断可采用堆栈进行全部上下文保护。

TMS32010 特性如下:

- ・运算速度 5MIPS (20MHz 工作时钟)

- · 指令周期 200ns

- ・片内数据 RAM144 字

- · 外部程序存储器可扩展至 4K 字并全速运行 (5MIPS)

- ·16位指令/数据字

- ・32 位算术运算单元/累加器

- · 16 位乘 16 位运算用时 200ns

- ・0~15 位桶形移位器

- · 16 位双向数据传输

- · 全部上下文保护中断

- · 40 引脚双列直插封装件

TMS32010 自 1983 年出品以来,在许多领域得到了广泛的应用, 同时根据各自应用范围不同,又开发了一些新的品种。

TMS320C10 与 TMS320C10~25 是 1985 年开发的新产品。TMS320C10 采用了2.0 μmCMOS 工艺,功耗是 NMOS 芯片的 1/6,为 165mW,指令周期为 200ns,并与 TMS32010 目标代码及硬件兼容。通常用于需要低耗的场合。TMS320C10~25 是 TMS320C10 的变通产品,主时钟为 25MHz,指令周期是 160ns,具有低功耗、高速度的特点。

TMS320C15/E15 是 1986 年开发的产品。TMS320C15/E15 采用了2.0 μmCMOS 工艺,指令周期为 200ns,与 TMS32010 的目标代码和硬件完全兼容。但片内 RAM 扩展到 256 字,并增加了 4K 字 ROM (TMS320E15 型式)。

TMS320C17/E17 是 1987 年开发的产品。TMS320C17/E17 采用了2.0  $\mu$ mCMOS 工艺,指令周期为 200ns,是一种专用的微处理器,片内程序 ROM(TMS320C17)或 EPROM (TMS320E17)为4K字,具有一个双工串行接口,片内压缩扩展硬件( $\mu$ 律/A律)和一个串行口定时器。程序和 TMS32010目标代码兼容。

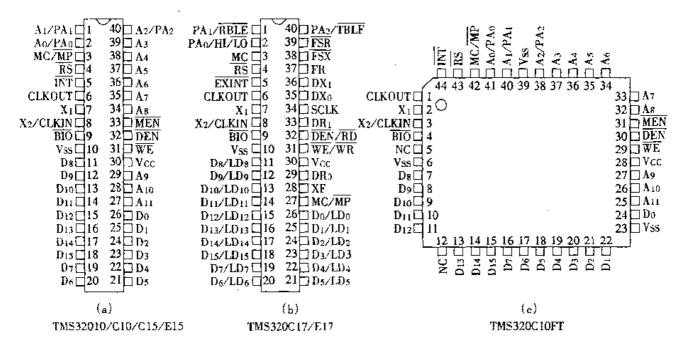

TMS32010 系列管脚配置如图 2~1 所示。各管脚功能如表 2~1。

图 2~1 TMS32010 系列引脚图配置

表 2~1 TMS32010 - 320E15 引脚功能

| 信号                    | 引脚序号 | 輸入輸出 | 功能                           |

|-----------------------|------|------|------------------------------|

| V <sub>nn</sub>       | 30   | 输入   | 电源电压 + 5V                    |

| V.,                   | 10   | 输入   | 接地                           |

| X2/CLKIN              | 8    | 输入   | 晶振输入或外部时钟输入                  |

| X1                    | 7    | 输出   | 内部时钟输出                       |

| CLKOUT                | 6    | ' 输出 | 时钟输出信号。CLKOUT的频率为外部时钟输入      |

| :                     |      | İ    | 或内部晶振频率的 1/4, 占空比为 0.5       |

| WE                    | 31   | 輸出   | 在"L"有效时,表示来自 TMS32010 数据总线上  |

|                       |      |      | 的数据有效。仅在 OUT 指令的第 1 周期和 TBLW |

|                       |      |      | 指令的第2周期有效。WE有效时,MEN及DEN常     |

|                       |      |      | 为 "H" 电平。                    |

| DEN                   | 32   | 輸出   | "L"有效,表示 TMS32010 处于从数据总线接收  |

|                       |      | }    | 数据的状态。仅在 iN 指令的第一周期有效,       |

|                       |      |      | 此时MEN和WE常为"H"。               |

| MEN                   | 33   | 輸出   | "L"有效、WE和DEN无效时,对在片离片程序程     |

|                       |      | ·    | 序存储器,取指时有效。                  |

| $\overline{	ext{RS}}$ | 4    | 输人   | 复位。                          |

| ĪNĪ                   | 5    | 输人   | 中断。在INT引脚加下降沿或电平作为中断产生信      |

|                       |      |      | 号。"L" 电平时允许中断。               |

| BIO                   | 9    | 输入   | L/O 分支控制。在执行 BIOZ 指令时,BIO引脚置 |

|                       |      |      | "L" 电平时, 则转向指令指定的地址。         |

| 1 015  | 10         | I        | DIS (MCD)   DO (150)                 |

|--------|------------|----------|--------------------------------------|

| D15    | 81         |          | DI5 (MSB) ~ DO (LSB)                 |

| 1      | l          | 输入/      | 数据总线当WE为"L" 电平时有效,此外常为高阻。            |

| D8     | <b>1</b> I | 输出/      |                                      |

| Ð7     | 19         | 高阻       | İ                                    |

| i      | ı          |          |                                      |

| D0     | 26         |          |                                      |

| A11    | 27         | 輸出       | 程序存储器地址 A11~A0 及通道                   |

| A10    | 28         |          | 地址 PA2 (MSB) ~ PAO (LSB)、A11~A0 非高阻。 |

| A9     | 29         |          | 执行 IN/OUT 指令时,通道地址为 PA2~ PAO。        |

| A8     | 34         |          |                                      |

| ι      | ı          |          | !                                    |

| А3     | 39         |          |                                      |

| A2/PA2 | 40         |          |                                      |

| A1/PA1 | 1          |          |                                      |

| AO/PAO | 2          |          |                                      |

| MC/MP  | 3          | 输人       | 设置微计算机方式或微处理器方式。                     |

|        |            |          | 当 MC/MP为 0 时,为微处理器方式,程序存储器只          |

|        |            |          | 能对外部存储器进行存取, 而对片内 EPROM 或掩摸          |

|        |            |          | ROM 不能进行存取。当 MC/MP为 1 时,为微计算         |

|        |            | <u> </u> | 机方式。可使用内部掩模 ROM 和 EPROM。             |

### 2.2 TMS32010 的硬件结构

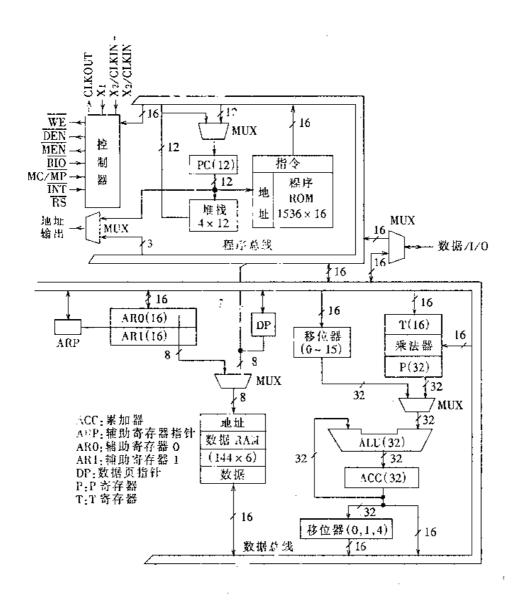

TMS32010 信号处理器的硬件结构框图如图 2-2 所示。

#### 一、运算单元

运算单元主要由 16 位×16 位的补码乘法器和累加器组成。

乘法运算时,先将数据存储器的数据(用LT指令)置入T寄存器,再用乘算指令(MPY)将数据存储器的数据和T寄存器的数据相乘、并将结果存入P寄存器。

P寄存器的数据可用传送指令(PAC指令)置入累加器。实际上,TMS32010有LTA、LTD等复合指令,可以高效率地进行T寄存器的数据置入以及送入累加器的加算数据的传送等操作。累加器长32位,可直接取入乘算结果。另外还设有将数据存储器的数据从0位到15位进行任意移位并置入累加器的定标移位器。累加器输出的高16位可进行0位、1位、4位的移位操作,以便在固定小数点运算中对齐小数点。

#### 二、数据存储器,DP, AR

TMS32010 片内存储器 (RAM) 为 144 字, 分为两页, 即 0 页和 1 页。0 页容量为 128 字, 1 页容量为 16 字,字长 16 位。TMS320C15/E15 及 TMS320C17/E17 片内 RAM 有 256 字,其中 0 页和 1 页各 128 字。寻址时由页面指针 DP 进行页选择。

图 2-2 TMS32010 构成框图

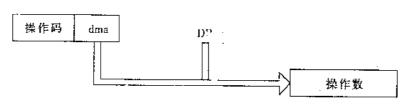

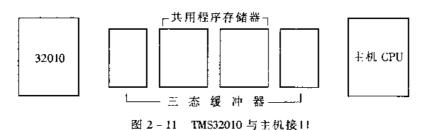

直接寻址方式如图 2-3 所示。在8位地址操作数中,1位是数据页面指针,其余7位嵌在操作码中。由DP和操作码实现直接寻址。

图 2-3 直接寻址方式

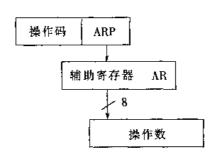

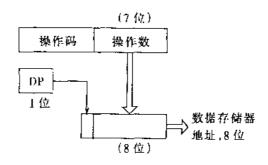

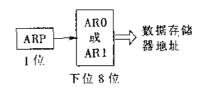

间接寻址方式时,由辅助寄存器指针 ARP 选择辅助寄存器 ARO 和 AR1,如图 2-4 所示。指令执行后 ARO 或 AR1 的内容自动进行加减。间接寻址方式时的指令方式如表 2-2 所示。

图 2-4 间接寻址方式

辅助寄存器 ARO 和 AR1 不仅可以用作存储器指针,在 BANZ 指令中还可用作循环计数器,作为暂时保留数据的临时寄存器。

| 寻址方式            | 操作                                  |

|-----------------|-------------------------------------|

| OP * (, NAPR)   | AR不变化                               |

| OP * + (, NAPR) | 用当前 AR 内容指定的数据存储器地址进行存取后, AR 的内容加 1 |

| OP * - (, NAPR) | 用当前 AR 内容指定的数据存储器地址进行存取后, AR 内容碱 !  |

表 2~2 间接寻址的指令方式

#### 三、程序总线

程序总线挂接程序计数器 (PC)、堆栈 (12位×4级)、掩模 ROM (1.5 K 字) 及控制单元等。

程序存储器空间为 4K 字, 12 根地址线 (AII ~ AO); I/O 通道 PAO ~ PA2 与地址总线多路复用。

与通用微处理器一样,堆栈不是外部存储器的指针,而是一个4级堆栈。中断产生或调用子程序时,(PC+1)的值进入堆栈;恢复中断或调用结束时,由RET指令从堆栈弹出,其值返回到PC内。此外,表读、写指令也可以使用堆栈的一个级,因而在使用表读、表写指令产生中断或调用子程序时,要注意堆栈的溢出。

根据需要,也可由程序将堆栈扩展到数据存储器或程序存储器,或用 TRLW 指令在外部存储器中建立极大的堆栈。

控制单元输出控制外部存储器和 1/0 的信号及各种接口信号。

#### 四、状态寄存器

如图 2-5 所示,状态寄存器由 5 个状态位组成。其中仅 OV 是由运算结果引起内容变化的状态位。OV 状态位在累加器溢出时是"H"电平,经过指令 BV 测试后可清除。其他各状态位由图中所示指令进行置位或复位。

| 累加器溢出标志<br>寄存器 OV | 溢出方式位<br>OVM | 中断屏蔽位<br>INTM | 辅助寄存器指针<br>ARP | 数据存储器<br>页指针 DP |

|-------------------|--------------|---------------|----------------|-----------------|

|                   | 1            | ļ             | \              | I               |

|                   | SOVM/ROVM    | EINT          | MAR/LARP       | LDPK/LDP        |

|                   |              | DINT          | 或间接寻址方式        |                 |

图 2-5 状态寄存器

使用 SST/LST 指令对状态寄存器进行存储和装入。直接寻址方式时,状态寄存器内容存入 1 页数据存储器。由于 TMS32010 的数据存储器有 144 字,因此地址需用 0-15 的数值。用间接寻址方式存储时不存在任何问题。

将数据置入状态寄存器使用 LST 指令。但该指令对中断屏蔽位 INTM 无效。中断屏蔽位由 EINT/DINT 指令进行置位和复位。

#### 五、存储器

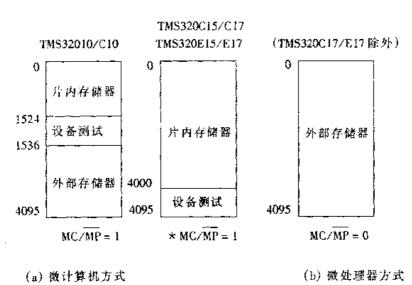

TMS32010 系列具有片内 ROM 或 EPROM,同时,通过 MC/MP 切换引脚可进行外部存储器和在片掩模 ROM/EPROM 之间的切换。如图 2-6 所示。

图 2-6 存储器分配图 (程序存储器)

一般而言,TMS32010/320C15/320C17 多不用掩模 ROM 而用外部存储器作为程序存储器。但 320E15/320E17 有在片 EPROM,在微计算机方式时用作程序存储器。TMS320C17/320E17 无外部地址线,在微计算机方式工作时,不能配外部存储器。

#### 六、1/0 接口

I/O 接口可使用 8 个输入、输出通道。通道地址 PAO~ PA2 与总线多路复用, A2~ A0 为通道地址。

#### 七、BIO与中断输入INT

BIO和INT是输入与外部系统接口信号的引脚。

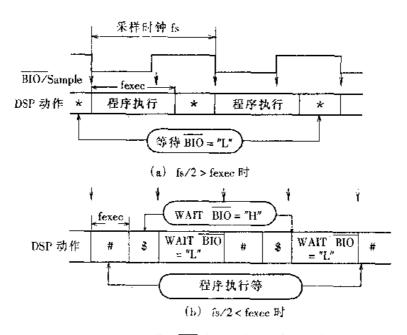

当输入外部标志置 BIO 引脚为 "L" 电平时,使用 BIOZ 指令可进行分支。BIO 引脚还可用于采样频率和程序的同步(如图 2-7)及 L/O 接口的状态监视。当 BIO 从 "H" 变为 "L" 电平时,DSP 从等待状态转移到执行状态,直至整体处理结束、下一个采样数据有效。

图 2-7 使用BIO引脚的采样频率的同步

当 DSP 的实时处理时间比采样周期小时,可按图 2-7(b)进行设定,检测出 BIO的 "H","L" 电平,则可完全与采样时钟同步工作。

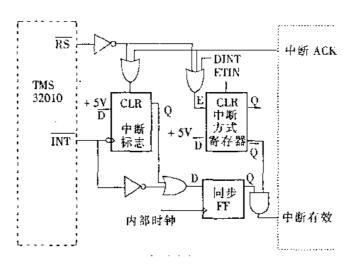

图 2-8 中断输入的内部结构

INT是中断信号输入引脚。中断输入的内部结构如图 2-8 所示。允许中断时需在INT引脚加 "L" 电平信号,在脉冲的下降沿产生中断并转移到中断矢量 002 地址,同时 PC 的值压入堆栈。但是,在下述三种情况下,中断处理要延迟到处理结束:

- (1) 乘算全周期结束;

- (2) 乘算指令下一条指令执行完毕;

- (3) EINT指令的下一条指令执行完毕。

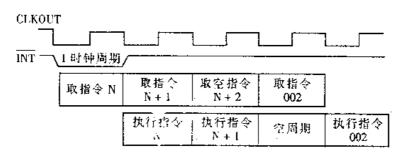

图 2-9 表示中断发生时的指令顺序。中断信号加入时从 N 地址和 N+1 地址取出的指令,在中断前执行;但不执行从 N+2 地址伪取的内容。待中断处理了程序执行完毕后,再取 N+2 地址的内容执行之。

图 2-9 中断时指令顺序

#### 八、复位

在 RS 引脚加上长达 5 个时钟周期以上的 "L" 电平的脉冲时, TMS32010 则复位。复位时 TMS32010 各引脚信号如图 2-10 所示。

图 2-10 复位时引脚信号

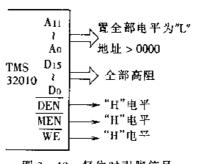

因此,当在主处理器和 32010 之间设置共用存储器时(如图 2-11), DSP 地址总线和存储器之间,必需设置一个三态缓冲器。

TMS32010 的 RS 引脚一旦设置为"H"电平,则复位状态结束。

- 12 -

## 2.3 寻址方式和指令系统

#### 一、TMS32010 寻址方式

TMS32010 有直接寻址、间接寻址、立即寻址等三种寻址方式。立即寻址又有指令助记符直接寻址和指令助记符间接寻址。此外,数据存储器和程序存储器间数据传送指令由累加器指定程序存储器空间的地址;分支指令时程序存储器仅有直接寻址;使用调用子程序指令时、程序存储器可直接寻址或由累加器寻址。

#### 1、直接寻址

直接寻址方式中操作数值本身就是地址。这种方式下,由数据页面指针 (DP)决定对包含 128×16 位字的 0 页进行存取或对包含 16×16 位字的 1 页进行存取。如图 2-12 所示,1 位的数据页面指针和程序总线上指令字中 7 位操作数连接生成 8 位数据存储器地址。

图 2-12 直接寻址方式

#### 2. 间接寻址

这种方式是由两个 16 位辅助寄存器 ARO 和 ARI 中的一个来完成的。该寄存器的低 8 位对数据 RAM 寻址。辅助寄存器指针(ARP)是状态寄存器中的一位,用来确定选择哪一个辅助寄存器。间接寻址方式时数据存储器地址生成如图 2~13 所示。

图 2-13 间接寻址数据存储器地址生成

间接寻址方式有几种不同的形式。一是指令执行后,辅助寄存器能自动增量或自动减量;二是相同的指令执行后,用以后的指令可变更辅助寄存器指针的值;在自动增量、减量或变更辅助寄存器指针值时,指令的执行时间不变。

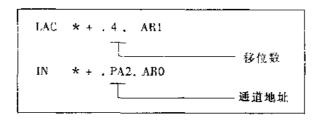

用汇编语言表示间接寻址操作数的方法如表 2-3 所示。在同时书写操作数移位数、通

道地址和指定下一个有效辅助寄存器指针时,应先写移位数和通道地址,如图 2-14 所示。

| 符 号       | 操作                                   |

|-----------|--------------------------------------|

| *         | 指令执行后, AR、ARP 的当前内容不变                |

| * +       | 指令执行后, AR 内容增 1, ARP 的内容不变           |

| * -       | 指令执行后, AR 内容减 1、ARP 内容不变             |

| * , ARm   | 指令执行后, ARP的值变为由 ARm 指定的值             |

| * + , ARm | 指令执行后, AR 的当前值增 1, ARP 值变为由 ARm 指定的值 |

| * + , ARm | 指令执行后, AR 的当前值减 1, ARP 值变为由 ARm 指定的值 |

表 2-3 间接寻址的形式

\* 表中 ARm 表示 ARO 或 AR1

图 2-14 间接寻址时的书写顺序

### 3. 立即寻址

有 5 条指令(LACK, LARK, LARP, LDRK, MPYK) 可将立即操作数嵌入操作码中。

#### 二、TMS32010 指令集

TMS32010的指令按功能分类如表 2-4 所示。

遊明 周期数 字数 操作码指令寄存器 助记符 15 14 13 12 11 10 9876543210 累加器指令 1 1 1 1 1 1110001000 累加器的绝对值 1 ABS ADD 加到累加器带移位 1 1 0 0 0 加弱高位累加器 Ò 0 0 001 ← D → ADDH 1 1 1 1 0 0 0 0 11 -- D ---加到累加器无符号扩展 ADDS 1 1 1 1 0 011 --- 0---与累加器"与" AND 1 ← → D - → 送累加器带移位 LAC 1 1 LACK 送累加器立即数 1 0 101←—D——→ 与累加器"或" 0R1 ←X → 1 ←-- D ---SACH **储存高位累加器位带移位**

表 2-4 TMS32010 指令

| SACL         | 储存低位累加器位               | 1                   | 1           | 0                      | 1              |                                       |          | 0 |     | 001 0              |

|--------------|------------------------|---------------------|-------------|------------------------|----------------|---------------------------------------|----------|---|-----|--------------------|

| SUB          | 从紧加器中减带移位              | 1                   | 1           | 0                      | 0              | 0                                     | 1        |   | S   | → 1← <del></del> D |

| SUBC         | <br>  条件減法 (用于除法)      | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 0 | 1   | 0 0 1 D            |

| SUBH         | 从高位累加器位减               | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 0 | 0   | 101 D              |

| SUBS         | 从果加器中减带无符号扩展           | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 0 | 0   | 111 D              |

| XOR          | 与暴加器"异或"               | 1                   | 1           | 0                      | 1              | 1                                     | 1        | 1 | 0   | 0 0 1 D            |

| LAC          | 累加器回零                  | ι                   | 1           | 0                      | . 1            | 1                                     | 1        | 1 | 1   | 1 1 1 0 0 0 1 0 0  |

| ZALH         | <br>  累加器回零并送人高位位      | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 0 | 1   | 0 1 1 D            |

| ZALS         | 累加器回零并送人带无符号           | 1                   | ı           | 0                      | I              | 1                                     | 0        | 0 | 1   | 101 D              |

|              | 扩展的低位位                 | 7 <del>7 -</del> 59 | n 32        | <del>≠</del> 99.10     | n STG .:+      | ار خالا ٠                             |          |   |     |                    |

| APAC         | P寄存器加到累加器              | F存器。<br>ℓ           | 1 1111<br>1 | 1 <del>7 韓本</del><br>0 | ⊬ 34€ 725<br>1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1        | 1 | 1   | 111000111          |

| LT           | 送入下寄存器                 | 1                   | ı           | 0                      | 1              | 1                                     | 0        | 1 | -   | 101 <del></del> 0  |

| LTA          | LIDA 把LIT和 APAC 组合成-条  |                     |             | 0                      | 1              | 1                                     | 0        |   | 1   |                    |

| LTD          | LID 把LT,APAC 和 DMDV 组合 | 1                   | _           | _                      | 1              | _                                     | -        |   | . 0 |                    |

| LID          | LID                    | 1                   | 1           | U                      | 1              | 1                                     | Ů        | 1 | . 0 | 111                |

| MPY          | 与 T 寄存器相乘; 乘积存人?       | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 1 | 1   | 011 D              |

| MPYK         | T 寄存器与立即数相乘; 乘         | 1                   | 1           | 1                      | 0              | 0 -                                   | •        |   |     | к                  |

|              | 寄存器                    |                     |             |                        |                |                                       |          |   |     |                    |

| PAC          | 从 P 寄存器送入累加器           | 1                   | 1           | 0                      | 1              | 1                                     | 1        | 1 | 1   | 111000111          |

| SPAC         | 「累加器减 ₽寄存器             | 1                   | 1           | 0                      | 1              | 1                                     | 1.       | 1 | 1   | 111001000          |

|              |                        |                     | 控制          | 指令                     |                |                                       |          |   | •   | •                  |

| DINT         | 禁止中断                   | 1                   | 1           | 0                      | 1              | j                                     | 1        | 1 | 1   | 111000000          |

| EINT         | 允许中断                   | 1                   | 1           | 0                      | 1              | í                                     | 1        | 1 | 1   | 111000001          |

| LST          | 送入状态寄存器                | 1                   | 1           | 0                      | 1              | 1                                     | 1        | 1 | 0   | 111 ← D —          |

| NOP          | 空操作                    | 1                   | 1           | 0                      | 1              | 1                                     | 1        | 1 | 1   | 111000000          |

| POP          | 弹出堆栈送累加器               | 2                   | 1           | 0                      | 1              | 1                                     | 1        | Ī | 1   | 111001110          |

| PUSH         | 从累加器压入堆栈               | 2                   | 1           | 1                      | 1              | 1                                     | 1        | 1 | 1   | 111001110          |

| ROVM         | 复位溢出方式                 | I                   | 1           | 0                      | ì              | l                                     | 1        | 1 | 1   | 111000101          |

| SOVM         | 置溢出方式                  | 1                   | 1           | 0                      | 1              | 1                                     | ι        | ı | 1   | 111000101          |

| SST          | ]<br>  贮存状态寄存器         | 1                   | i           | 0                      | 1              | 1                                     | 1        | 1 | ı   | 0 0 1 ←— D —       |

| <del>-</del> |                        | 1/0 \$              | 印数据         | 存储器                    | 5操作            |                                       |          |   |     |                    |

| DMOV         | 数据存储器地址单元内容重写在         | 1                   | 1           | 0                      | 1              | 1                                     | 0        | 1 | 0   | 011 ← - D          |

|              | 下一个地址单元                |                     |             |                        |                |                                       |          |   |     |                    |

| IN           | 从端口输入数据                | 2                   | 1           | 0                      | 1              | 0                                     | 0        | 0 | P   | A 1 + I)           |

| OUT          | 数据输出到端口                | 2                   | 1           | 0                      | 1              | 0                                     | 0        | ] | P   | A 1 + D            |

| TBLR         | 表格从程序存储器读到数据 RAM       | 3                   | 1           | 0                      | 1              | ı                                     | 0        | 0 | 1   | 111 - D -          |

|              | 表格从數是 RAM 写到程序存储器      | 3                   | 1           | 0                      | 1              | l                                     | 1        | 1 | 1   | 011 ← D —          |

|              |                        | J                   | 4           | v                      | 1              |                                       | ī        | T | Ţ   | 211 - D            |

| TBLW         |                        | 安存品                 | 足折粉         | 据语言                    | が出る            | - <del></del>                         | <u>.</u> |   |     |                    |

|              |                        | 寄存記                 | 器和数         | 据页面                    | 面指令            | 指4                                    | <b>₹</b> | 1 |     | 0 R 1 D            |

| LARP | 送入辅助寄存器指针立即数   | 1 | 1  | 0  | 1 | 1 | Q    | 1 | 0 | 0 0 1 0 0 0 0 0 0 K         |

|------|----------------|---|----|----|---|---|------|---|---|-----------------------------|

| IDP  | 送入数据存储器页面指针    | 1 | 1  | 0  | 1 | 1 | 0    | 1 | 1 | 1 1 1 <b>←</b> D <b>─</b> ► |

| LDPK | 送入数据存储器页面指针立即数 | 1 | 1  | 0  | 1 | 1 | 0    | 1 | ŀ | 100000000K                  |

| MAR  | 修改辅助寄存器和指针     | 1 | 1  | 0  | 1 | 1 | 0    | 1 | 1 | 1 1 0 ← - D                 |

| SAR  | 储存辅助寄存器        | 1 | 1  | 0  | 0 | 1 | 1    | 0 | 0 | 0 R 1 ←— D —→               |

|      |                | _ | 转移 | 指令 |   |   |      |   |   |                             |

| В    | 无条件转移          | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 0 | 0100000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | -转移地址 — <del>—</del> —→     |

| BANZ | 辅助寄存器非零转移      | 2 | 2  | 1  | 1 | 1 | 1    | 0 | 1 | 000000000                   |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | ·转移地址 ————                  |

| BGEZ | 如果累加器≥0 则转移    | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 1 | 0100001000                  |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   | _ | 转移地址 ────                   |

| BGZ  | 如果累加器 > 0 则转移  | 2 | 2  | 1  | 1 | i | 1    | 1 | I | 0000000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | 转移地址→                       |

| BIOG | BIO = 0 则转移    | 2 | 2  | 1  | 1 | 1 | 1    | 0 | 1 | 10000000000                 |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | 转移地址 ───→                   |

| BLEZ | 如果累加器≤0 则转移    | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 0 | 1100000000                  |

|      |                |   |    | 0  | 0 | 0 | () - |   |   | 转移地址 ────→                  |

| BLZ  | 如果累加器<0则转移     | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 0 | 1000000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 -  |   |   | -转移地址 <del></del>           |

| BNZ  | 如果加器≠0则转移      | 2 | 2  | 1  | 1 | ł | 1    | 1 | ı | 1000000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | 转移地址 ──                     |

| BV   | 溢出转移则转移        | 2 | 2  | 1  | 1 | 1 | 1    | 0 | 1 | 0100000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 +  |   |   | -转移地址                       |

| ΒZ   | 如果累加器=0则转移     | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 1 | 1100000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 🕶  |   |   | 转移地址→                       |

| CALA | 根据累加器调用子程序     | 2 | 2  | 0  | 1 | 1 | 1    | 1 | 1 | 1110001100                  |

| CALL | 立即调用子程序        | 2 | 2  | 1  | 1 | 1 | 1    | 1 | 0 | 0000000000                  |

|      |                |   |    | 0  | 0 | 0 | 0 -  |   |   | 转移地址 ──                     |

| RET  | 从子程序返回         | 2 | 1  | 1  | 1 | 1 | 1    | 1 | 1 | 1 10001101                  |

|      |                |   |    |    |   | _ |      |   |   |                             |

TMS32010 支持交叉汇编语言的伪指令如表 2-5 所示。

表 2-5 TMS32010 伪指令

| 伪指令  | 功        | 能     |

|------|----------|-------|

| AORG | 指定程序存储器的 | 的首地址  |

| BSS  | 预约数据存储器内 | 7.空区域 |

| DORG | 指定数据存储器的 | 的首地址  |

| END  | 指示源程序结束  |       |

| EQU  | 定义常数     |       |

### 三、汇编语言语法

1. 数据表示法

(1) 10 进制数(整数)

例: 1234, 8752, -5322

(2) 16 进制数

数据打头用"\$",例如,\$5678

(3) 10 进制数(小数)

用 10 进制数书写的小数、附加 Qn, n 表示小数点后的位数。例如,0.5Q15 , -1.72Q12 等。这种格式称为 Q 格式。

2. 指令行的构成

汇编语言源语句的各行构成例如下:

LOOP

IAC

datal, 4

ACC←左移 4 位

(标号)

(指令助记符)

(操作数)

(注 释)

一般由标号、指令助记符、操作数和注释四部分组成,各字段的定界符为一个以上的空格或标记码。各字段书写内容如下:

#### (1) 标号字段

标号或符号书写在每行的行首。字符个数虽无限制,但只有前 8 个字符有效。在该字段内不写任何东西时,应打入一个以上的空格或写人标记。

若第一个字符为\*时,该行为注释行。

(2) 指令字段

在该字段内书写指令或伪指令的助记符且必须用大写字符书写。

(3) 操作数字段

操作数的个数超过一个时,各操作数间用","号分开。操作数也可以是用+、-运算符组成的表达式,例如,A+B,X1+X2-\$10等。

### 2.4 TMS32010 程序设计

#### 一、程序结构

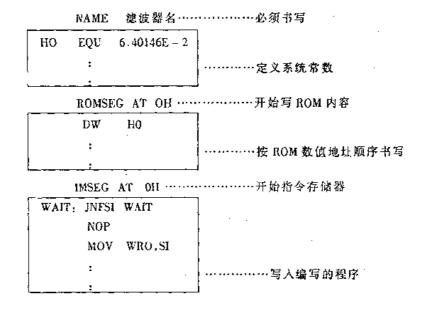

TMS32010 的程序如图 2-15 所示那样,主要由三部分组成。

- ・DSP 内部初始化

- ·设定常数

- ・程序体

图 2-15 基本程序流程

#### 1. 初始化

将 TMS32010 复位而处于解除状态时,除状态寄存器的中断位处于中断禁止外,寄存器的内容处于不定状态,因此必需重新设定各寄存器的值。

#### 2. 设定常数

由于数据存储器是 RAM, 必需将必要的数据从程序 ROM 传送到数据 RAM 中去。

3. 程序本体

在初始化和设定常数之后, 开始进行实际处理的程序部分。

#### 二、初始化程序

初始化程序如 LIST1 所示。TMS32010 复位解除后,从 0 地址开始进行处理。 旦进入中断,则从 2 地址开始处理。因此,在初始化程序中,在 0 地址置无条件分支指令(B)。

LIST1:初始化程序

| 1  |      | 0000          | ·       | AORG   | 0       | 解除复位,从0地址开始处理 |

|----|------|---------------|---------|--------|---------|---------------|

| 2  | 0000 | F900          |         | В      | INITIAL |               |

| 3  |      | 0100          |         |        |         |               |

| 4  |      |               |         |        |         |               |

| 5  |      | 0100          | AORG    | \$ 100 |         |               |

| 6  | 0100 | 7 <b>F</b> 8B | INITIAL | SOVM   |         | 设定溢出方式        |

| 7  | 0101 | F500          |         | BV     | OVRST   | 溢出标志复位        |

| 8  |      | 0103          |         |        |         |               |

| 9  | 0103 | 6880          | OVRST   | LARP   | 0       | 选择 ARO        |

| 10 | 0104 | 6E00          |         | LDPK   | 0       | 选择数据存储器的 0 页  |

指令 SOVM 设定 DSP 的溢出方式。在溢出方式下,累加器溢出后被置为正数 \$7FFFFFFF, 负数为 \$800000000。

指令 BV 用于将溢出标志复位。

LARP 将辅助寄存器指针 (ARP) 置 0, 确定 ARO 为辅助寄存器。

LDPK 置数据页面指针 (DP) 为 0, 直接寻址时在 0 页数据存储器进行存取。

#### 三、循环程序结构的控制

带循环结构的程序如 LIST2 所示。这个程序是从 I/O 的 0 通道读入 8 个数据,并依次存储在从 \$ 10 开始的数据存储器内。

LIST2: 使用 BANZ 指令的循环程序控制

| 1 |      | 0010 |        | DORG | \$ 10          |             |

|---|------|------|--------|------|----------------|-------------|

| 2 | 0010 |      | block1 | BSS  | 8              | 预约 8 字数据存储区 |

| 3 |      | 0100 |        | AORG | \$ 100         |             |

| 4 | 0100 | 7010 |        | LARK | ARO, block1    | ARO←存储区首地址  |

| 5 | 0101 | 7107 |        | LARK | AR1, 7         | 计数器置位       |

| 6 | 0102 | 6880 | LOOP   | LARP | 0              |             |

| 7 | 0103 | 40A1 |        | IN   | * + , PAO, AR1 | 由 1/0 输入    |

| 8 | 0104 | F400 |        | BANZ | LOOP           | 计数器监视       |

| 9 |      | 0102 |        |      |                |             |

伪指令 BSS 预约数据存储器的存储区,辅助寄存器 ARO 为指示数据存储目的地址指针,辅助寄存器 ARI 为计算循环次数的减 1 计数器。

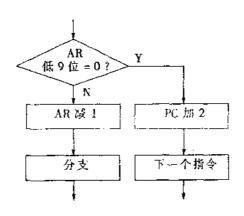

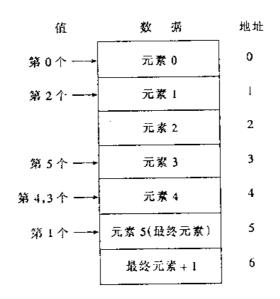

BANZ 为辅助寄存器非零转移指令,其操作如图 2-16 所示。首先判别当前辅助寄存器 指针指向的辅助寄存器 (AR) 的值是否为零,不为零时,辅助寄存器减 1,程序转移到由操 作数指定的地址;当值为零时,则依次执行下一个地址的指令。这样,使用 BANZ 指令控制 有循环结构的程序时,作为减 1 计数器的辅助寄存器的值为循环次数减 1。例如,本程序例 中循环次数为 8,因此在第 5 行中 AR1 内的值为 7。

图 2-16 BANZ 的操作功能

#### 四、设定常数的程序

LIST3 为将程序存储器 \$ 20~ \$ 24 地址内的常数传送到数据存储器 \$ 10~ \$ 14 地址内的程序例。程序存储器内的常数为 Q 格式。

该程序的要点是 16 行 TBLR 指令的用法。TBLR 指令将程序存储器的数据传送到数据存储器。该指令使用累加器为指示程序存储地址的指针。第 16 行中的 ARO 指定数据存储器的地址。

LIST3:设定程序存储器分配器的常数和传送

| l |      | 0010         | 0     | DORG | \$ 10        |           |

|---|------|--------------|-------|------|--------------|-----------|

| 2 | 0010 |              | blk I | BSS  | 5            | 预约5字存储区   |

| 3 | 0015 |              | ONE   | BSS  | 1            | 常数 1      |

| 4 |      | 0020         |       | AORG | \$ 205       |           |

| 5 | 0020 | <b>60</b> 7D | const | DATA | 0. 7538Q15   | 程序存储器上的常数 |

| 6 | 0021 | 58EC         |       | DATA | 0. 6947Q15   |           |

| 7 | 0022 | 938F         |       | DATA | - 0. 8472Q15 |           |

| 8 | 0023 | 0ADE         |       | DATA | 0. 0849Q15   | ·         |

| 9   | 0024 | ÇD1B |      | DATA | -0. 3976Q15 |              |

|-----|------|------|------|------|-------------|--------------|

| 10  |      |      |      |      |             |              |

| 11  |      | 0110 |      | AORG | \$ 110      |              |

| 12  | 0110 | 7010 |      | LARK | ARO, blk1   | ARO←数据存储器首地址 |

| 13  | 0111 | 7104 |      | LARK | AR1, 4      | 计数器置位        |

| 14  | 0112 | 7E20 |      | LACK | consl       | Acc←程序存储器首地址 |

| 15  | 0113 | 6880 | LOOP | LARP | 0           |              |

| 16  | 0114 | 67A1 |      | TBLR | * + , AR1   |              |

| 17  | 0115 | 0015 |      | ADD  | ONE         |              |

| 18  | 0116 | F400 |      | BANZ | LOOP        | 监视计数器的次数     |

| .19 |      | 0113 |      |      |             |              |

每传送完一个数据,则指向程序存储器和数据存储器的指针均加 1, 做好下一个数据传送的准备。

本程序例中 ARO 为数据存储器指针,其自动增 1 表现为操作数自动增 1;而累加器虽为程序存储器的指针,但因无增 1 指令,其增 1 操作由第 17 行的相加指令来完成。因此,在程序存储器的 \$ 15 地址(标号为 ONE),在程序执行前设定了常数 1。

#### 五、移位操作程序

TMS32010 有两种移位器。一种是将数据存储器的数据进行移位后传送到 ALU 的桶形移位器;一种是将累加器的内容移位后送到数据存储器的并行移位器。这两种移位器均只能进行数据的左移位操作。

这两种移位器和一般 CPU 移位的差别在于,它们不是将累加器内容进行移位的移位器, 因而在 TMS32010 中无移位操作指令。

桶形移位器可左移 0~15 位,用于 LAC、ADD、SUB 等指令;并行移位器与指令 SACH 一起使用,可左移 0位、1位或 4位。使用桶形移位器使数据进行算术右移的程序如 LIST4 所示。

LIST4: 使用定标移位器移位操作

| 1 |      | 0010 |            | DORG | \$ 10     |                 |

|---|------|------|------------|------|-----------|-----------------|

| 2 | 0010 |      | data1      | BSS  | 1         |                 |

| 3 | 0011 |      | data2      | BSS  | 1         |                 |

| 4 |      |      | · <b>*</b> |      |           |                 |

| 5 | 0000 | 2A10 |            | LAC  | data1, 10 | 左移 10 位后置入 ACC  |

| 6 | 0001 | 5811 |            | SACH | data2     | 存储 ACC 的上位 16 位 |

程序中第五行 LAC 指令是将数据 datal 送入累加器,由于 LAC 的第二个操作数为 10,则 datal 的内容左移 10 位后送入累加器。

由于 TMS32010 数据存储器字长为 16 位、累加器长 32 位、因此、累加器的上位 6 位和下 10 位虽是空位、但上位 6 位可进行符号扩展、下位 10 位可填入 0。

第 6 行是将 data2 存入累加器的上位 16 位,结果是将 data1 的内容向右移 4 位后以存放 data2。

#### 六、使用子程序的程序

TMS32010 有两种调用子程序的指令:

CALL:直接调用子程序

CALA:间接调用子程序

从子程序返回主程序的指令是 RET,该指令也可用于由中断处理返回主程序。 子程序例如 LIST5 所示。

#### LIST5:

| 1  |      | 0010 |             | DORG        | \$ 10         |

|----|------|------|-------------|-------------|---------------|

| 2  | 0010 |      | blk!        | BSS         | 5             |

| 3  | 0015 |      | ONE         | BSS         | 1             |

| 4  |      | 0020 |             | AORG        | \$ 20         |

| 5  | 0020 | 607D | const       | DATA        | 0. 7538Q15    |

| 6  | 0021 | 58EC |             | DATA        | 0. 6947Q15    |

| 7  | 0022 | 938F |             | DATA        | - 0. 8472Q15  |

| 8  | 0023 | OADE |             | DATA        | 0. 0849Q15    |

| 9  | 0024 | CD1B |             | DATA        | - 0. 3976Q15  |

| 10 |      |      |             |             |               |

| 11 |      | 0110 |             | AORG        | \$ 110        |

| 12 | 0110 | 7010 |             | LARK        | ARO, blk1     |

| 13 | 0111 | 7104 |             | LARK        | ARI, 4        |

| 14 | 0112 | 7E20 |             | LACK        | const         |

| 15 | 0113 | F800 |             | CALL        | MOVE          |

| 16 |      | 0180 |             |             |               |

| 17 |      |      |             |             |               |

| 18 |      |      |             |             |               |

| 19 |      |      | * * * * * * | * * * * * * | * *           |

| 20 |      |      | * 子         | 程 序         | *             |

| 21 |      |      | * * * * * * | * * * * * * | * *           |

| 22 |      | 0180 |             | AORG        | <b>\$</b> 180 |

| 23 | 0180 | 6880 | MOVE        | LARP        | 0             |

| 24 | 0181 | 67A1 |             | TBLR        | * + , AR1     |

| 25 | 0182 | 0015 |             | ADD         | ONE           |

| 26 | 0183 | F400 |             | BANZ        | MOVE          |

| 27 |      | 0180 |             |             |               |

| 28 | 0185 | 7E8D |             | RET         |               |

|    |      |      |             |             |               |

使用 CALL和 CALA 指令时,返回地址先压入堆栈,然后执行子程序。产生中断或执行 TBLR、TBLW 指令时,亦使用堆栈。

#### 七、乘法程序

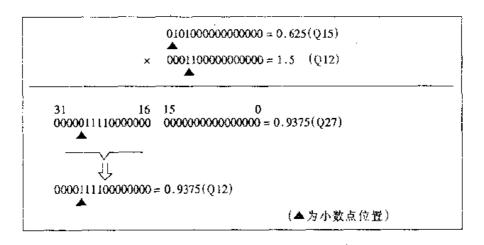

两个小数相乘时应注意小数点的位置。使用固定小数点运算的处理器时,在数字信号处理中其系数的绝对值大多数小于 1 并通常采用 Q15 格式表示之。Q15 格式系指小数点后有 15 位的表示形式。

本例的乘法运算,是求用 Q15 格式表示的数和任意 Q 格式表示的数的乘积,例如和 Q12 表示的小数的乘积,其示意图如图 2-17。16 位长的两个数相乘,其积长 32 位。如将其积的上位 16 位 (第 31~16 位) 取出并作为结果存储时,则积是用 Q11 格式表示的。但这样以来,在进行乘算时移动小数点位置,在小数处理是非常不方便的;因而希望小数点位置不变。为此,常取第 30 位~15 位作为积存储起来,仍为 Q12 格式,这就需要对小数点位置进行修正、修正的方法是将 32 位数左移 1 位,然后取其上位 16 位作为积。

图 2-17 与 Q15 格式的数机乘

LIST6 为任意格式的数和 Q15 格式的数相乘其结果仍用 Q 格式表示,并将其存入数据存储器的程序。这个程序分为两部分,前半部分为不进行舍入,后半部分则进行舍入操作。 LIST6:

| 1  |      | * * * * * | 无舍入时 | * * * * * |                   |

|----|------|-----------|------|-----------|-------------------|

| 2  |      | 0020      |      | DORG      | \$ 20P            |

| 3  | 0020 | x         | BSS  | 1         |                   |

| 4  | 0021 | у         | BSS  | 1         |                   |

| 5  | 0022 | z         | BSS  | 1         |                   |

| 6  | 0023 | ONE       | BSS  | 1         |                   |

| 7  |      | *         |      |           |                   |

| 8  | 0200 |           | AORG | \$ 200    |                   |

| 9  | 0200 | 6A20      | CT   | х         | $z \rightarrow T$ |

| 10 | 0201 | 6D21      | MPY  | У         | Τ× y              |

| 11 | 0202 | 7F8E      | PAC  |           | Acc∗-P            |

| 12 | 0203 | 5922             | SACH       | z, 1    | 存储结果 |

|----|------|------------------|------------|---------|------|

| 13 |      | *                |            |         |      |

| [4 |      | ⊲ <b>+ + + +</b> | 有舍入时       | * * * * |      |

| 15 |      |                  | , <b>*</b> |         |      |

| 16 | 0204 | 6A20             | LT         | x       |      |

| 17 | 0205 | 6D21             | MPŸ        | у       |      |

| 18 | 0206 | 7F8E             | PAC        |         |      |

| 19 | 0207 | 0E23             | ADD        | ONE, 14 | 舍人操作 |

| 20 | 0208 | 5922             | SACH       | z, 1    |      |

程序中由第 12 行(或 20 行)的指令 SACH 进行小数点修正。该指令原是将累加器上位 16 位进行存储,但因第二个操作数是 1,因而成为将累加器内容左移 1 位后,将其上位 16 位进行存储的操作。

舍入操作是将存放在数据存储器内的 16 位的第 1 位右侧加 1。在本程序例中,由于存储的是第 30~15 位,因而在第 14 位进行加 1 操作。在第 19 行中将 1 左移 14 位再与累加器内容相加,从而实现舍入操作。

#### 八、积加运算程序

在数字信号处理中,常进行数字滤波器的运算,其基本运算是积加运算。LIST7 为进行 多项式

$$y = a_0b_0 + a_1b_1 + a_2b_2 + a_3b_3 + \cdots$$

#### 运算的程序例。

| 1   | JST | 7. | 扣    | Ηn   | 程     | 120                   |

|-----|-----|----|------|------|-------|-----------------------|

| - 1 | 171 |    | 7000 | 1111 | T + T | $\boldsymbol{\sigma}$ |

|     | 1. 12.1. |      |     |       |         |                                                         |

|-----|----------|------|-----|-------|---------|---------------------------------------------------------|

| 1   |          | 0030 |     | DORG  | \$ 30   |                                                         |

| 2   | 0030     |      | ь0  | BSS   | 4       | a0 ~ a3                                                 |

| 3   | 0034     |      | bO  | BSS   | 4       | b0 ~ b3                                                 |

| 4   | 0038     |      | y   | BSS   | 1       | 卷积结 果                                                   |

| 5   | 0039     |      | ONE | BSS   | 1       |                                                         |

| 6   |          |      |     |       |         |                                                         |

| 7   |          | 0200 |     | AORGO | \$ 200  |                                                         |

| 8   | 0200     | 7F89 |     | ZAC   |         | Acc 清 0                                                 |

| 9 . | 0201     | 6A34 |     | ŁT    | Ь0      | Tp0                                                     |

| 10  | 0202     | 6D30 |     | MPY   | a0      | $T \times a\theta$                                      |

| 11  | 0203     | 6C35 |     | LTA   | b0 + 1  | T-b1; $Acc$ -Acc + $b0 \times a0$                       |

| 12  | 0204     | 6031 |     | MPY   | a0 + 1  | T x al                                                  |

| 13  | 0205     | 6C36 |     | LTA   | b0 + 2  | $T \leftarrow b2$ ; $Acc \leftarrow Acc + b1 \times a1$ |

| 14  | 0206     | 6D32 |     | MPY   | a0 + 2  | T x a2                                                  |

| 15  | 0207     | 6C37 |     | LTA   | b0 + 3  | T-b3; $Acc$ -Acc + $b2 \times a2$                       |

| 16  | 0208     | 6D33 |     | MPY   | a0 + 3  | $T \times a3$                                           |

| 17  | 0209     | 7F8F |     | APAC  |         | $Aee - Aee + b3 \times a3$                              |

| 18  | 020 A    | 0E39 |     | ADD   | ONE, 14 | 舍入                                                      |

| 19  | 020B     | 5938 |     | SACH  | y, 1    | 存储结果                                                    |

|     |          |      |     |       |         |                                                         |

程序中第 11 行、13 行、15 行的指令 LTA 可并行完成两种操作。一是将由操作数指定地址的数据存储器的内容送 T 寄存器,二是将当前 P 寄存器的内容与累加器内容相加。因此,在反复进行积加运算的场合,可同时进行将前次的积加到累加器及将下一个数据送人 T 寄存器的操作。每个积加运算执行时间为 2 个机器周期(400ns)。

### 九、除法程序

TMS32010 中无进行除算的指令。但使用条件减算指令 SUBC,可编成比较简单的除法程序,如 LIST8 所示。

LIST8: 除算程序

| 1  |      | 0000 |       | DORG | <b>\$</b> O |      |

|----|------|------|-------|------|-------------|------|

| 2  | 0000 |      | numer | BSS  | 1           | 被除数  |

| 3  | 0001 |      | denom | BSS  | 1           | 除数   |

| 4  | 0002 |      | quot  | BSS  | 1 .         | 商    |

| 5  |      | *    |       |      |             |      |

| 6  |      | 0200 |       | AORG | \$ 200      |      |

| 7  | 0200 | 6500 | •     | ZALH | numer       |      |

| 8  | 0201 | 700E |       | LARK | ARO, 14     | 置计数器 |

| 9  | 0202 | 6401 | LOOP  | SUBC | denom       | 条件减  |

| 10 | 0203 | F400 |       | BANZ | LOOP        |      |

| 11 |      | 0202 |       |      |             |      |

| 12 | 0205 | 5002 |       | SACL | quot        |      |

除算方法有恢复法和不恢复法。本例程序是采用 SUBC 指令的恢复法除算程序。

程序中第 9 行为 SUBC 指令。除算程序的主体是重复 15 次执行 SUBC 指令。该程序执行时,必需满足下述条件;

- ·被除数<除数

- ·被除数≥0;除数>0

- ·除数、被除数的小数点位置相同,即采用相同的 Q 格式的数。此时,商的值为 Q15 格式表示的数。

### 2.5 TMS32010 外部电路设计

#### 一、TMS32010 电路设计上的注意点

使用 TMS32010 系列处理器时, 在电路设计上必需注意解决以下问题。

1. 执行 OUT, TBLW 指令后的数据干扰

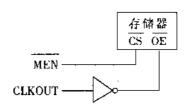

从 TBLW 指令和 OUT 指令时序可知,当由 MEN 信号控制存储器输出时,在一个最大为 35ns 的间隔内,DSP 和程序存储器之间,会引起总线冲突。为防止出现这种情况,可使用 CLKOUT 信号和 MEN 信号,如图 2-18 那样,对存储器的输出进行控制。

图 2-18 防止数据干扰的电路

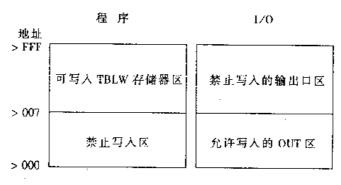

TBLW 指令和 OUT 指令时序的非区别性如图 2-19 所示那样,在\$000~\$007 地址内, 无法区别 TBLW 和 OUT 指令。当然,如果程序存储器全部为 ROM 且不使用 TBLW 指令时,则无需进行地址译码。问题是程序存储器使用 RAM 且使用 TBLW 指令时,如果没有地址译码器,则在全地址空间无法区别这两个指令。

图 2-19 有译码器时地址分配图

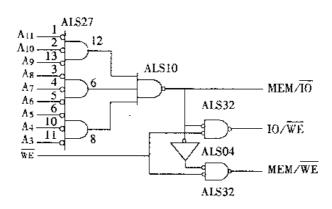

为了区别这两条指令,可使用图 2-20 的译码电路。使 \$000 - \$007 地址仅对 OUT 指令有效,而不向存储器写入数据。这样,在设计存储器电路和 1/0 电路时,应综合考虑,要特别注意 TBLW 和 OUT 都使用 $\overline{WE}$ 信号这一特点。

图 2-20 译码电路

#### 2. 使用控制信号时的注意点

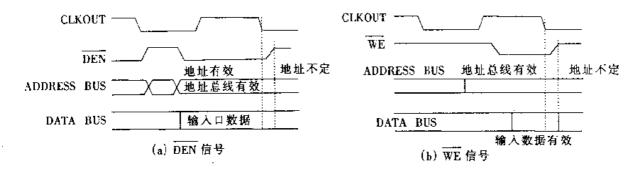

在设计存储器、I/O 电路时、为防止数据干扰、MEN信号一定要由 CLKOUT 进行译码。

DEN和WE的时序如图 2-21 所示。如图 (a) 所示那样, DEN信号的上升沿迟于 CLKOUT 信号的下降沿时,在 CLKOUT 下降沿后呈现不确定地址,因而在数据总线上有可能出现不确定的数据。

图 2-21 DEN 和 WE 时序

同样的,如图(b)那样,地址总线直到CLKOUT下降沿前有效。但当WE的上升沿较CLKOUT的下降沿滞后时,则在CLKOUT的下降沿后,会出现将数据写入不确定的地址之内的情况。因而,WE也必需用CLKOUT进行译码。

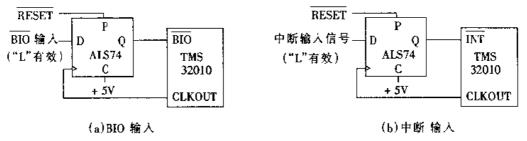

#### 3. TMS32010 BIO、INT 引脚处理

在使用 TMS32010 时,如图 2-22 那样, $\overline{BIO}$ 引脚和 $\overline{INT}$ 引脚应接入同步双稳态电路以防止误操作。

图 2-22 TMS32010 中 BIO、INT 引脚处理

TMS320C10, 320C15/E15 是改良型的信号处理单片机,不必使用双稳态电路。

#### 4. X2/CLKIN 引脚的连接

在 TMS320C10 引脚中,许多引脚和 TTL 兼容, X2/CLKIN 引脚为 V1H = 3V。因此,当用 HC 型 CMOS 驱动或用 TTL 驱动时,接一个前置电阻,只要满足 V1II 为 3V 即可。

#### 二、TMS32010 接口设计

#### 1. 主时钟周期和指令周期

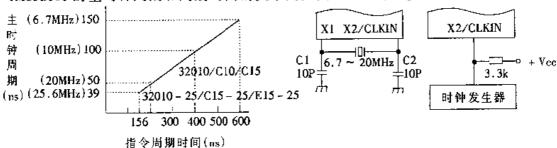

TMS32010 的主时钟周期和周期时间的关系则如图 2-23 所示。

图 2-23 主时钟和周期时间

即主时钟在 4 分频后作为 CLKOUT 信号输出到外部,周期时间为主时钟的 4 倍。主时钟的频率范围为 6.7MHz~20MHz(32010/CI0/CI5/EI5),因而指令周期时间在 600ns~200ns 范围内。

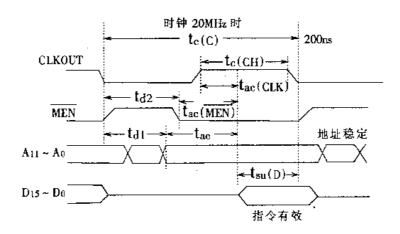

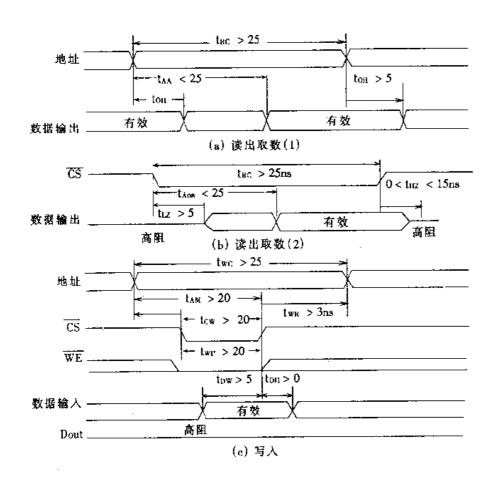

2. 存储器、I/O的存取时序

图 2-24 为存储器的读出时序。从存储器的读出周期来看,有三种存取时间:

(1) tm 从地址有效开始的存取时间。从图 2-23 中看出, tm 为:

$$t_{ac} = t_{c} \cdot (e) - t_{dl} - t_{su} \cdot (0) = t_{c} \cdot (e) - 100 = 100 \text{ (ns)} \cdot (20 \text{MHz})$$

为避免总线上数据冲突、多不使用。

(2) tae (CLK) 从 CLKOUT 有效开始的存取时间:

$$t_{uc}$$

(CLK) =  $\frac{1}{2}t_c$  (c)  $-20-50=30$  (ns)

这时虽有总线冲突,但由于 tac (CLK) = 30ns,接口时需用高速存储器。

(3) Lc (MEN) 从MEN信号有效开始的存取时间:

$$t_{ac} (\overline{MEN}) = t_{c} (c) - t_{d2} - t_{su} (d) = 85 \text{ns}$$

图 2-24 存储器读出时序

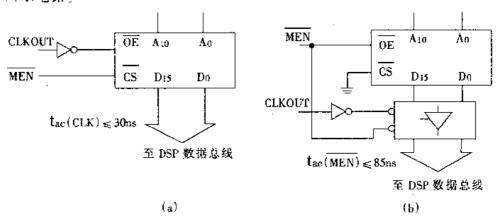

、此时虽可能引起总线冲突,但如果用 CLKOUT 信号控制输入输出,对数据总线进行离线控制,可适用于比  $t_{\rm sec}$  (CLK) 速度稍慢的存储器。例如,使用 CLKOUT 信号进行控制时,用图 2 – 25 所示电路。

图 2-25 由 CLKOUT 信号控制输入输出

图 2-25 (a) 为从 CLKOUT 有效开始的存取时间为 30ns 以下时存储器译码电路,图 2-25 (b) 为从MEN有效开始的存取时间在 85ns 以下时的存储器译码电路。

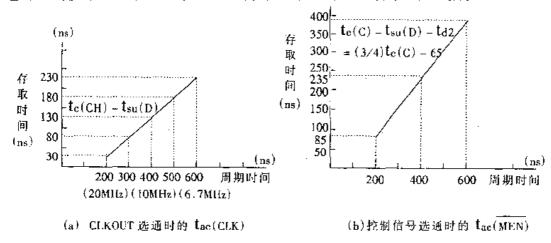

上述存取时间  $t_{ac}$  (CLK) 和  $t_{ac}$  (MEN) 与周期时间的关系如图 2 – 26 所示。但这些数值中不包含总线缓冲器和译码器的延迟时间,因而在设计时必须考虑这一点。

图 2-26 周期时间与存储器存取时间

#### 三、TMS32010 与存储器接口

1. TMS32010 与商速 EPROM 接口

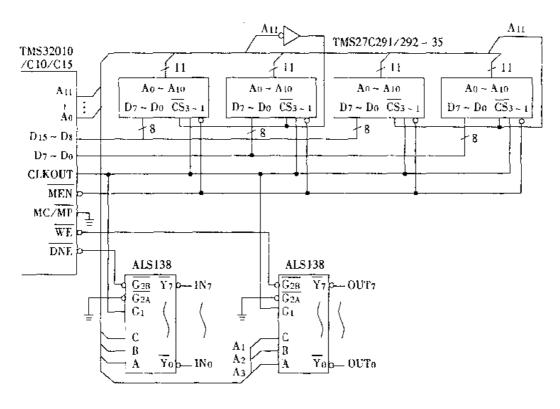

图 2-27 为 TMS32010 与高速 EPROM TMS27C291/29235 接口的实际电路图。

图 2 - 27 TMS32010 与高速 EPROM 接口

EPROM 从接受片选信号开始的存取时间是  $25 \, \mathrm{ns}$ ,满足图 2-24 中的存取时间  $t_{\mathrm{ac}}$  (CLK)。因此,电路中将 CLKOUT 引脚与 EPROM 的片选引脚直接相接。同时,用最上位地址  $A_0$ 进行存储器译码,以构成容量为  $2 \, \mathrm{K} \times 8$  位的存储器。

本例中全部程序空间均由 ROM 组成, 所有地址均不能使用 TBLW 指令。

2. TMS32010 和高速 EPROM 和高速 SRAM 接口(1)

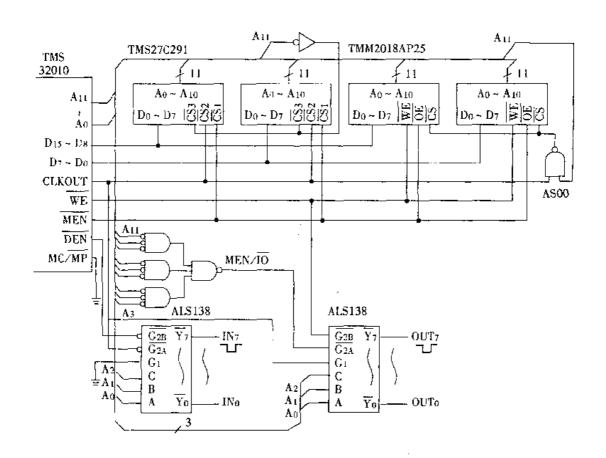

图 2-28 为 TMS32010 与 2K 字 EPROM 和 2K 字高速 SRAM 接口电路图。

图 2-28 TMS32010 与 EPROM/SRAM 接口

电路中使用了高速 RAM (存取时间 25ns) 作为程序存储器,因而附加了译码器电路,译码器电路生成MEN/IO信号,以区别 TBLW 和 OUT 指令。

同样,在\$000~\$007H地址内,硬件电路也不能对TBLW和OUT进行区别,因而,在这个区域内,不能使用TBLW指令。

另外、由于 EPROM 和 SRAM 有相同的存取时间 (25ns), 小于 t<sub>ac</sub> (CLK), 可以用 CLK-OUT 信号直接进行译码。

3. TMS32010 与 EPROM 和高速 SRAM 接口 (2)

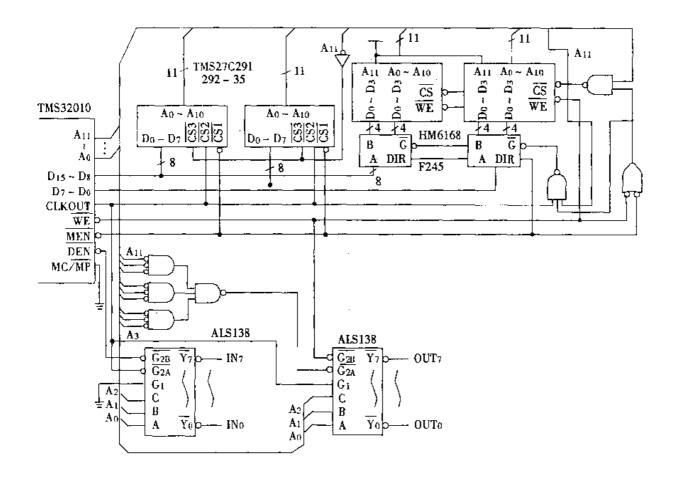

前两例中介绍的都是使用存取时间为 25ns 的集成电路存储器,图 2-29 所示的是时钟仍为 20MHz,但使用存取时间稍长一些的集成电路存储器时的接口电路。

图 2-29 TMS32010 与 EPROM/SRAM 接口 (2)

正如在存储器存取时序中叙述的那样,在存储器一侧不用 CLKOUT 信号而仅用控制信号进行译码。为避免总线冲突,在 RAM 和 DSP 之间,介入双向数据总线缓冲器并由 CLKOUT 进行控制。

这时,存储器的存取时间变为  $t_{ac}$  (MEN) (85ns),但尚需从  $t_{ac}$  (MEN) 中减去缓冲器的延迟时间,因而,实际的存储器的存取时间为  $t_{ac}$  (MEN) – 15ns = 70ns,因而可以使用存取时间为 70ns 左右的存储器。

#### 4. TMS32010 和通用 EPROM 的接口

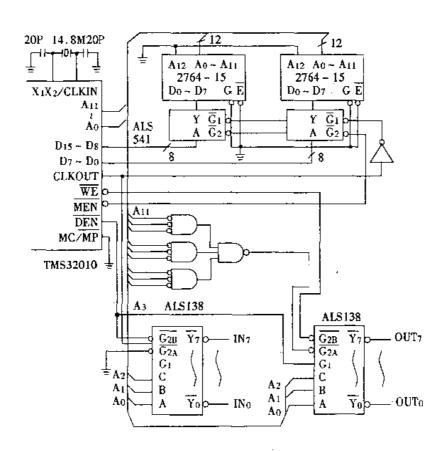

在允许降低执行速度的场合,可以降低时钟频率而和通用存储器接口。图 2-30 为使用高速型(存取时间在 150ns 左右)存储器 2764 接口的电路图。

设从地址有效开始的存取时间为 150ns。为避免总线冲突, 电路中附加外部总线缓冲器, 并由控制信号MEN和 CLKOUT信号进行控制。总线缓冲器和反相器的延迟时间约为 20ns, 因而需时钟周期 t<sub>a</sub>(c)为 270ns, 即主时钟频为 14.8MHz。

图 2-30 TMS32010 与 2764 接口

#### 四、TMS32010 和 1/0 接口的实际电路

#### 1. I/O 存取时间

执行 IN 指令时的存取时间从 $\overline{DEN}$ 脉冲开始,为  $t_c$  (c)  $-t_{04}-t_{su}$  (D),在主时钟为 20MHz 时为 85ns。

#### 2. 1/0 接口

L/O 接口和存储器接口时一样,当使用微处理器的外围集成电路时,必须降低时钟频率。在主时钟为 20MHz 时,可使用 ALS/LS 型 TTL,或 HC/HCT 型标准逻辑器件作为外部设备。如果考虑到扇出等因素,与数据总线有关设备,在速度允许的情况下也可以使 HC 型逻辑电路。但是,译码电路中总是有延迟的,因而要使用 ALS、AS或F型的器件。

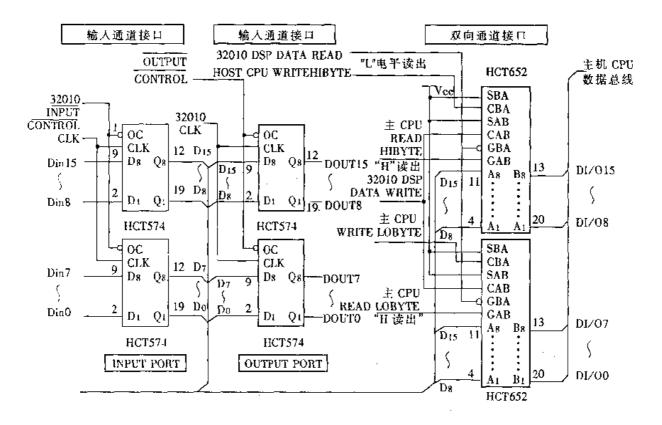

#### 3. 输入通道和输出通道

输入通道和输出通道的电路例如图 2-31。输入和输出通道都使用 HCT574 型锁存器。如果在 CLK 引脚加上正向脉冲时,数据置位,直到下一个上升沿数据被锁存。

图 2-31 输入通道与输出通道

数据读出时在 OC 引脚置 "L" 电平。

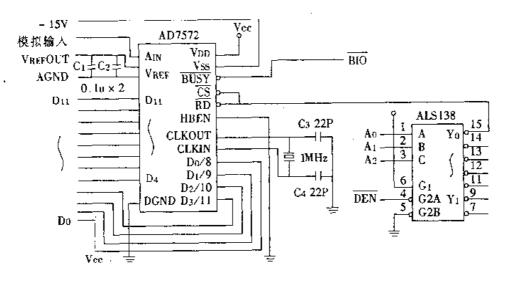

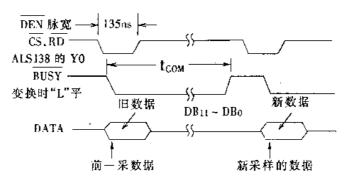

#### 五、TMS32010 与 A/D 转换器接口

图 2-32 为 TMS32010 与 AD7572 接口的线路。

图 2-32 TMS32010 与高速 A/D 接口

图中, DSP 的数据总线直接和 AD7572 相连。AD7572 的使用方式, 称为 ROM 并行读出方式。即由一个 READ 操作使转换开始, 前次转换结果(12 位数据)出现在数据输出引脚 DH1~D0。该数据如不需要可以舍去; 然后由第二个 READ 操作读取新的数据(DH~D0)并开始下一个转换。

在两次 READ 操作之间,最少有 AD7572 转换时间的延迟。这时的时序如图 2-33 所示。 DEN信号和地址译码之后,生成RD信号。即用两次 READ 操作得到新的变换数据。

图 2-33 TMS32010 与 A/D 接口时序

#### 六、TMS32010 与串行型 A/D 转换器接口

一般的 TMS32010 无串行口, 因而在与具有串行型输入输出的 A/D 转换器接口时, 需介入移位寄存器, DSP 对进入移位寄存器的数据进行存取。

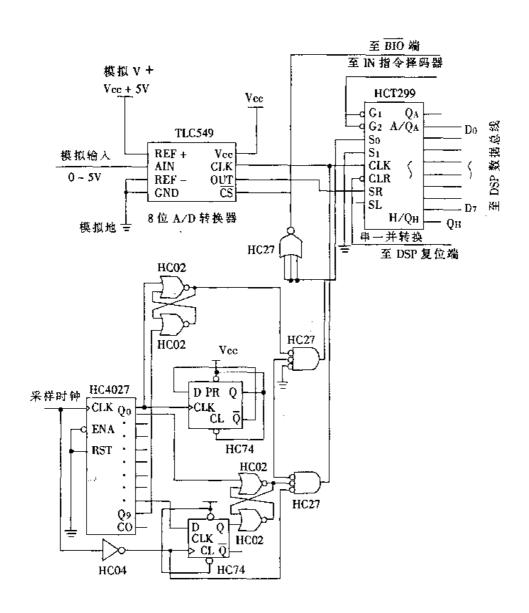

图 2-34 为 8 位 A/D 转换器 TLC549 与 TMS32010 接口的线路图。

图 2 · 34 TMS32010 与 D/A 转换器接口

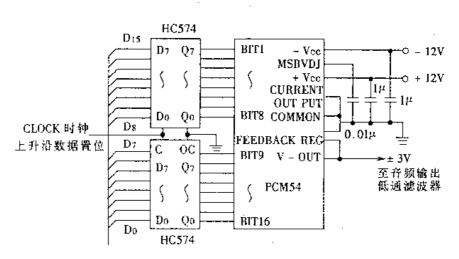

#### 七、TMS32010 与 D/A 转换器接口

图 2-35 为 D/A 转换器通过锁存器与 DSP 的接口电路。

图 2-35 TMSA32010 与 D/A 转换器接口

#### 八、TMS32010 与扩展存储器接口

TMS32010 可外接程序存储器和 I/O, 但不能外接数据存储器。但是, 在 I/O 空间设置锁存器, 并以此为地址使用数据输入输出指令而对数据进行存取, 虽然需要一定的时间, 但终究可作为数据存储器。

图 2-36 为扩展存储器的接口电路。

图 2-36 TMS32010 与扩展存储接口(64K字)

**—** 35 —

# 第三章 TMS32020 系列处理器

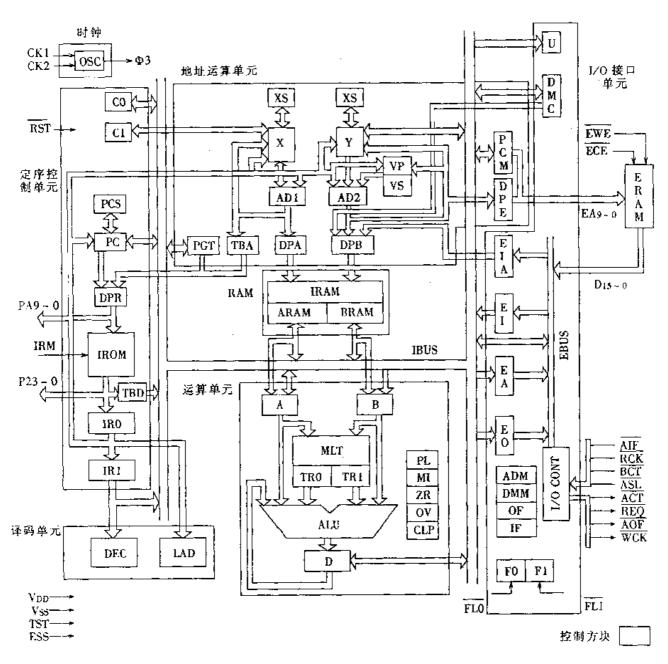

# 3.1 TMS32030 概述

TMS32020系列是美国 TI 公司开发的第二代数字信号处理器。它主要有两个产品: TMS32020 和 TMS320C25。

#### 一、TMS32020 特性

TMS32020 是美国 TI 公司 1985 年开发的产品。TMS32020 在保持 TMS32010 优点的基础上 又增加和扩充了许多功能。

TMS32020 芯片采用了特殊的系统结构(哈佛结构),程序存储器和数据存储器分离,这使得指令与数据存取可以同时进行,从而提高了执行速度。32020 的时钟频率为 20MHz,指令执行速度达 5MIPS。它的指令集是针对信号处理工作的。寻址方式有直接和问接寻址方式。对不同的工作要求,可以构成不同配置的各种系统,如最小配置的独立系统、局部存储器的主从系统、以及全局存储器的多处理器系统等。芯片的功能适用于数字信号处理、图形图像处理、语音处理、测量与控制以及通信等领域。

TMS32020 的主要特性有:

- · 可执行片内 RAM(BO块)中的程序;

- · 片內数据 RAM544 字,其中 256 字可任意地配置为程序或数据存储器;

- · 外部存储器扩展空间 128K 字(64K 字程序存储器和 64K 字数据存储器);

- · 单周期乘法/累加指令;

- · 指令系统支持浮点操作;

- · 具有多处型器和全局数据存储器接口:

- · 同步多处理器配置的能力;

- 可实现数据 /程序管理的块传送;

- 有与慢速外存储器及外围设备通信的等待状态;

- · 具有片内定时器和串行口;

- · 5个辅助寄存器带有他们自己的算术单元操作指令;

- 有3个外部可屏蔽用户中断;

- · 68 脚 PGA 阵列封装;

- · 具有 DMA 操作功能;

- · 当允许流水线操作时,重复指令能充分利用程序空间;

- · 具有 16 个输入和 16 个输出通道;

- · 采用 2.4 μm NMOS 工艺。

- · 200ns 的指令周期。

## 二、TMS32020 引脚及信号

### 1.TMS30020 引脚及信号

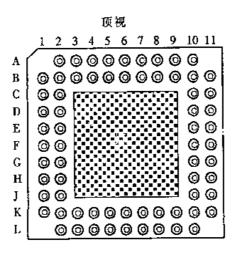

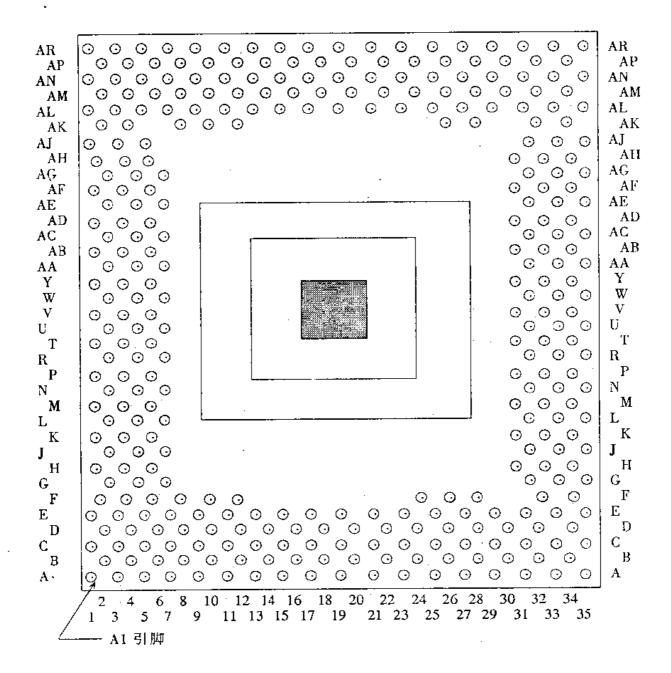

TMS32020 是 68 引脚 PGA 阵列封装。图 3 – 1 为 TMS32020 微处理器的引脚排列,表 3 – 1 是引脚/信号位置表。表 3 – 2 列出了 TMS32020 的信号状态及功能。

图 3-1 TMS32020 引脚排列

表 3-1 引脚信号

| 引開  | 信号                 | 引脚  | 信号      | 引脚  | 信号       | 引脚  | 信号   | 引舞  | 信号                       |

|-----|--------------------|-----|---------|-----|----------|-----|------|-----|--------------------------|

| A2  | D8                 | B6  | D15     | E1  | D2       | H10 | STRB | K9  | A14                      |

| А3  | D10                | В7  | BIO     | E2  | Di       | H12 | R∕W  | K10 | $\overline{\mathrm{DS}}$ |

| Λ4  | D12                | B8  | READY   | E10 | HOLDA    | J1  | DR   | KH  | Vss                      |

| A5  | D15                | B9  | CLKR    | EII | DX       | J2  | FSR  | 12  | Vss                      |

| Λ6  | Vec                | B10 | Vec     | F1  | DO       | 110 | ΡS   | 1.3 | A2                       |

| A7  | HOLD               | B11 | TACK    | F2  | SYNC     | 111 | īs   | 1.4 | Α4                       |

| Α8  | $\overline{ m RS}$ | Cl  | D6      | F10 | FSX      | k1  | A0   | 5.ا | A6                       |

| A9  | CLKX               | C2  | D5      | F11 | X2/CLKIN | К2  | Al   | 1.6 | Vec                      |

| A10 | Vec                | C10 | MSC     | G1  | OFAI     | К3  | A3   | 1.7 | Α9                       |

| BI  | Vss                | C11 | CLKOUTI | G2  | ÎÑTÎ     | K4  | A5   | 1.8 | A11                      |

| B2  | D7                 | DI  | D4      | G10 | XI       | K5  | Α7   | 1.9 | A13                      |

| В3  | D9                 | D2  | 1)3     | GH  | BR       | К6  | A8   | L13 | A15                      |

| B4  | DH                 | 010 | CLKOUT2 | HII | ĬÑTZ     | K7  | A10  |     |                          |

| B5  | D13                | DI  | XF      | H12 | Vee      | 8.3 | A12  |     |                          |

表 3-2 TMS32020 引脚信号说明

|       | 信号               | U0/Z                 | 说明                                                                                 |

|-------|------------------|----------------------|------------------------------------------------------------------------------------|

| 地 址 / | A15(MSB) A0(LSB) | 0/Z                  | 并行地址总线。多路复用寻址外部数据/程序存储器<br>或 I/O。保持方式时呈高阻抗状态。                                      |

| 数据总线  | D15(MSB)         | L/O/Z                | 并行数据总线。多路复用,在 TMS32020 和外部数据/程序存储器或 I/O 器件之间传送数据。当不输出或者当RS或HOLD信号有效时,呈高阻抗状态。       |

|       | DS<br>PS<br>IS   | 0/Z                  | 数据、程序和 I/O 空间选择信号。通常呈高电平状态。<br>保持方式呈高阻抗状态。                                         |

| 端口控   | READY            | I                    | 数据准备好输入。若外部器件未准备好,则 TMS32020<br>等待一个周期并再次检测 READY,在 BR信号之后,<br>READY 向一个外部器件表示总线许可 |

| 制信号   | R∕W              | 0/Z                  | 读/写信号。当与外部器件通讯时指定传送方向。通常在读方式(高电平),只有在执行写操作时才呈低电平。在保持方式时显高阻抗状态。                     |

|       | STRB             | 0/2                  | 选通信号。通常显现高电平。在保持方式时处于高阻<br>抗状态。                                                    |

| 多     | <del>।</del>     | 0                    | 总线请求信号。在 TMS32020 要求存取一个外部全局<br>数据存储器空间时建立。                                        |

| 位 处   | HOLD             | ı                    | 保持输入。当有效时 TMS32020 进入闲置方式并数据、<br>地址和控制总线显高阻抗状态。                                    |

| 理信    | HOLKA            | 0                    | 保持响应信号。表示 TMS32020 已经进入保持方式。                                                       |

| 号     | SYNC             |                      | 同步输入。允许两个或多个 TMS32020 的时钟同步。<br>低电平有效,必须在 CLKIN 上升沿时建立。                            |

|       | BIO              | i                    | 转移控制输入。由 IBOZ 指令查询。若为低,执行转移操作。该信号必须在 BIOZ 指令读取期间保持有效                               |

| 中     | TACK             | 0                    | 中断响应信号。仅当 CLKOUTI 为低时,其输出有效。                                                       |

| 断和其他  | INT2 INT1 I      | ]<br> <br> <br> <br> | 外部的用户中断输入                                                                          |

| 信号    | MSC              | o                    | 微状态完成信号。当刚完成一个存储器操作时变为低电平,且仅当 CLKOUTI 量低电平期间有效。                                    |

|       | RS               | Ι .                  | 复位输入。                                                                              |

|       | XF               | 0.                   | 经部标志输出(由软件转接的锁存信号)                                                                 |

|     | CLKOUTI         | j o | 主时钟输出信号                                         |

|-----|-----------------|-----|-------------------------------------------------|

|     | CLKOUT2         | 0   | 第二个时钟输出信号                                       |

| 电源  | V <sub>ce</sub> | I   | 5个5伏电源引脚,在外面连接在一起                               |

| 振荡  | V <sub>ss</sub> | I   | 3 个接地引脚, 在外面连接在一起                               |

| 器信号 | X1              | 0   | 内部振荡器到晶体的输出引脚,如不用晶体,引脚空置                        |

|     | X2/CLKIN        | ī   | 从晶体到内部振荡器的输入引脚。如果不用晶体,在<br>该引脚向器件输入时钟           |

|     | CLKR            | 1   | 接收时钟输入                                          |

|     | CLKX            | 1   | 发送时钟输入。为记录从 DXR 到 DX 引脚的为数据的外部时钟信号。当使用串行口时,必须出现 |

|     | DR              | I   | 数据接收输入端。串行数据经 DR 引脚接收到 DRR 中                    |

| 口信号 | DX              | 0/Z | 数据发送输出端。串行数据从 DXR 经 DX 引脚发出。<br>不发送时呈高阻状态       |

|     | FSR             | 1   | 接收帧同步脉冲输入端。                                     |

|     | FSX             | I/O | 发送帧同步脉冲输入/输出端。                                  |

(1/0/2,表示输入/输出/高阻状态)

# 3.2 TMS32020 硬件结构

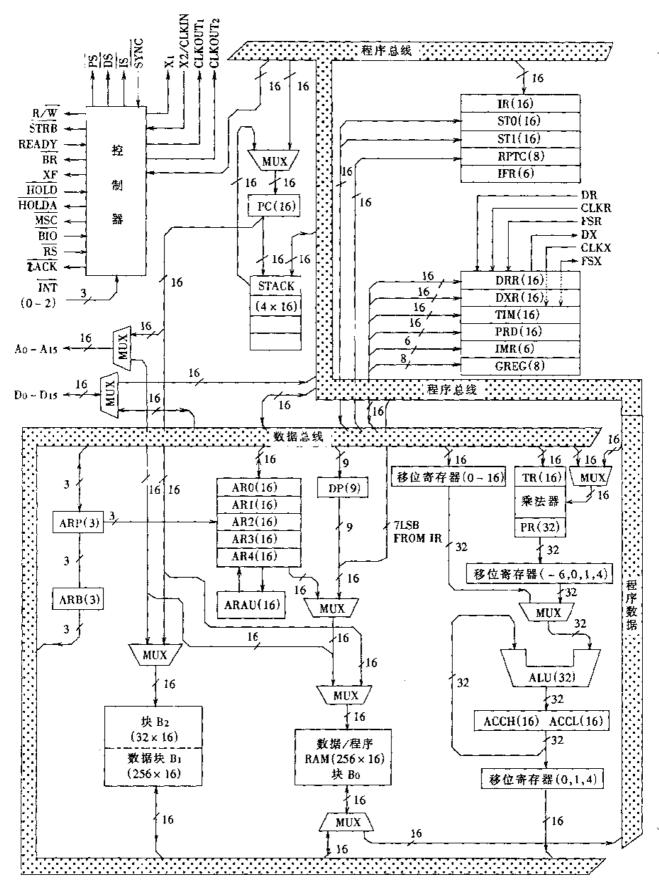

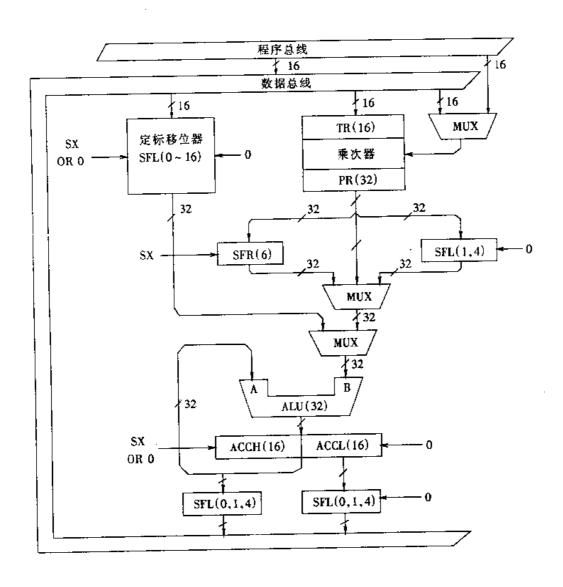

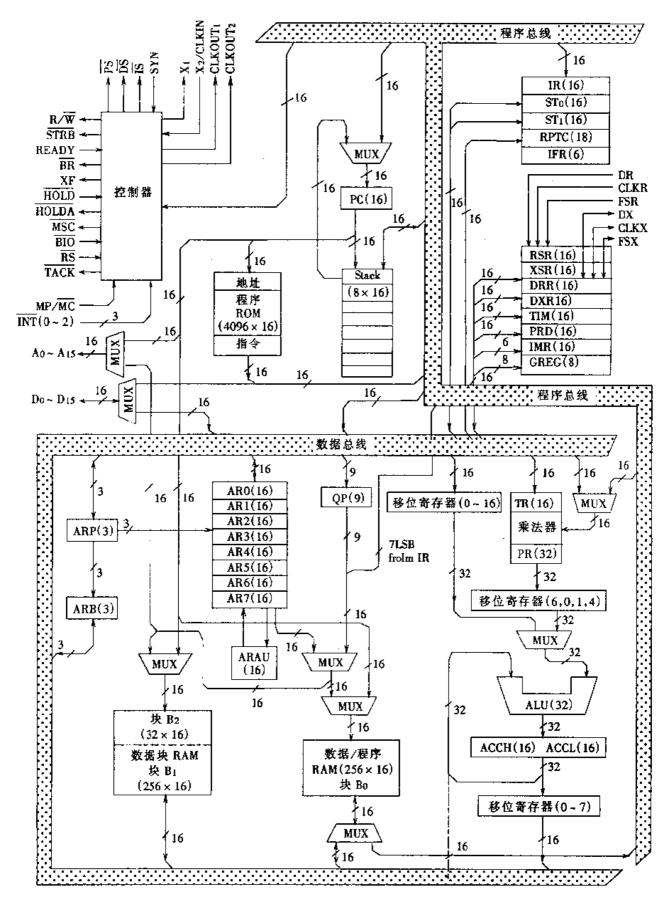

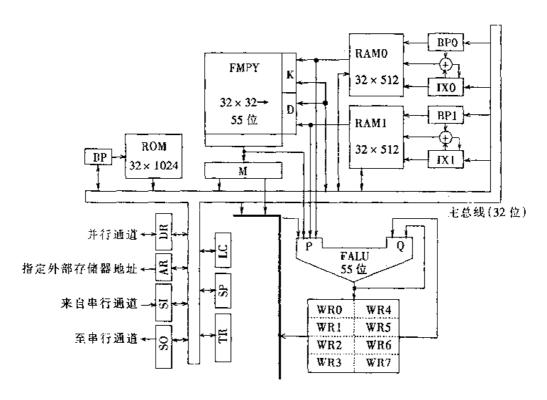

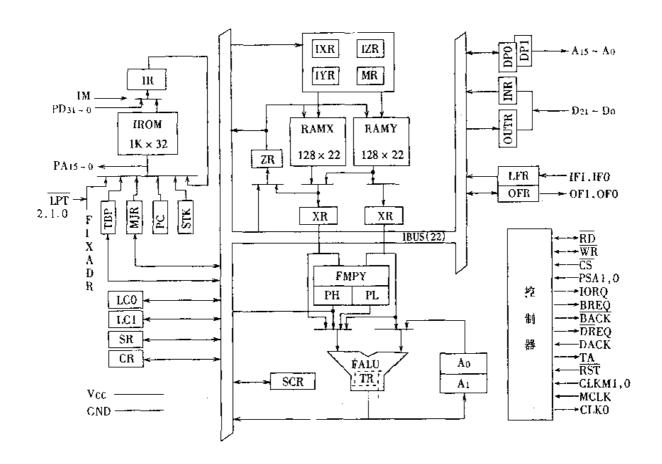

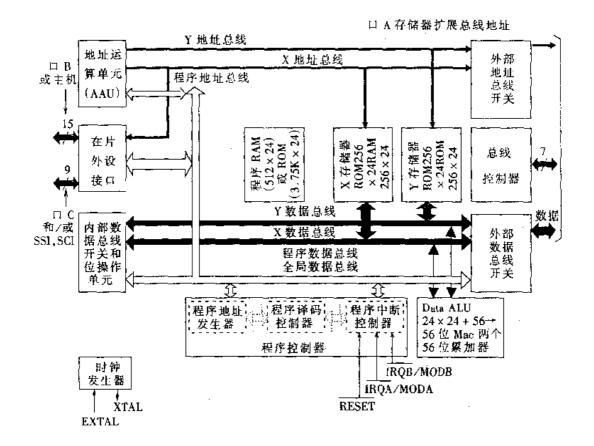

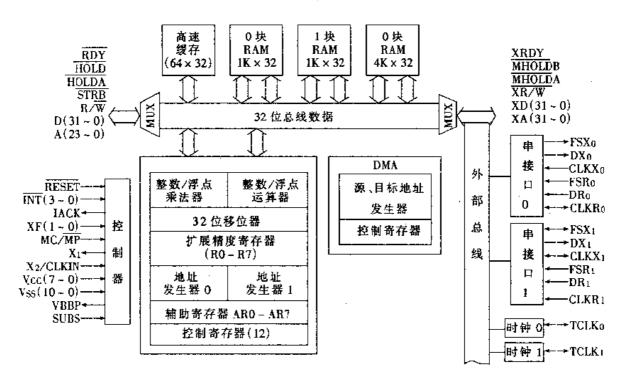

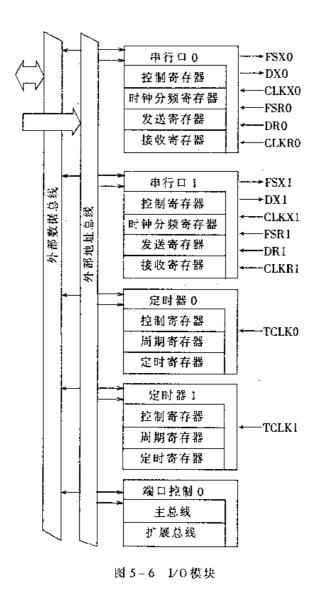

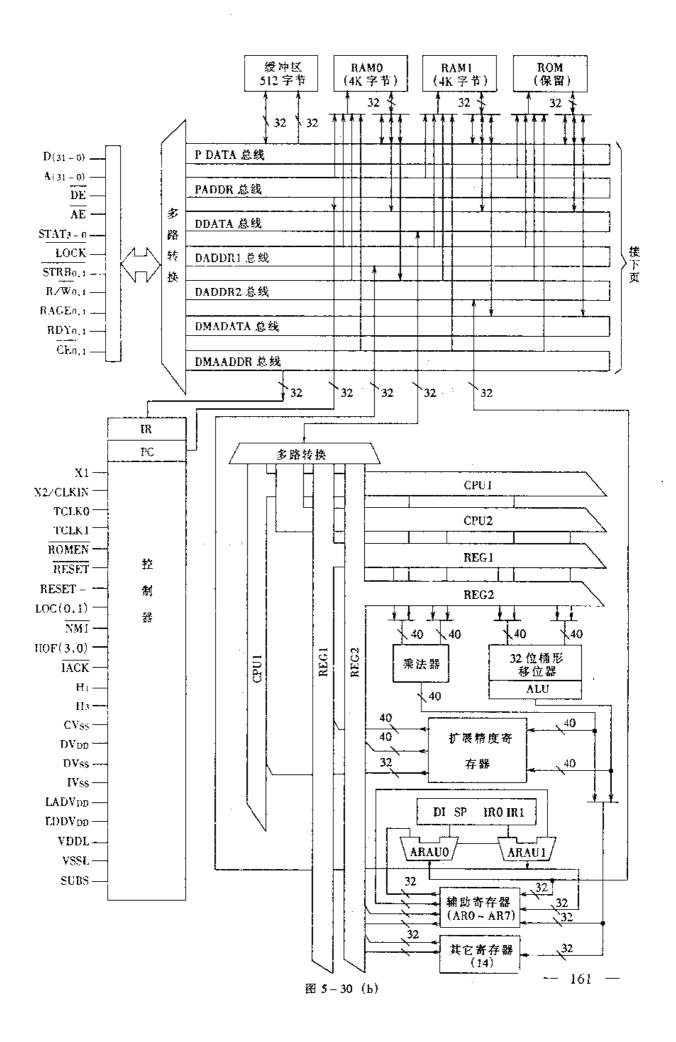

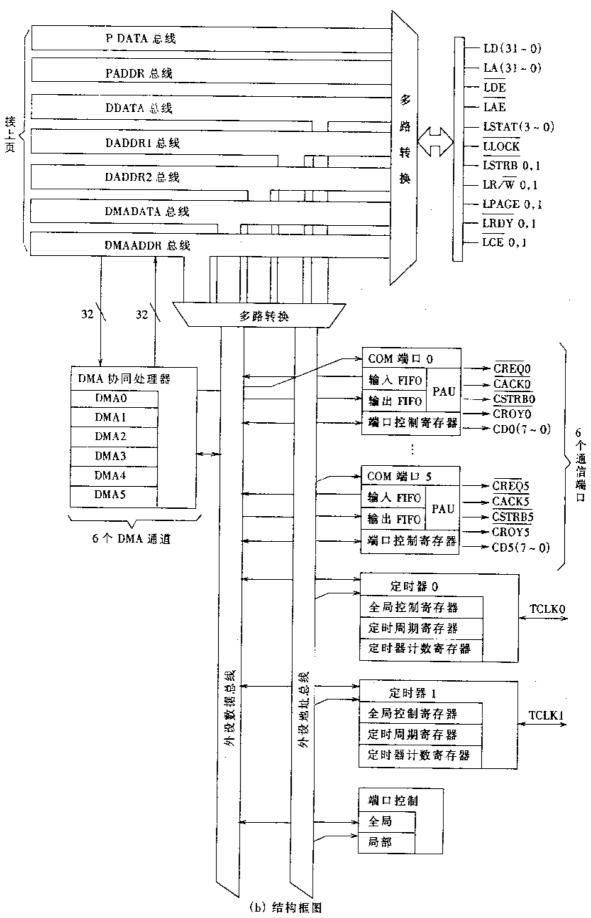

TMS32020 芯片的功能框图如图 3-2 所示。

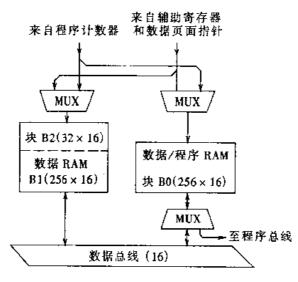

TMS32020 的结构是围绕着两条主要的总线建立的。程序总线传送来自程序存储器的指令代码和立即操作数。数据总线将中央算术逻辑单元 (CALU)和辅助寄存器堆等部件互连到数据 RAM。程序总线和数据总线一起可在单个周期内将来自两个片内 RAM 块的数据传送给乘法器进行乘法/累加操作。

TMS32020 具有高度并行性, 当数据正由 CALU 执行的同时, 还可以在辅助寄存器算术单元(ARUA)中实现算术运算。这种并行性使算术, 逻辑和位操作运算均可在单个机器周期内完成。

图 3-2 TMS32020 功能框图

图 3-2 中各符号说明如下:

ACCL 累加器低 16 位; 累加器高16位; ACCH 辅助寄存器指针缓冲器; 辅助寄存器算术单元; ARB ARAÜ 数据存储器页指针; ARP 辅助寄存器指针; DP 串行口数据发送寄存器; 串行口数据接收寄存器; DXR DRR 中断标志寄存器; 全局存储器定位寄存器; IFR GREG 重复指令计数器; 中断屏蔽寄存器; RPTC IMR P寄存器: PR 指令寄存器; IR 关于定时器的周期寄存器; 定时器; TIM PRD T暂时寄存器; STO、ST1 状态寄存器 TR

#### 一、内部硬件及功能

TMS32020 用内部硬件实现其他处理器通常用软件或微码完成的功能。例如,它包含用于 16×16 位单周期乘法、数据移位和地址操作的硬件。TMS32020 内部硬件的概要如表 3-3。

表 3-3 内部硬件功能

|    | 单 元                | 符号                                | 功 能                                                                 |

|----|--------------------|-----------------------------------|---------------------------------------------------------------------|

|    | 算术逻辑单元             | ALU                               | 32 位补码算术逻辑单元,有两个 32 位输入口,一个 32 位输出口馈给累加器                            |

|    | 中央算术逻辑单元           | CALU                              | ALU、乘法器、累加器和定标器的集合                                                  |

| :  | 乘法器                | MUL                               | 16×16 位并行乘法器                                                        |

| 处  | 周期寄存器              | PRD                               | 用于重新装入定时器的存储映射 16 位寄存器                                              |

|    | 程序计数器              | PC                                | 一个 16 位程序计数器,用于寻址程序存储器,当用块传送和乘法/累加指令时,还用于寻址数据存储                     |

| 理  | 随机存取存储器(数<br>据或程序) | RAM(BO)                           | 256 字×16 位的 RAM 块,可配置为数据或程序存储器                                      |

|    | 随机存取存储器(仅<br>数据)   | RAM(B1)                           | 数据 RAM 块                                                            |

| 部  | 随机存取存储器(仅<br>数据)   | RAM(B2)                           | 数据 RAM 块                                                            |

| 44 | 辅助寄存器算术单<br>元      | ARAU                              | 16 位无符号算术单元,用来对辅助寄存器<br>数据进行运算                                      |

| i  | 重复计数器              | RPTC                              | 8位计数器,用于控制单一指令的重复执行                                                 |

| 件  | 移位器                | SFL,SFR                           | 移位器 SFL(左移)和 SFR(右移)置于 ALU<br>输入端,累加器输出端和乘积寄存器输出<br>端。累加器内还有一个就地移位器 |

|    | 定时器                | ТІМ                               | 存储器映射 16 位定时器(计数器),用于定时控制                                           |

|    | 累加器                | ACCH<br>(31 ~ 16)<br>ACCL(15 ~ 0) | 32 位累加器分为两半, ACCII 和 ACCL, 用于存储 ALU 的输出                             |

|                                       | <b>補助寄存器指针</b>       | ARP(2-0)    | 一个 3 位寄存器,用于选择五个辅助寄存器中的一个                                                               |  |  |  |  |

|---------------------------------------|----------------------|-------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 辅助 寄 存 器 指 针 缓<br>冲器 | ARB(2~0)    | 用于缓冲 ARP 的 3 位寄存器。除了在执行 LST 指令周期外,每次装入 ARP,老的值就被写人 ARB。当用 LSTI 指令装入 ARB时,相同的值也被复制到 ARP中 |  |  |  |  |

|                                       | 数据存储器页指针             | DP(8-0)     | 9 位寄存器,指向当前页地址。                                                                         |  |  |  |  |

| 光                                     | 全局存储器定位寄<br>存器       | CREG(7~0)   | 存储器映射的 8 位寄存器。用来确定全局<br>存储器空间的容量                                                        |  |  |  |  |

|                                       | 指令寄存器                | IR(15~0)    | 16 位寄存器,用来存储目前正执行的指令                                                                    |  |  |  |  |

| 存                                     | 中断标志寄存器              | IFR(5 ~ 0)  | 6 位标志寄存器,用于锁存以低有效的外部用户中断 INT(2-0) 及内部中断 XINT/RINT和 TINT。IFR 不能通过软件存取                    |  |  |  |  |

|                                       | 中断屏蔽寄存器              | IMR(5 - 0)  | 存储器映射的6位寄存器,用于屏蔽中断                                                                      |  |  |  |  |

|                                       | 乘积寄存器                | PR(31~0)    | 32 位寄存器,容纳乘法器的乘积                                                                        |  |  |  |  |

| HS<br>기업                              | 堆栈                   | STACK       | 4×16 硬堆栈, 在中断或调用期间用米存储 PC.ACCL和数据存储器值也可以压入<br>或弹出堆栈                                     |  |  |  |  |

|                                       | 申行口 数据接收寄<br>存器      | DRR(15 ~ 0) | 存储器映射的 16 位串行口数据接收寄存器。字节方式时只使用低 8 位                                                     |  |  |  |  |

|                                       | 串行口发送寄存器             | DXR(15~0)   | 存储器映射的 16 位申行口数据发送寄存器。在字节方式时只用低 8 位                                                     |  |  |  |  |

|                                       | 状态寄存器                | STO, STI    | 两个 16 位状态寄存器,包含状态位和控制<br>位                                                              |  |  |  |  |

|                                       | 暂存寄存器                | TR(15~0)    | 16 位寄存器,保存乘法器的一个操作数或<br>关于定标移位器的移位代码                                                    |  |  |  |  |

|                                       | 辅助寄存器堆总线             | AFB(15 ~ 0) | 16 位总线, 传送由 ARP 指定的 AR 来的数据                                                             |  |  |  |  |

| 总                                     | 数据总线                 | DB(15 ~ 0)  | 流通数据的 16 位总线                                                                            |  |  |  |  |

|                                       | 数据存储器地址总线            | DAB(15 ~ 0) | 16 位总线,传送数据存储器地址                                                                        |  |  |  |  |

| 线                                     | 直接数据存储器地址总线          | DRB(15 ~ 0) | 16 位总线, 为数据存储器传送"直接"地址, 它是 DP 寄存器与指令字低 7 位的级联                                           |  |  |  |  |

| 叔                                     | 程序总线                 | P(15~0)     | 流通指令的 16 位总线                                                                            |  |  |  |  |

|                                       | 程序存储器地址总线            | PAB(15~0)   | 16 位总线,传送程序储器地址                                                                         |  |  |  |  |

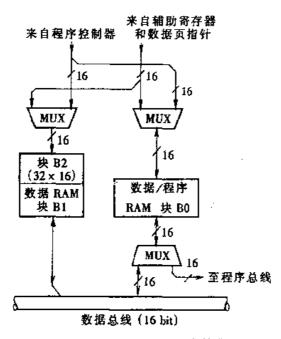

#### 二、存储器、寄存器、堆栈

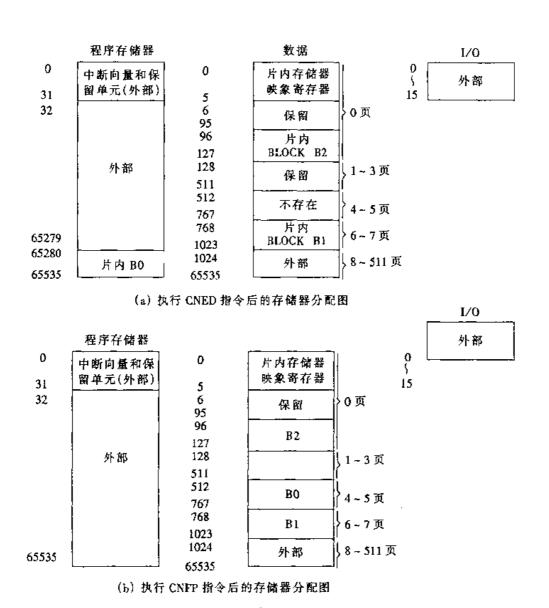

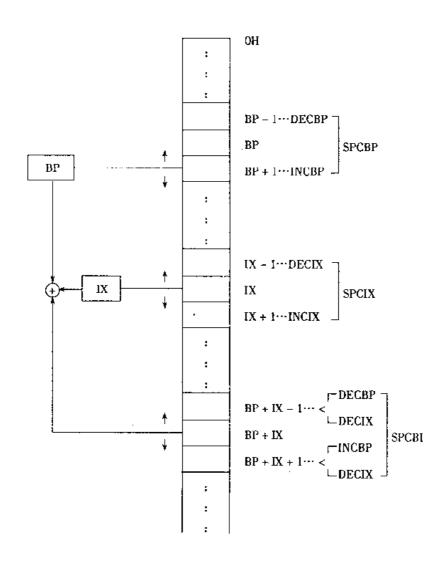

TMS32020 内部配置有 544 字的片内数据存储器 RAM, 并分成三个独立的块(B0、B1 和 B2),如图 3-3 所示。块 B0(256 字)可以用作数据或程序存储器,块 B1 和 B2 只用做数据存储 器。数据存储器容量允许 TMS32020 处理 512 字的数组(如果片内 RAM 用作程序存储器,则是 256字的数组),留下的32个单元作中间存储。当块B0用作程序存储器时,可用RPTK和 BLKP 指令将程序从外部程序存储器装入 BO 块。

图 3-3 片内数据存储器

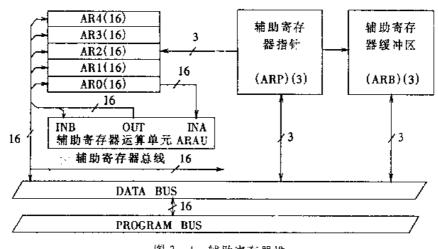

TMS32020 提供一个包含 5 个辅助寄存器(ARO~AR4)的寄存器堆。辅助寄存器可用于数 据寄存器的间接导址,或作为数据暂存器。间接辅助寄存器寻址允许将指令操作数据的数据 存储器地址放在某个辅助寄存器。这些寄存器由一个3位辅助寄存器指针(ARP)指定。该指 针可装入 0,1,2,3 或 4,分别指定 AR0~AR4。可以任意地将数据存储器中的数或指令中定义 的立即操作数装入辅助寄存器和 ARP。这些寄存器的内容也可以存到数据存储器中。

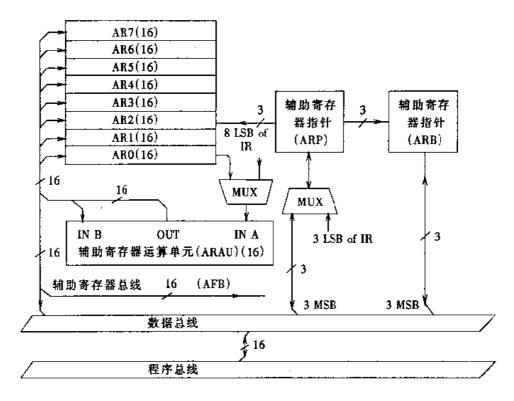

辅助寄存器堆(AR0 - AR4)连接到 ARAU(辅助寄存器算术单元),如图 3 - 4 所示。

图 3-4 辅助寄存器堆

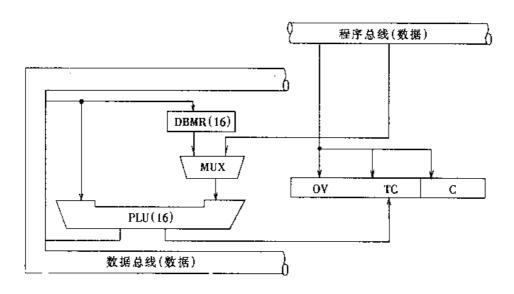

当数据存储器单元正被寻址时,ARAC可自动变址当前辅助寄存器。可以±1变址,或者相对于ARO的内容变址。TMS32030为程序存储器、数据存储器和1/0提供了三个独立的地址空间(图 3-5)。并在外部由下S、DS和TS信号进行空间选择。TMS32020提供了可实现数据块和程序块的存储器一存储器传送功能的指令,以进行片内或片外存储器的块传送。

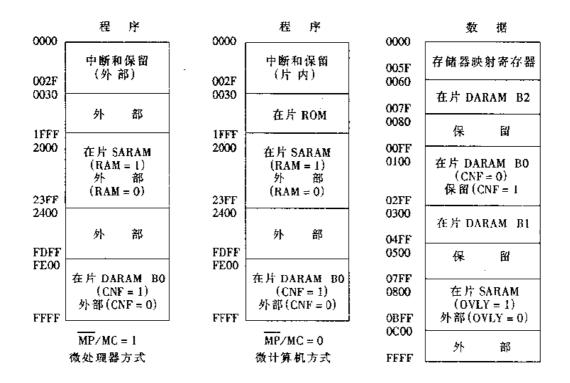

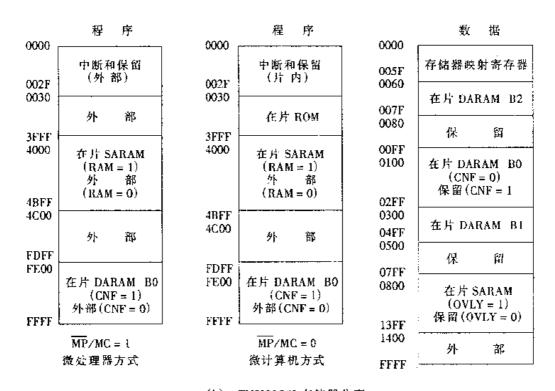

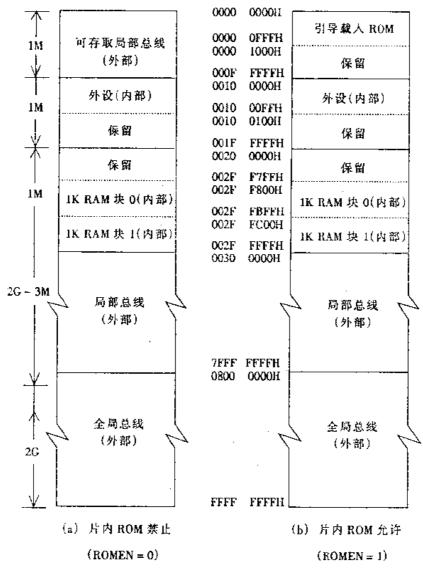

图 3-5 存储器分配图

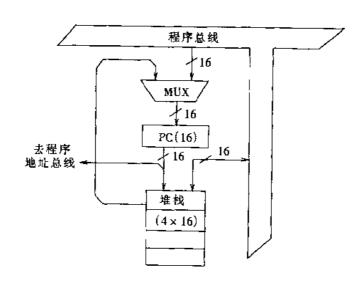

TMS32020 有一个 16 位程序计数器(PC)和一个用来存储 PC 的 4 个单元的硬堆栈(图 3 - 6)。在取指时程序计数器寻址内部和外部程序存储器;在中断、子程序调用以及某些有两地址操作的专用指令期间使用堆栈。

程序计数器经过程序地址总线(PAB)寻址片内或片外程序存储器。通过 PAB 从程序存储器取出指令并装入指令寄存器(IR)后。PC 就准备开始下一个取指周期。当块 B0 用作程序存

储器时,PC 可寻址块 BO,或者通过地址总线 A15~A0 和外部数据总线 D15~D0 寻址片外程序存储器。

程序计数器在 BLKD 指令期间还寻址数据存储器,该指令从数据存储器的某一段向另一段传送数据块。

图 3-6 程序计数器和堆栈

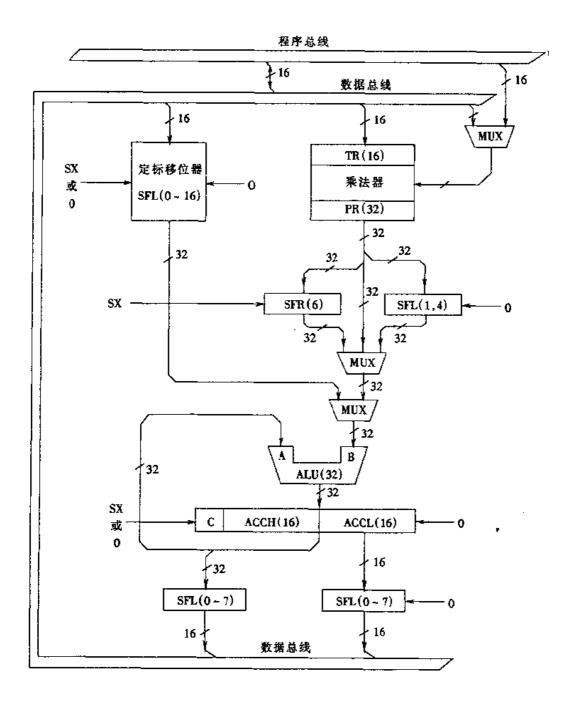

### 三、中央算术逻辑单元(CALU)

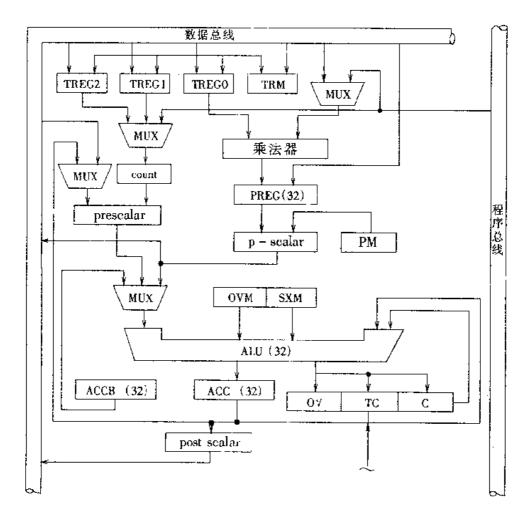

TMS32020 的中央算术逻辑处理单元(CALU)包含一个 16 位定标移位器、一个 16×16 位并联乘法器、一个 32 位算术逻辑单元(ALU)、一个 32 位累加器(ACC)和累加器与乘法器输出端附带的一些移位器。如图 3-7 所示。典型的 ALU 指令执行算术操作;结果送到累加器。

ALU的一个输入总是来自累加器,而另一个输入则由乘积寄存器(PR)或定标移位器馈给,定标移位器的输入来自数据存储器。TMS32020 定标移位器的 16 位输入连接到数据总线,32 位输出连接到 ALU。定标移位器依照指令产生 0 到 16 位左移。TMS32020 还包含另外几个移位器,允许它执行数字定标、位抽出、扩展算术运算和防止溢出。这些移位器连接到乘法器和累加器的输出端。TMS32020 有 32 位算术逻辑单元(ALU)和累加器,可以执行算术和逻辑指令,大多数指令是在单个时钟周期内执行的。输入 ALU 的数据可由定标移位器定标。TMS32020 执行由 ALU 状态确定的转移指令支持浮点操作。为把数据存到数据存储器中,32位累加器分成两段,每段 16 位,ACCH(累加器高 16 位)和 ACCL(累加器低 16 位)。在累加器的输出端附加了一个可左移 0,1 或 4 位的移位器。这种移位是在数据向数据总线传送准备存储时完成的。累加器还有一个就地 1 位移位,用来使累加器的内容左移或右移 1 位。TMS32020 有一个补码 16×16 位硬件乘法器,它能够在单个机器周期内计算得到 32 位乘积。两个寄存器是和乘法器联系在一起;一是 16 位暂存寄存器(TR),保存乘法器的一个操作数。另一个是 32 位乘积寄存器(PR),保存乘积。

通常由 LT(装入 T 寄存器)指令将数据总线上的数据装入 TR,为乘法器提供一个操作数, 面 MPY(乘法)指令提供另一个操作数(也来自数据总线)。在这种情况下,每两个周期得到一个乘积。

两个 16 位补码数相乘以后,32 位乘积装进 32 位乘积寄存器(PR)。P 中的乘积可以直接。传送给 ALU,或者也可以在送到 ALU 之前先经过移位。

图 3-7 中央算术逻辑单元

乘积移位方式(PM)有 4 种。状态寄存器 STI 的 PM 字段规定 PM 移位方式,如表 3-4 所示。

表 3-4 PM 移位方式

| PM值 | 结 | 果     |

|-----|---|-------|

| 00  |   | 移位    |

| 01  | 左 | 移1位   |

| 10  | 左 | 移 4 位 |

| 11  | 右 | 移6位   |

T寄存器(TR)的低 4 位为 LACT/ADDT/SUBT(装入累加器/加到累加器/从累加器减,包含一 46 一

由 TR 规定的移位)指令规定通过定标移位器的移位。这些指令用在浮点算术运算中。位测试指令(BITT)允许根据 TR 中低 4 位的值测试数据存储器中一个字的某一位。

#### 四、系统控制

TMS32020 通过片内定时器、重复计数器、3 个外部可屏蔽中断、由串行口操作或定时器产生的内部中断以及外部复位信号提供控制操作。

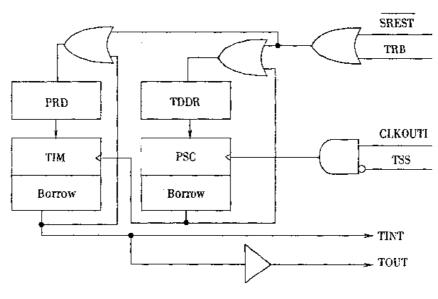

TMS32020 提供一个存储器映射 16 位定时器和一个片内定时寄存器(TIM)。它是一个减计数器,由一个内部时钟连续减 1。这个内部时钟是对 CLKOUTI 4 分频得到的。复位将定时器置为最大值(> FFFF)但并不对周期(PRD)寄存器初始化。复位信号释放后,定时器开始减量。以后,在程序控制下可重新装入定时器或周期寄存器。每当定时器减到零,就产生定时中断。在定时器减到零的同一周期内,可用周期寄存器(PRD)中的值重新装入定时器。这样可以通过编程使中断以 4×(PRD)×CLKOUTI 为周期等间隔地出现。这种情况对于同步采样或向外围设备同步输出是很有用的,可以在任何时候对定时寄存器(TIM)和周期寄存器(PRD)进行存取。周期寄存器的值不能为零。如果不用定时器,定时器中断应被屏蔽,或者用 DINT 指令禁止所有的可屏蔽中断。

TMS32020 的设计包括一种重复特性,它允许一条指令最多可重复执行 256 次。它可将数据存储器的值(用 RPT 指令)或一个立即数(用 RPTK)装入重复计数器(RPTC)。该操作数之值应比下一条指令被执行的次数小 1。重复特性可在乘法/累加、块传送、I/O 传送和表格读/写这样一些指令中使用。

TMS32020提供3个外部的可屏蔽用户中断(INT2~INT0),由外部器件用来中断处理器。内部中断由串行口、定时器和软件中断指令产生。中断有优先级,复位有最高优先级,而串行口发送中断有最低优先级。所有的中断单元都在两字的边界,如果需要可在那些单元中安排转移指令。

RS信号使 TMS32020 中止执行并强制使程序计数器为零。RS影响各种寄存器和状态位。当接通电源时,处理器的状态是不确定的。为了通电后的系统操作,必须建立复位(RS)信号至少3个时钟周期以确保器件复位。处理器从0单元开始执行。0单元中通常包含一条转移(B)指令,把程序执行转向系统初始化程序。

TMS32020 有两个状态寄存器 STO 和 STI,包含各种条件和方式的状态。用 SST 和 SSTI 指令把状态寄存器的内容存进数据存储器中。而用 IST 和 ISTI 指令从数据存储器装入状态寄存器。使用这种方法可在中断和子程序调用时保存器件的当前状态。

#### 五、外部接口

TMS32020 三个独立的数据、程序和 I/O 地址空间提供了到存储器和 I/O 的接口,局部存储器接口包括:

- ·16 位并行数据总线(D15 ~ D0)。

- ·16 位地址总线(A15~A0)。

- ·数据、程序和 I/O 空间选择信号(DS、PS和IS)。

- ·各种系统控制信号。R/W 信号控制传送方向,而STRB提供定时信号来控制传送。

TMS32020 用和存储器相同的方法处理 I/O 器件,利用处理器的外部地址和数据总线把 I/O 器件映射到 I/O 地址空间。

用 READY 线来完成与各种不同速度的存储器和 I/O 器件接口。当与较慢的器件通信时, TMS32020 处理器进行等待,直到那个器件完成它的功能并经过 READY 线向处理器发出信号为止。然后 TMS32020 继续工作。

申行口用来与申行器件直接通讯,如编码译码器、申行 A/D 转换器和其他申行系统。接口信号是与编码译码器和许多其他申行器件兼容的。只需要很少的外部硬件,申行口还可在多道处理应用中用于处理器之间的交互通信。

TMS32020 的灵活性使它能满足广泛的系统需要。使用 TMS32020 的一些系统配置如下:

- ·独立自主的系统(单个处理器)。

- ·共享全局数据存储器的主/从式或并行多道处理系统。

- ·使用接口控制信号的主/外围式协同处理器配置。

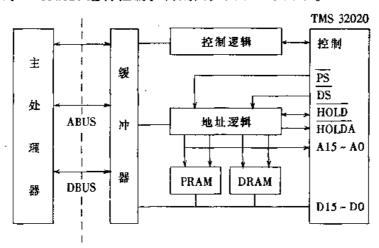

在多道处理应用中,TMS32020 能定位全局数据存储器空间,并通过BR(总线请求)和READY 控制信号与该空间通信。全局存储器是由一个以上处理器共享的数据存储器。全局数据存储器存取必须经过仲裁。

在多道处理器环境中,使用SYNC输入可极大地简化处理器间的接口。该输入用来使系统 中每个 TMS32020 的内部时钟同步,因此允许多个处理器同步地运行。

TMS32020 用HOLD和HOLDA(保持响应)信号支持它的外部程序/数据存储器的 DMA(直接存储器存取)。另一个处理器通过向HOLD送一个"低",可以完全控制 TMS32020 的外部存储器。这使 TMS32020 的地址、数据和控制总线处于高阻抗状态。

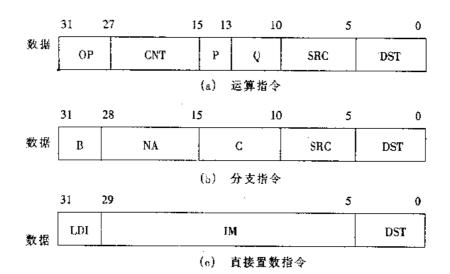

# 3.3 TMS32020 的指令系统

#### 一、存储器等址方法

TMS32020指令系统支持三种存储器寻址方式、即直接寻址方式、间接寻址方式和立即寻址方式。

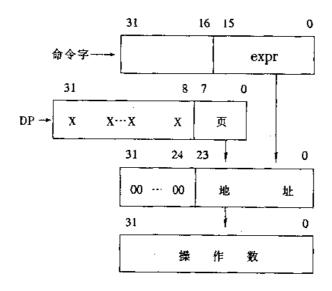

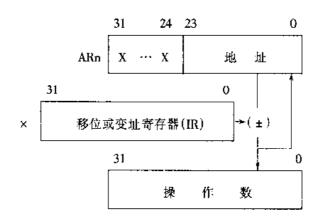

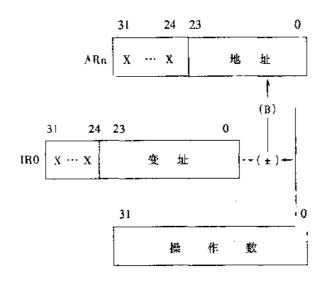

#### 1 直接基址方式

在直接寻址方式中,指令字包含数据存储器地址的低 7 位,该字段与 9 位数据存储器页面指针(DP)寄存器衔接,形成完整的 16 位数据存储器地址。除了 CALL 指令、转移指令、立即数指令和无操作数指令外,直接寻址适用于所有指令。直接寻址指令格式如下:

| 15 | ]4 | 13 | 12  | 11       | 10           | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1 | 0 |

|----|----|----|-----|----------|--------------|---|---|---|---|---|---|------|------|---|---|

| -  |    | 操作 | 码 - | <u>.</u> | <del>-</del> |   |   | 0 |   |   |   | - dn | na – |   |   |

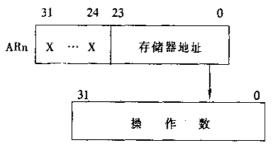

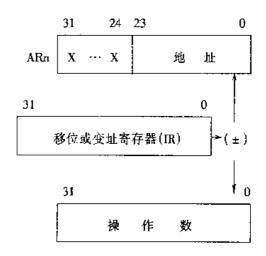

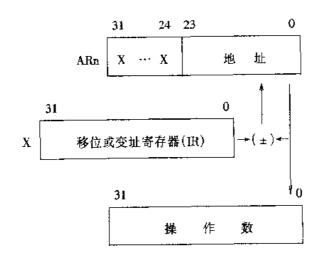

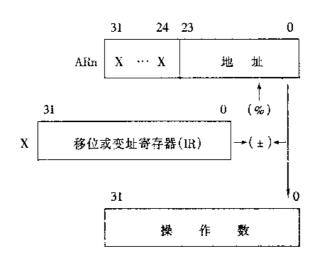

#### 2.间接寻址方式

TMS32020 通过辅助寄存器 AR0—AR4 能够灵活方便地完成间接寻址。为了选中一个辅助寄存器,将 0—4 中指定的数字装入辅助寄存器指针(ARP)即可。

在间接寻址中,64K 字数据存储器空间中的任何单元都可以用辅助寄存器内容的 16 位地址进行存取。用 LAR、LARK 或 LRLK 指令可以装入需要的数据存储器地址。通过 MAR 指令或指令字中的修改辅助寄存器指针内容来改变辅助寄存器指针。

间接寻址方式中常用下列符号:

\* AR(ARP) 当前内容作为数据存储器地址。

- \* AR(ARP) 当前内容作为数据存储器地址,在数据存储器存取后其内容减1、

- \* + AR(ARP) 当前内容作为数据存储器地址,在数据存储器存取后其内容加 1。

- \*0- AR(ARP) 当前内容作为数据存储器地址,存储器存取后,其内容减 ARO 内容。

- \*0+ AR(ARP) 当前内容作为数据存储器地址,数据存储器存取后,AR内容加上ARO的内容。

在间接寻址方式中包含两种变址型间接寻址,即加1和减I的简单变址型间接寻址和基于 ARO 值的变址型间接寻址。在两种情况中,由 ARP 寄存器指定的辅助寄存器内容用作数据存储器操作的地址。随后 ARPU 对指定的辅助寄存器进行算术操作。另外,间接寻址方式的指令可以装入一个新的 ARP 值。间接寻址可以和除了立即数指令、无操作数指令之外的所有指令一起使用。间接寻址字段如表 3-5 所示。间接寻址格式如下:

| 15           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4   | 3   | 2 | 1 | 0    |

|--------------|----|----|----|----|----|---|---|---|-----|-----|-----|-----|---|---|------|

| <del>-</del> |    | 操作 | 乍码 |    |    | · |   | 0 | IDA | INC | DEC | NAR |   | - | lma→ |

位 3 = 1 则将位 0~位 2 的内容装入 ARP。

位 3=0 则 ARP 指针的内容保持不变。

位 4(DEC) 控制辅助寄存器减 1。当位 4=1 时,ARP 指定的辅助寄存器减 1,当

位 4=0 时不减。

位 5(INC) 控制辅助寄存器增 1。当位 5=1 时,ARP 指定的辅助寄存器增 1,当

位 5=0 时不增。

位 6(IDV) 决定变址的类型。位 6=0 时,当前辅助寄存器加 1 或减 1,位 6=1

时, 当前辅助寄存器加或域 ARO。

位7 位7~1表示指令为间接寻址的方式。

位 8~位 15 指令操作码。

表 3-5 间接寻址字段表

|              | 指          | 令 字          | 段 位     |                     | 符号     | 操                                 | 作          |

|--------------|------------|--------------|---------|---------------------|--------|-----------------------------------|------------|

| 15 14        | 13 12 11 1 | 0 9 8 7      | 6 5 4 3 | 2 1 0               |        |                                   |            |

| ←—           | OPCODE     | <b>→ 1</b>   | 0 0 0 0 | <b>←</b> Y <b>→</b> | *      | NOmanipulation of ARS/            | /ARP       |

| <del>-</del> | OPCODE     | <del></del>  | 0 0 0 1 | <b>-</b> Y →        | * ,Y   | Y→ARP                             |            |

|              | OPCODE     | 1            | 0 0 1 0 | <b>←</b> Y <b>→</b> | *      | $AR(ARP) - 1 \rightarrow AR(AR$   | IP)        |

| <b>-</b>     | OPCODE     | <b>-</b> →1  | 0 0 1 1 | <b></b> Y →         | * - ,Y | AR(ARP) - 1→AR(AR                 | P) Y→ARP   |

| <b>-</b>     | OPCODE     | —→ 1         | 0 1 0 0 | <b>←</b> Y →        | * +    | AR(ARP) + 1-+AR(AR                | IP)        |

| <b>-</b> -   | OPCODE     | <b>-</b> →1  | 0 1 0 1 | <b>←</b> Y →        | * + ,Y | $AR(ARP) + 1 \rightarrow AR(ARP)$ | P) Y→ARP   |

| <b>←</b> —   | OPCODE     | <b>-</b> → 1 | 1 0 1 0 | <b>←</b> Y →        | * 0 -  | AR(ARP) – ARO→AR(                 | ARP)       |

| <del></del>  | OPCODE     | <b></b> → 1  | 1 0 1 1 | <b>←</b> Y <b>→</b> | * 0-,Y | AR(ARP) – ARO→AR(                 | ARP) Y→ARP |

|              | OPCODE     | <b>-</b> → 1 | 1 1 0 0 | <b>-</b> Y →        | * 0 +  | AR(ARP) + ARO - AR(               | ARP)       |

|              | OPCODE     | → l          | 1 1 0 1 | <b>←</b> Y <b>→</b> | *0+,Y  | AR(ARP) + ARO - AR(               | ARP) Y→ARP |

#### 3. 立即寻址方式

在立即寻址中,指令字包含立即数的值。立即数可以包含在指令字内或者在紧接操作码后面的一个字中。下列指令的指令字中包含立即数,并在单指令周期内执行。其操作数的长度由指令决定。

LACK 将短立即数装入累加器(8位绝对数)。

LARK 将短立即数装入辅助寄存器(8位绝对常数)。

LARP 装入辅助寄存器指针(3位常数)。

LDPK 将立即数装入数据存储器页面指针(9位常数)。

MPYK 乘立即数(13位二进制补码常数)。

RPTK 由立即数指定重复次数的重复指令(8位常数)。

下列立即数指令中,紧接指令操作码后面的---个字中包含 16 位常数值。16 位值可以选择作为绝对常数或二进制的补码数使用。

ADLK 长立即数经移位加到累加器(绝对的或二进制补码值)。

ANDK 立即数同累加器"与",带移位。

LALK 长立即数经移位装入累加器(绝对的或二进制补码值)。

LRLK 将长立即数装入辅助寄存器。

ORK 立即数与累加器"或",带移位。

SBLK 累加器减经移位的长立即数(绝对的或二进制补码值)。

XORK 立即数与累加器"异或",带移位。

# 二、TMS32020 指令系统

从指令的功能上看,可以把 32020 的指令划分为 6 类;即设置累加器 Acc 和数据存储器 DRAM 操作指令;有关辅助寄存器 AR 和页指针 DP 的指令;关于 TR、FR 和乘法器的指令;转移和调用的指令;有关控制、调试的指令; I/O 和 DRAM 传送的指令。实际上,这些指令完成的功能与通用处理器指令功能和似,也是包括运算逻辑、传送、判断和转移以及 I/O 功能等。

TMS32020 的 Acc 是算术逻辑运算的中心,甚至转移地址也用 Acc 内容。对于两个操作数的运算,一个隐含于 Acc,另一个为指令中的显式操作数。

显式操作数有二种可能情形。一种为立即数,有长短之分。长短立即数分别为 16 位和 8 位。另一种为 DRAM 单元。分为直接、回接寻址两种。另外,TMS32020 的一些指令也很特别,如对片外 RAM BO 块的设置、数据块传送等。

指令系统、使用符号和缩写说明见附录中的一。

#### 1、累加器、存储器指令

在这类指令中,含有加、减或异或等通用算逻指令。操作数一个为 Ace,另一个是立即数 或 DRAM 单元,结果在 Acc 中,规格化指令 NORM 对于浮点运算很有用。它把不规格化的数转变为尾数和阶码的形式。例如:

LARP 1 ;ARI 存指数

LARK 1,0 ;ARI 清 0

RPTK 14 ;15 位规格化

#### NORM ;规格化

2.辅助寄存器和页指针指令

这类指令为寻址寄存器和指针的指令。LARP、LAR 和 LDP 分别对辅助寄存器指针、辅助寄存器和 DRAM 页指针装入。

3.关于乘法的指令

这类指令中包括对 TR、PR 和 PM 的装入指令 LT、LPH 和 SPM。还有积寄存器 PR 移入 Acc 以及作积和、积差的指令 PAC 和 APAC、SPAC。乘积功能指令包括操作数在 DRAM 中的乘积 MPY、平方累加 SQRA 等以及 DRAM 与单元间的积累加 MAC 和 MACD 等。例如作积累加的程序如下:

SPM 3

;PR 累加前右移 6 位

LARP 1

LRLK 1, > 300

;ARI 指向 BI 块

CNFP

;BO 块配置为 PRAM

PR7K > FF

:重复

MAC > FF00, \* +

;积加

4.关于转移和调用指令

这类指令用于控制程序执行流程,包括无条件转移和条件转移以及调用子程序指令等。 控制条件有辅助寄存器内容和位控制以及 Acc 内容等。例如 AR2 作循环控制向一块单元中填 0 的程序如下。

LARP 1

ZAC

LARK 1, BEGIN

置 ARI 填区首址

LARK 2, NUM

;重复次数

LOOP SACL \* + ,0,2

:墳0

BANZ LOOP, \* - 1

:判断结束

调用子程序时要注意堆栈空间的限制,嵌套调用不能超过 4 层。

5.控制和测试指令

这类指令是控制和测试指令。位测试指令常用于转移指令,此类指令中还包括对处理状态的设置。用 CNFP 可把片内 BO 块 RAM 设置成程序存储器 PRAM 地址在 > FFOO 至 FFFF;用 CNFD 设置 BO 块为 DRAM,地址在 > 200 至 > 2FF。重复指令 RPT 与多周期指令连用可提高效率。例如,

RPTK > 7F

;重复 128 次

BLKD > 2000, \* +

;源首址 > 2000,目的地址

;由 AR 指出

6.1/0 和数据存储器操作、指令

这一类指令是 I/O 和 DRAM 块操作指令。输入指令 IN 将输入口(共有 16 个)的数据读入。通常开机后,第一次是起初始化作用,因而首先读两次取得可靠值。输出指令 OUT 把数据写入到输出口,共有 16 个。读表指令 TBLR 把 PRAM 中数据读入 DRAM 中。PRAM 地址由Ace 提供,DRAM 地址在指令中给出。写表指令 TBLM 方向与 TBLR 相反。

块传送指令 BLKP 和 BLKD 分别把 PRAM 和 DRAM 中数据送到 DRAM 中。它们常与 RPT 指令合用传送一块数据。值得注意的是表读写和块传送指令执行都用到堆栈。执行后会破坏原栈底数据。数据下移指令 DMOV 只能在片内 DRAM 中使用,在片外无效。

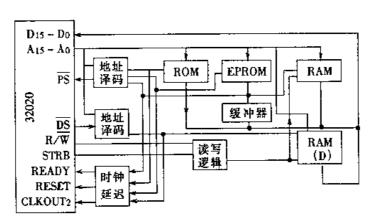

# 3.4 TMS32020 与外部设备接口

#### 一、TMS32020 与外部设备接口

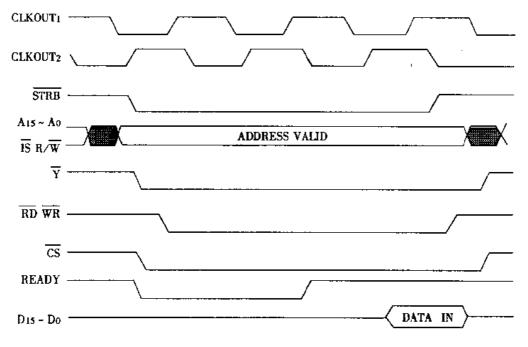

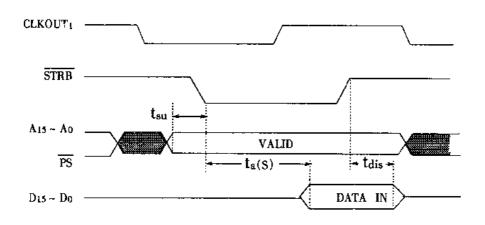

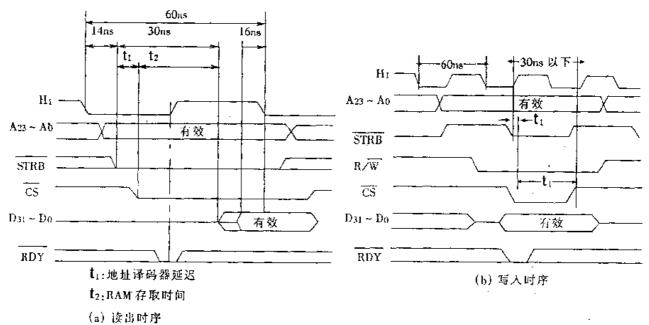

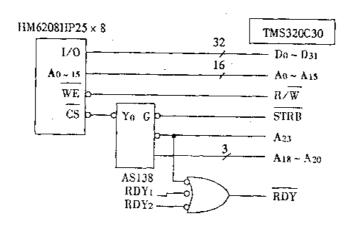

TMS32020 对外部存储器或 I/O 装置的响应速度的要求为:

读周期: 当存储器或 I/O 装置被PS、DS或IS选中后(通常是只读器件),必须在 90ns 以内给予数据响应。故所用的外部存储器或 I/O 装置必须有较快的寻址时间,否则为完成读操作需插入适当的等待状态。当用PS、DS或IS同STRB一起作为控制信号时(通常适用于读写器件),存储器或 I/O 装置必须在 STRB 变低的 50ns 之内作出响应。

写周期:TMS32020提供了50ns写数据的建立时间,若有必要,可用STRB信号产生等待状态。可以看出:TMS32020同外部存储器或1/0装置连接时,如何解决快速处理芯片与低速的被连接器件之间的时间上配合(或速度匹配)问题,是设计一个合理的接口电路的关键所在。

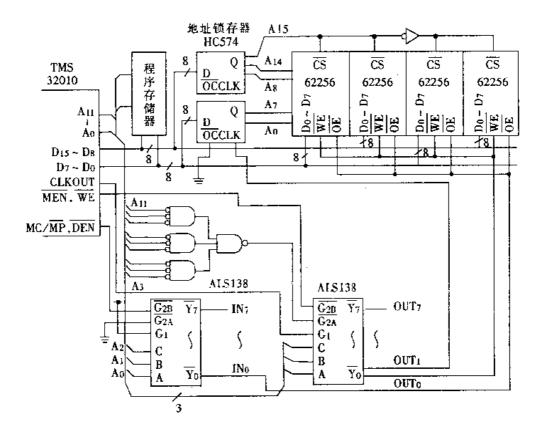

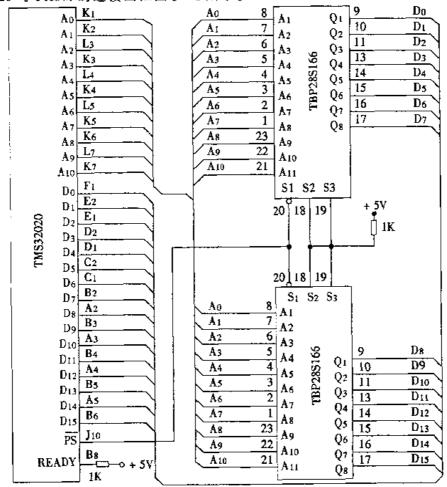

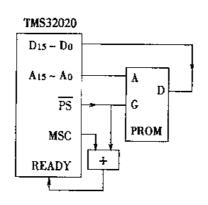

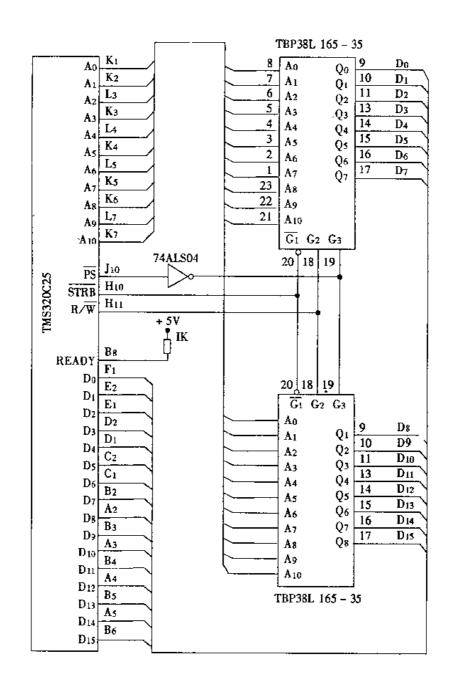

#### 1.TMS32020 与 PROM 的连接

TMS32020 与 PROM 的连接图如图 3-8 所示。

图 3-8 TMS32020 与 TBP28S166 接口

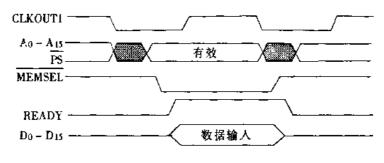

TBP28S166 是 2048 × 8 的 PROM,输出有三态,导址时间为 75ns(小于 90ns),能满足 TMS32020 衍定时要求 这里用ISF作片选信号。若一个系统中有多组存储器,可用PS作为译码器的控制信号,用几位高地址经译码器译码输出实现组的寻址,如图 3 – 9 所示,定时关系如图 3 – 10。

图 3-9 带泽码器的 TBP28S166 与 TMS32020 连接

图 3-10 TBP28S166 与 TMS32020 接口时序

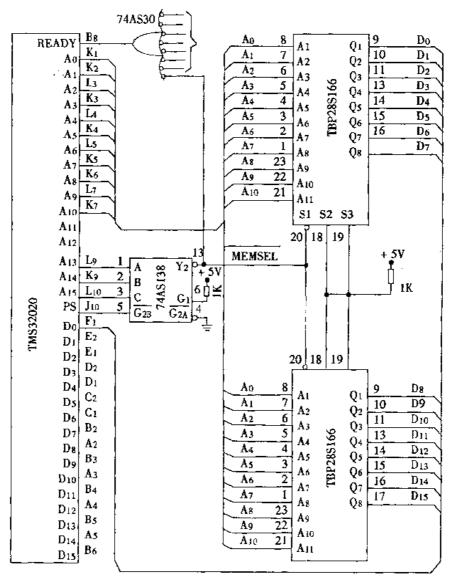

## 2.TMS32020 与 EPROM 的连接

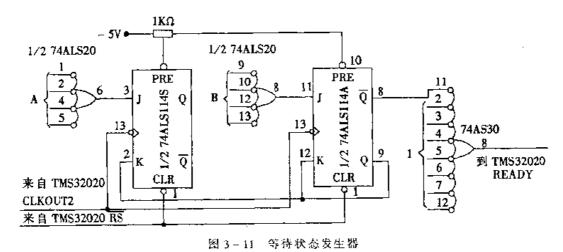

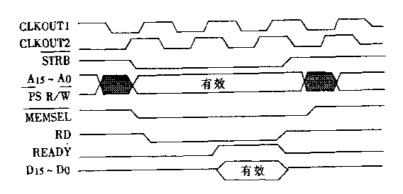

TMS2764-35 EPROM(8192×8)的寻址时间是 350ns(>90ns),不能直接满足 TMS32020 定时要求,需要一个等待状态产生器提供两个 200ns 等待状态。图 3-11 是等待状态发生器电路,在 A 处输入时,产生两个等待状态的输出,在 B 处输入时,产生一个等待状态的输出,定时关系如图 3-12 所示。74ASI38 译码器输出作为控制信号。考虑到 EPROM 有较长的截止时间,为了避免数据总线冲突,在 TMS2764-35 输出端增加了 74AS244 作为缓冲器。图 3-13 表示定时关系。图 3-14 是 TMS32020 与 TMS2764-35 连接图。

CLKOUT1

CLKOUT2

Ao ~ A15

有效

PS DS IS

有效

Ao ~ A15

有效

PS DS IS

有效

B

-个等符状态

READY

图 3 - 12

等符状态发生器时序图

图 3-13 TMS2764 与 TMS32020 接口定时

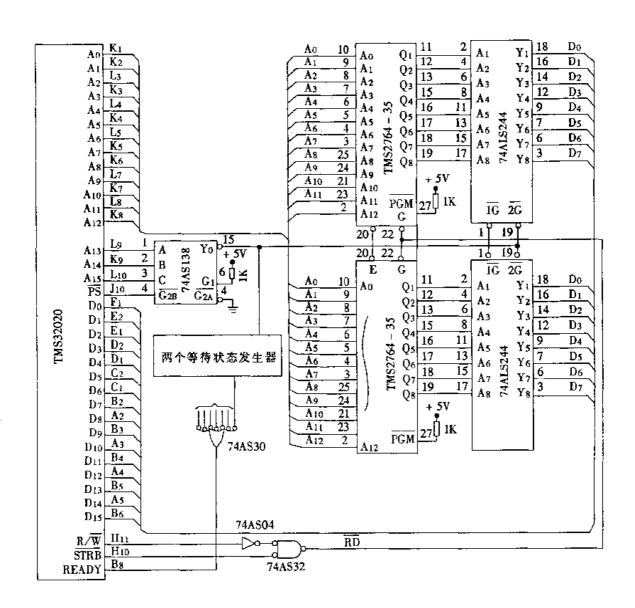

图 3-14 TMS2764与 TMS32020 连接图

#### 3.TMS32020 与静态 RAM 的连接

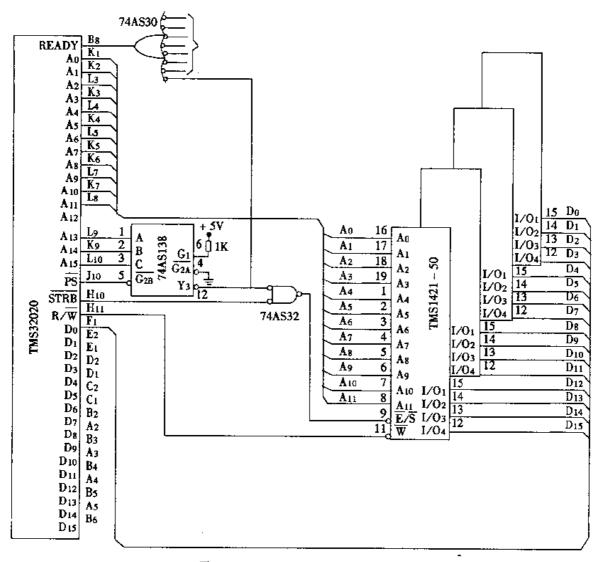

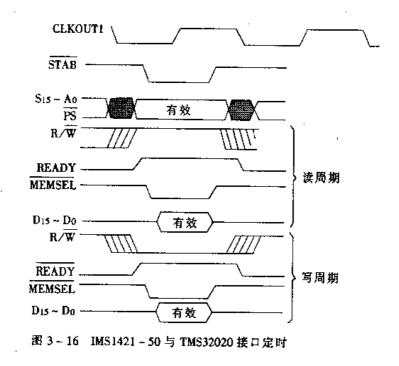

图 3-15 为 INMOS IMSI421-50 静态 RAM(4096×4)间 TMS32020 的连接,图中 RAM 为程序存储器,PS为控制信号,定时关系如图 3-18。在读周期,IMS 1421-50 在被选中后 40ns 内给于数据响应,能满足 TMS32020 的要求,在写周期,MEMSEL形成写时间,为保证可靠写入并些负数据总裁发生冲突, $\overline{W}$ (写信号)应在数据出现在数据总线的就已经稳定,并在数据消失后切保持一段时间。

若将 IMS1421 设计成数据存储器,只需将PS改为DS,其它完全一致。

若选择其它存储器,不能满足 TMS32020 的要求,可以用等待状态产生器插入适当的等待状态来驱动 TMS32020 READY 线。

若存储器的截止时间过长,可增加输出缓冲器,防止总线冲突。

图 3-15 IMS1421-50 与 TMS32020 连接

#### 4.TMS32020 与 D/A 转换器接口

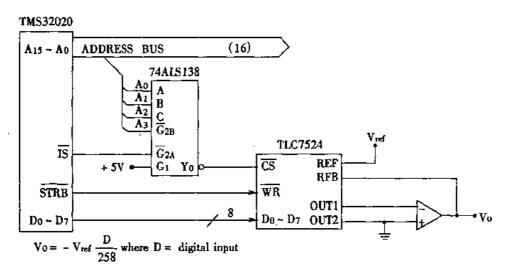

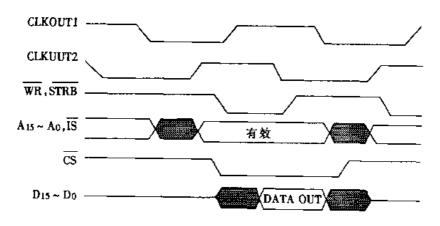

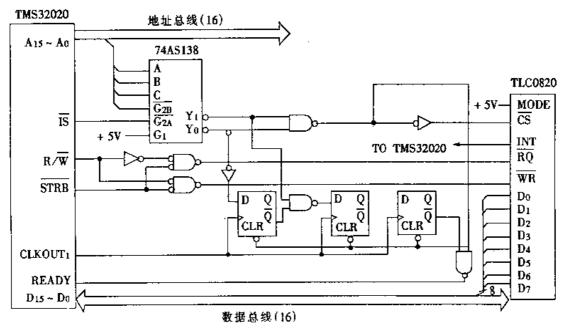

8 位 D/A 转换器 TLC 7524 可以以最小的外部电路请求与 TMS32020 相连,如图 3-17 所示,接口电路包括有一个 SN74LS138 的 3-8 线译码器,用于对外围设备地址译码。

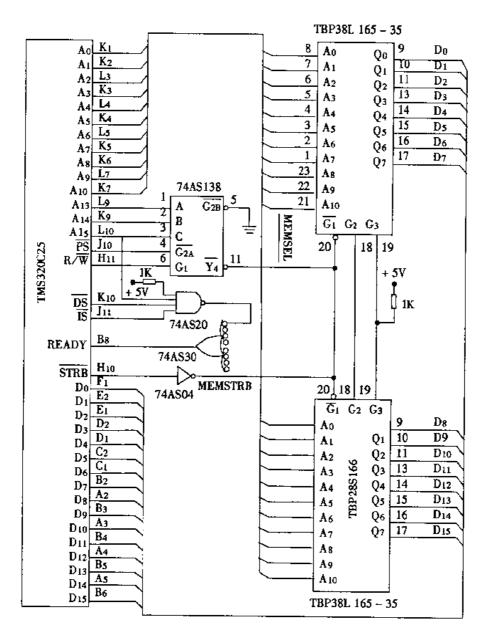

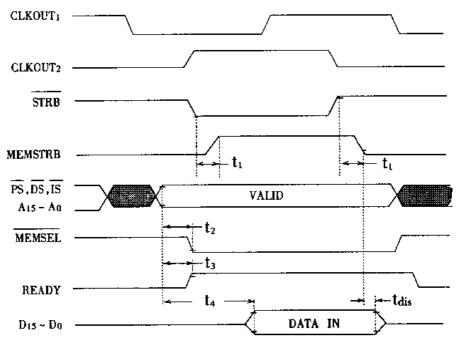

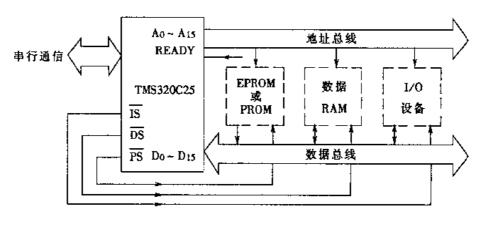

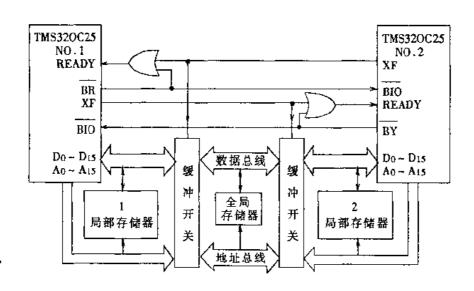

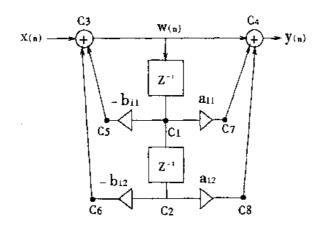

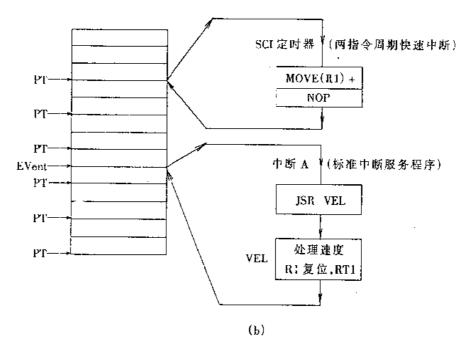

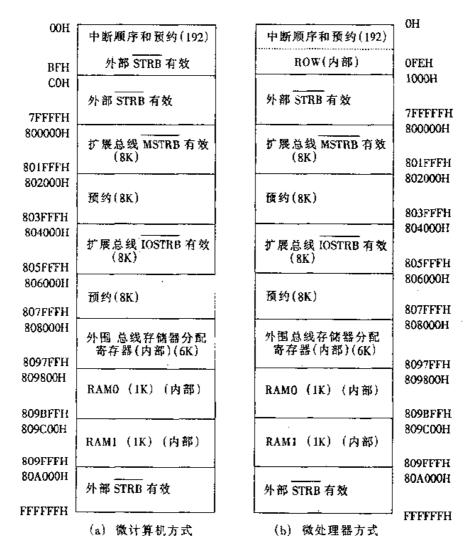

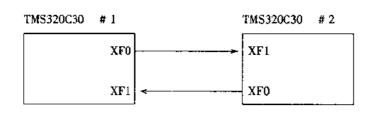

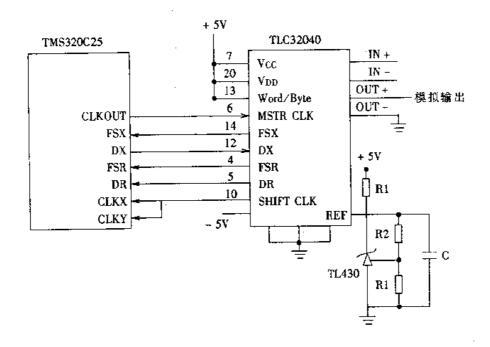

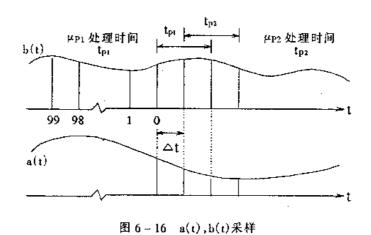

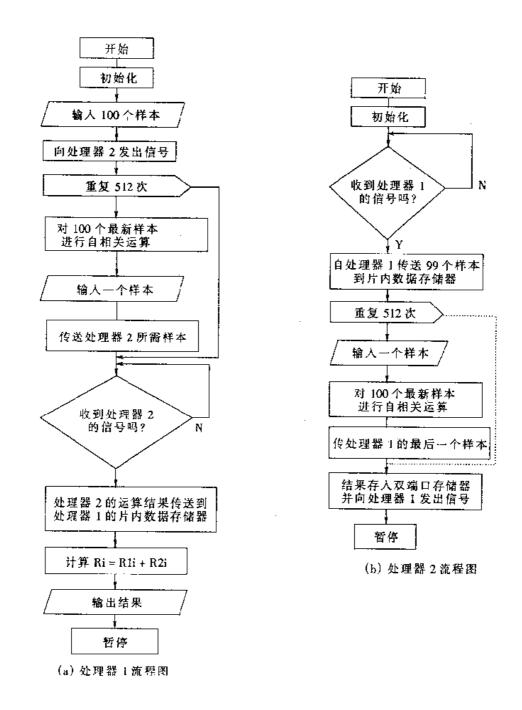

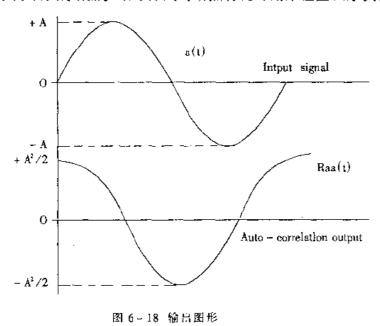

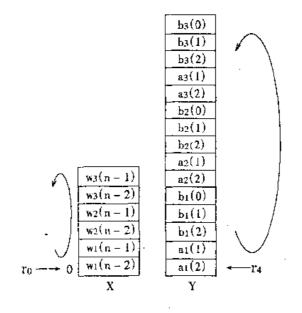

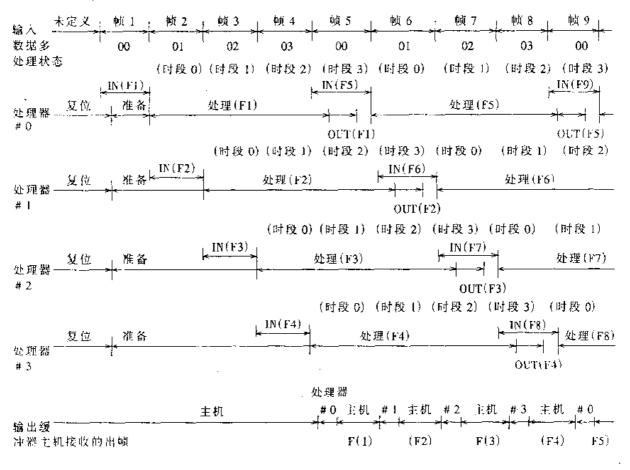

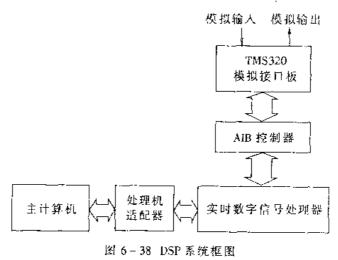

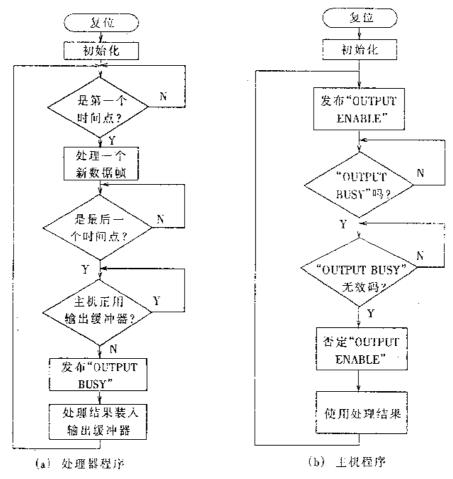

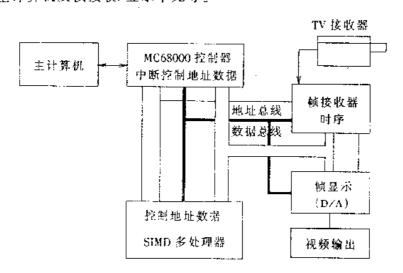

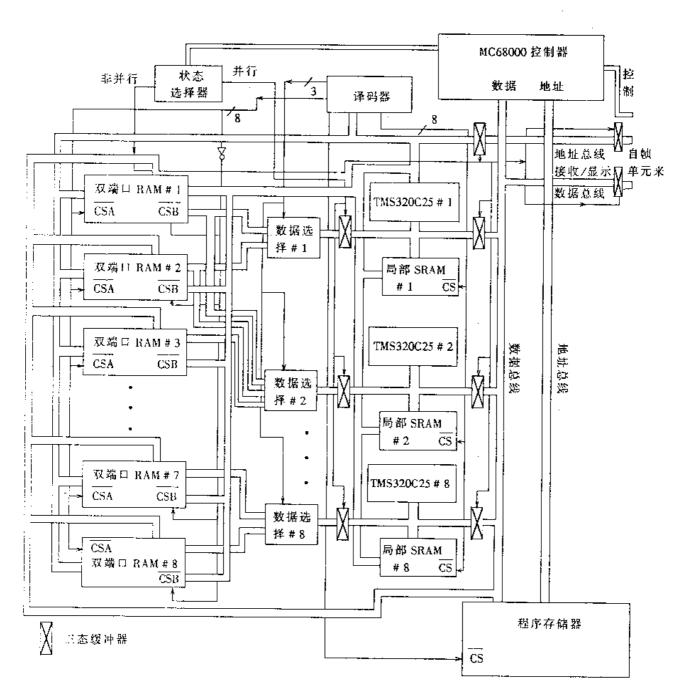

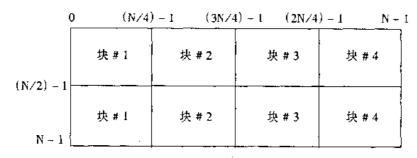

图 3-17 TMS32020 与 TLC7524 接口