# 三、MC68HC908GP32 单片机

#### 3.10、概述:

MC68HC908GP32 具有以下特性:

- 32K 片内 FLASH 程序存储器, 具有在线编程能力和保密功能

- 512B 片内 RAM

- 8MHZ 内部总线频率

- 增强型串行口通讯口 SCI

- 串行外围接口 SPI

- 两个 16 位双通道定时器接口模块 (TIM1 和 TIM2), 每个通道可选择为输入捕获、输出捕获和 PWM, 其时钟可分别选为内部总线的 1、2、4、8、16、32 和 64 的分频值

- 8路8位A/D转换器

- 系统保护特性:

- 一计算机工作正常 (COP) 复位

- 一低电压检测复位,可选为 3V 或 5V 操作

- -非法指令码检测复位

- -非法地址检测复位

- 时钟发生器模块, 具有 32KHZ 晶振 PLL 电路, 可产生各种工作频率

- 33 根通用 I/0 脚, 包括 26 根多功能 I/0 脚和 5 或 7 根专用 I/0 脚

- PA、PC和PD的输入口有可选择的上拉电阻

- 所有口有 10mA 吸流和放流能力, PTC0- PTC4 有 15mA 吸流和放流能力

- 带时钟预分频的时间基模块有 8 种周期性实时中断 (1、4、16、256、512、1024、2048 和 4096HZ),可在 STOP 方式时使用外部 32KHZ 晶振周期性唤醒 CPU

- 8位键盘唤醒口

- 所有口有最高 5mA 输入电流保护功能

- 具有 PDIP40、SDIP42 和 QFP44 封装形式 CPU08 特性:

- 增强的 HC05 CPU 结构

- 16 种寻址方式(比 HC05 多 8 种)

- 16 位变址寄存器和堆栈指针

- 存储器至存储器数据传送

- 快速 8×8 乘法指令

- 快速 16/8 除法指令

- 扩展的循环控制功能

- BCD 指令

- 优化用于控制应用

- 优化支持 C 语言

# 3.2、基本结构

## 3.2.1、MCU 结构

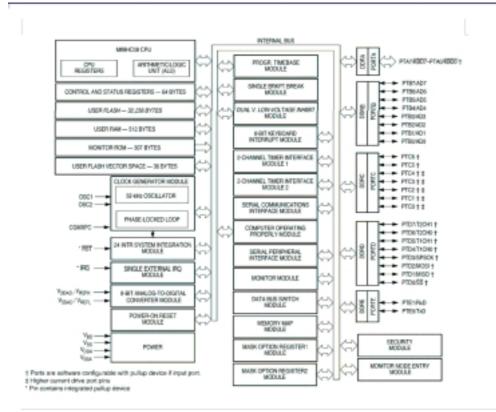

图 3.1 为 MC68HC908GP32 的框图

图 3.1 MC68HC908GP32 的框图

# 3.2.2、引脚

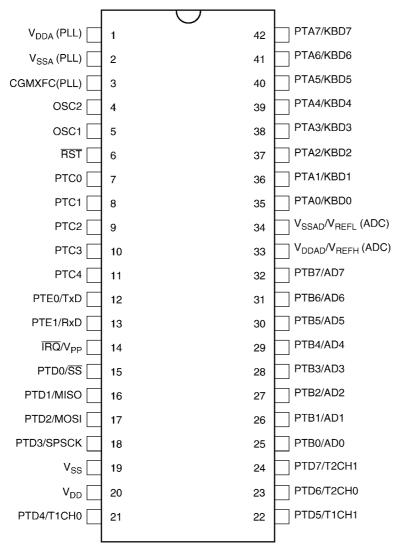

图 3-2、3-3、3-4 分别为 PDIP40、SDIP42、QFP44 的引脚图

|                        | •  |        | `  |                                            |

|------------------------|----|--------|----|--------------------------------------------|

| V <sub>DDA</sub> (PLL) |    | $\cup$ |    | PTA7/KBD7                                  |

|                        | 1  |        | 40 | ⊢┘                                         |

| V <sub>SSA</sub> (PLL) | 2  |        | 39 | PTA6/KBD6                                  |

| CGMXFC(PLL)            | 3  |        | 38 | PTA5/KBD5                                  |

| OSC2                   | 4  |        | 37 | PTA4/KBD4                                  |

| OSC1                   | 5  |        | 36 | PTA3/KBD3                                  |

| RST                    | 6  |        | 35 | PTA2/KBD2                                  |

| PTC0                   | 7  |        | 34 | PTA1/KBD1                                  |

| PTC1                   | 8  |        | 33 | PTA0/KBD0                                  |

| PTC2                   | 9  |        | 32 | V <sub>SSAD</sub> /V <sub>REFL</sub> (ADC) |

| PTC3                   | 10 |        | 31 | V <sub>DDAD</sub> /V <sub>REFH</sub> (ADC) |

| PTC4                   | 11 |        | 30 | PTB7/AD7                                   |

| PTE0/TxD               | 12 |        | 29 | PTB6/AD6                                   |

| PTE1/RxD               | 13 |        | 28 | PTB5/AD5                                   |

| ĪRQ∕V <sub>PP</sub> ☐  | 14 |        | 27 | PTB4/AD4                                   |

| PTD0/SS                | 15 |        | 26 | PTB3/AD3                                   |

| PTD1/MISO              | 16 |        | 25 | PTB2/AD2                                   |

| PTD2/MOSI              | 17 |        | 24 | PTB1/AD1                                   |

| PTD3/SPSCK             | 18 |        | 23 | PTB0/AD0                                   |

| V <sub>SS</sub>        | 19 |        | 22 | PTD5/T1CH1                                 |

| V <sub>DD</sub>        | 20 |        | 21 | PTD4/T1CH0                                 |

| l                      |    |        |    | I                                          |

Note: PTC5, PTC6, PTD6, and PTD7 were removed for this package.

图 3-2 40 脚 PDIP 引脚图

Note: PTC5, PTC6 were removed for this package.

图 3-3 42 脚 SDIP 引脚图

- (1) VDD和 VSS: 电源供给端

- (2) 0SC1和0SC2: 片内振荡器引脚

- (3) RST: 外部低有效复位输入或输出脚,有内部上拉电阻

- (4) IRO: 外部中断输入脚, 有内部上拉电阻

- (5) VDDA和 VSSA: 时钟发生器模块(CGM)的电源供给端

- (6) CGMXFC: CGM 的外部滤波电容连接脚

- (7) VDDAD和 VSSAD: A/D 转换器电源供给端

- (8) VREFH 和 VREFL: A/D 转换器的高和低参考电压输入端

- (9) PTA7/KBD7—PTA0/KBD0: 8 位通用双向 I/0 口,每个可编程为键盘输入脚。作输入时,每个可选择有上拉电阻

- (10) PTB7/AD7-PTB0/AD0: 8 位通用双向 I/0 口, 可用作 A/D 输入

- (11) PTC6—PTC0: 7位通用双向 I/0 口。作输入时,每个可选择有上拉电阻

- (12) PTD7/T2CH1—PTD0/ SS: 8 位特殊功能、双向 I/0 口。PTD0—PTD3 可用作 SPI 脚, PTD4—PTD7 可分别用于定时器模块 (TIM1 和 TIM2)。在作输入时,每个可选择有上拉电阻

- (13) PTE1/RXD、PTE0/TXD: 2位通用双向 I/0口。它们可用作 SCI 脚

# 3.3.3、存储器

Note: \$FFF6-\$FFFD

reserved for

8 security bytes

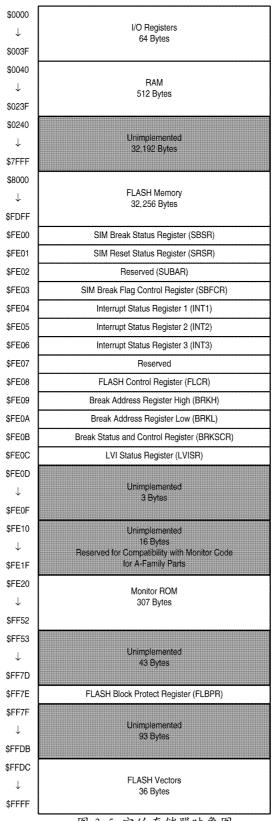

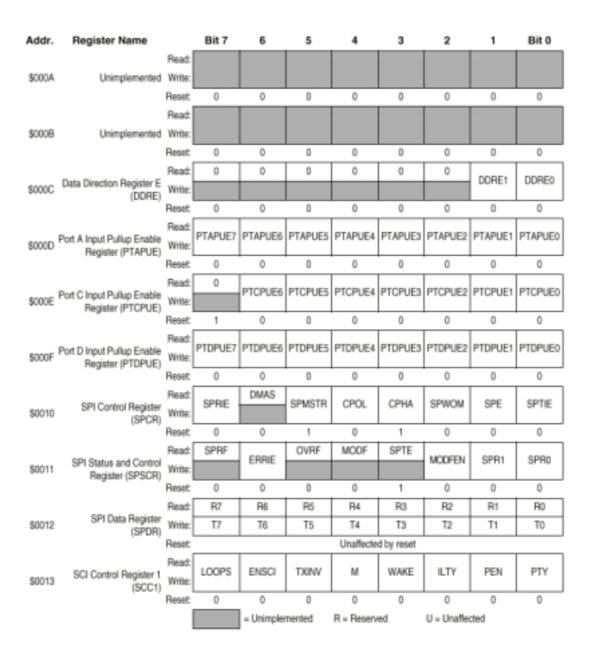

MC68HC908GP32 可寻址 64K 地址空间。图 3-5 为它的存储器映象图。图 3-6 为它的 I/0 寄存器。

图 3-5 它的存储器映象图

| Addr.  | Register Name                           |                 | Bit 7                                       | 6     | 5     | 4         | 3          | 2     | 1     | Bit 0 |  |

|--------|-----------------------------------------|-----------------|---------------------------------------------|-------|-------|-----------|------------|-------|-------|-------|--|

| \$0000 | Port A Data Register<br>(PTA)           | Read:<br>Write: | PTA7                                        | PTA6  | PTA5  | PTA4      | PTA3       | PTA2  | PTA1  | PTA0  |  |

|        | 44                                      | Reset:          |                                             |       |       | Unaffecte | d by reset |       |       |       |  |

| \$0001 | Port B Data Register<br>(PTB)           | Read:<br>Write: | PTB7                                        | PTB6  | PTB5  | PTB4      | PTB3       | PTB2  | PTB1  | PTB0  |  |

|        | ,,                                      | Reset:          |                                             |       |       | Unaffecte | d by reset |       |       |       |  |

| \$0002 | Port C Data Register<br>(PTC)           | Read:<br>Write: | 0                                           | PTC6  | PTC5  | PTC4      | PTC3       | PTC2  | PTC1  | PTC0  |  |

|        | (, 10)                                  | Reset:          |                                             |       |       | Unaffecte | d by reset |       |       |       |  |

| \$0003 | \$0003 Port D Data Register             | Read:<br>Write: | PTD7                                        | PTD6  | PTD6  | PTD4      | PTD3       | PTD2  | PTD1  | PTD0  |  |

|        | Ų 10 <sub>1</sub>                       | Reset:          |                                             |       |       | Unaffecte | d by reset |       |       |       |  |

| \$0004 | \$0004 Data Direction Register A (DDRA) | Read:<br>Write: | DDRA7                                       | DDRA6 | DDRA5 | DDRA4     | DDRA3      | DDRA2 | DDRA1 | DDRA0 |  |

|        |                                         | Reset:          | 0                                           | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

| \$0005 | Data Direction Register B (DDRB)        | Read:<br>Write: | DDR87                                       | DDRB6 | DDR85 | DORB4     | DDRB3      | DDRB2 | DDRB1 | DORB0 |  |

|        | (aut to)                                | Reset:          | 0                                           | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

| \$0006 | Data Direction Register C<br>(DDRC)     | Read:<br>Write: | 0                                           | DDAC6 | DDRC5 | DDRC4     | DDRC3      | DDRC2 | DDRC1 | DDRCO |  |

|        | , ,                                     | Reset:          | 0                                           | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

| \$0007 | Data Direction Register D<br>(DDRD)     | Read:<br>Write: | DDRD7                                       | DORD6 | DDRD5 | DORD4     | DDRD3      | DORD2 | DDRD1 | DORDO |  |

|        | (22.2)                                  | Reset:          | 0                                           | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | Read:           | 0                                           | 0     | 0     | 0         | 0          | 0     | PTE1  | PTE0  |  |

| \$0008 | Port E Data Register<br>(PTE)           | Write:          |                                             |       |       |           |            |       | PIEI  | PIEU  |  |

|        | (-12)                                   | Reset:          |                                             |       |       | Unaffecte | d by reset |       |       |       |  |

|        |                                         | Read:           |                                             |       |       |           |            |       |       |       |  |

| \$0009 | Unimplemented                           | Write:          |                                             |       |       |           |            |       |       |       |  |

|        |                                         | Reset:          | 0                                           | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         |                 | = Unimplemented R = Reserved U = Unaffected |       |       |           |            |       |       |       |  |

| Addr.  | Register Name                                    |                 | Bit 7 | 6         | 5      | 4          | 3     | 2          | 1       | Bit 0 |

|--------|--------------------------------------------------|-----------------|-------|-----------|--------|------------|-------|------------|---------|-------|

| \$0014 | SCI Control Register 2<br>(SCC2)                 | Read:<br>Write: | SCTIE | TCIE      | SCRIE  | ILIE       | TE    | RE         | RWU     | SBK   |

|        | (OOOL)                                           | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        |                                                  | Read:           | R8    | ТВ        | DMARE  | DMATE      | ORIE  | NEIE       | FEIE    | PEIE  |

| \$0015 | SCI Control Register 3<br>(SCC3)                 | Write:          |       | 10        | DWANE  | DWATE      | OHIE  | NEIE       | FEIE    | PEIE  |

|        | (2000)                                           | Reset:          | U     | U         | 0      | 0          | 0     | 0          | 0       | 0     |

|        | 0010-1-0-1                                       | Read:           | SCTE  | TC        | SCRF   | IDLE       | OR    | NF         | FE      | PE    |

| \$0016 | SCI Status Register 1<br>(SCS1)                  | Write:          |       |           |        |            |       |            |         |       |

|        | (000.)                                           | Reset:          | 1     | 1         | 0      | 0          | 0     | 0          | 0       | 0     |

|        | 0010-1-0-11-0                                    | Read:           |       |           |        |            |       |            | BKF     | RPF   |

| \$0017 | SCI Status Register 2<br>(SCS2)                  | Write:          |       |           |        |            |       |            |         |       |

|        | (0000)                                           | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        | 000 0 . 0                                        | Read:           | R7    | R6        | R5     | R4         | R3    | R2         | R1      | R0    |

| \$0018 | SCI Data Register<br>(SCDR)                      | Write:          | T7    | T6        | T5     | T4         | T3    | T2         | T1      | T0    |

|        | (0001)                                           | Reset:          |       |           |        | Unaffecte  |       |            |         |       |

|        | 0010-101-0                                       | Read:           |       |           | SCP1   | SCP0       | R     | SCR2       | SCR1    | SCR0  |

| \$0019 | SCI Baud Rate Register<br>(SCBR)                 | Write:          |       |           | SOFT   | SUFU       | n     | JUNE       | JUNI    | SUNU  |

|        | (===-,                                           | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        | Keyboard Status                                  | Read:           | 0     | 0         | 0      | 0          | KEYF  | 0          | IMASKK  | MODEK |

| \$001A | and Control Register                             | Write:          |       |           |        |            |       | ACKK       | INFORM  | MODEN |

|        | (INTKBSCR)                                       | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        |                                                  | Read:           | KBIE7 | KBIE6     | KBIE5  | KBIE4      | KBIE3 | KBIE2      | KBIE1   | KBIE0 |

| \$001B | Keyboard Interrupt Enable<br>Register (INTKBIER) | Write:          | NOIE/ | NDIEG     | Notes  | NDIC4      | Raica | NDICZ      | KDIET   | NDIEU |

|        | , , , , , , , , , , , , , , , , , , , ,          | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        |                                                  | Read:           | TBIF  | TBR2      | TBR1   | TBR0       | 0     | TBIE       | TBON    | R     |

| \$001C | Time Base Module Control<br>Register (TBCR)      | Write:          |       | TONE      | Ibni   | 1010       | TACK  | TOIL       | IDON    | n     |

|        | rogani (roary                                    | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        |                                                  | Read:           | 0     | 0         | 0      | 0          | IRQF1 | 0          | IMASK1  | MODE1 |

| \$001D | IRQ Status and Control<br>Register (INTSCR)      | Write:          |       |           |        |            |       | ACK1       | IMPatri | WOOE! |

|        |                                                  | Reset:          | 0     | 0         | 0      | 0          | 0     | 0          | 0       | 0     |

|        |                                                  |                 |       | = Unimple | mented | R = Reserv | red   | U = Unaffe | cted    |       |

|        |                                                  |                 |       | -         |        |            |       |            |         |       |

|        |                                                  |                 |       |           |        |            |       |            |         |       |

| Addr.  | Register Name                                      |        | Bit 7  | 6       | 5       | 4            | 3                    | 2     | 1       | Bit 0  |

|--------|----------------------------------------------------|--------|--------|---------|---------|--------------|----------------------|-------|---------|--------|

|        | Configuration Register 2                           | Read:  | 0      | 0       | 0       | 0            | 0                    | 0     | OSC-    | SCIBD- |

| \$001E | (CONFIG2)†                                         | Write: |        |         |         |              |                      |       | STOPENB | SAC    |

|        |                                                    | Reset: | 0      | 0       | 0       | 0            | 0                    | 0     | 0       | 0      |

|        |                                                    | Read:  | COPRS  | LVISTOP | LVIRSTD | LVIPWRD      | Luconat              | conco | eron    | COPD   |

| \$001F | Configuration Register 1<br>(CONFIG1) <sup>†</sup> | Write: | COPHS  | LVISTOP | LVIHSTU | LVIPWHD      | LVI5OR3 <sup>†</sup> | SSREC | STOP    | COPD   |

|        | (00111101)                                         | Reset: | 0      | 0       | 0       | 0            | 0                    | 0     | 0       | 0      |

|        |                                                    | Read:  | TOF    | TOIE    | TOTOD   | 0            | 0                    | PS2   | PS1     | neo    |

| \$0020 | Timer 1 Status and Control<br>Register (T1SC)      | Write: | 0      | TOTE    | TSTOP   | TRST         |                      | Paz   | PSI     | PS0    |

|        | riegister (1 100)                                  | Reset: | 0      | 0       | 1       | 0            | 0                    | 0     | 0       | 0      |

|        |                                                    | Read:  | Bit 15 | 14      | 13      | 12           | 11                   | 10    | 9       | Bit 8  |

| \$0021 | Timer 1 Counter Register<br>High (T1CNTH)          | Write: |        |         |         |              |                      |       |         |        |

|        | g-(0                                               | Reset: | 0      | 0       | 0       | 0            | 0                    | 0     | 0       | 0      |

|        | \$0022 Timer 1 Counter Register<br>Low (T1CNTL)    | Read:  | Bit 7  | 6       | 5       | 4            | 3                    | 2     | 1       | Bit 0  |

| \$0022 |                                                    | Write: |        |         |         |              |                      |       |         |        |

|        |                                                    | Reset: | 0      | 0       | 0       | 0            | 0                    | 0     | 0       | 0      |

|        |                                                    | Read:  | Bit 15 | 14      | 13      | 12           | 11                   | 10    | 9       | Bit 8  |

| \$0023 | Timer 1 Counter Modulo<br>Register High (T1MODH)   | Write: | DE 15  | 14      | 13      | 12           | "                    | 10    | 9       | DILO   |

|        | - again right ( rimes in                           | Reset: | 1      | 1       | 1       | 1            | 1                    | 1     | 1       | 1      |

|        |                                                    | Read:  | Bit 7  | 6       | 5       | 4            | 3                    | 2     | 1       | Bit 0  |

| \$0024 | Timer 1 Counter Modulo<br>Register Low (T1MODL)    | Write: | DE/    |         | 2       | , ,          | 3                    | 2     | '       | BILO   |

|        | riogato con (rimoce)                               | Reset: | 1      | 1       | 1       | 1            | 1                    | 1     | 1       | 1      |

|        | Timer 1 Channel 0 Status                           | Read:  | CH0F   | CHOIE   | MSOB    | MSOA         | ELSOB                | ELS0A | TOVO    | CHOMAX |

| \$0025 | and Control Register                               | Write: | 0      | CHUE    | Maub    | MOUA         | ELOUD                | ELSUA | 1000    | CHUMAX |

|        | (T1SC0)                                            | Reset: | 0      | 0       | 0       | 0            | 0                    | 0     | 0       | 0      |

|        |                                                    | Read:  | Divis  | 14      | 40      | 12           |                      | 10    | 0       | Die o  |

| \$0026 | Timer 1 Channel 0<br>Register High (T1CH0H)        | Write: | Bit 15 | 14      | 13      | 12           | 11                   | 10    | 9       | Bit 8  |

|        | region rigit (1 fortier)                           | Reset: |        |         |         | Indeterminat | e after reset        |       |         |        |

|        |                                                    | Read:  | D) 7   |         | -       |              |                      |       |         | Dia A  |

| \$0027 | Timer 1 Channel 0<br>Register Low (T1CH0L)         | Write: | Bit 7  | 6       | 5       | 4            | 3                    | 2     | 1       | Bit 0  |

|        | ricgiotes com (1 forfoc)                           | Reset: |        |         |         | Indeterminat | e after reset        |       |         |        |

<sup>†</sup> One-time writeable register after each reset, except LVISOR3 bit. LVISOR3 bit is only reset via POR (power-on reset).

| Addr.  | Register Name                                    |                 | Bit 7     | 6         | 5      | 4           | 3             | 2           | 1    | Bit 0   |

|--------|--------------------------------------------------|-----------------|-----------|-----------|--------|-------------|---------------|-------------|------|---------|

|        | Timer 1 Channel 1 Status                         | Read:           | CH1F      | CHIE      | 0      | MS1A        | EI CAD        | ELETA       | TOMA | CHILIAN |

| \$0028 | and Control Register                             |                 | 0         | CH1IE     |        | MSIA        | ELS1B         | ELS1A       | TOV1 | CH1MAX  |

|        | (T1SC1)                                          | Reset:          | 0         | 0         | 0      | 0           | 0             | 0           | 0    | 0       |

| \$0029 | Timer 1 Channel 1<br>Register High (T1CH1H)      | Read:<br>Write: | Bit 15    | 14        | 13     | 12          | 11            | 10          | 9    | Bit 8   |

|        | riegista riigii (r retriir)                      | Reset:          |           |           |        | Indetermina | te after rese |             |      |         |

| \$002A | Timer 1 Channel 1<br>Register Low (T1CH1L)       | Read:<br>Write: | Bit 7     | 6         | 5      | 4           | 3             | 2           | 1    | Bit 0   |

|        |                                                  | Reset:          |           |           |        | Indetermina | te after rese | t           |      |         |

| \$002B | Timer 2 Status and Control                       | Read:<br>Write: | TOF<br>0  | TOIE      | TSTOP  | 0<br>TRST   | 0             | PS2         | PS1  | PS0     |

|        | Register (T2SC)                                  | Reset:          | 0         | 0         | 1      | 0           | 0             | 0           | 0    | 0       |

|        |                                                  | Read:           | Bit 15    | 14        | 13     | 12          | 11            | 10          | 9    | Bit 8   |

| \$002C | High (T2CNTH)                                    | Write:          |           |           |        |             |               |             |      |         |

|        |                                                  | Reset:          | 0         | 0         | 0      | 0           | 0             | 0           | 0    |         |

|        |                                                  | Read:           | Bit 7     | 6         | 5      | 4           | 3             | 2           | 1    | Bit 0   |

| \$002D | Timer 2 Counter Register<br>Low (T2CNTL)         | Write:          |           |           |        |             |               |             |      |         |

|        | 2011 (1201112)                                   | Reset:          | 0         | 0         | 0      | 0           | 0             | 0           | 0    | 0       |

| \$002E | Timer 2 Counter Modulo<br>Register High (T2MODH) | Read:<br>Write: | Bit 15    | 14        | 13     | 12          | 11            | 10          | 9    | Bit 8   |

|        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,          | Reset:          | 1         | . 1       | 1      | 1           | 1             | 1           | 1    | . 1     |

| \$002F | Timer 2 Counter Modulo<br>Register Low (T2MODL)  | Read:<br>Write: | Bit 7     | 6         | 5      | 4           | 3             | 2           | 1    | Bit 0   |

|        |                                                  | Reset:          | 1         | 1         | 1      | 1           | 1             | 1           | 1    | 1       |

| \$0030 |                                                  | Read:<br>Write: | CH0F<br>0 | CHOIE     | MS0B   | MSOA        | ELS0B         | ELS0A       | TOVO | CHOMAX  |

|        | (T2SC0)                                          | Reset:          | 0         | 0         | 0      | 0           | 0             | 0           | 0    | 0       |

| \$0031 | Timer 2 Channel 0<br>Register High (T2CH0H)      | Read:<br>Write: | Bit 15    | 14        | 13     | 12          | 11            | 10          | 9    | Bit 8   |

|        |                                                  | Reset:          |           |           |        | Indetermina | te after rese | t           |      |         |

|        |                                                  |                 |           | = Unimple | mented | R = Reserv  | ed            | U = Unaffer | cted |         |

| Addr.  | Register Name                                   |                 | Bit 7  | 6         | 5      | 4           | 3             | 2          | 1    | Bit 0 |

|--------|-------------------------------------------------|-----------------|--------|-----------|--------|-------------|---------------|------------|------|-------|

| \$0032 | Timer 2 Channel 0<br>Register Low (T2CH0L)      | Read:<br>Write: | Bit 7  | 6         | 5      | 4           | 3             | 2          | 1    | Bit 0 |

|        | regiser cow (rzonoc)                            | Reset:          |        |           |        | Indetermina | te after rese | t          |      |       |

|        | Timer 2 Channel 1 Status                        | Read:           | CH1F   | CHAPE     | 0      |             | 51.010        | 51011      | 7000 |       |

| \$0033 | and Control Register                            | Write:          | 0      | CH1IE     |        | MS1A        | ELS1B         | ELS1A      | TOV1 | CH1MA |

|        | (T2SC1)                                         | Reset:          | 0      | 0         | 0      | 0           | 0             | 0          | 0    | 0     |

|        | T                                               | Read:           | Bit 15 | 14        | 13     | 12          | 11            | 10         | 9    | Bit 8 |

| \$0034 | Timer 2 Channel 1<br>Register High (T2CH1H)     | Write:          | DIL 13 | 14        | 13     | 12          |               | 10         |      | Dito  |

|        | ,                                               | Reset:          |        |           |        | Indetermina | te after rese | ŧ          |      |       |

|        | Timer 2 Channel 1                               | Read:           | Bit 7  | 6         | 5      | 4           | 3             | 2          | 1    | Bit 0 |

| \$0035 | Register Low (T2CH1L)                           | Write:          | Dit 1  |           |        | _ `         |               | -          |      | Di U  |

|        |                                                 | Reset:          |        |           |        | Indetermina | te after rese | ŧ          |      |       |

|        | PLL Control Register                            | Read:           | PLLIE  | PLLF      | PLLON  | BCS         | PRE1          | PRE0       | VPR1 | VPR0  |

| \$0036 | (PCTL)                                          | Write:          |        |           |        |             |               |            |      |       |

|        |                                                 | Reset:          | 0      | 0         | 1      | 0           | 0             | 0          | 0    | 0     |

|        | PLL Bandwidth Control                           | Read:           | OTUA   | LOCK      | ACQ    | 0           | 0             | 0          | 0    | R     |

| \$0037 | Register (PBWC)                                 | Write:          |        |           |        |             |               |            |      |       |

|        |                                                 | Reset:          | 0      | 0         | 0      | 0           | 0             | 0          | 0    | 0     |

|        | PLL Multiplier Select High                      | Read:           | 0      | 0         | 0      | 0           | MUL11         | MUL10      | MUL9 | MULB  |

| \$0038 | Register (PMSH)                                 | Write:          |        |           |        |             |               |            |      |       |

|        |                                                 | Reset:          | 0      | . 0       | 0      | 0           | . 0           | 0          | . 0  | 0     |

|        | PLL Multiplier Select Low                       | Read:           | MUL7   | MUL6      | MUL5   | MUL4        | MUL3          | MUL2       | MUL1 | MULO  |

| \$0039 | Register (PMSL)                                 | Write:          |        |           |        |             |               |            |      | Ь.    |

|        |                                                 | Reset:          | 0      | 1         | 0      | 0           | 0             | 0          | 0    | 0     |

| \$003A | PLL VCO Select Range<br>Register (PMRS)         | Read:<br>Write: | VRS7   | VRS6      | VRS5   | VRS4        | VRS3          | VRS2       | VRS1 | VRS0  |

|        | riogator (rimito)                               | Reset:          | 0      | 1         | 0      | 0           | 0             | 0          | 0    | 0     |

|        |                                                 | Read:           | 0      | 0         | 0      | 0           | RDS3          | RDS2       | RDS1 | RDS0  |

| \$003B | PLL Reference Divider<br>Select Register (PMDS) | Write:          |        |           |        |             | HUSS          | HUSZ       | HDS1 | HUSU  |

|        | Contra inspirate in motor                       | Reset:          | 0      | 0         | 0      | 0           | 0             | 0          | 0    | 1     |

|        |                                                 | - [             |        | = Unimple | mented | R = Reserv  | red           | U = Unaffe | cted |       |

| Addr.   | Register Name                                     |        | Bit 7 | 6         | 5      | 4           | 3             | 2           | 1      | Bit 0 |

|---------|---------------------------------------------------|--------|-------|-----------|--------|-------------|---------------|-------------|--------|-------|

|         | Analog-to-Digital Status                          | Read:  | 0000  | 4154      | 4000   | 40000       | 100110        | 40000       | 400114 | 4000  |

| \$003C  | and Control Register                              | Write: | R     | AIEN      | ADCO   | ADCH4       | ADCH3         | ADCH2       | ADCH1  | ADCH  |

|         | (ADSCR)                                           | Reset: | 0     | 0         | 0      | 1           | 1             | 1           | 1      | 1     |

|         |                                                   | Read:  | AD7   | AD6       | AD5    | AD4         | AD3           | AD2         | AD1    | AD0   |

| \$003D  | Analog-to-Digital Data<br>Register (ADR)          | Write: | R     | R         | R      | R           | R             | R           | R      | R     |

|         | riogioso (viori)                                  | Reset: |       |           |        | Indetermina | te after rese | ot          |        |       |

|         |                                                   | Read:  | ADIV2 | ADIV1     | ADIVO  | ADICLK      | 0             | 0           | 0      | 0     |

| \$003E  | Analog-to-Digital Input<br>Clock Register (ADCLK) | Write: | AUIVZ | ADIYI     | ALIVU  | ADICLK      | R             | R           | R      | R     |

|         | onon ragam (rasery                                | Reset: | 0     | 0         | 0      | 0           | 0             | 0           | 0      | 0     |

|         |                                                   | Read:  |       |           |        |             |               |             |        |       |

| \$003F  | Unimplemented                                     | Write: |       |           |        |             |               |             |        |       |

|         |                                                   | Reset: |       |           |        |             |               |             |        |       |

|         |                                                   | Read:  | 0     | 0         | 0      | 1           | 0             | 0           | BW     | 0     |

| \$FE00  | SIM Break Status Register<br>(SBSR)               | Write: | R     | R         | R      | R           | R             | R           | NOTE   | R     |

|         | (0201)                                            | Reset: | 0     | 0         | 0      | 1           | 0             | 0           | 0      | 0     |

| Note: W | riting a logic 0 clears BW.                       |        |       |           |        |             |               |             |        |       |

|         |                                                   | Read:  | POR   | PIN       | COP    | ILOP        | ILAD          | MODRST      | LVI    | 0     |

| \$FE01  | SIM Reset Status Register<br>(SRSR)               | Write: |       |           |        |             |               |             |        |       |

|         | (2.121)                                           | POR:   | 1     | 0         | 0      | 0           | 0             | 0           | 0      | 0     |

|         |                                                   | Read:  | В     | R         | В      | R           | R             | R           | R      | R     |

| \$FE02  | SIM Upper Byte Address<br>Register (SUBAR)        | Write: | "     | n         | "      | n           | "             | "           | "      | "     |

|         |                                                   | Reset: |       |           |        |             |               |             |        |       |

|         | CALC. I Fire Control                              | Read:  | BCFE  | R         | R      | R           | R             | R           | R      | R     |

| \$FE03  | SIM Break Flag Control<br>Register (SBFCR)        | Write: | DOTE  | - "       | "      | "           |               | "           | "      | _ "   |

|         |                                                   | Reset: | 0     |           |        |             |               |             |        |       |

|         | harry or Control Desires 4                        | Read:  | IF6   | IF5       | IF4    | IF3         | IF2           | IF1         | 0      | 0     |

| \$FE04  | Interrupt Status Register 1<br>(INT1)             | Write: | R     | R         | R      | R           | R             | R           | R      | R     |

|         |                                                   | Reset: | 0     | 0         | 0      | 0           | 0             | 0           | 0      | 0     |

|         | Internal Chat - Decision -                        | Read:  | IF14  | IF13      | IF12   | IF11        | IF10          | IF9         | IF8    | IF7   |

| \$FE05  | Interrupt Status Register 2<br>(INT2)             | Write: | R     | R         | R      | R           | R             | R           | R      | R     |

|         | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,           | Reset: | 0     | 0         | 0      | 0           | 0             | 0           | 0      | 0     |

|         |                                                   | - 1    |       | = Unimple | mented | R = Reserv  | ed            | U = Unaffec | ted    |       |

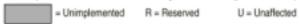

图 3-6 MC68HC908GP32 的 I/0 寄存器

# 3.3、复位和中断

MC68HC908GP32 具有上电复位 (POR) 计算机工作正常 (COP)、低电压复位、非法指令码和非法地址等复位源。SIM 复位状态寄存器 (SRSR) (\$FE01) 为复位标志 (它们在读出后清零)。

GP32 具有 24 个中断源和 17 个中断入口向量,见表 3-1。它共有 16 个中断状态位,位于 \$  $FE04^-06$  寄存器中。

表 3-1 MC68HC908GP32 中断源

|                           | 7 J  | C0011C90001 32 | 1 5/94            |     |               |

|---------------------------|------|----------------|-------------------|-----|---------------|

| 中断源                       | 标志   | 屏蔽             | INT 寄<br>存器标<br>志 | 优先级 | 向量地址          |

| Reset                     | None | None           | None              | 0   | \$FFFE~\$FFFF |

| SWI instruction           | None | None           | None              | 0   | \$FFFC~\$FFFD |

| IRQ pin                   | IRQF | IMASK1         | IF1               | 1   | \$FFFA~\$FFFB |

| CGM(PLL)                  | PLLF | PLLIE          | IF2               | 2   | \$FFF8~\$FFF9 |

| TIM1 channel0             | CH0F | CH0IE          | IF3               | 3   | \$FFF6~\$FFF7 |

| TIM1 channel1             | CH1F | CH1IE          | IF4               | 4   | \$FFF4~\$FFF5 |

| TIM1 overflow             | TOF  | TOIE           | IF5               | 5   | \$FFF2~\$FFF3 |

| TIM2 channel0             | CH0F | CH0IE          | IF6               | 6   | \$FFF0~\$FFF1 |

| TIM2 channel1             | CH1F | CH1IE          | IF7               | 7   | \$FFEE~\$FFEF |

| TIM2 overflow             | TOF  | TOIE           | IF8               | 8   | \$FFEC~\$FFED |

| SPI receiver full         | SPRF | SPRIE          |                   |     |               |

| SPI overflow              | OVRF | ERRIE          | IF9               | 9   | PEEEA PEEED   |

| SPI mode fault            | MODF | ERRIE          | 1179              | 9   | \$FFFA~\$FFFB |

| SPI transmitter empty     | SPTE | SPTIE          | IF10              | 10  | \$FFE8~\$FFE9 |

| SCI receiver overrun      | OR   | ORIE           |                   |     |               |

| SCI noise fag             | NF   | NEIE           |                   |     |               |

| SCI framing error         | FE   | FEIE           | IF11              | 11  | \$FFE6~\$FFE7 |

| SCI parity error          | PE   | PEIE           |                   |     |               |

| SCI receiver full         | SCRF | SCRIE          |                   |     |               |

| SCI input idle            | IDLE | ILIE           | IF12              | 12  | \$FFE4~\$FFE5 |

| SCI transmitter empty     | SCTE | SCTIE          |                   |     |               |

| SCI transmission complete | TC   | TCIE           | IF13              | 13  | \$FFE2~\$FFE3 |

| Keyboard pin              | KEYF | IMASKK         | IF14              | 14  | \$FFE0~\$FFE1 |

| ADC conversion complete   | COCO | AIEN           | IF15              | 15  | \$FFDE~\$FFDF |

| Timebase                  | TBIF | TBIE           | IF16              | 16  | \$FFDC~\$FFDD |

## Note:

COP 可由系统设置寄存器设置溢出周期和禁止。在允许后,软件必须周期性地向 \$ FFFF 写入任意值 (32、768KHZ 慢速方式时,COP 溢出周期为 250ms)。

外部中断 (IRQ) 可由 INTSCR (\$001D) 设置为下降沿和低电压触发 (MODE=1), 可禁止 IRQ 中断 (IMASK=1), 有 IRQ 标志位 (IRQF), 它由向 ACK 位写入 1 清零。

## 3.4、A/D 转换器

GP32 具有 8 路 8 位 A/D,它有一个 AD 状态和控制寄存器 (ADSCR)(\$003C),包括 AD 完成标志 (COCO)和 AD 中断允许 (AIEN)、AD 连续转换控制 (ADCO)及 AD 通道选择 (ADCH4¯ADCH0)。ADCH4¯ADCH0=11111时,关闭 A/D 电源,ADCH4¯ADCH0=00000¯00111选择 8 路 A/D 输入 (PTB0/AD0¯PTB7/AD7)。A/D 结果寄存器 (ADR)位于\$003D,存放最新的 A/D 转换结果。AD 时钟寄存器 (ADCLK)(\$003E)选择 A/D 时钟及其分频率,ADICLK 位=0 选择外部晶振时钟(CGMXCLK),=1 选择总线时钟。ADIV2¯ADIV0 选择 A/D 时钟分频率 (ADIV2¯ADIV0=000、001、010、011、1××,分频率分别为 1、2、4、8、16),应选择分频率使 A/D 时钟为约 1MHZ。

# 3.5、时钟发生模块和系统设置

## 3.5.1、时钟发生模块(CGMC)

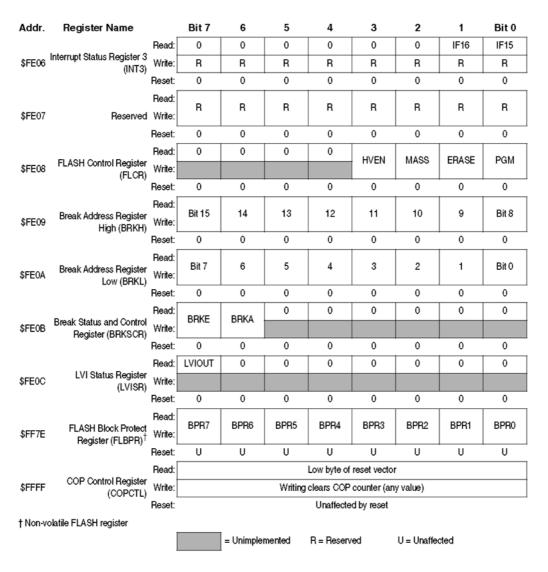

CGMC 包括晶振电路、锁相关 (PLL) 和基时钟选择电路。

- (1) 晶振电路: 它产生 CGMXCLK。一般可在 OSC1 与 OSC2 间接晶振,也可在 OSC1 输入外部时钟。

- (2) 锁相关 (PLL): 它可工作于获取和跟踪方式,它包括压控振荡器 (VCO)、参考分频率、预分频器、VCO分频器、相位检测、滤波器、锁相检测器。

- (3) PLL 参考时钟等于晶振频率(fRCLK)除以 R,它一般应为 30<sup>-</sup>100KHZ。对 30<sup>-</sup>100KHZ 外部晶振, R=1。PLL 有多个控制寄存器,在晶振频率为 32.768KHZ 时,对不同的总线频率 (fBUS),可如表 3-2 选择 PCTL 寄存器的 PREi (P)、VPRi (E) 位, PMSL (低位)、PMSH (高位)寄存器的值 (N), PMRS 寄存器的值 (L), PMDS 寄存器的值 (R)。

|                            | • -                       |   | •   |   |   |    |

|----------------------------|---------------------------|---|-----|---|---|----|

| $\mathbf{f}_{	extbf{BUS}}$ | $\mathbf{f}_{	ext{RCLK}}$ | R | N   | P | E | L  |

| 2.0MHz                     | 32.768kHz                 | 1 | F5  | 0 | 0 | D1 |

| 2.4576MHz                  | 32.768kHz                 | 1 | 12C | 0 | 1 | 80 |

| 2.5MHz                     | 32.76kHz                  | 1 | 132 | 0 | 1 | 83 |

| 4.0MHz                     | 32.768kHz                 | 1 | 1E9 | 0 | 1 | D1 |

| 4.9152MHz                  | 32.768kHz                 | 1 | 258 | 0 | 2 | 80 |

| 5.0MHz                     | 32.768kHz                 | 1 | 263 | 0 | 2 | 82 |

| 7.3728MHz                  | 32.768kHz                 | 1 | 384 | 0 | 2 | C0 |

| 8.0MHz                     | 32.768kHz                 | 1 | 3D1 | 0 | 2 | D0 |

表 3-2 PLL 编程实例

CGMC 的晶振电路需外接五个元件: 晶振、固定电容(C1)、微调电容(C2)、反馈电阻(RB)、串联电阻,见图 3-7。

Note: Filter network in box can be replaced with a 0.47 µF capacitor, but will degrade stability.

图 3-7 CGMC 外部连接

PLL 有两个控制器 (PCTL, \$0036; PBWC, \$0037), 前者的 PLLON=1 允许 PLL 和 VCO 时钟; PLLIE 和 PLLF 为 PLL 中断允许和标志位, 可在锁相成功时产生中断; BCS 为基时钟选择位: =0 使用 CGMXCLK, =1 使用 VCO 时钟。PEWC 控制 PLL 工作方式: 自动方式 (AUTO=1), 手动方式(由 ACO 选择获取和跟踪方式), LOCK 表示锁相成功(AUTO=1 时)。

### 3.5.2、系统设置

GP32 有两个系统设置寄存器(CONFIG1,\$001F; CONFIG2,\$001E),它们可允许晶振在 STOP 时继续运行(OSCSTOPENB 位=1),选择 SCI 波特率时钟源(SCIBDSRC=1,选内部总线时钟,=0,选外部振荡器),选择 COP 速率(COPRS=1,COP 溢出周期为  $2^{13-24}$  )、CGMXCLK 周期;=0,为  $2^{18-24}$  周期),允许 STOP 方式的 LVI 功能(LVISTOP=1),禁止 LVI 复位信号(LVIRSTD=1,禁止),禁止 LVI 电源(LVIPWRD=1 禁止),选择 LVI 为 5V 或 3V 方式(LVI5OR3=1,为 5V;=0,为 3V),选择短 STOP 恢复(SSREC=1,为 32CGMXCLK周期;=0,为 4096 周期),允许 STOP 指令(STOP 位=1),禁止 COP(COPP=1 禁止)。

## 3.6、闪速 FLASH 存储器

MC68HC908GP32 具有 32K FLASH 存储器,它由 FLCR 寄存器(\$FE08)控制写入、擦除,其中 HVEN 为高电压允许位(=1,执行写入或擦除),MASS 为全局擦除位(=1,选择全局擦除),ERASE 为擦除控制位(=1,选择擦除),PGM 为编程选择位(=1,选择编程)。

# 3.6.1、擦除操作

- (1) 置位 ERASE 位(全局擦除时,还应置位 MASS 位)

- (2) 读出 FLASH 块保护寄存器

- (3) 向页地址范围(每页为128字节)内任意 FLASH 地址写入任意值

- (4) 等待至少 10us

- (5) 置位 HVEN 位

- (6) 等待至少 1ms (全局擦除时为 4ms)

- (7) 清零 ERASE 位

- (8) 等待 5us 以上(全局擦除时为 100us)

- (9) 清零 HVEN 位

- (10) lus 后,该存储器可读出

# 3.6.2、编程操作

GP32 的 FLASH 存储器采用行编程方式, 一行为 64 字节 (起始地址为 \$XX00, \$XX40, \$XX80, \$XXC0)。

- (11) 置位 PGM 位

- (12) 读出 FLASH 块保护寄存器

- (13) 向页地址范围内任意 FLASH 单元写入任意位

- (14) 等待 10us 以上

- (15) 置位 HVEN 位

- (16) 等待 5us 以上

- (17) 向一个 FLASH 地址写入编程数据

- (18) 等待 30us 以上

- (19) 重复(7)、(8), 直至一页内各字节编程完成

- (20)清零PGM

- (21) 等待 5us 以上

- (22) 清零 HVEN 位

- (23) 在 lus 以后, 可读出

#### 3. 6. 3、FLASH 块保护

FLASH 块保护寄存器 (FLBPR) (\$FF7E) 可指出保护区首地址,末地址为\$FFFF。FLBR 保护值如下:

\$00=保护全部 FLASH 存储器

\$ 01=保护区: \$ 8080 \$ FFFF \$ 02=保护区: \$ 8100 \$ FFFF

\$FE=保护区: \$FF00<sup>-</sup>\$FFFF

\$FF=不保护

## 3.7、I/O端口

### 3. 7. 1. PA ロ

PA 为双向 I/O 口,作输入时可具有上升电阻(由 PTAPUE 所允许)。在允许时,PA 可用作键盘中断输入。INTKBSCR(\$001A)为键盘状态和控制寄存器,IMASKK 位允许键盘中断(=0),MODER 选择触发方式(=1 为下跳变和负电平,=0 为仅下跳变),KEYF为键盘中断标志位,向 ACK 位写入 1 清零 KEYF。INTKBIER(\$001B)允许 PA 的各位用作键盘输入。

#### 3. 7. 2、PB ロ

PB 为双向 I/0 口,也可用作 A/D 输入。AD 状态控制寄存器的通道选择位决定哪个 PB 口用作 A/D 输入(这时不受 DDRB 所控制)。

## 3. 7. 3、 PC ロ

PC 为 7 位双向 I/O 口, 在作输入时, 可具有上拉电阻 (由 PTCPUE 寄存器所允许)。

#### 3.7.4、PD ロ

PD 为 8 位双向 I/0 口,它也用作定时器和 SPI 引脚。在作输入时,可具有上拉电阻 (由 PTDPUE 寄存器所允许)。

#### 3.7.5, PE ロ

PD 为 2 位双向 I/O 口, 它也用作 SCI 引脚 (这时, 它不受 DDRE 影响)。

## 3.8、SCI和SPI串行口

# 3.8.1、SCI 串行通信接口

GP32 的 SCI 比 HC05C8 的 SCI 功能强,它具有硬件奇偶校验、噪声检测等功能。它有 三个控制寄存器 (SCC1、SCC2、SCC3) 和两个状态寄存器 (SCS1、SCS2)。SCC1 包括: LOOPS (=1, 测试用), ENSCI (=1, 允许 SCI), TXINV (=1, 发送输出为反码), M (字符长度, =1, 9位; =0, 8位), WAKE (唤醒条件, =1, 地址唤醒; =0, 空闲线唤醒), ILTY (空闲线方式, =1,从停止位开始计数:=0,从起始位开始计数),PEN(=1,允许奇偶校验),PTY(=1, 奇校验: =0, 偶校验)。SCC2 包括: SCTIE (=1, 允许 SCI 发送中断), ILCE (=1, 允许发送 完成中断), SCRIE (=1, 允许 SCI 接收中断), ILIE (=1, 允许空闲中断), TE (=1, 允许 发送器), RE (=1, 允许接收器), RWU (=1, 置 SCI 为等待状态), SBK (=1, 发送终止码)。 SCC3 包括: R8 (接收位 8, 只读), T8 (发送位 8), DMARE 和 DMATE (保留位, 应=0), ORIE (=1, 允许接收器溢出中断), NEIE(=1, 允许接收器噪声错中断), FEIE(=1, 允许接收 器帧错误中断), PEIE (=1, 允许接收器奇偶错中断)。SCS1 包括: SCTE (发送缓冲区空标 志,读出 SCS1 再写入 SCDR 时清 0), TC (发送完成标志), SCRF (接收缓冲区空标志,读 出 SCS1 再读出 SCDR 时清 0), IDLE (接收器空闲标志,读出 SCS1 再读出 SCDR 时清 0), OR (接收器溢出标志,读出 SCS1 再读出 SCDR 时清 0), NF (接收器噪声标志,在一位的三次 测试中不相同置位,读出 SCS1 再读出 SCDR 时清 0),FE (接收器帧错误标志,读出 SCS1 再读出 SCDR 时清 0), PE (接收器奇偶错标志,读出 SCS1 再读出 SCDR 时清 0)。 SCS2 包括: BKF(终止码标志。读出 SCS1 再读出 SCDR 时清 0), RPF(正在接收标志)。SCDR 为接收(读) /发送(写)缓冲器,地址\$0018。SCBR(\$0019)设置波特率,它与 HC05C8 的 BAUD 寄存 器相同。在 Fbus=4.9152MHZ 时, 取 SCBR=\$03, 可设波特率为 9600。

# 3.8.2、SPI 串行外围接口

GP32 的 SPI 与 HC05C8 的 SPI 基本相同,只是它增加了出错标志,有分开的接收与发送中断和灵活的 I/0 脚控制。SPI 有两个控制和状态寄存器。SPCR(\$0010)包括: SPRIE (=1,允许接收中断),DMAS (保留位),SPMSTR (=1,主机方式),CPOL 和 CPHA (设置 SPSCK 时钟相位,同 HC05C8),SPWOM (=1,允许 SPSCK、MOSI 和 MISO 脚为开漏输出),SPE (=1,允许 SPI),SPTIE (=1,允许发送中断)。SPSCR (\$0011)包括: SPRF (接收缓冲器满标志,读出 SPSCR 再读出 SPDR 时清 0),ERRIE (=1,允许出错中断),OVRF (溢出错标志,读出 SPSCR 再读出 SPDR 时清 0),MODF (方式错标志,读出 SPSCR 再读出 SPDR 时清 0),SPTE (发送缓冲区空标志),MODFEN (方式错允许位,=1,允许检测方式错; =0,不检测,这时主机方式时,SS可用作通用 I/0 口),SPR1 和 SPR0 (SPI 波特率选择,00,CGM 输出二分频;01,八分频;10,32分频;11,128分频)。SPDR 为接收(读)/发送(写)数据寄存器,地址为\$0012。

## 3.9、定时器

## 3.9.1、定时器接口模块 (TIM)

GP32 有两个定时器接口模块 (TIM1、TIM2), 每个 TIM 有以下功能:

- 两个输入捕获/输出比较通道:

- 一上升、下降、或任何跳变输入捕捉触发

- 一置位、清零、取反输出比较操作

- 缓冲或非缓冲脉宽调制 (PWM) 发生

- TIM 时钟可程控为内部总线时钟的七种分频值

- 自由运行或取模加1计数操作

- 溢出时变换通道

- TIM 计数器停止和复位位

- (1) 计数器分频: 由 TSC 寄存器的 PS2 PS0 选择为内部总线时钟的 1 64 分频

- (2) 计数控制: 计数器模数寄存器 (TiMODH、TiMODL) 可控制计数器的最大计数值。在 计数器达到 TiMOD 值时, 清 0 计数器, 并置位溢出标志 (TOF)。

- (3) 输入捕获:由TiSCj寄存器的MSjB和MSjA位=00选择为输入捕捉方式,ELSjB和ELSjA位=01,上升沿捕捉;=10,下降沿捕捉;=11,上升或下降沿捕捉。发生捕捉时置位CHjF标志(读出TiSCj再向CHjF写入0时清0),并把计数器值(TCNTH、TCNTL)存入TCHjH、TCHjL中。

- (4) 非缓冲输出比较:由 TiSCj 寄存器的 MSjB 和 MSjA 位=01 选择为输出比较方式,ELSjB 和 ELSjA 位=01,比较完成时取反输出;10,清零输出;=11,置位输出。TCHjH、TCHjL 为输出比较值,它们与计数器值相同时为比较完成,这时置位 CHjF 标志。

- (5) 非缓冲 PWM: 使用计数器模数寄存器和 TOVj (TiSCj 寄存器中)位可使计数器在达到计数器模数寄存器值时置位溢出位 (TOF), 并取反输出位。以后再由输出比较置位或清零,从而可输出宽度可变的脉冲。它的周期由计数器模数寄存器决定,脉宽由输出比较决定。

- (6) 缓冲输出比较和 PWM: 通道 0 和 1 可相连,构成缓冲输出比较或 PWM。可置通道 0 的 MS 0B 位=1。这时通道 0 的寄存器控制脉冲宽度,写入通道 1 寄存器可使通道 1 同步地控制下一个输出比较或 PWM 周期。在每次溢出后,最后写入的通道成为现行控制通道。通道 0 的控制和状态寄存器 (TSC0) 控制和监视缓冲操作。TSC1 不使用。通道 1 的脚 (TCH1) 可用作通用 I/0 脚。

- (7) 定时器中断: TIM 状态和控制寄存器 (TSC) 的 TOIE 允许计数器溢出中断 (标志为 TOF, 读出 TSC 再向 TOF 写入 0 清 0)。每个通道有一个中断允许位 (CHjIE) 和中 断标志位 (CHjF)。

- (8) 其他操作: 置位 TSC 的 TSTOP 位可停止 TIM 计数器。向 TSC 的 TRST 位写入 1 可复位 TIM 计数器和预分频器。

置位各通道的 CH jMAX 位 (在 TOV j 位=0 时) 可使 PWM 输出为 100%。

# 3.9.2、定时基模块(TBM)

TBM 可产生周期性中断,可选择 8 种速率。它由 TBCR (\$001C)的 TBR2 TBR0 所控制,在 fOSC1=32.768KHZ 时,TBM 速率如下表:

|      |      |      |         | Timerbase interrupt Rate |       |  |

|------|------|------|---------|--------------------------|-------|--|

| TBR2 | TBR1 | TBR0 | Divider | Hz                       | ms    |  |

| 0    | 0    | 0    | 32,768  | 1                        | 1000  |  |

| 0    | 0    | 1    | 8192    | 4                        | 250   |  |

| 0    | 1    | 0    | 2048    | 16                       | 62.5  |  |

| 0    | 1    | 1    | 128     | 256                      | ~3.9  |  |

| 1    | 0    | 0    | 64      | 512                      | ~2    |  |

| 1    | 0    | 1    | 32      | 1024                     | ~1    |  |

| 1    | 1    | 0    | 16      | 2048                     | ~0.5  |  |

| 1    | 1    | 1    | 8       | 4096                     | ~0.24 |  |

表 3-3 定时基速率选择 (fOSC1=32.768KHZ)

TBCR 的 TBIE 为 TBM 中断允许位, TBIF 为中断标志位, 向 TACK 位写入 1 清 0 TBIF 位, TBON 为定时基允许位 (=1, 允许; =0, 禁止)。

# 3.10、电气参数

在 5V 电源时,运行电流小于 30mA,等待电流小于 12mA,允许 TBM 时停止电流约为 20uA,允许 LVI 和 TBM 时停止电流约为 300uA。 I/0 口的吸流、放流值为 10mA,上拉电阻约为  $33K\Omega$ 。低电压复位阀值约为  $4.3^{-}4.4V$ 。晶振频率为  $30^{-}100KHZ$ ,外部时钟为  $DC^{-}32.8MHZ$ ,内部总线频率最高为 8.2MHZ。

在 3V 电源时,电流分别为 10mA、6mA、12uA、200uA。低电压复位阀值约为  $2.6^-2.66V$ 。 外部时钟为  $DC^-16.4MHZ$ ,内部总线频率最高为 4.1MHZ。