# PDIUSBD12: 带并行总线的 USB 接口器件

# 特性

- 符合通用串行总线(USB)1.1版规范

- 高性能 USB 接口器件,集成了 SIE、FIFO 存储器、收发器以及电压调整器

- 符合大多数器件的分类规格

- 可与任何外部微控制器/微处理实现高速并行接口(2M字节/秒)

- 完全自治的直接内存存取(DMA)操作

- 集成 320 字节多结构 FIF0 存储器

- 主端点的双缓冲配置增加了数据吞吐量并轻松实现实时数据传输

- 在批量模式和同步模式下均可实现 1M 字节/秒的数据传输速率

- 具有良好 EMI 特性的总线供电能力

- 在挂起时可控制 LazyClock 输出

- 可通过软件控制与 USB 的连接

- 采用 GoodLink 技术的连接指示器, 在通讯时使 LED 闪烁

- 可编程的时钟频率输出

- 符合 ACPI、OnNOW 和 USB 电源管理的要求

- 内部上电复位和低电压复位电路

- 有 S028 和 TSS0P28 封装

- 工业级操作温度: -40℃~+85℃

- 高于 8kV 的在片静电防护电路,减少了额外元件的费用

- 具有高错误恢复率(>99%)的全扫描设计确保了高品质

- 双电源操作: 3.3±0.3V 或扩展的 5V 电源, 范围为 3.6~5.5V

- 多中断模式实现批量和同步传输

### 描述

PDIUSBD12 是一款性价比很高的 USB 器件。它通常用作微控制器系统中实现与微控制器进行通信的高速通用并行接口。它还支持本地的 DMA 传输。

这种实现 USB 接口的标准组件使得设计者可以在各种不同类型微控制器中选择出最合适的微控制器。这种灵活性减小了开发的时间、风险以及费用(通过使用已有的结构和减少固件上的投资),从而用最快捷的方法实现最经济的 USB 外设的解决方案。

PDIUSBD12 完全符合 USB1.1 版的规范。它还符合大多数器件的分类规格:成像类、海量存储器件、通信器件、打印设备以及人机接口设备。同样地,PDIUSBD12 理想地适用于许多外设,例如:打印机、扫描仪、外部的存储设备(Zip 驱动器)和数码相机等等。它使得当前使用 SCSI 的系统可以立即降低成本。

PDIUSBD12 所具有的低挂起功耗连同 LazyClock 输出可以满足使用 ACPI、OnNOW 和 USB 电源管理 的要求。低的操作功耗可以应用于使用总线供电的外设。

此外它还集成了许多特性,包括  $SoftConnet^{TM}$ 、 $GoodLink^{TM}$ 、可编程时钟输出、低频晶振和终止寄存器集合。所有这些特性都为系统显著节约了成本,同时使 USB 功能在外设上的应用变得容易。

### 订购信息

| 封装           | 温度范围       | 编号           |

|--------------|------------|--------------|

| 28 脚塑料 SO    | -40°C~85°C | PDIUSBD12 D  |

| 28 脚塑料 TSSOP | -40℃~85℃   | PDIUSBD12 PW |

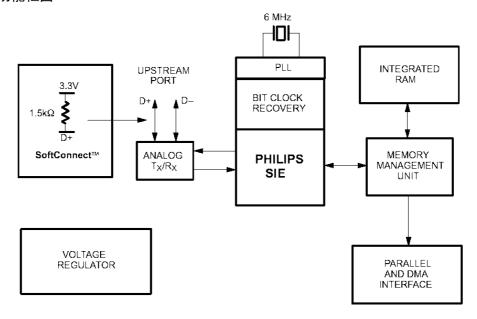

## 功能框图

注:这是一个概念性的框图,并不包括每一个单独的信号

### 模拟收发器

集成的收发器接口可通过终端电阻直接与 USB 电缆相连。

#### 电压调整器

片内集成了一个 3.3V 的调整器用于模拟收发器的供电。该电压还作为输出连接到外部 1.5k $\Omega$ 的上拉电阻。可选择 PDIUSBD12 提供的带 1.5k $\Omega$ 内部上拉电阻的软件连接技术。

#### PLL

片内集成了 6M 到 48M 时钟乘法 PLL。这样就可使用低成本的 6M 晶振。EMI 也随之降低。PLL 的工作不需要外部元件。

### 位时钟恢复

位时钟恢复电路使用 4X 过采样规则,从进入的 USB 数据流中恢复时钟。它能跟踪 USB 规定范围内的抖动和频漂。

## Philips 串行接口引擎 (PSIE)

Philips SIE 实现了全部的 USB 协议层。完全由硬件实现而不需要固件的参与。该模块的功能包括:同步模式的识别、并行/串行转换、位填充/解除填充、CRC 校验/产生、PID 校验/产生、地址识别和握手评估/产生。

## SoftConnect™

与 USB 的连接是通过 1.5kΩ上拉电阻将 D+ (用于高速 USB 器件)置为高实现的。1.5kΩ上拉电阻集成在 PDIUSBD12 片内,默认状态下不与 VCC 相连。连接的建立通过外部/系统微控制器发送命令来实现。这就允许系统微控制器在决定与 USB 建立连接之前完成初始化时序。USB 总线连接可以重新初始化而不需要拔出电缆。

PDIUSBD12 在连接可以建立之前会检测 USB VBUS 是否可用。VBUS 可通过 EOT\_N 管脚进行检测。详情请参阅管脚描述一节。

需要注意的是,内部电阻的误差(25%)大于 USB 规格的 5%。但用于连接的 VSE 电压规格仍然有足够的余量。SoftConnect™ 是 Philips 半导体一项尚未获批准的专利技术。

#### GoodLink™

GoodLink™ 技术可提供良好的 USB 连接指示。在枚举中,LED 指示根据通信的状况间歇闪烁。当 PDIUSBD12 成功地枚举和配置后,LED 指示将一直点亮。随后与 PDIUSBD12 之间成功的传输(带应答)将关闭 LED,处于挂起状态时,LED 将会关闭。

该特性为 USB 器件、集线器和 USB 通信状态提供了用户友好的指示。作为一个诊断工具,它对隔离故障的设备是很有用的。该特性降低了现场支持和热线的成本。

#### 存储器管理单元(MMU)和集成 RAM

在以 12M/s 的速率传输并与微控制器并口相连时, MMU 和集成 RAM 作为 USB 之间速度差异的缓冲区。这就允许微控制器以它自己的速率对 USB 信息包进行读写。

### 并行和 DMA 接口

一个普通的并行接口定义成易于使用,快速而且可以与主流的微控制器直接接口。对一个微控制器而言,PDIUSBD12 看起来就象一个带 8 位数据总线和一个地址位(占用 2 个位置)的存储器件。PDIUSBD12 支持多路复用和非复用的地址和数据总线。还支持主端点与本地共享 RAM 之间直接读取的 DMA 传输。支持单周期和突发模式的 DMA 传输。

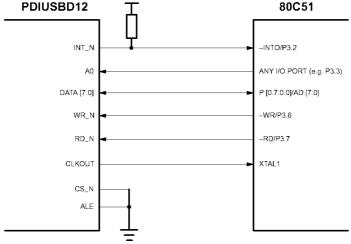

#### 与80051并行接口举例

在该例中,ALE 接为低电平,表示一个独立的地址和数据总线配置。PDIUSBD12 的 A0 脚与 80C51 的任意一个 I/O 口相连。该端口控制 PDIUSBD12 的命令和数据状态。80C51 的多位地址和数据总线可直接与 PDIUSBD12 的数据总线相连。80C51 的频率输入可由 PDIUSBD12 的 CLKOUT 提供。

### DMA 传输

直接存储器寻址 (DMA) 允许在主端点和本地共享存储器间实现数据块的有效传输。使用 DMA 控制器, PDIUSBD12 的主端点和本地共享存储器间的数据传输可自主进行而不需要本地 CPU 的干预。要处理任何 DMA 传输,本地 CPU 从主机接收必要的 SETUP 信息并对 DMA 控制器进行相应的编程。典型的,对 DMA 控制器的传输模式、字节计数寄存器和地址计数器进行正确的编程。在该模式下,PDIUSBD12 发出请求时开始传输,当字节计数器减少为零时终止。在 DMA 控制器编程之后,本地 CPU 在初始化传输时将 PDIUSBD12 中的 DMA 使能位置位。

PDIUSBD12 可编程为单周期 DMA 或突发模式 DMA。在单周期 DMA 中,DMREQ 在每单个应答后直到被 DMACK\_N 重新激活之前保持无效。在突发模式 DMA 中,DMREQ 在器件中突发编程时一直保持有效。该过程持续到 PDIUSBD12 通过 EOT\_N 接收到一个 DMA 终止信息。这时产生一个中断指示本地CPU,DMA 操作已经完成。

在 DMA 读操作时,DMREQ 仅当缓冲区完全表示主机成功的发送了一个信息包到 PDIUSBD12 时才有效。由于具有双缓冲配置,主机可以在第一个缓冲区被读出时对第二个缓冲区进行填充。这种并行的处理有效的增加了数据吞吐量。当主机没有完全填满缓冲区的情况下(单向 ISO 配置时小于 64 或 128 字节),

DMREQ 会在缓冲区的最后一个字节时无效,而不管当前的 DMA 突发计数。在更新了 DMA 突发计数的下一个包发送时,DMREQ 再次被激活。

DMA 的写操作与之相似,当缓冲区未装满时,DMREQ 一直有效。当缓冲区填满时,在下一个 IN 标志将信息包送入主机,当传输完成之后 DMREQ 变为无效。同样的,双缓冲配置在这也改善了数据的吞吐量。在非同步传输中(批量模式和中断),在数据被发送到主机之前,缓冲区需要通过 DMA 写操作完全装满。唯一的例外是,在 DMA 传输结束时,EOT\_N 接收的信号将会停止 DMA 写操作并且在下一个 IN 标志置位时将缓冲区的内容传送到主机。

在同步模式中,本地 CPU 和 DMA 控制器必须保证它们在一个 USB 帧(1ms)中能够吞吐的最大信息包的规模。DMACK\_N 的激活将自动选择主端点(端点 2)而不管当前选择的端点。PDIUSBD12 的 DMA 操作可通过普通的 I/O 对其它端点的存取实现交叉存取。DMA 操作可通过以下方式终止:复位 DMA 使能寄存器位或 EOT N 加上 DMACK N 以及 RD N/WR N 的激活。

PDIUSBD12 支持单地址模式中的 DMA 传输,也可以在 DMA 控制器的双地址模式中工作。在单地址模式中,DMA 通过 DREQ,DMACK\_N,EOT\_N,WR\_N 和 RD\_N 控制线实现传输。在双地址模式中,DMREQ,DMACK\_N 和 EOT\_N 未用,取而代之的是 CS\_N,WR\_N 和 RD\_N 控制信号。需要遵循 PDIUSBD12 的 I/O 模式传输协议。在读周期中对 DMAC 信号源进行访问,在写周期对目标进行访问。传输需要两个单独的总线周期来储存暂存在 DMAC 中的数据。

## 端点描述

PDIUSBD12 的端点适用于不同类型的设备,例如图像、打印机、海量存储器和通信设备。端点可通过 "Set Mode"命令配置为 4 种不同的模式,分别为:

模式 0 (Non-ISO 模式): 非同步传输

模式 1 (ISO-OUT 模式): 同步输出传输

模式 2 (ISO-IN 模式): 同步输入传输

模式 3 (ISO-IO 模式): 同步输入输出传输

## 模式 0(非同步模式)

| 端点数 | 端点索引   | 传输类型         | 端点类型     | 方向       | 最大信息包规<br>格(字节)                    |

|-----|--------|--------------|----------|----------|------------------------------------|

| 0   | 0<br>1 | 控制输出<br>控制输入 | 默认       | 输出<br>输入 | 16<br>16                           |

| 1   | 2 3    | 普通输出<br>普通输入 | 普通<br>普通 | 输出<br>输入 | 16<br>16                           |

| 2   | 4<br>5 | 普通输出<br>普通输入 | 普通<br>普通 | 输出<br>输入 | 64 <sup>4</sup><br>64 <sup>4</sup> |

### 模式 1(同步输出模式)

| 端点数 | 端点索引   | 传输类型         | 端点类型     | 方向       | 最大信息包规<br>格(字节)  |

|-----|--------|--------------|----------|----------|------------------|

| 0   | 0<br>1 | 控制输出<br>控制输入 | 默认       | 输出<br>输入 | 16<br>16         |

| 1   | 2 3    | 普通输出<br>普通输入 | 普通<br>普通 | 输出<br>输入 | 16<br>16         |

| 2   | 4      | 同步输出         | 同步       | 输出       | 128 <sup>4</sup> |

# 模式 2(同步输入模式)

| 端点数 | 端点索引   | 传输类型         | 端点类型     | 方向       | 最大信息包规<br>格(字节) |

|-----|--------|--------------|----------|----------|-----------------|

| 0   | 0<br>1 | 控制输出<br>控制输入 | 默认       | 输出<br>输入 | 16<br>16        |

| 1   | 2 3    | 普通输出<br>普通输入 | 普通<br>普通 | 输出<br>输入 | 16<br>16        |

| 2   | 4      | 同步输入         | 同步       | 输入       | 1284            |

模式 3 (同步输入/输出模式)

| 端点数 | 端点索引   | 传输类型         | 端点类型     | 方向       | 最大信息包规<br>格(字节)                    |

|-----|--------|--------------|----------|----------|------------------------------------|

| 0   | 0<br>1 | 控制输出<br>控制输入 | 默认       | 输出<br>输入 | 16<br>16                           |

| 1   | 2 3    | 普通输出<br>普通输入 | 普通<br>普通 | 输出<br>输入 | 16<br>16                           |

| 2   | 4<br>5 | 同步输出<br>同步输入 | 同步<br>同步 | 输出<br>输入 | 64 <sup>4</sup><br>64 <sup>4</sup> |

## 主端点

主端点(端点 2)在有些方面是比较特别的。它是进行吞吐大数据的主要端点。同样地,它执行主机的特性以减轻传输大数据的任务:

- 1. 双缓冲。允许 USB 与本地 CPU 之间的并行读写操作,这样就增加了数据的吞吐量。缓冲区 切换是自动处理的。这导致了透明的缓冲区操作。

- 2. 支持 DMA(直接存储器访问)操作。可以和对其它端点的正常 I/O 操作交叉进行。

- 3. DMA 操作中的自动指针处理。在跨过缓冲区边界时不需要本地 CPU 的干预。

- 4. 可配置为同步传输或非同步(批量和中断)传输

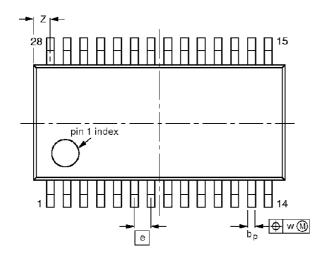

## 管脚配置

## 管脚描述

| 管脚 | 符号      | 类型    | 描述                                                       |

|----|---------|-------|----------------------------------------------------------|

| 1  | DATA<0> | IO2   | 双向数据位 0                                                  |

| 2  | DATA<1> | IO2   | 双向数据位 1                                                  |

| 3  | DATA<2> | IO2   | 双向数据位 2                                                  |

| 4  | DATA<3> | IO2   | 双向数据位 3                                                  |

| 5  | GND     | P     | 地                                                        |

| 6  | DATA<4> | IO2   | 双向数据位 4                                                  |

| 7  | DATA<5> | IO2   | 双向数据位 5                                                  |

| 8  | DATA<6> | IO2   | 双向数据位 6                                                  |

| 9  | DATA<7> | IO2   | 双向数据位 7                                                  |

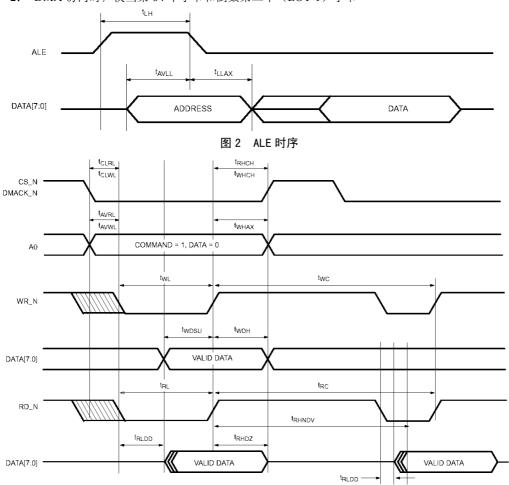

| 10 | ALE     | I     | 地址锁存使能。在多路地址/数据总线中,下降沿关闭地址信息<br>锁存。将其固定为低电平用于单地址/数据总线配置。 |

| 11 | CS_N    | I     | 片选 (低有效)                                                 |

| 12 | SUSPEND | I,OD4 | 器件处于挂起状态                                                 |

| 13 | CLKOUT  | O2    | 可编程时钟输出()                                                |

| 14 | INT_N   | OD4   | 中断(低有效)                                                  |

| 15 | RD_N             | I   | 读选通(低有效)                                                                          |

|----|------------------|-----|-----------------------------------------------------------------------------------|

| 16 | WR_N             | I   | 写选通(低有效)                                                                          |

| 17 | DMREQ            | O4  | DMA 请求                                                                            |

| 18 | DMACK_N          | I   | DMA 应答(低有效)                                                                       |

| 19 | EOT_N            | I   | DMA 传输结束(低有效)。EOT_N 仅当 DMACK_N 和 RD_N 或 WR_N 一起激活时才有效。                            |

| 20 | RESET_N          | Ι   | 复位(低有效且不同步)。片内上电复位电路,该管脚可固定接<br>V <sub>CC</sub> 。                                 |

| 21 | GL_N             | OD8 | GoodLink LED 指示器(低有效)                                                             |

| 22 | XTAL1            | I   | 晶振连接端 1(6MHz)                                                                     |

| 23 | XTAL2            | О   | 晶振连接端 2(6MHz)。如果采用外部时钟信号取代晶振,可连接 XTAL1, XTAL2 应当悬空。                               |

| 24 | V <sub>CC</sub>  | P   | 电源电压(4.0V~5.5V), 要使器件工作在 3.3V, 对 V <sub>CC</sub> 和 V <sub>OUT3.3</sub> 脚都提供 3.3V。 |

| 25 | D-               | A   | USB D-数据线                                                                         |

| 26 | D+               | A   | USB D+数据线                                                                         |

| 27 | $V_{\rm OUT3.3}$ | P   | 3.3V 调整输出。要使器件工作在 3.3V, 对 V <sub>CC</sub> 和 V <sub>OUT33</sub> 脚都提供 3.3V。         |

| 28 | A0               | I   | 地址位。A0=1 选择命令指令,A0=0 选择数据。该位在多路地址/数据总线配置时可忽略,应将其接高电平。                             |

注: O2 : 2mA 驱动输出 OD4 : 4mA 驱动开漏输出

OD8: 8mA 驱动开漏输出 IO2: 4mA 输出

# 命令汇总

| 命令名     | 接收者     | 编码    | 数据       |

|---------|---------|-------|----------|

|         |         | 初始化命令 | 1        |

| 设置地址/使能 | 器件      | D0h   | 写1字节     |

| 设置端点使能  | 器件      | D8h   | 写1字节     |

| 设置模式    | 器件      | F3h   | 写 2 字节   |

| 设置 DMA  | 器件      | FBh   | 写/读1字节   |

|         |         | 数据流命令 |          |

| 读中断寄存器  | 器件      | F4h   | 读 2 字节   |

| 选择端点    | 控制输出    | 00h   | 读1字节(可选) |

|         | 控制输入    | 01h   | 读1字节(可选) |

|         | 端点1输出   | 02h   | 读1字节(可选) |

|         | 端点1输入   | 03h   | 读1字节(可选) |

|         | 端点2输出   | 04h   | 读1字节(可选) |

|         | 端点2输入   | 05h   | 读1字节(可选) |

| 读最后处理状态 | 控制输出    | 40h   | 读1字节     |

|         | 控制输入    | 41h   | 读1字节     |

|         | 端点1输出   | 42h   | 读1字节     |

|         | 端点1输入   | 43h   | 读1字节     |

|         | 端点2输出   | 44h   | 读1字节     |

|         | 端点2输入   | 45h   | 读1字节     |

| 读缓冲区    | 选择的端点   | F0h   | 读n字节     |

| 写缓冲区    | 选择的端点   | F0h   | 写n字节     |

| 设置端点状态  | 控制输出    | 40h   | 写1字节     |

|         | 控制输入    | 41h   | 写1字节     |

|         | 端点1输出   | 42h   | 写1字节     |

|         | 端点1输入   | 43h   | 写1字节     |

|         | 端点2输出   | 44h   | 写1字节     |

|         | 端点 2 输入 | 45h   | 写1字节     |

| 应答设置    | 选择的端点   | F1h   | 无        |

| 缓冲区清零   | 选择的端点   | F2h   | 无        |

| 使缓冲区有效  | 选择的端点   | FAh   | 无        |

|         |         |       |          |

| 普通命令   |  |     |        |  |

|--------|--|-----|--------|--|

| 发送恢复   |  | F6h | 无      |  |

| 读当前帧数目 |  | F5h | 读1或2字节 |  |

### 命令描述

有3种基本的类型的命令:初始化,数据流和通用命令。

## 初始化命令

初始化命令在 USB 网络进行枚举处理时使用。这些命令用于使能端点的功能。还可用来设置 USB 分配的地址。

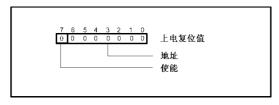

## 设置地址/使能

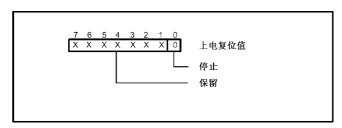

命令: D0h

处理:写1字节

该命令用于设置 USB 分配的地址和使能功能。

地址 写入的值即为地址

使能 置1使能该功能

### 设置端点使能

命令: D8h

处理: 写1字节

通过设置设置地址/使能命令后才可使能普通/同步端点。

普通/同步

端点 值 1 表示普通/同步端点使能

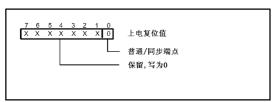

### 设置模式

命令: F3h

处理: 写2字节

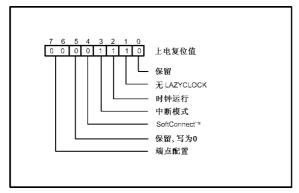

设置模式命令后跟 2 个写入的数据,第一个字节包含配置字节信息,第二个字节是时钟分频因素字节。 配置字节

无 LazyClock 1表示 CLKOUT 不会切换到 LazyClock。0表示 CLKOUT 在 Suspend 脚变高之后切换

到 LazyClock。LazyClock 频率是 30KHz±40%。编程值将不过会被总线复位所改变。

时钟运行 1表示内部时钟和 PLL 即使在挂起状态下仍然运行, 0表示只要不需要时, 内部时钟、

晶振和 PLL 就停止运行。为了满足严格的挂起电流要求,该位需要设置为 0。已编程

的值不会被总线复位所改变。

中断模式 1 表示报告所有的错误和"NAKing"并产生一个中断。0 表示只有 OK 被报告。编程

值不会被总线复位所改变。

SoftConnect 1表示如果 VBUS 可用,上行数据上拉电阻就被连接。0表示不连接。已编程的值不

会被总线复位所改变。

端点配置 该 2 位设置端点配置如下:

模式 0 (非同步模式) 模式 1 (同步输出模式) 模式 2 (同步输入模式)

模式3(同步输入/输出模式)

更多细节请参阅有关端点的描述。

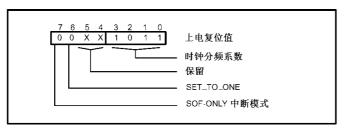

## 时钟分频系数字节

时钟分频系数 该值用来表示 CLKOUT 的时钟分频系数。用 N 表示分频系数,那么输出频率就为 48MHz/(N+1)。复位值为 11。这产生 4MHz 的输出频率,然后可由用户自行调节。当 N 为 0 时,得到最大频率 48MHz。当 N 取最大 11 时,得到最小频率 4MHz。PDIUSBD12 的设计确保了在改变频率时不会出现干扰。已编程的值不会被总线复位所改变。

SET\_TO\_ONE 该位需要在任何 DMA 读或写操作之前置为 1。该位在上电复位值为 0。复位后可将 其一直设为 1。

仅有 SOF 中断模式 将该位置 1 后,仅当帧时钟的起始(SOF)时刻引起中断的产生,而不管引脚中断模式的设置状态(设置 DMA 位 5)。

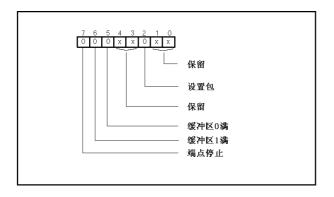

# 设置 DMA

命令: FBh

处理:读/写1字节

设置 DMA 命令后跟 1 个字节数据写入/读出 DMA 配置寄存器。

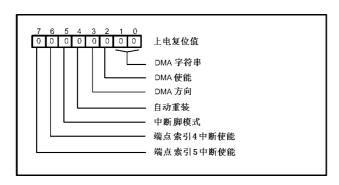

#### DMA 配置寄存器

在 DMA 操作中,两字节的缓冲区头(状态和字节长度信息)不参与传送。这就允许了 DMA 数据的连续性,不插入信息头。 DMA 读操作时,信息头被 PDIUSBD12 跳过。见读缓冲区命令。在 DMA 写操作时,信息头由 PDIUSBD12 自动添加。这就提供了一个简洁的 DMA 数据传输。

DMA 突发串 选择 DMA 操作的突发串长度:

00 单周期 DMA

01 突发串 (4 周期) DMA

10 突发串 (8 周期) DMA

11 突发串 (16 周期) DMA

DMA 使能 向该位写入 1 会通过激活 DMREQ 启动 DMA 操作。在激活 DMREQ 之前需要

装满(DMA 读操作)或清空(DMA 写操作)主端点缓冲区。在单周期 DMA模式中,DMREQ 在突发串数目耗尽后无效。然后下一个突发串时重新激活。这个过程一直持续到 EOT\_N 和 DMACK\_N 以及 RD\_N 或 WR\_N 一起被激活,此

时将该位置 0 并终止 DMA 操作。DMA 操作也可通过直接向该位写入 0 来终止。

DMA 方向 该位决定了 DMA 传输时数据流的方向。1 表示从外部共享存储器到 PDIUSBD12

(DMA 写操作); 0表示从 PDIUSBD12 到外部共享存储器 (DMA 读操作)。

自动重装 当该位设为 1, DMA 操作会自动重新启动。

中断脚模式 0表示正常的中断脚模式,中断寄存器所有位的逻辑或产生中断。当该位写入1

时表示中断会在 USB 总线上行数据流出现帧时钟(SOF) 起始位时产生中断。

其它中断仍然有效。

端点索引 4 中断使能 该位为 1 表示只要端点缓冲区包含一个有效的信息包就会产生中断。通常在 DMA 操作时关闭以减少不必要的 CPU 响应。

端点索引 5 中断使能 该位为 1 表示只要端点缓冲区有效(见缓冲区生效命令)就会产生中断。通常在 DMA 操作时关闭以减少不必要的 CPU 响应。

### 中断模式

| 时钟分频系数寄存器位 7:<br>仅有 SOF 中断模式 | 设置 DMA 寄存器位 5:<br>中断脚模式 | 中断类型      |

|------------------------------|-------------------------|-----------|

| 0                            | 0                       | 正常中断      |

| 0                            | 1                       | 正常中断+SOF  |

| 1                            | X                       | 仅有 SOF 中断 |

#### 数据流命令

数据流命令用于管理 USB 端点和外部微控制器之间的数据传输。通过微控制器中断初始化大量的数据流。微控制器利用这些命令访问和决定端点的 FIFO 是否含有有效的数据。

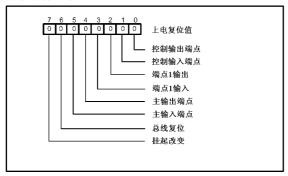

## 读中断寄存器

命令: F4h

处理:读2字节

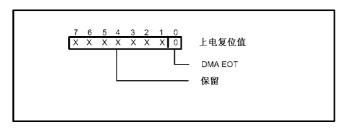

中断寄存器字节1

中断寄存器字节2

该命令指示中断的来源。通过读端点最后处理状态寄存器将端点中断位(位  $0\sim5$ )清零。其它位在读中断寄存器后被清零。

总线复位 在总线复位后将产生一个中断将该位置 1。总线复位与通过 RESET N 脚的硬件

复位基本相同,有一点除外,就是总线复位产生一个中断并且器件在默认地址0

处使能。

挂起改变 当 PDIUSBD12 没有收到 3 个 SOF 时,将会进入挂起状态并将挂起改变位置位。

任何挂起或唤醒状态的改变都会将该位置位并产生中断。

DMA EOT 该位表示 DMA 操作已结束。

### 选择端点

命令: 00-05h

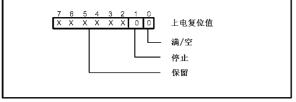

处理: 可选读1字节

选择端点命令将内部指针初始化到选择的缓冲区起始位置。可选的,该命令可跟一个返回的读出字节。

满/空 1表示缓冲区已满,0表示缓冲区为空。

停止 1表示选择的端点处于停止状态。

### 读端点状态

命令: 80-85h 处理: 读1字节

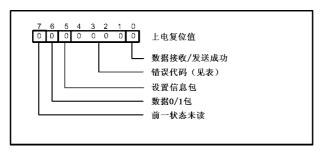

### 读最后处理状态寄存器

命令: 40-45h

处理:读1字节

读最后处理状态寄存器命令后跟一个数据返回端点最后处理的状态。该命令同时复位中断寄存器中的相应位并将状态清零表示已经读取。由于它保留了每次处理的记录,所以该命令在以调试为目的时很有用。 在每次新的处理之后会将原来的状态信息覆盖。

数据接收/发送成功 1表示数据已经成功地接收或发送。

错误代码 见下表

SETUP 信息包 1 表示最后成功接收的信息包有一个 SETUP 标志 (对 IN 缓冲区进行读总为 0)

数据 0/1 包 1 表示最后成功接收/发送包含有一个 DATA1 PID。 前一状态未读 1 表示在前一状态被读出之前发生了第二个事件

# 错误代码

| 错误代码 | 结果                              |

|------|---------------------------------|

| 0000 | 无错                              |

| 0001 | PID 编码错误: 位 7-4 不是位 3-0 的取反     |

| 0010 | PID 未知:编码有效,但 PID 不存在           |

| 0011 | 不期望的信息包:不是所期望的信息包(=标志,数据        |

|      | 或应答)或 SETUP 标志指向非控制端点           |

| 0100 | 标志 CRC 错误                       |

| 0101 | 数据 CRC 错误                       |

| 0110 | 时间溢出错误                          |

| 0111 | 串扰错误                            |

| 1000 | 不期望的信息包结束                       |

| 1001 | 发送或接收 NAK                       |

| 1010 | 发送停止,已接收到标志,但端点已停用。             |

| 1011 | 溢出错误,接收的信息包大于可用的缓冲区空间           |

| 1101 | Bitstuff 错误                     |

| 1111 | 错误 DATA PID:接收的 DATA PID 不是所期望的 |

### 读缓冲区

命令: F0h

处理: 读多个字节(最大130)

读缓冲区命令后,返回一系列从选择的端点数据缓冲区读出的数据。每读一个字节,内部缓冲区指针自动加一。读缓冲区命令不会将缓冲区指针复位到缓冲区起始端。这意味着可被其它的命令所中断(选择端点命令除外)。

缓冲区数据结构如下:

字节1:保留:可为任意值

字节 2: 数据字节的数目/长度

字节3:数据字节1

字节4:数据字节2

. . . . . .

头两个字节在 DMA 读操作中可跳过。因此第一个读出的字节是数据字节 1。第二个读出的是数据字节 2,等等。PDIUSBD12 可通过 USB 信息包的 EOP 终止来决定包的最后一个字节。

#### 写缓冲区

命令: F0h

处理: 写多个字节(最大130)

写缓冲区命令后跟一系列需要写入端点缓冲区的数据。数据的结构必须与前面描述的读缓冲区命令一样。第一个字节(保留)总为 0。在 DMA 写操作中,头两个字节会被绕过。因此,第一个写入的字节是数据字节 1。第二个写入的是数据字节 2,等等。在非同步传输(批量或中断)中,数据被发送到主机之前缓冲区必须被完全填满并切换到下一个缓冲区。例外的情况是,当前的缓冲区内容将要被发送到主机时,由有效的 EOT N 指示 DMA 传输的结束。

#### 警告:

越过缓冲区边界的写入/读出或写入 OUT 缓冲区或读出 IN 缓冲区都是不受保护的。其中的任何一个都会导致错误的操作。OUT 缓冲区的数据只在成功发送之后才有意义。例外的情况是在主端点的 DMA 操作时,指针在到达边界(双缓冲结构)后会自动指向第二个缓冲区。

### 清缓冲区

命令: F2h

处理: 无

当一个信息包完全接收之后,内部端点缓冲区满标志置位。所有后续的包将被返回的 NAK 拒绝。当 微控制器已读取数据,它应当通过清缓冲区命令来释放缓冲区。。当缓冲区清空之后,新的信息包就可被接受了。

### 使缓冲区有效

命令: Fah

处理: 无

当微控制器已将数据写入 IN 缓冲区,它应当通过使缓冲区有效命令设置缓冲区满标志。这表示缓冲区内的数据有效并可在接收到下一个 IN 标志时将其送入主机。

### 设置端点状态

命令: 40-45h

处理: 写1字节

当一个停止控制的端点接收到 SETUP 标志时自动解除停止,而不管信息包的内容如何。如果端点应当停在停止状态,微控制器可以重新停止它。

当一个停止的端点解除了停止(设置端点命令或接收到一个 SETUP 标志),它同时被重新初始化。将缓冲区刷新,如果是OUT缓冲区就等待一个DATA 0 PID,如果是IN缓冲区就写入一个DATA 0 PID。即使在解除停止时,将设置端点状态写为 0 也将初始化端点。

停止

1表示端点处于停止状态。

### 应答 SETUP

命令: F1h

处理: 无

一个 SETUP 信息包的到达将 IN 缓冲区刷新并禁止对 IN 和 OUT 端点的两条命令: 使缓冲区有效和清零缓冲区命令。微控制器需要通过应答 SETUP 命令重新使能这些命令。这确保了最后的 SETUP 包留在缓冲区内,并且在微控制器看到 SETUP 包并应答之前,不会有任何包发回主机。微控制器必须将应答 SETUP 命令发送到 IN 和 OUT 端点。

#### 普通命令

### 发送恢复

命令: F6h

处理: 无

发送一个上行数据流恢复信号 10ms。该命令通常用于器件处于挂起状态时。恢复命令后不跟读出或写入的数据。

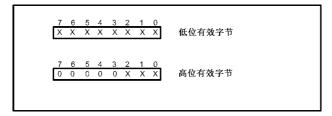

### 读当前帧数目

该命令后跟 1 到 2 个读出的字节并返回最后成功接收的 SOF 帧数目。帧数目为返回的低位字节

# 推荐的操作条件

| 符号                | 参数               | 测试条件                                   | 最小  | 最大       | 单位                   |

|-------------------|------------------|----------------------------------------|-----|----------|----------------------|

| $V_{CC1}$         | 电源电压(主模式)        | 仅将 V <sub>CC1</sub> 连接到 Vcc 脚          | 3.6 | 5.5      | V                    |

| $V_{CC2}$         | 电源电压 (可选模式)      | 将 V <sub>CC1</sub> 和 Vout3.3 连接到 Vcc 脚 | 3.0 | 3.6      | V                    |

| $V_{I}$           | DC 输入电压范围        |                                        | 0   | 5.5      | V                    |

| V <sub>I/O</sub>  | DC 输入电压范围(I/O 口) |                                        | 0   | 5.5      | V                    |

| V <sub>AI/O</sub> | DC输入电压范围(模拟I/O口) |                                        | 0   | 3.6      | V                    |

| Vo                | DC 输出电压范围        |                                        | 0   | $V_{CC}$ | V                    |

| Tamb              | 操作环境温度范围         | 见每个器件的 DC 和 AC 特性                      | -40 | 85       | $^{\circ}\mathbb{C}$ |

# DC 特性(数字脚)

| 符号             | 参数       | 测试条件                         | 最小      | 典型 | 最大  | 单位 |

|----------------|----------|------------------------------|---------|----|-----|----|

| 输入电            | 平        |                              |         |    |     |    |

| $V_{IL}$       | 低电平输入电压  |                              |         |    | 0.8 | V  |

| $V_{IH}$       | 高电平输入电压  |                              | 2.0     |    |     | V  |

| $V_{HYS}$      | 滞后电压     | ST(施密特触发)脚                   | 0.4     |    | 0.7 | V  |

| 输出电            | 平        |                              |         |    |     |    |

| V              | 低电平输出电压  | I <sub>OL</sub> =额定驱动        |         |    | 0.4 | V  |

| $V_{OL}$       | 队电丨棚山电压  | I <sub>OL</sub> =20μA        |         |    | 0.1 | V  |

| $V_{OH}$       | 高电平输出电压  | I <sub>OH</sub> =额定驱动        | 2.4     |    |     | V  |

|                |          | I <sub>OH</sub> =20μA        | Vcc-0.1 |    |     | V  |

| 漏电流            |          |                              |         |    |     |    |

| $I_{OZ}$       | OFF 状态电流 |                              |         |    | ±5  | μΑ |

| $I_L$          | 输入漏电流    | _                            |         |    | ±5  | μΑ |

| $I_S$          | 挂起电流     | 晶振停止,输入到 GND/V <sub>CC</sub> |         |    | 15  | μΑ |

| I <sub>O</sub> | 操作电流     |                              |         | 15 |     | mA |

# DC 特性(模拟 I/0 脚)

| 符号        | 参数          | 测试条件                      | 最小  | 最大  | 单位 |

|-----------|-------------|---------------------------|-----|-----|----|

| 漏电流       |             | •                         |     |     |    |

| $I_{LO}$  | 高阻态数据输入线漏电流 | $0V < V_{IN} < 3.3V$      |     | ±10 | μA |

| 输入电       | 平           |                           |     |     |    |

| $V_{DI}$  | 差分输入灵敏度     | (D+) - (D-)               | 0.2 |     | V  |

| $V_{CM}$  | 差分共模范围      | 包含 VDI 范围                 | 0.8 | 2.5 | V  |

| $V_{SE}$  | 单端接收器阀值电压   |                           | 0.8 | 2.0 | V  |

| 输出电       | 平           |                           |     |     |    |

| $V_{OL}$  | 静态输出低电压     | 对地负载 $R_L$ =1.5 $k\Omega$ |     | 0.3 | V  |

| $V_{OH}$  | 静态输出高电压     | 对地负载 $R_L$ =15k $\Omega$  | 2.8 | 3.6 | V  |

| 电容        |             |                           |     |     |    |

| $C_{IN}$  | 收发器电容       | 脚对地                       |     | 20  | pF |

| 输出电阻      | <u></u>     |                           |     | •   | •  |

| $Z_{DRV}$ | 驱动器输出电阻     | 稳态驱动                      | 29  | 44  | Ω  |

| 上拉电阻      | <u></u>     |                           |     | •   | •  |

| $Z_{PU}$  | 上拉电阻        | SoftConnect 打开            | 1.1 | 1.9 | kΩ |

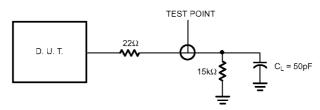

# D+/D-负载

## 1.5kΩ IS INTERNAL

# AC 特性 (I/O 口, 全速)

| 符号               | 参数           | 测试条件              | 最小    | 最大   | 单位 |

|------------------|--------------|-------------------|-------|------|----|

| 驱动器特             | <b>针性</b>    | $C_L$ =50PF       |       |      |    |

|                  |              | Rpu=1.5kΩ D+到 Vcc |       |      |    |

|                  | 转换时间         |                   |       |      |    |

| Tr               | 上升时间         | 10%到 90%之间        | 4     | 20   | ns |

| Tf               | 下降时间         |                   | 4     | 20   | ns |

| $T_{RFM}$        | 上升/下降时间匹配    | $(t_r/r_f)$       | 90    | 110  | %  |

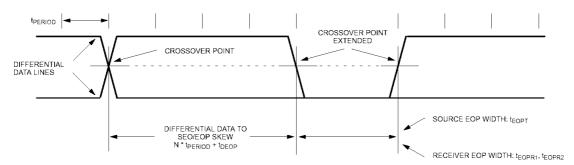

| V <sub>CRS</sub> | 输出信号交迭电压     |                   | 1.3   | 2.0  | V  |

| 驱动器时             | 序            |                   |       |      |    |

| $T_{EOPT}$       | 源 EOP 宽度     | 图 1               | 160   | 175  | ns |

| $T_{DEOP}$       | 差分数据到 EOP 转换 | 图 1               | -2    | 5    | ns |

| 接收器时             | 序            |                   |       |      |    |

|                  | 接收数据抖动误差     | 该特性并未经生产测试        |       |      |    |

| $T_{JR1}$        | 到下一次转换       | 而是由设计保证           | -18.5 | 18.5 | ns |

| $T_{JR2}$        | 成对的转换        |                   | -9    | 9    | ns |

|                  | 接收器 EOP 宽度   |                   |       |      |    |

| $T_{EOPR1}$      | 必须拒绝         | 图 1               | 40    |      | ns |

| $T_{EOPR2}$      | 必须接受         |                   | 82    |      | ns |

图 1 差分数据的 EOP 转换失真和 EOP 宽度

# AC 特性(并行接口)

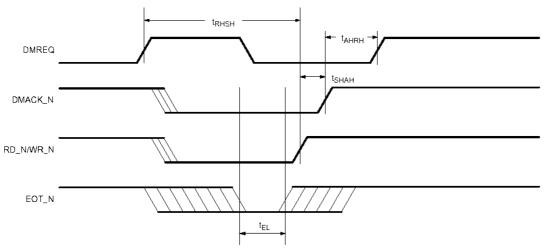

| 符号                | 参数                                          | 测试条件 | 最小        | 最大 | 单位 |

|-------------------|---------------------------------------------|------|-----------|----|----|

| ALE 时序            |                                             |      |           |    |    |

| $T_{LH}$          | ALE 高脉冲宽度                                   |      | 20        |    | ns |

| $T_{AVLL}$        | 地址有效到 ALE 变低时间                              |      | 10        |    | ns |

| $T_{LLAX}$        | ALE 低到地址转换时间                                |      |           | 10 | ns |

| 突发 DMA F          | <b></b><br>                                 |      |           |    |    |

| $T_{CLWL}$        | CS_N (DMACK_N) 低到 WR_N 低时间                  |      | $0^1$     |    | ns |

| $T_{WHCH}$        | WR_N 高到 CS_N(DMACK_N)高时间                    |      | 5         |    | ns |

| T <sub>AVWI</sub> | A0 有效到 WR N 低时间                             |      | $0^1$     |    | ns |

| 1 AVWL            | _                                           |      | $130^{2}$ |    | ns |

| $T_{WHAX}$        | WR_N 高到 A0 转换时间                             |      | 5         |    | ns |

| $T_{WL}$          | WR_N 低脉宽                                    |      | 20        |    | ns |

| $T_{WDSU}$        | 写数据建立时间                                     |      | 30        |    | ns |

| $T_{WDH}$         | 写数据保持时间                                     |      | 10        |    | ns |

| $T_{WC}$          | 写周期                                         |      | 500       |    | ns |

| 读时序               |                                             |      |           |    |    |

| Т                 | CS N(DMACK N)低到 RD N 低时间                    |      | $0^{1}$   | 40 | ns |

| $T_{CLRL}$        | C2_IN(DIVIACK_IN)[K] FIJ KD_IN [K] FIJ [II] |      | $130^{2}$ |    | ns |

| $T_{RHCH}$        | RD_N 高到 CS_N(DMACK_N)高时间                    |      | 5         |    | ns |

| T <sub>AVRL</sub> | A0 有效到 RD_N 低时间                             |      | $0^1$     |    | ns |

| $T_{RL}$   | RD_N 低脉宽          | 20  |    | ns |

|------------|-------------------|-----|----|----|

| $T_{RLDD}$ | RD_N 低到数据驱动时间     |     | 20 | ns |

| $T_{RHDZ}$ | RD_N 高到数据 Hi-Z 时间 |     | 20 | ns |

| $T_{RC}$   | 读周期               | 500 |    | ns |

# 1. 可以为负

# 2. DMA 访问时,仅当第 64 个字节和倒数第二个(EOT-1)字节

图 3 并行接口时序(I/O和DMA)

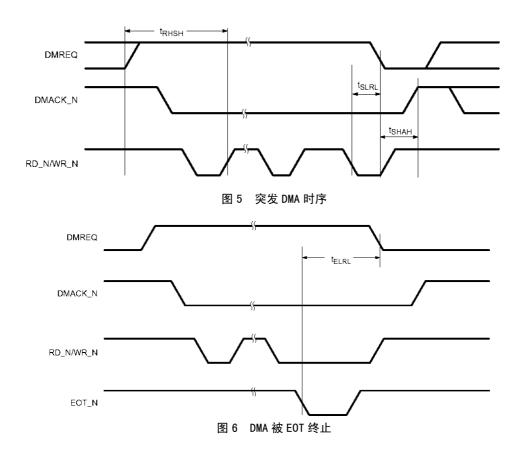

# AC 特性 (DMA)

| 符号          | 参数                                              | 测试条件 | 最小  | 最大  | 单位 |

|-------------|-------------------------------------------------|------|-----|-----|----|

| 单周期 DMA     | 时序                                              |      |     |     |    |

| $T_{AHRH}$  | DMACK_N 高到 DMREQ 高时间                            |      |     | 330 | ns |

| $T_{SHAH}$  | RD_N/WR_N 高到 DMACK_N 高时间                        |      | 130 |     | ns |

| $T_{RHSH}$  | DMREQ 高到 RD_N/WR_N 高时间                          |      | 120 |     | ns |

| $T_{EL}$    | EOT_N低脉冲宽度(DMACK_N,RD_N/WR_N<br>和 EOT_N 同时为低时间) |      | 10  |     | ns |

| 突发 DMA 时    | <b></b><br>                                     |      |     |     |    |

| $T_{SLRL}$  | RD_N/WR_N 低到 DMREQ 高时间                          |      |     | 40  | ns |

| $T_{RHNDV}$ | RD_N 高到下个数据有效                                   |      |     | 420 | ns |

| EOT 时序      |                                                 |      |     |     | •  |

| $T_{ELRL}$  | EOT_N 低到 DMREQ 低时间                              |      |     | 40  | ns |

注: 当 DMACK\_N, RD\_N/WR\_N 和 EOT\_N 全为低时,EOT\_N 被认为有效。

图 4 单周期 DMA 时序

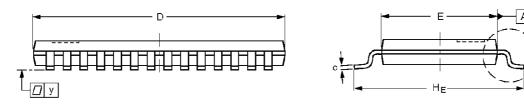

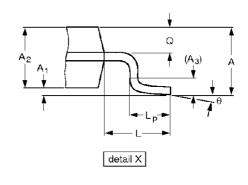

# TSSOP28: 塑料极小型封装; 28 脚; 本体宽度 4.4mm

# DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С          | D <sup>(1)</sup> | E (2)      | е    | HE         | L   | Lp           | Q          | v   | w    | У   | Z <sup>(1)</sup> | 0        |

|------|-----------|----------------|----------------|----------------|--------------|------------|------------------|------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 9.8<br>9.6       | 4.5<br>4.3 | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.8<br>0.5       | 8°<br>0° |

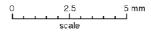

# S028: 塑料小型封装; 28 脚; 本体宽度 7.5mm

0 5 10 mm

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | <b>A</b> <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp             | c              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q          | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|-----------------------|----------------|----------------|----------------|----------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10          | 2.45<br>2.25   | 0.25           | 0.49<br>0.36   | 0.32<br>0.23   | 18.1<br>17.7     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0 | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004        | 0.096<br>0.089 | 0.01           | 0.019<br>0.014 | 0.013<br>0.009 | 0.71<br>0.69     | 0.30<br>0.29     | 0.050 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | o° |